Networks on Chip Axel Jantsch 1 Shashi Kumar

- Slides: 21

Networks on Chip Ø Axel Jantsch 1 Ø Shashi Kumar 1, Juha-Pekka Soininen 2, Martti Forsell 2, Mikael Millberg 1, Johnny Öberg 1, Kari Tiensurjä 2, Ahmed Hemani 3 Ø 1 Lab. Ø 2 VTT Ø 3 Spirea Of Electronics and Computer Systems, Royal Institute of Technology, Stockholm Electronics, Oulu, Finland AB, Kista Axel Jantsch 1

Outline Ø Background and Introduction Ø NOC Architecture: Basic features v. Physical Level_Architectural Level Design Integration v. Packets switched communication rather than wires v. Region Ø A Methodology for NOC design Ø Conclusions RVK 2002, Stockholm 10 -13 th Junel 2002 Axel Jantsch 2

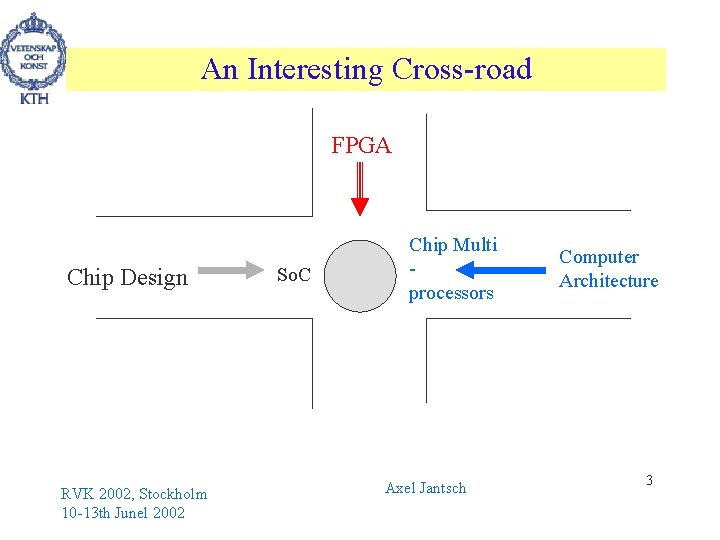

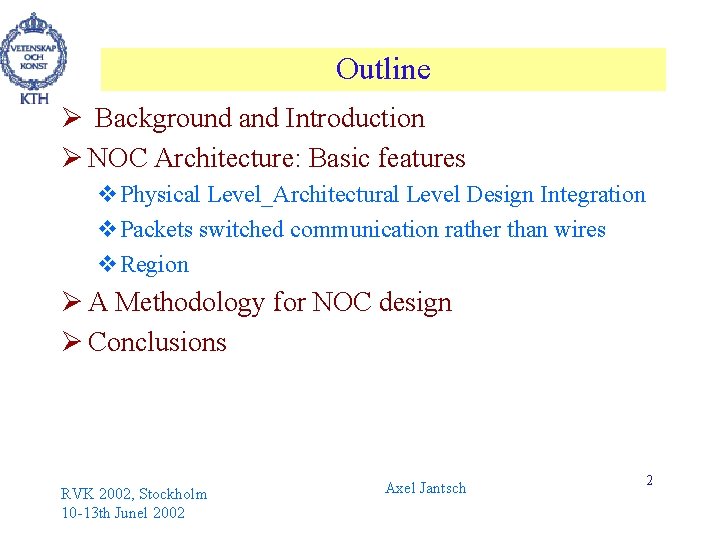

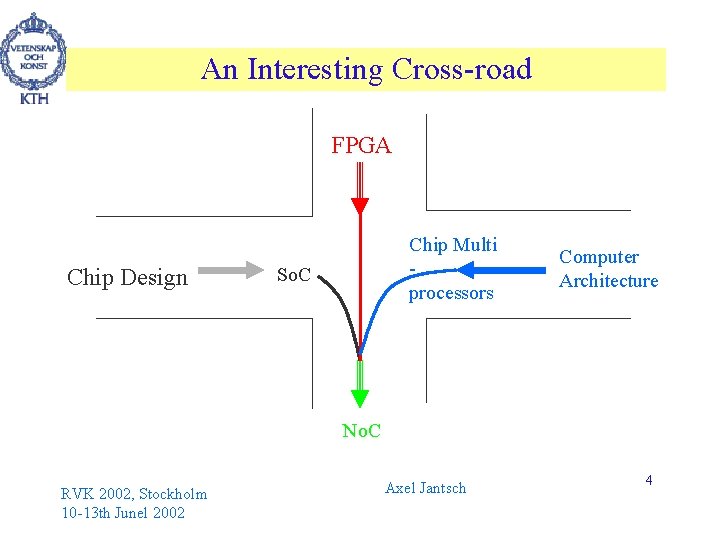

An Interesting Cross-road FPGA Chip Design RVK 2002, Stockholm 10 -13 th Junel 2002 So. C Chip Multi processors Axel Jantsch Computer Architecture 3

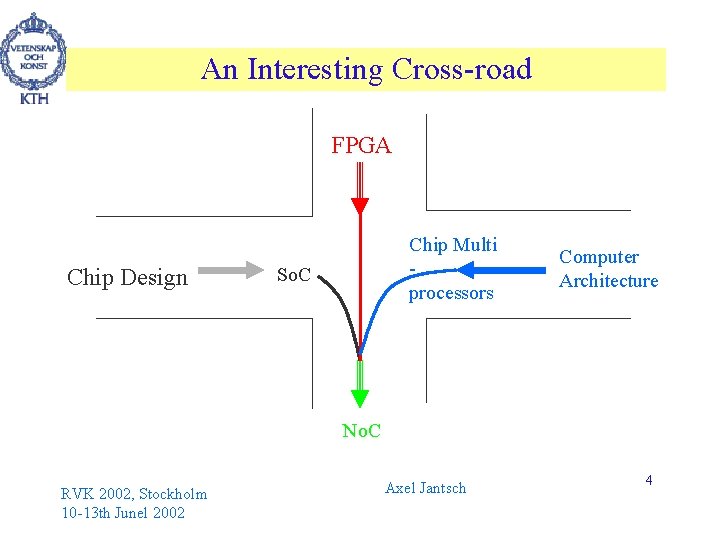

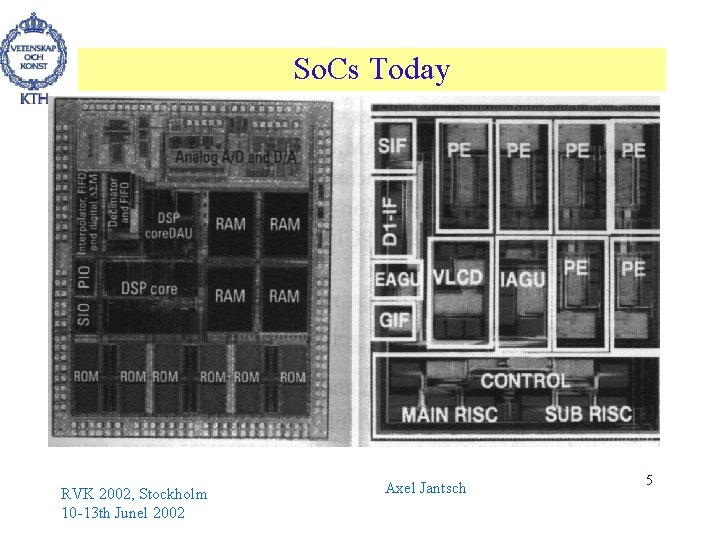

An Interesting Cross-road FPGA Chip Design Chip Multi processors So. C Computer Architecture No. C RVK 2002, Stockholm 10 -13 th Junel 2002 Axel Jantsch 4

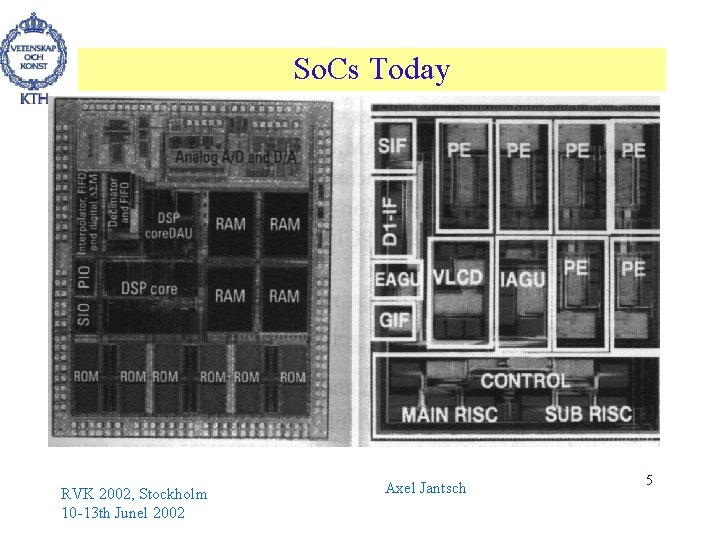

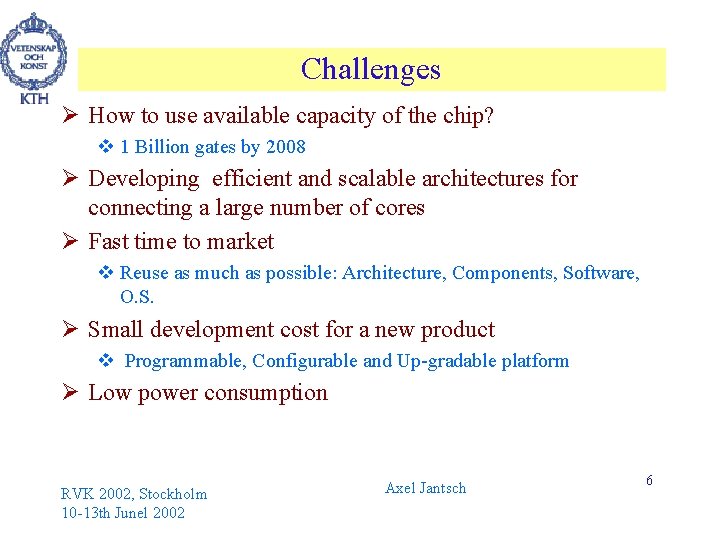

So. Cs Today RVK 2002, Stockholm 10 -13 th Junel 2002 Axel Jantsch 5

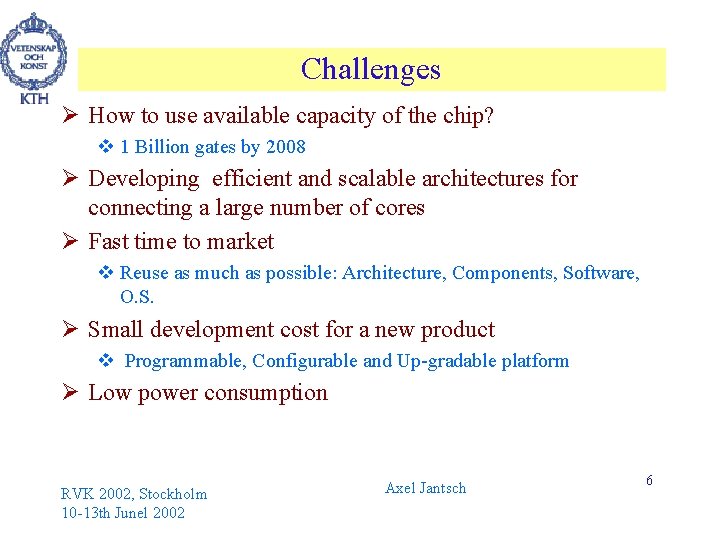

Challenges Ø How to use available capacity of the chip? v 1 Billion gates by 2008 Ø Developing efficient and scalable architectures for connecting a large number of cores Ø Fast time to market v Reuse as much as possible: Architecture, Components, Software, O. S. Ø Small development cost for a new product v Programmable, Configurable and Up-gradable platform Ø Low power consumption RVK 2002, Stockholm 10 -13 th Junel 2002 Axel Jantsch 6

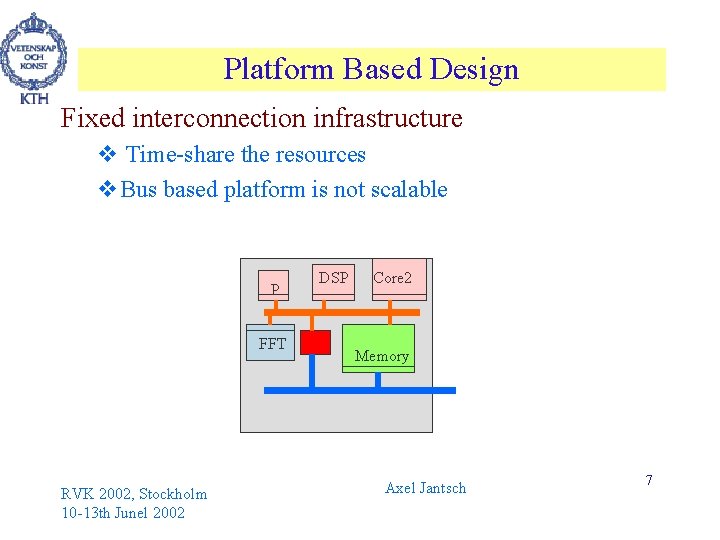

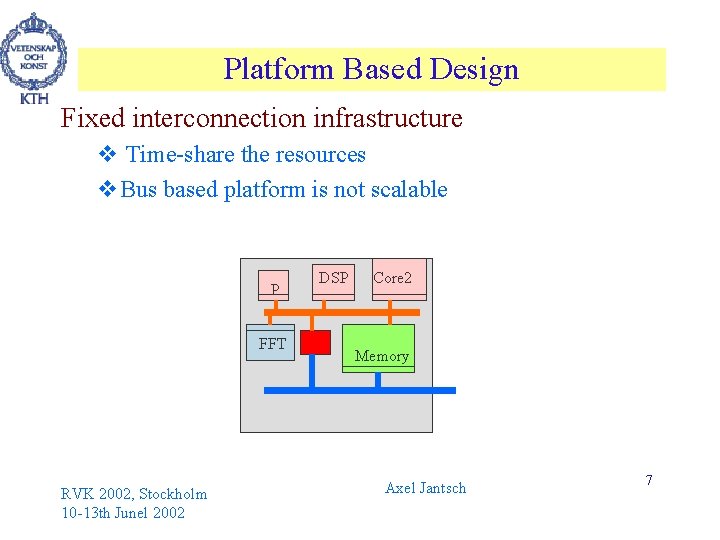

Platform Based Design Fixed interconnection infrastructure v Time-share the resources v. Bus based platform is not scalable P FFT RVK 2002, Stockholm 10 -13 th Junel 2002 DSP Core 2 Memory Axel Jantsch 7

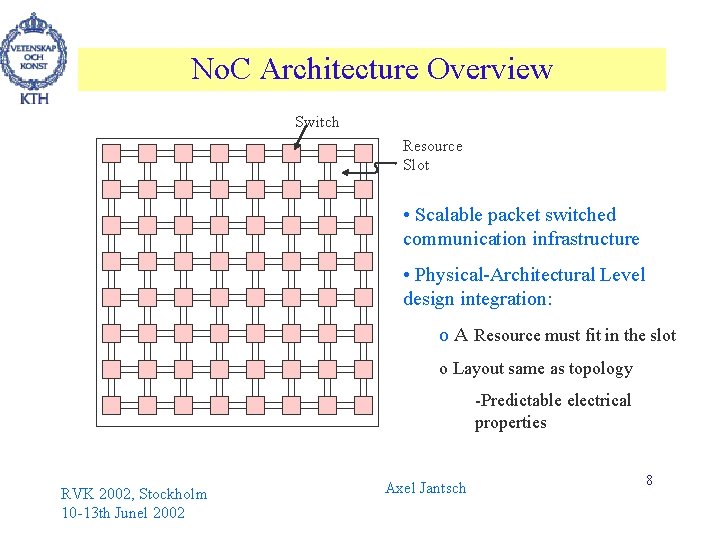

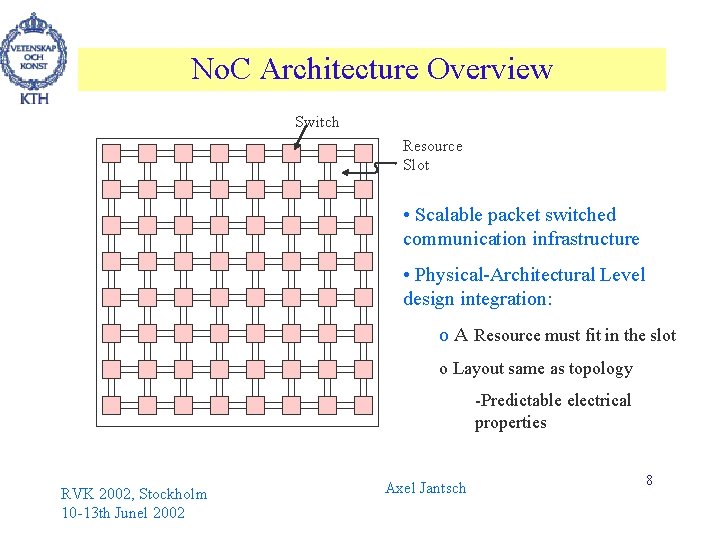

No. C Architecture Overview Switch Resource Slot • Scalable packet switched communication infrastructure • Physical-Architectural Level design integration: o A Resource must fit in the slot o Layout same as topology -Predictable electrical properties RVK 2002, Stockholm 10 -13 th Junel 2002 Axel Jantsch 8

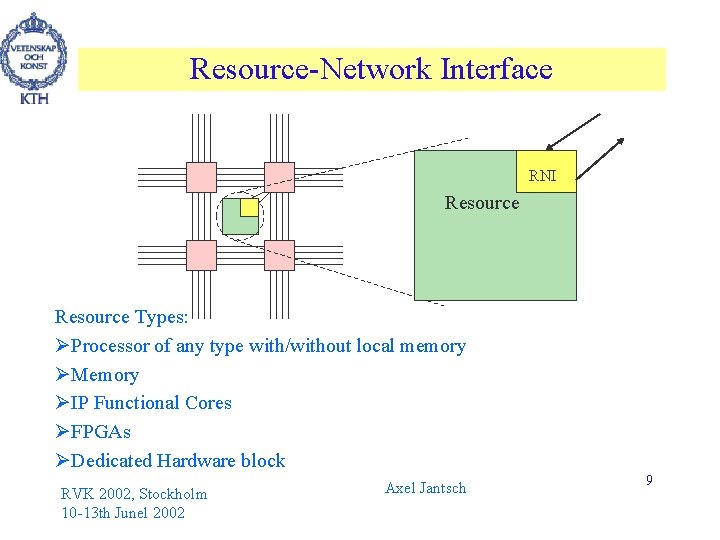

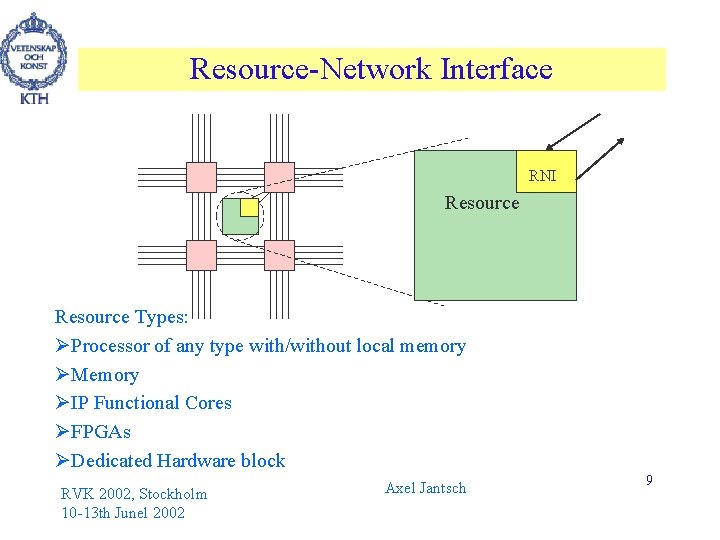

Resource-Network Interface RNI Resource Types: ØProcessor of any type with/without local memory ØMemory ØIP Functional Cores ØFPGAs ØDedicated Hardware block RVK 2002, Stockholm 10 -13 th Junel 2002 Axel Jantsch 9

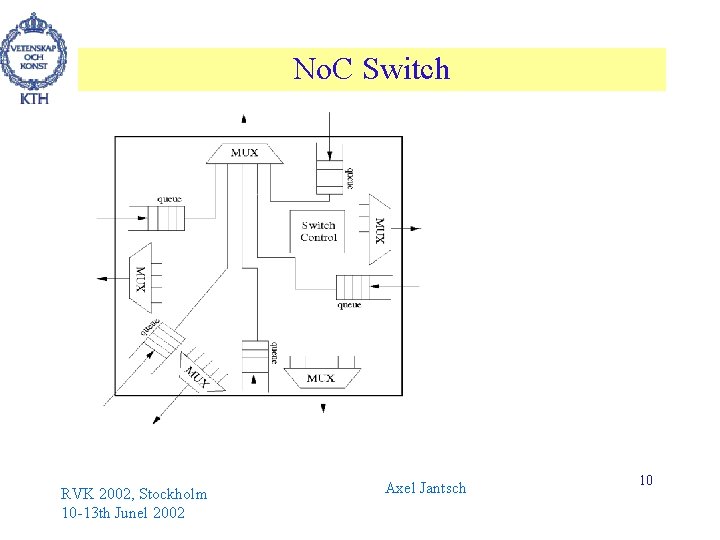

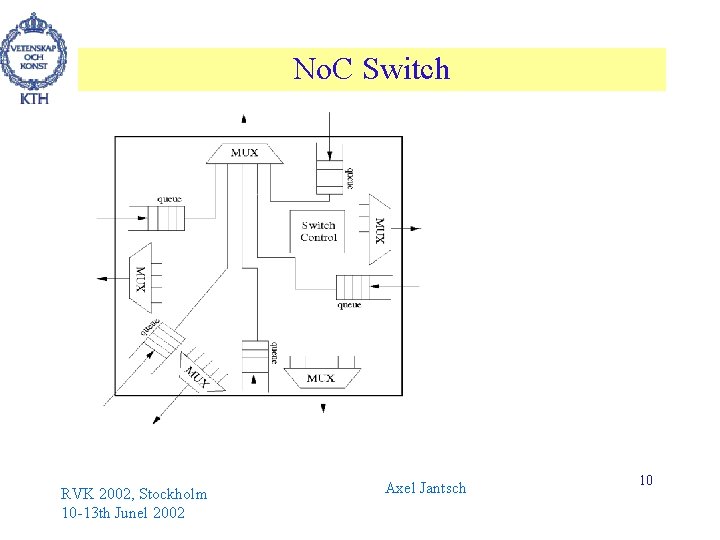

No. C Switch RVK 2002, Stockholm 10 -13 th Junel 2002 Axel Jantsch 10

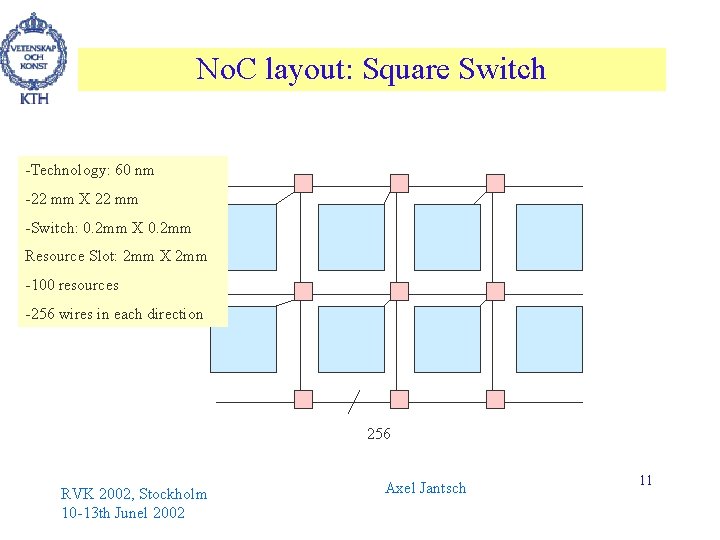

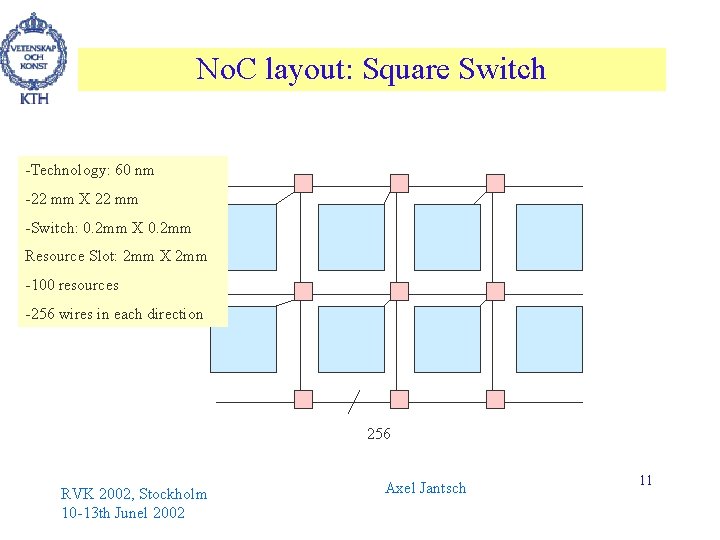

No. C layout: Square Switch -Technology: 60 nm -22 mm X 22 mm -Switch: 0. 2 mm X 0. 2 mm Resource Slot: 2 mm X 2 mm -100 resources -256 wires in each direction 256 RVK 2002, Stockholm 10 -13 th Junel 2002 Axel Jantsch 11

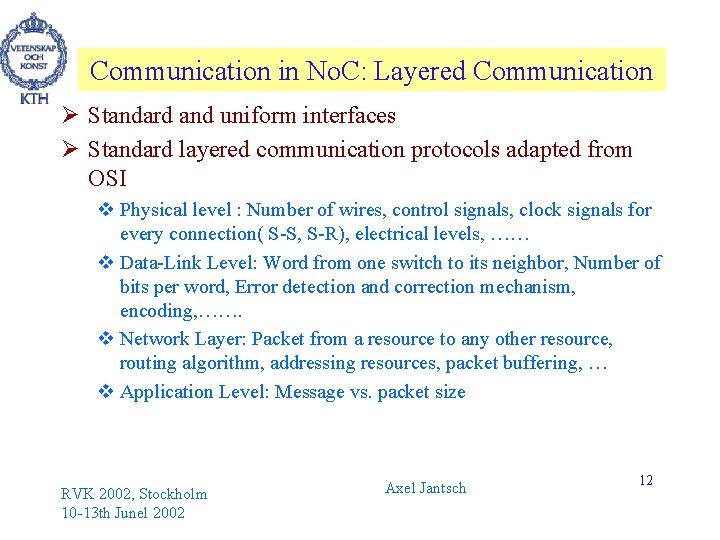

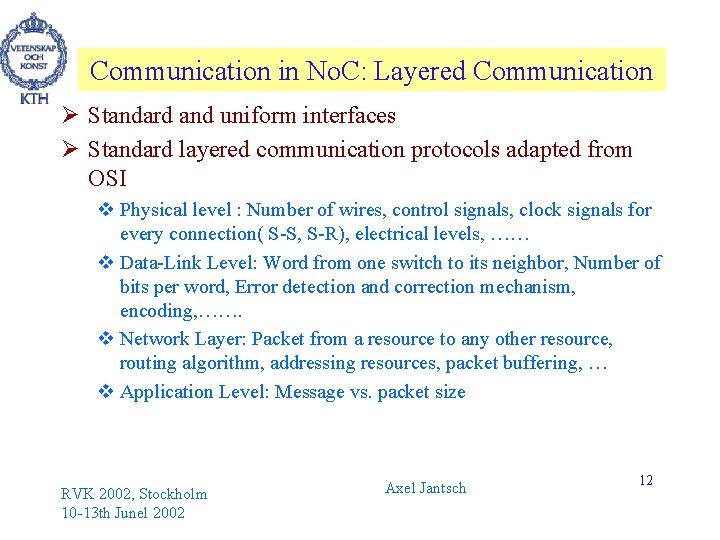

Communication in No. C: Layered Communication Ø Standard and uniform interfaces Ø Standard layered communication protocols adapted from OSI v Physical level : Number of wires, control signals, clock signals for every connection( S-S, S-R), electrical levels, …… v Data-Link Level: Word from one switch to its neighbor, Number of bits per word, Error detection and correction mechanism, encoding, ……. v Network Layer: Packet from a resource to any other resource, routing algorithm, addressing resources, packet buffering, … v Application Level: Message vs. packet size RVK 2002, Stockholm 10 -13 th Junel 2002 Axel Jantsch 12

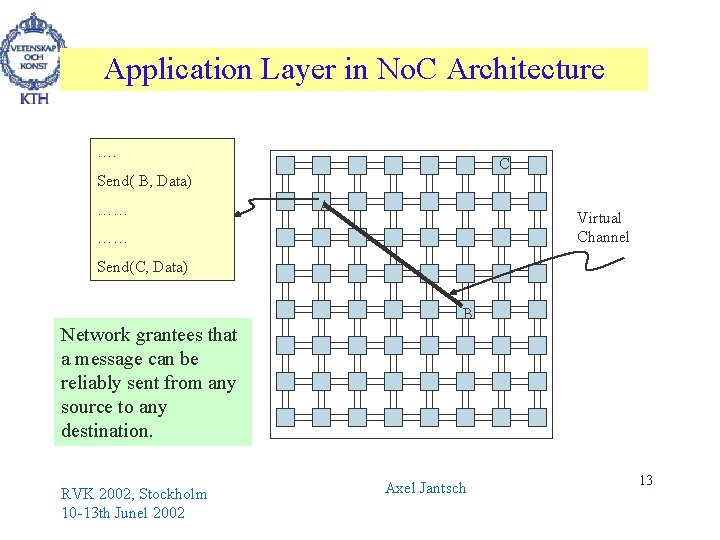

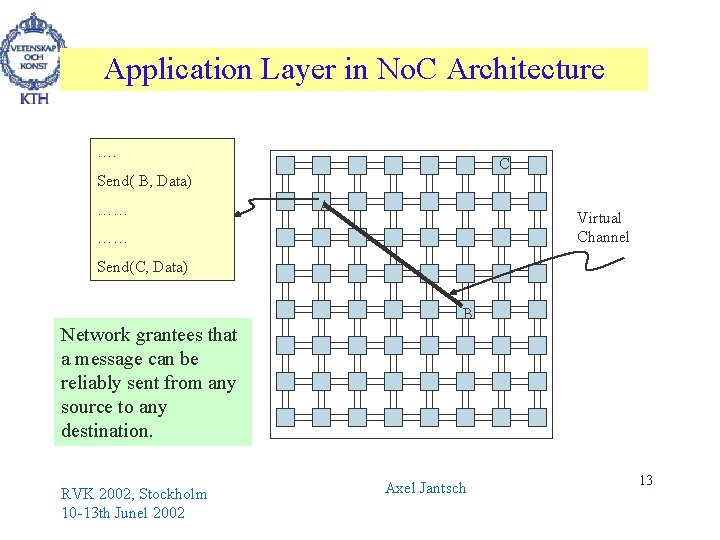

Application Layer in No. C Architecture …. C Send( B, Data) …… A Virtual Channel …… Send(C, Data) B Network grantees that a message can be reliably sent from any source to any destination. RVK 2002, Stockholm 10 -13 th Junel 2002 Axel Jantsch 13

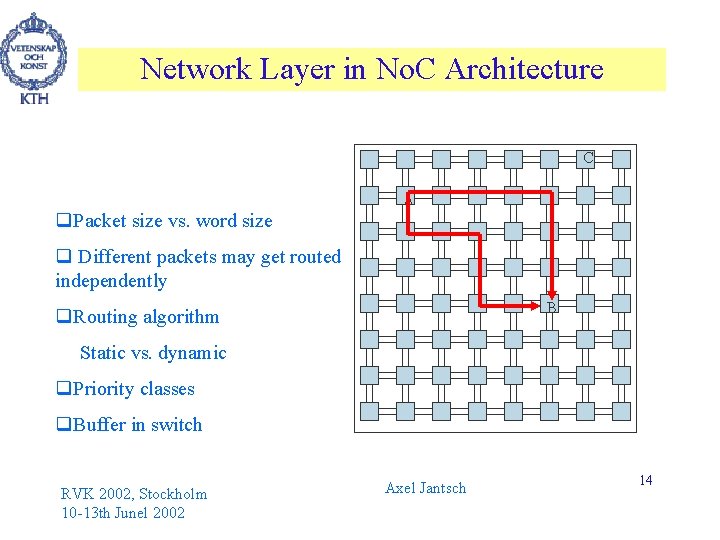

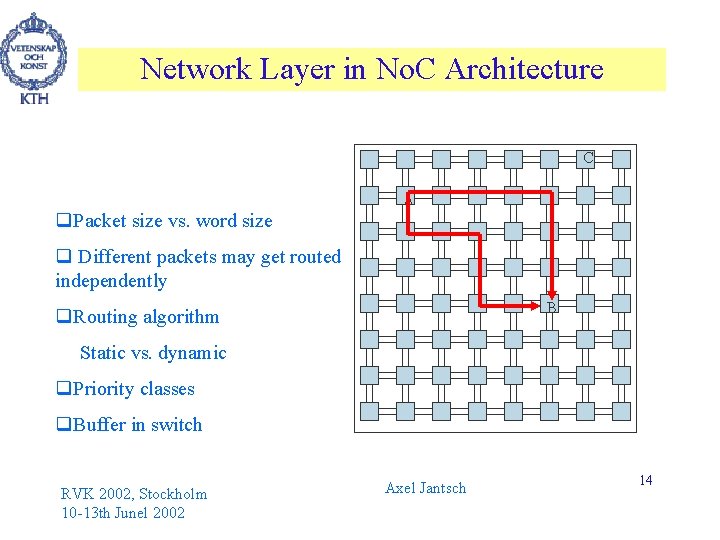

Network Layer in No. C Architecture C q. Packet size vs. word size A q Different packets may get routed independently B q. Routing algorithm Static vs. dynamic q. Priority classes q. Buffer in switch RVK 2002, Stockholm 10 -13 th Junel 2002 Axel Jantsch 14

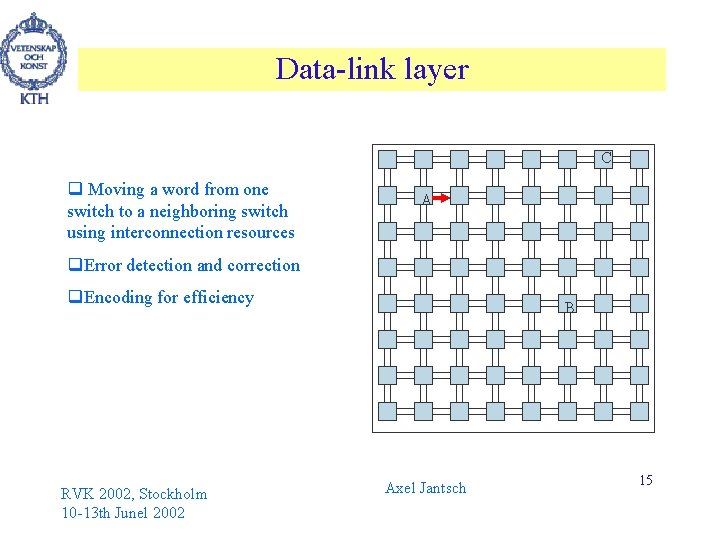

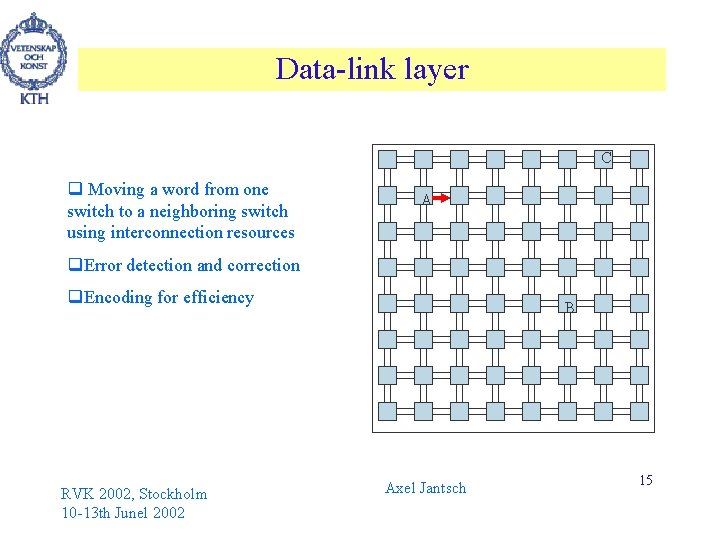

Data-link layer C q Moving a word from one switch to a neighboring switch using interconnection resources A q. Error detection and correction q. Encoding for efficiency RVK 2002, Stockholm 10 -13 th Junel 2002 B Axel Jantsch 15

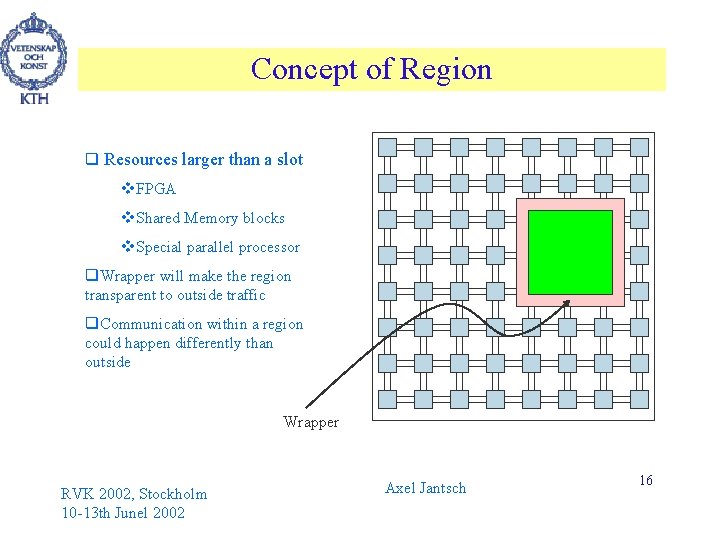

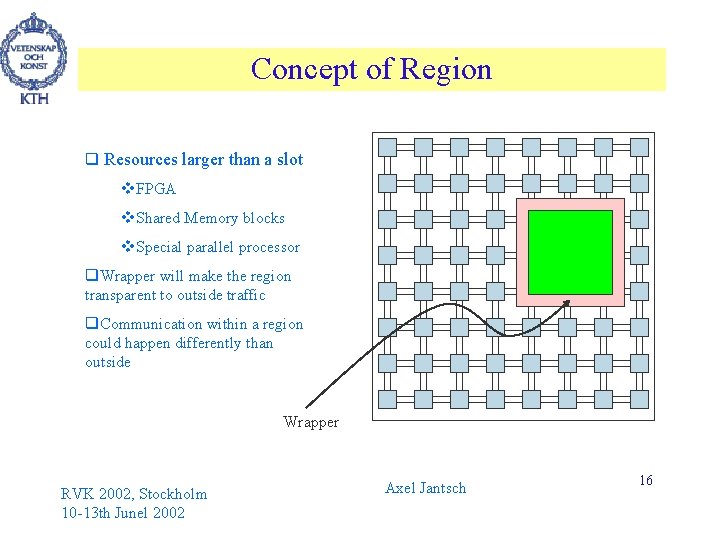

Concept of Region q Resources larger than a slot v. FPGA v. Shared Memory blocks v. Special parallel processor q. Wrapper will make the region transparent to outside traffic q. Communication within a region could happen differently than outside Wrapper RVK 2002, Stockholm 10 -13 th Junel 2002 Axel Jantsch 16

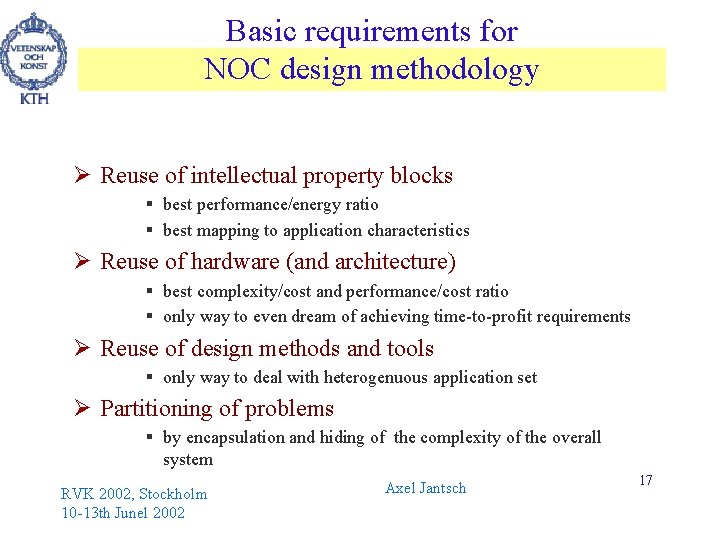

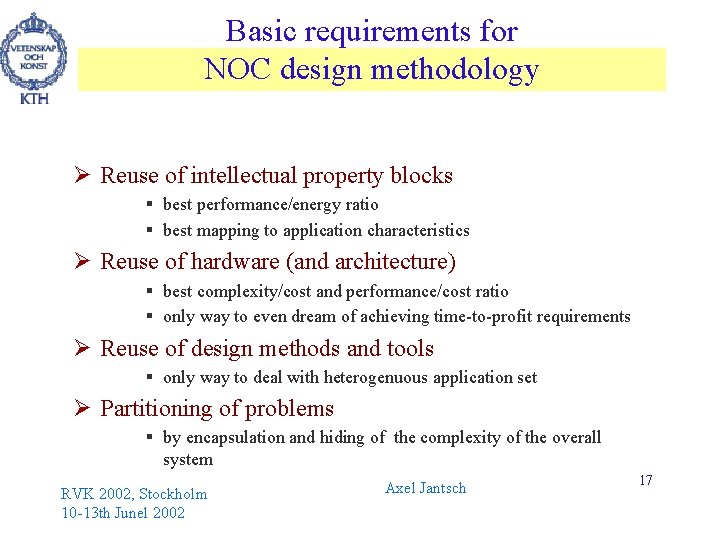

Basic requirements for NOC design methodology Ø Reuse of intellectual property blocks § best performance/energy ratio § best mapping to application characteristics Ø Reuse of hardware (and architecture) § best complexity/cost and performance/cost ratio § only way to even dream of achieving time-to-profit requirements Ø Reuse of design methods and tools § only way to deal with heterogenuous application set Ø Partitioning of problems § by encapsulation and hiding of the complexity of the overall system RVK 2002, Stockholm 10 -13 th Junel 2002 Axel Jantsch 17

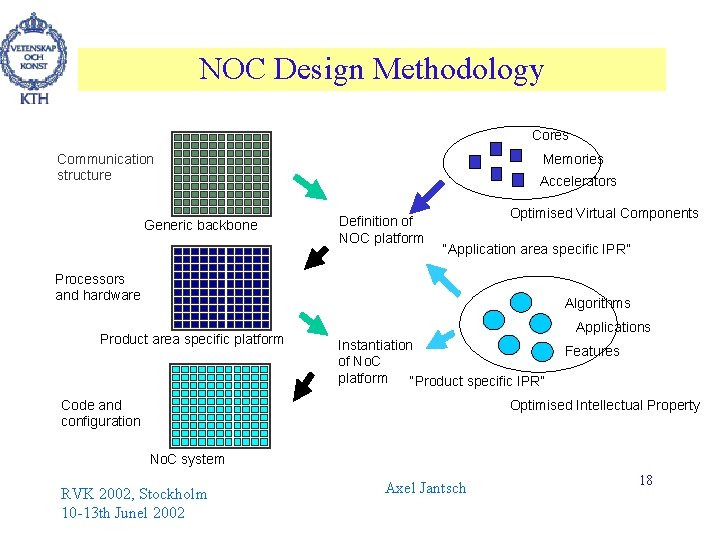

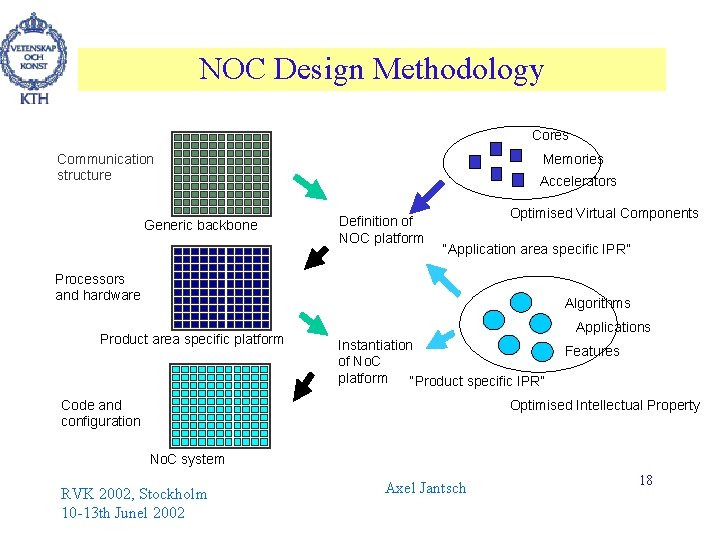

NOC Design Methodology Cores Communication structure Generic backbone Memories Accelerators Definition of NOC platform Optimised Virtual Components “Application area specific IPR” Processors and hardware Algorithms Product area specific platform Applications Instantiation of No. C platform “Product specific IPR” Code and configuration Features Optimised Intellectual Property No. C system RVK 2002, Stockholm 10 -13 th Junel 2002 Axel Jantsch 18

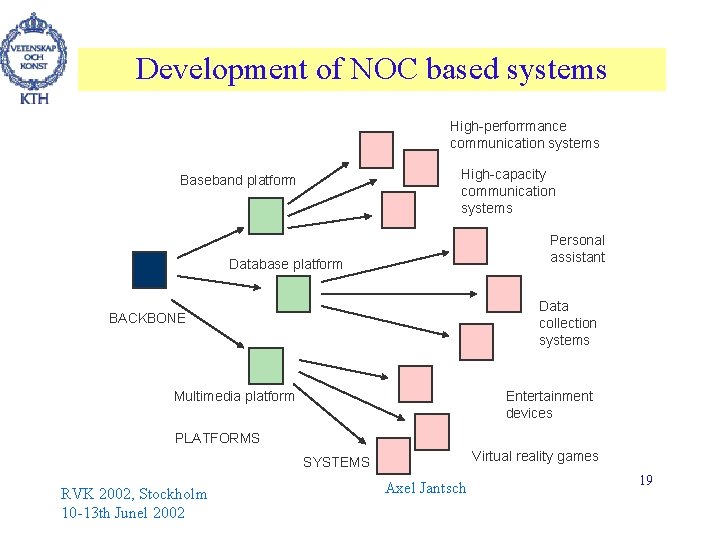

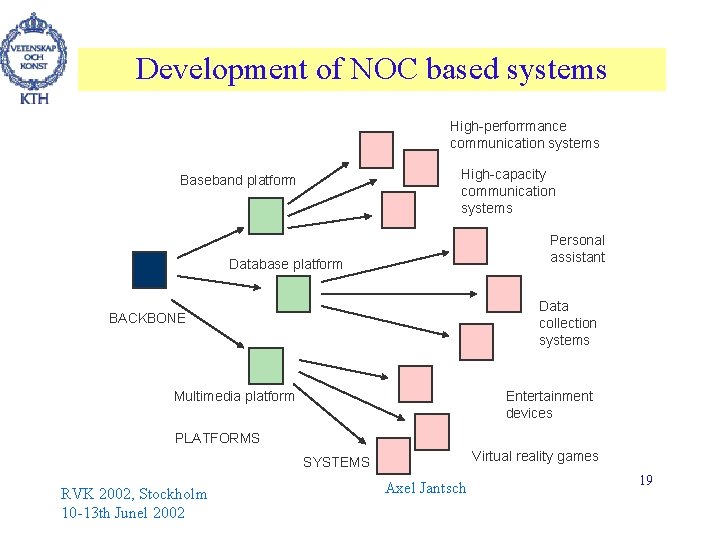

Development of NOC based systems High-perforrmance communication systems High-capacity communication systems Baseband platform Personal assistant Database platform Data collection systems BACKBONE Entertainment devices Multimedia platform PLATFORMS Virtual reality games SYSTEMS RVK 2002, Stockholm 10 -13 th Junel 2002 Axel Jantsch 19

Conclusions Ø No. C architecture provides a So. C development platform which allows reuse at many levels v. Reduces time to design v. Reduces time to test Ø Concurrency becomes a first class object Ø No. C design has a lot in common with Distributed System design RVK 2002, Stockholm 10 -13 th Junel 2002 Axel Jantsch 20

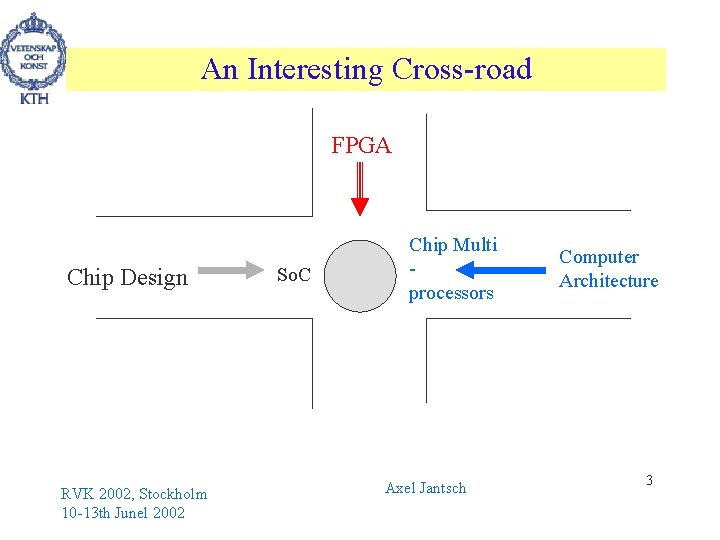

Key Prerequisites Ø No. C Architecture: sufficiently general and efficient Ø No. C Assembler Language: Standard interface between application and platform Ø No. C Operating System Ø No. C Design Methodology and Tools Ø Scalability: v Size v Performance v Power v Reliability v Technology RVK 2002, Stockholm 10 -13 th Junel 2002 Axel Jantsch 21