Delay Chip Prototype Delay Chip Test Board Joan

Delay Chip Prototype & Delay Chip Test Board Joan Mauricio – Xavier Ondoño La Salle (URL) 12/04/2013 09/02/2012 1

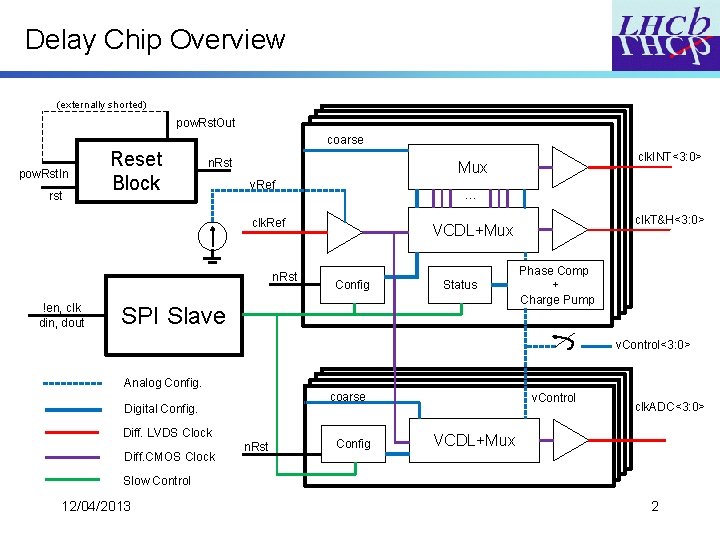

Delay Chip Overview (externally shorted) pow. Rst. Out coarse pow. Rst. In rst Reset Block n. Rst v. Ref ··· clk. Ref n. Rst !en, clk din, dout clk. INT<3: 0> Mux clk. T&H<3: 0> VCDL+Mux Config Status SPI Slave Phase Comp + Charge Pump v. Control<3: 0> Analog Config. coarse Digital Config. Diff. LVDS Clock Diff. CMOS Clock n. Rst Config v. Control clk. ADC<3: 0> VCDL+Mux Slow Control 12/04/2013 2

Delay Chip Features (1/3) – QFN 48 Package. – 4 DLL Channels (12 sub-channels). – Jitter: 4 ps. – DNL: 18 ps. – Delay Range: 17. 45 ~ 39. 88 ns. – ~280 m. W power consumption. – 70 m. W per DLL Channel. – INT/T&H DLL: 27 m. W. – ADC DLL: 13 m. W. – 3 LVDS Drivers: 30 m. W. 12/04/2013 3

Delay Chip Features (2/3) – Each DLL channel contains: – – – – 12/04/2013 1 x LVDS to CMOS driver. 2 x VCDLs. 3 x Multiplexors. 1 x Phase Comparator. 1 x Charge Pump. 2 x Configuration Registers. 1 x Status Register 3 x CMOS to LVDS driver. 4

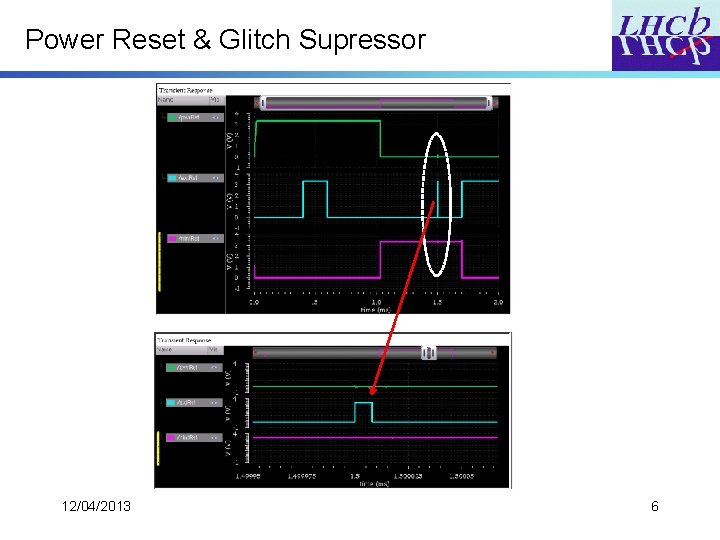

Delay Chip Features (3/3) – SPI Slave: – – Interfaces with SPI Master (Mode 1). Works fine @ 20 Mbps. Up to 32 Configuration registers and 32 Status Registers. Also implements a software reset (used to clear the charge pumps). – Serial Registers: – 16 Bits R/W TMR Registers (Configuration). – 8 Bits RO (Status). No memory. – Reset: – Power Reset signal (1 -ms-wide, active high) is generated. – Power Reset can be inhibited by not shorting pins 47 and 48. – Glitch supressor ensures that SETs do not accidentally reset the chip (up to 8 -ns-wide glitch). 12/04/2013 5

Power Reset & Glitch Supressor 12/04/2013 6

SPI Slave Addressing Scheme b 7 b 6 b 5 b 4 b 3 b 2 b 1 b 0 R/!W Pump Rst Status/!Conf RSEL 4 RSEL 3 RSEL 2 RSEL 1 RSEL 0 ADDR ICECAL Ch Width (bits) Description 0 x 00 0 x 01 0 x 02 0 x 03 ··· 0 x 10 0 x 11 0 x 12 0 x 13 ··· 0 x 40 ··· 0 x. A 0 0 x. A 1 0 x. B 0 0 x. B 1 ··· 0 x. FF 0 0 1 1 16 16 Integrator / Track&Hold Clock Configuration Register. ADC Clock Configuration Register. 2 2 3 3 16 16 Integrator / Track&Hold Clock Configuration Register. ADC Clock Configuration Register. Any - Software Reset of the Charge Pumps. 0 1 2 3 8 8 Status Register. - - SDI / SDO Bypass. For testing purposes. 12/04/2013 7

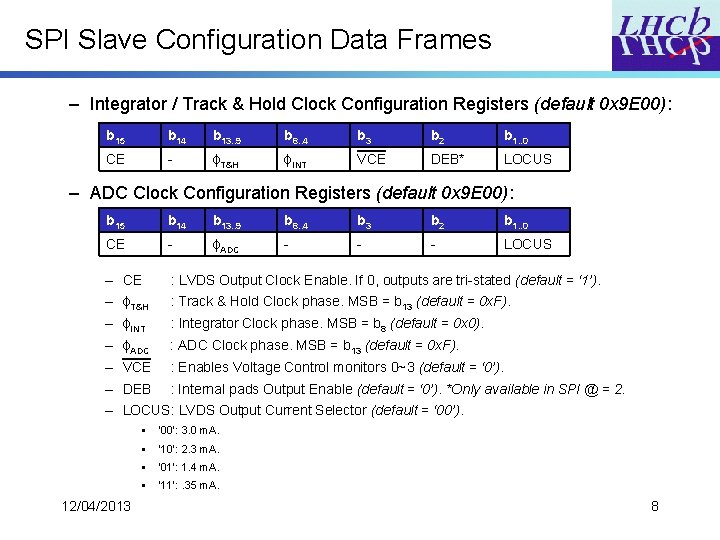

SPI Slave Configuration Data Frames – Integrator / Track & Hold Clock Configuration Registers (default 0 x 9 E 00): b 15 b 14 b 13. . 9 b 8. . 4 b 3 b 2 b 1. . 0 CE - ϕT&H ϕINT VCE DEB* LOCUS – ADC Clock Configuration Registers (default 0 x 9 E 00): b 15 b 14 b 13. . 9 b 8. . 4 b 3 b 2 b 1. . 0 CE - ϕADC - - - LOCUS – CE : LVDS Output Clock Enable. If 0, outputs are tri-stated (default = ‘ 1’). – ϕT&H : Track & Hold Clock phase. MSB = b 13 (default = 0 x. F). – ϕINT : Integrator Clock phase. MSB = b 8 (default = 0 x 0). – ϕADC : ADC Clock phase. MSB = b 13 (default = 0 x. F). – VCE : Enables Voltage Control monitors 0~3 (default = ‘ 0’). – DEB : Internal pads Output Enable (default = ‘ 0’). *Only available in SPI @ = 2. – LOCUS: LVDS Output Current Selector (default = ‘ 00’). 12/04/2013 § ‘ 00’: 3. 0 m. A. § ‘ 10’: 2. 3 m. A. § ’ 01’: 1. 4 m. A. § ‘ 11’: . 35 m. A. 8

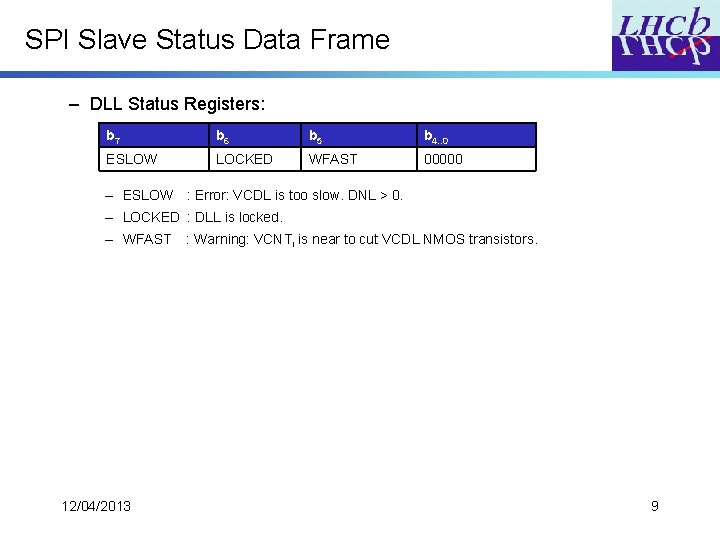

SPI Slave Status Data Frame – DLL Status Registers: b 7 b 6 b 5 b 4. . 0 ESLOW LOCKED WFAST 00000 – ESLOW : Error: VCDL is too slow. DNL > 0. – LOCKED : DLL is locked. – WFAST 12/04/2013 : Warning: VCNTi is near to cut VCDL NMOS transistors. 9

TEST BOARD… 09/02/2012

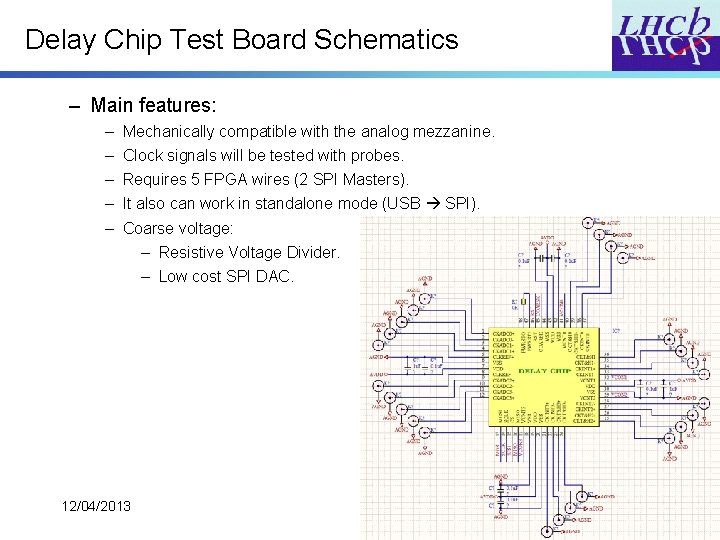

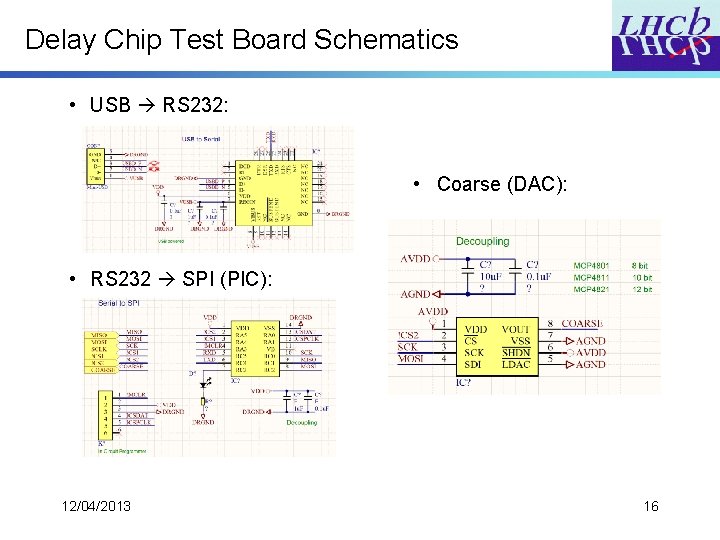

Delay Chip Test Board Schematics – Main features: – – – Mechanically compatible with the analog mezzanine. Clock signals will be tested with probes. Requires 5 FPGA wires (2 SPI Masters). It also can work in standalone mode (USB SPI). Coarse voltage: – Resistive Voltage Divider. – Low cost SPI DAC. 12/04/2013 11

BACKUP… 09/02/2012

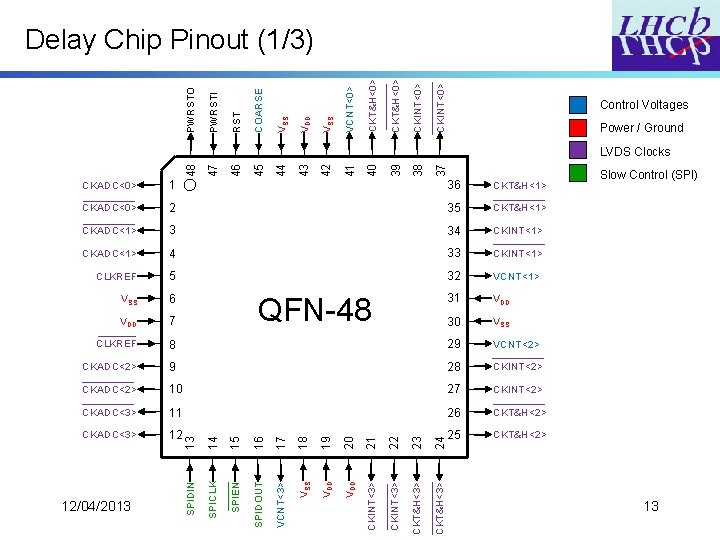

CKINT<0> CKT&H<0> VCNT<0> VSS VDD VSS COARSE RST PWRSTI PWRSTO Delay Chip Pinout (1/3) Control Voltages Power / Ground 37 38 39 40 41 42 43 44 45 46 47 48 LVDS Clocks CKADC<0> 1 36 CKT&H<1> CKADC<0> 2 35 CKT&H<1> CKADC<1> 3 34 CKINT<1> CKADC<1> 4 33 CKINT<1> CLKREF 5 32 VCNT<1> VSS 6 31 VDD 7 30 VSS CLKREF 8 29 VCNT<2> CKADC<2> 9 28 CKINT<2> CKADC<2> 10 27 CKINT<2> CKADC<3> 11 26 CKT&H<2> CKADC<3> 12 25 CKT&H<2> 13 14 15 16 17 18 19 20 21 22 23 24 SPIDIN SPICLK SPIEN SPIDOUT VCNT<3> VSS VDD CKINT<3> CKT&H<3> 12/04/2013 QFN-48 Slow Control (SPI) 13

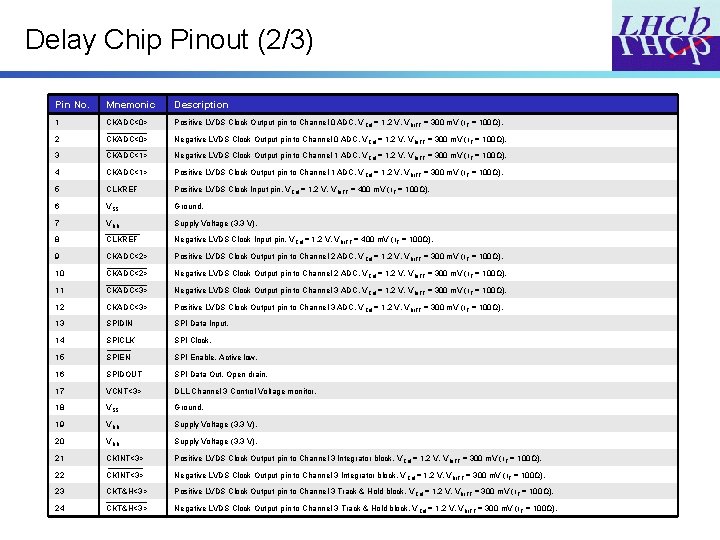

Delay Chip Pinout (2/3) Pin No. Mnemonic Description 1 CKADC<0> Positive LVDS Clock Output pin to Channel 0 ADC. V CM = 1. 2 V. V DIFF = 300 m. V (r. T = 100Ω). 2 CKADC<0> Negative LVDS Clock Output pin to Channel 0 ADC. V CM = 1. 2 V. V DIFF = 300 m. V (r. T = 100Ω). 3 CKADC<1> Negative LVDS Clock Output pin to Channel 1 ADC. V CM = 1. 2 V. V DIFF = 300 m. V (r. T = 100Ω). 4 CKADC<1> Positive LVDS Clock Output pin to Channel 1 ADC. V CM = 1. 2 V. V DIFF = 300 m. V (r. T = 100Ω). 5 CLKREF Positive LVDS Clock Input pin. V CM = 1. 2 V. V DIFF = 400 m. V (r. T = 100Ω). 6 VSS Ground. 7 VDD Supply Voltage (3. 3 V). 8 CLKREF Negative LVDS Clock Input pin. V CM = 1. 2 V. V DIFF = 400 m. V (r. T = 100Ω). 9 CKADC<2> Positive LVDS Clock Output pin to Channel 2 ADC. V CM = 1. 2 V. V DIFF = 300 m. V (r. T = 100Ω). 10 CKADC<2> Negative LVDS Clock Output pin to Channel 2 ADC. V CM = 1. 2 V. V DIFF = 300 m. V (r. T = 100Ω). 11 CKADC<3> Negative LVDS Clock Output pin to Channel 3 ADC. V CM = 1. 2 V. V DIFF = 300 m. V (r. T = 100Ω). 12 CKADC<3> Positive LVDS Clock Output pin to Channel 3 ADC. V CM = 1. 2 V. V DIFF = 300 m. V (r. T = 100Ω). 13 SPIDIN SPI Data Input. 14 SPICLK SPI Clock. 15 SPIEN SPI Enable. Active low. 16 SPIDOUT SPI Data Out. Open drain. 17 VCNT<3> DLL Channel 3 Control Voltage monitor. 18 VSS Ground. 19 VDD Supply Voltage (3. 3 V). 20 VDD Supply Voltage (3. 3 V). 21 CKINT<3> Positive LVDS Clock Output pin to Channel 3 Integrator block. V CM = 1. 2 V. V DIFF = 300 m. V (r. T = 100Ω). 22 CKINT<3> Negative LVDS Clock Output pin to Channel 3 Integrator block. V CM = 1. 2 V. V DIFF = 300 m. V (r. T = 100Ω). 23 CKT&H<3> Positive LVDS Clock Output pin to Channel 3 Track & Hold block. V CM = 1. 2 V. V DIFF = 300 m. V (r. T = 100Ω). 15/02/2013 CKT&H<3> 24 Negative LVDS Clock Output pin to Channel 3 Track & Hold block. V CM = 1. 2 V. V DIFF = 300 m. V (r. T = 100Ω). 14

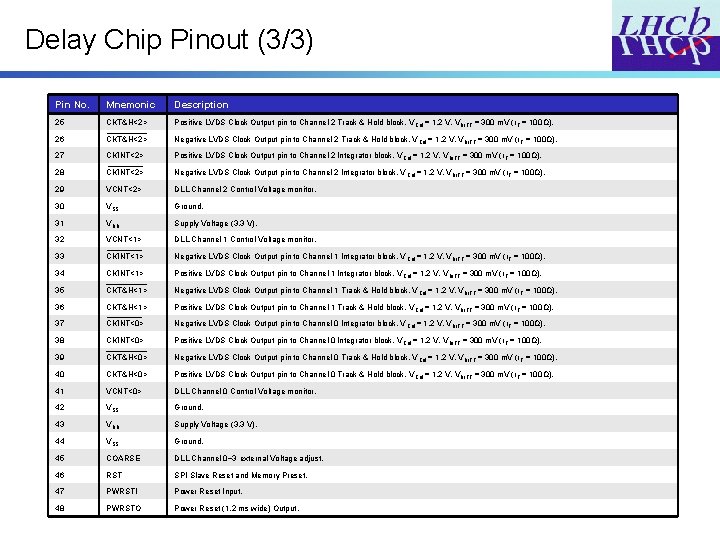

Delay Chip Pinout (3/3) Pin No. Mnemonic Description 25 CKT&H<2> Positive LVDS Clock Output pin to Channel 2 Track & Hold block. V CM = 1. 2 V. V DIFF = 300 m. V (r. T = 100Ω). 26 CKT&H<2> Negative LVDS Clock Output pin to Channel 2 Track & Hold block. V CM = 1. 2 V. V DIFF = 300 m. V (r. T = 100Ω). 27 CKINT<2> Positive LVDS Clock Output pin to Channel 2 Integrator block. V CM = 1. 2 V. V DIFF = 300 m. V (r. T = 100Ω). 28 CKINT<2> Negative LVDS Clock Output pin to Channel 2 Integrator block. V CM = 1. 2 V. V DIFF = 300 m. V (r. T = 100Ω). 29 VCNT<2> DLL Channel 2 Control Voltage monitor. 30 VSS Ground. 31 VDD Supply Voltage (3. 3 V). 32 VCNT<1> DLL Channel 1 Control Voltage monitor. 33 CKINT<1> Negative LVDS Clock Output pin to Channel 1 Integrator block. V CM = 1. 2 V. V DIFF = 300 m. V (r. T = 100Ω). 34 CKINT<1> Positive LVDS Clock Output pin to Channel 1 Integrator block. V CM = 1. 2 V. V DIFF = 300 m. V (r. T = 100Ω). 35 CKT&H<1> Negative LVDS Clock Output pin to Channel 1 Track & Hold block. V CM = 1. 2 V. V DIFF = 300 m. V (r. T = 100Ω). 36 CKT&H<1> Positive LVDS Clock Output pin to Channel 1 Track & Hold block. V CM = 1. 2 V. V DIFF = 300 m. V (r. T = 100Ω). 37 CKINT<0> Negative LVDS Clock Output pin to Channel 0 Integrator block. V CM = 1. 2 V. V DIFF = 300 m. V (r. T = 100Ω). 38 CKINT<0> Positive LVDS Clock Output pin to Channel 0 Integrator block. V CM = 1. 2 V. V DIFF = 300 m. V (r. T = 100Ω). 39 CKT&H<0> Negative LVDS Clock Output pin to Channel 0 Track & Hold block. V CM = 1. 2 V. V DIFF = 300 m. V (r. T = 100Ω). 40 CKT&H<0> Positive LVDS Clock Output pin to Channel 0 Track & Hold block. V CM = 1. 2 V. V DIFF = 300 m. V (r. T = 100Ω). 41 VCNT<0> DLL Channel 0 Control Voltage monitor. 42 VSS Ground. 43 VDD Supply Voltage (3. 3 V). 44 VSS Ground. 45 COARSE DLL Channel 0~3 external Voltage adjust. 46 RST SPI Slave Reset and Memory Preset. 47 PWRSTI Power Reset Input. 15/02/2013 PWRSTO 48 Power Reset (1. 2 ms wide) Output. 15

Delay Chip Test Board Schematics • USB RS 232: • Coarse (DAC): • RS 232 SPI (PIC): 12/04/2013 16

- Slides: 16