Kahn Process Networks Static Multirate Dataflow Dynamic Multirate

- Slides: 42

Возможности по моделированию • Kahn Process Networks • Static Multi-rate Dataflow • Dynamic Multi-rate Dataflow • Communicating Sequential Processes • Discrete Event as used for – RTL hardware modeling – Network modeling (e. g. stochastic or “waiting room” models) – Transaction-based So. C platform modeling

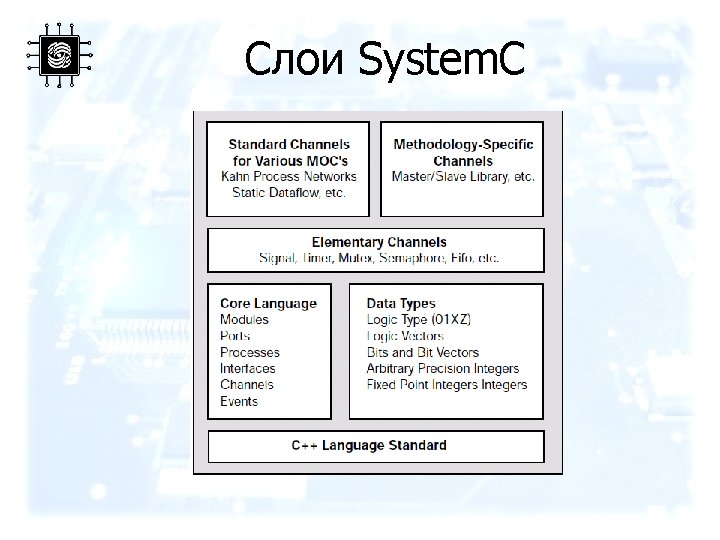

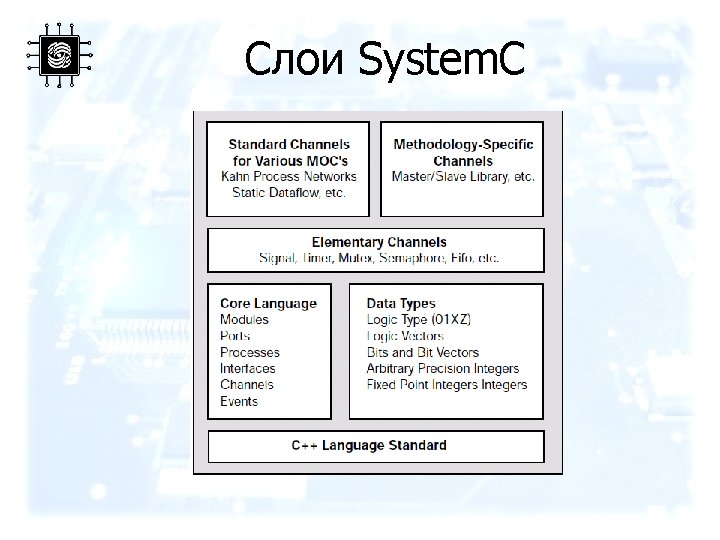

Слои System. C

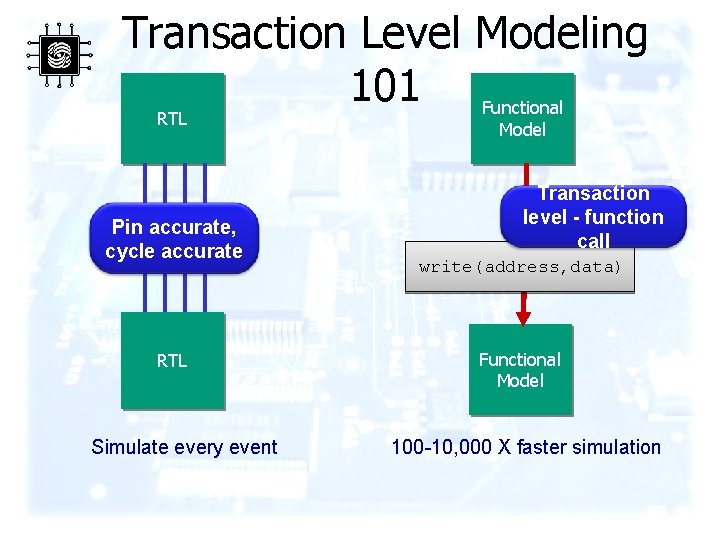

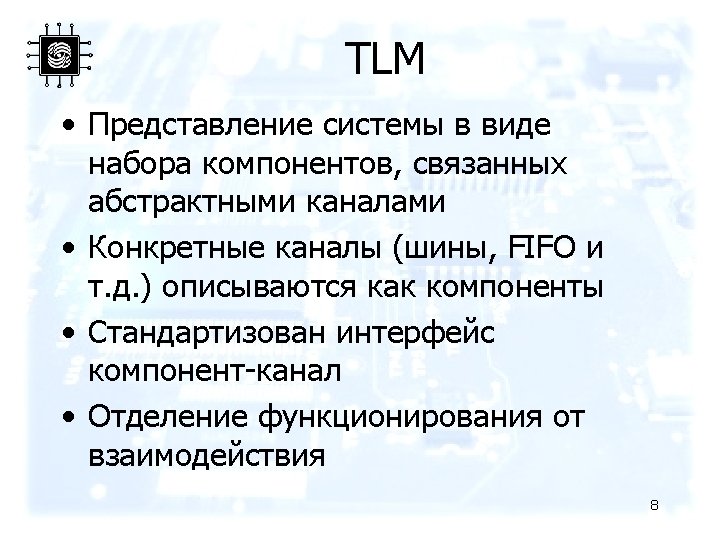

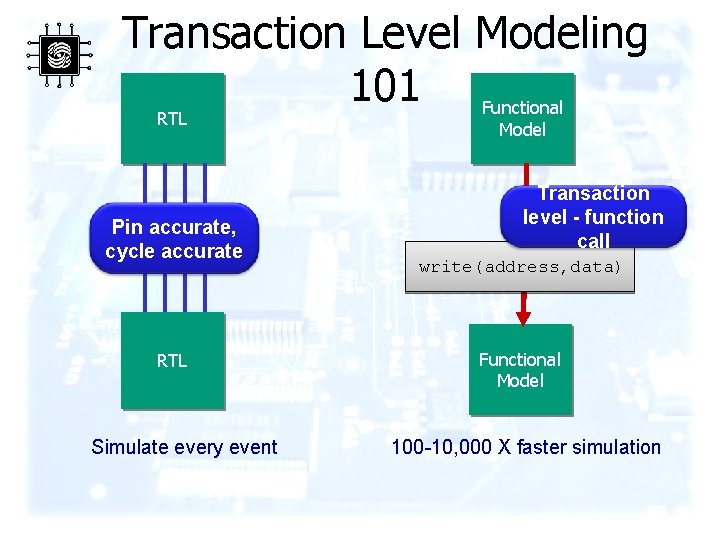

Transaction Level Modeling 101 Functional RTL Pin accurate, cycle accurate RTL Simulate every event 10 Model Transaction level - function call write(address, data) Functional Model 100 -10, 000 X faster simulation

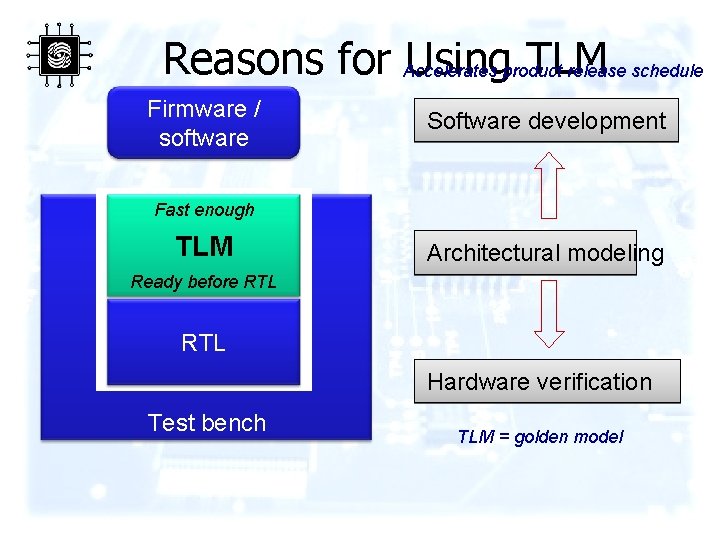

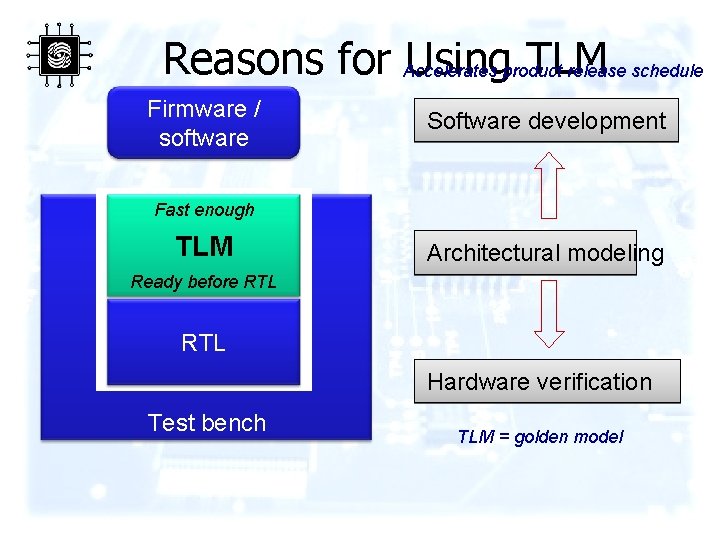

Reasons for Accelerates Usingproduct TLM release schedule Firmware / software Software development Fast enough TLM Architectural modeling Ready before RTL Hardware verification Test bench 11 TLM = golden model

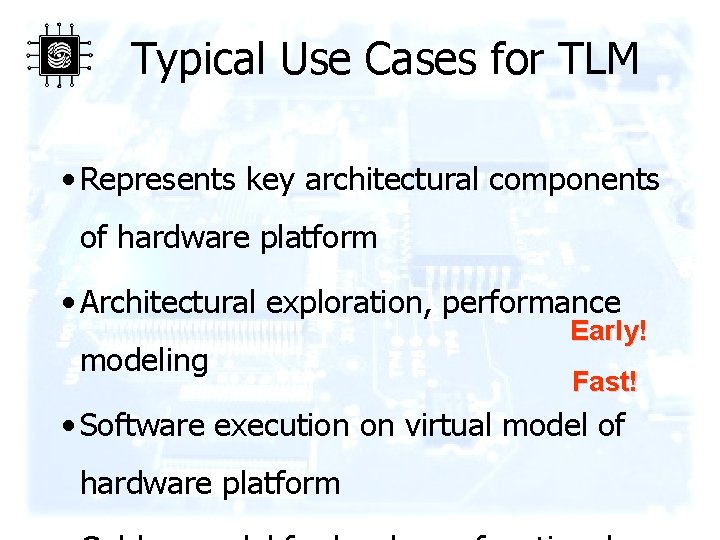

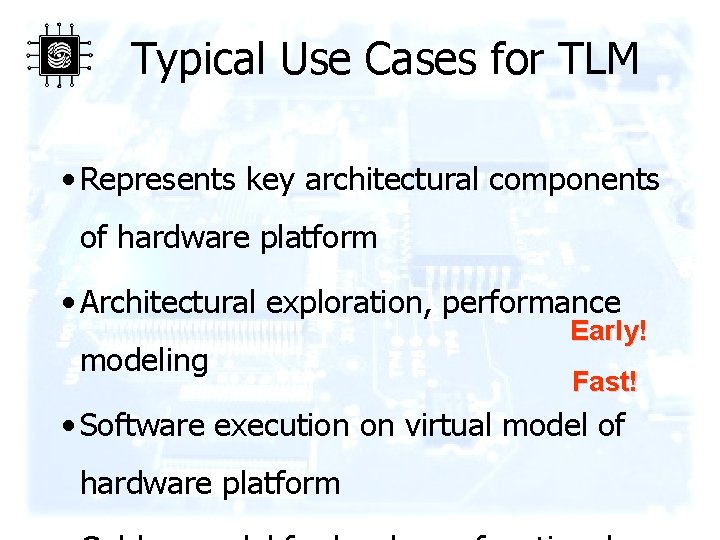

Typical Use Cases for TLM • Represents key architectural components of hardware platform • Architectural exploration, performance modeling Early! Fast! • Software execution on virtual model of hardware platform 12

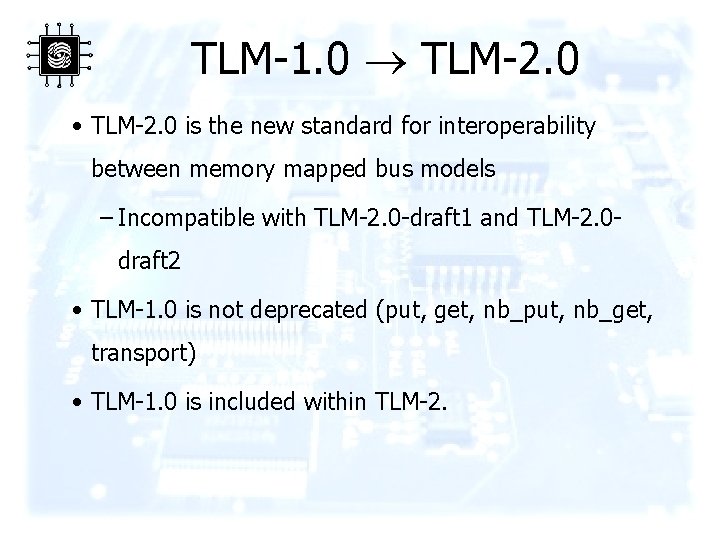

TLM-1. 0 TLM-2. 0 • TLM-2. 0 is the new standard for interoperability between memory mapped bus models – Incompatible with TLM-2. 0 -draft 1 and TLM-2. 0 draft 2 • TLM-1. 0 is not deprecated (put, get, nb_put, nb_get, transport) • TLM-1. 0 is included within TLM-2. 13

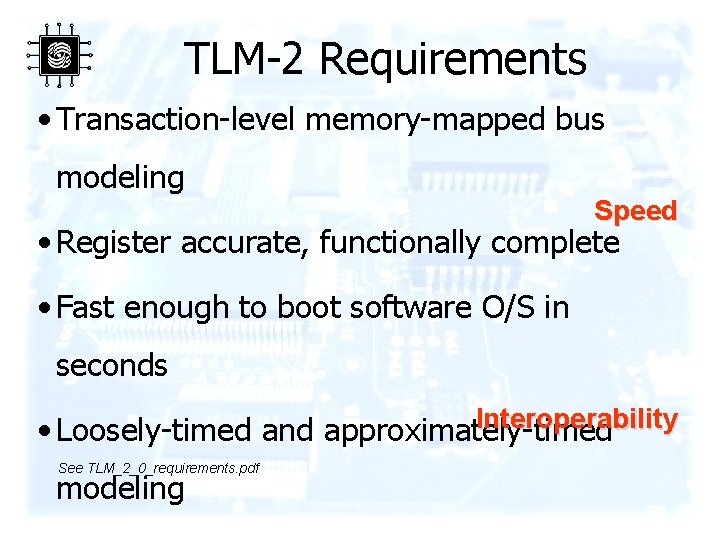

TLM-2 Requirements • Transaction-level memory-mapped bus modeling Speed • Register accurate, functionally complete • Fast enough to boot software O/S in seconds Interoperability • Loosely-timed and approximately-timed See TLM_2_0_requirements. pdf modeling 14

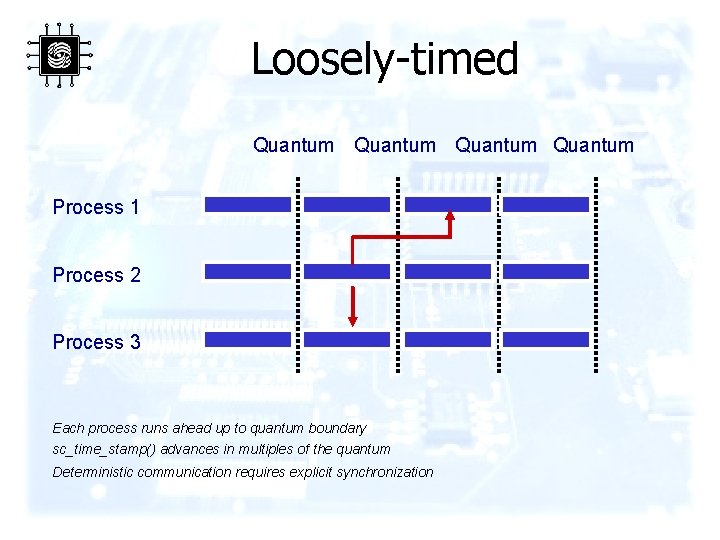

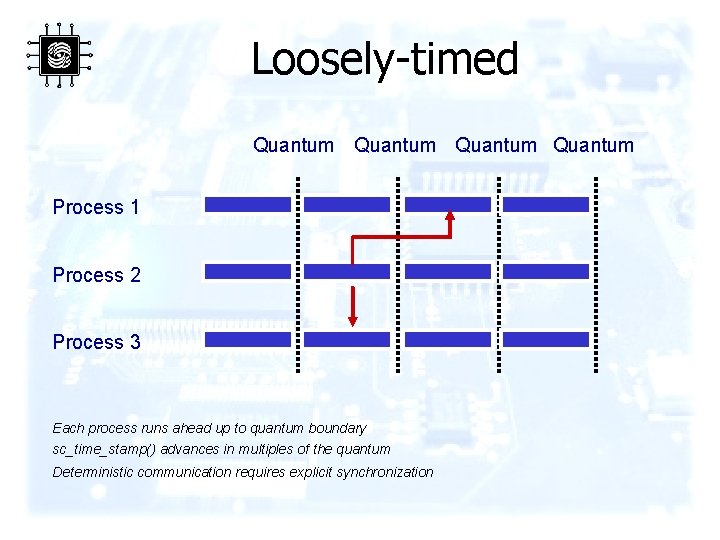

Loosely-timed Quantum Process 1 Process 2 Process 3 Each process runs ahead up to quantum boundary sc_time_stamp() advances in multiples of the quantum Deterministic communication requires explicit synchronization 15

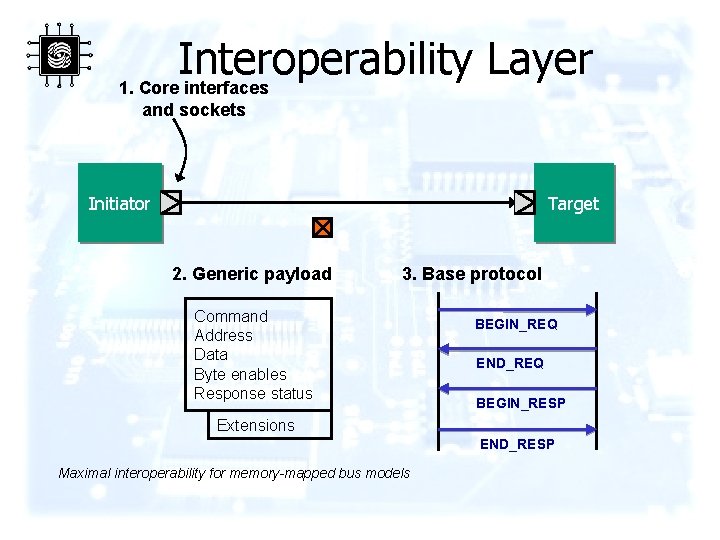

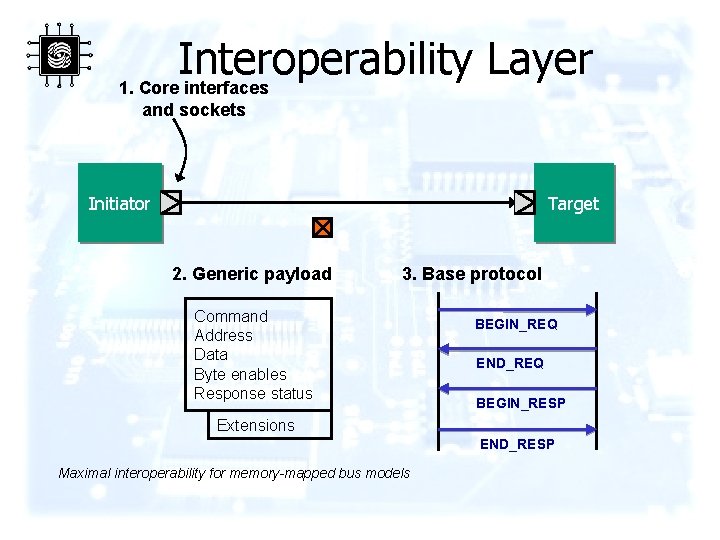

Interoperability Layer 1. Core interfaces and sockets Initiator Target 2. Generic payload 3. Base protocol Command Address Data Byte enables Response status BEGIN_REQ END_REQ BEGIN_RESP Extensions END_RESP Maximal interoperability for memory-mapped bus models 16

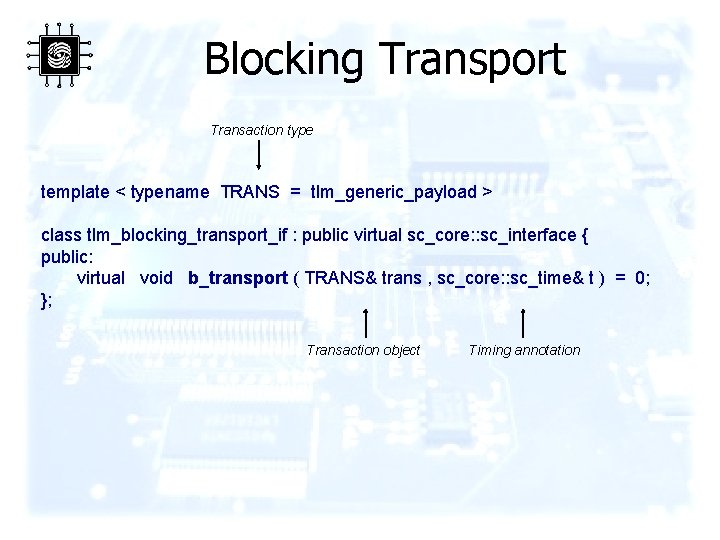

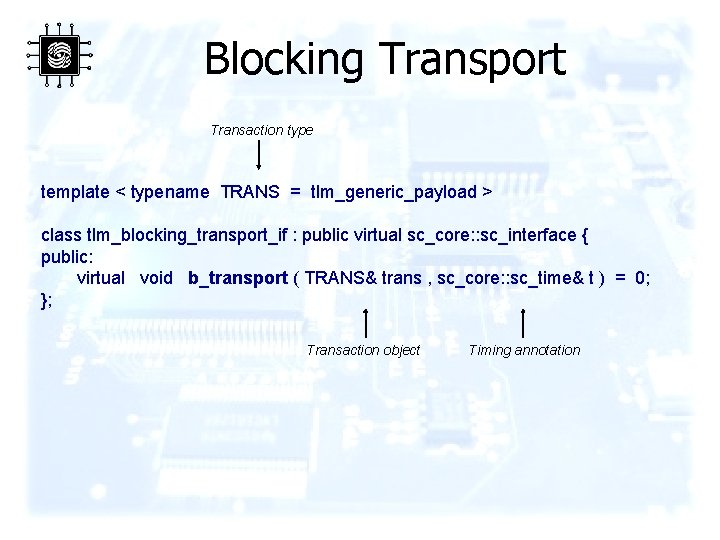

Blocking Transport Transaction type template < typename TRANS = tlm_generic_payload > class tlm_blocking_transport_if : public virtual sc_core: : sc_interface { public: virtual void b_transport ( TRANS& trans , sc_core: : sc_time& t ) = 0; }; Transaction object 17 Timing annotation

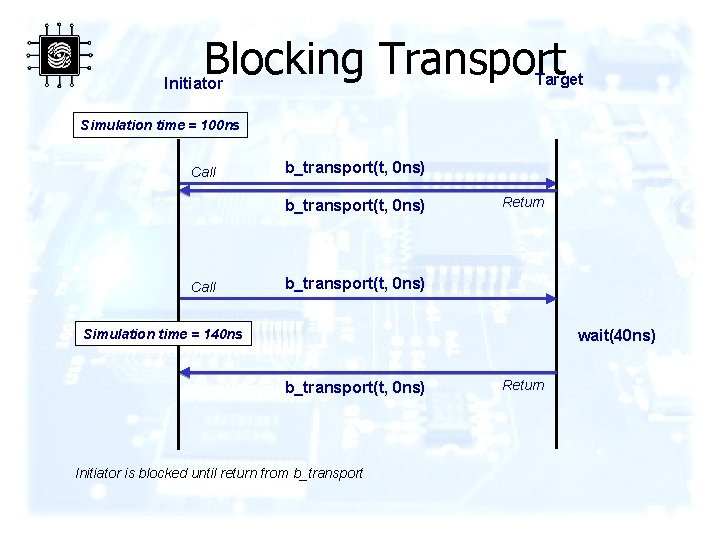

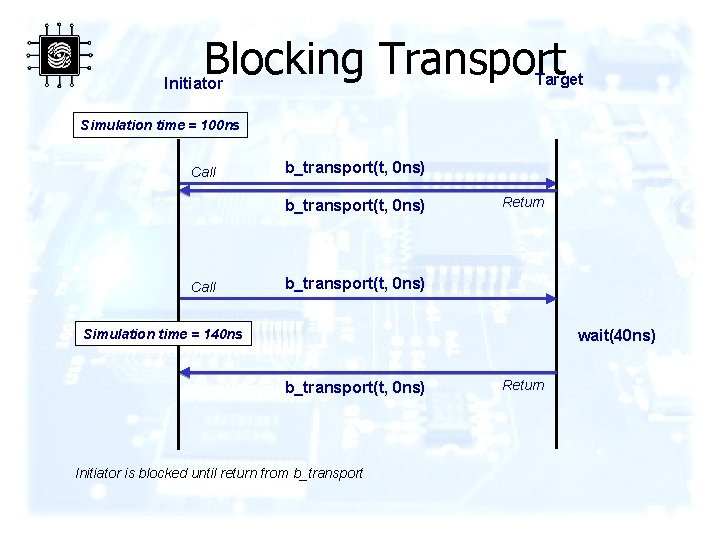

Blocking Transport Target Initiator Simulation time = 100 ns Call b_transport(t, 0 ns) Call Return b_transport(t, 0 ns) Simulation time = 140 ns wait(40 ns) b_transport(t, 0 ns) Initiator is blocked until return from b_transport 18 Return

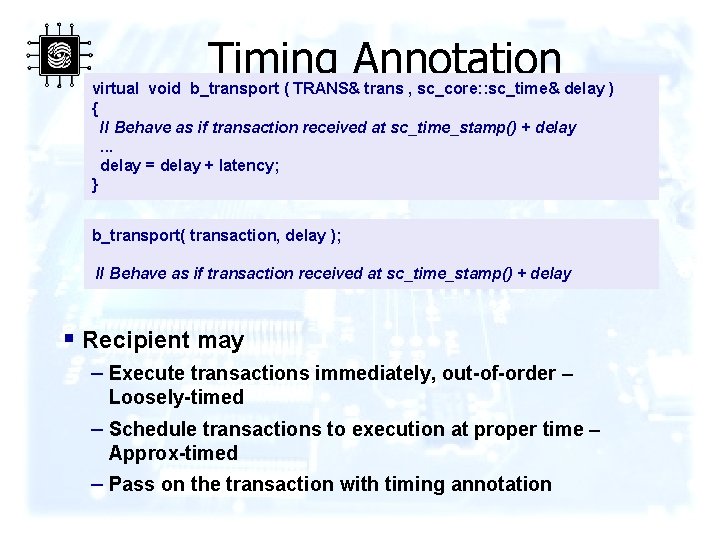

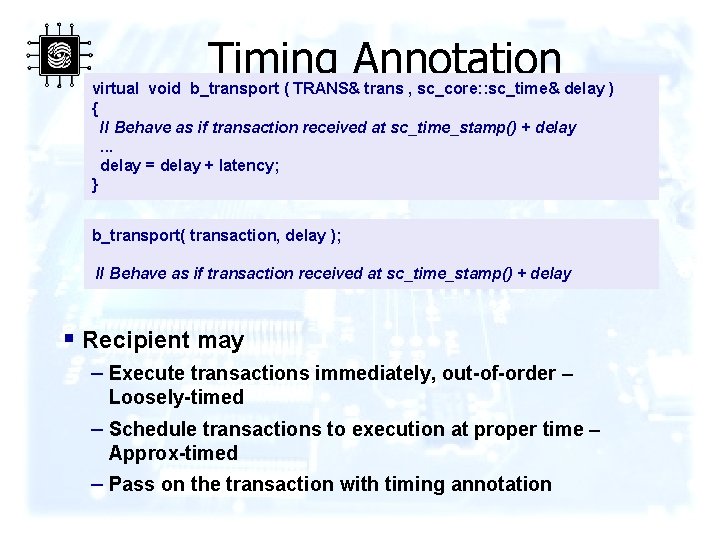

Timing Annotation virtual void b_transport ( TRANS& trans , sc_core: : sc_time& delay ) { // Behave as if transaction received at sc_time_stamp() + delay. . . delay = delay + latency; } b_transport( transaction, delay ); // Behave as if transaction received at sc_time_stamp() + delay § Recipient may – Execute transactions immediately, out-of-order – Loosely-timed – Schedule transactions to execution at proper time – Approx-timed – Pass on the transaction with timing annotation 19

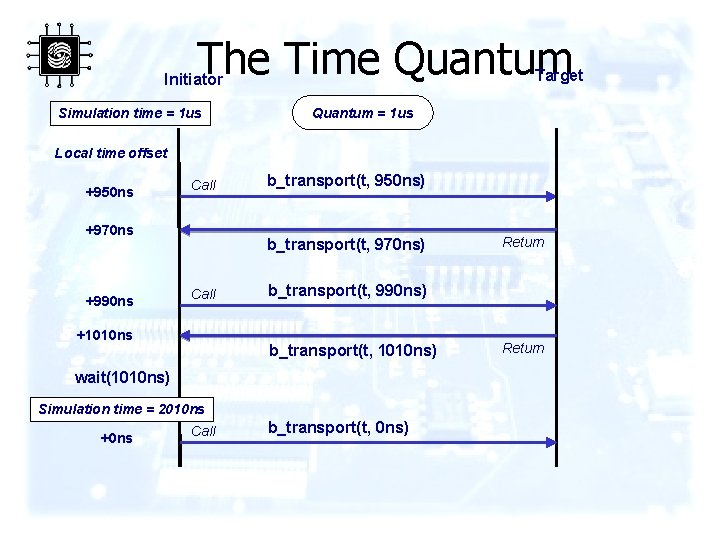

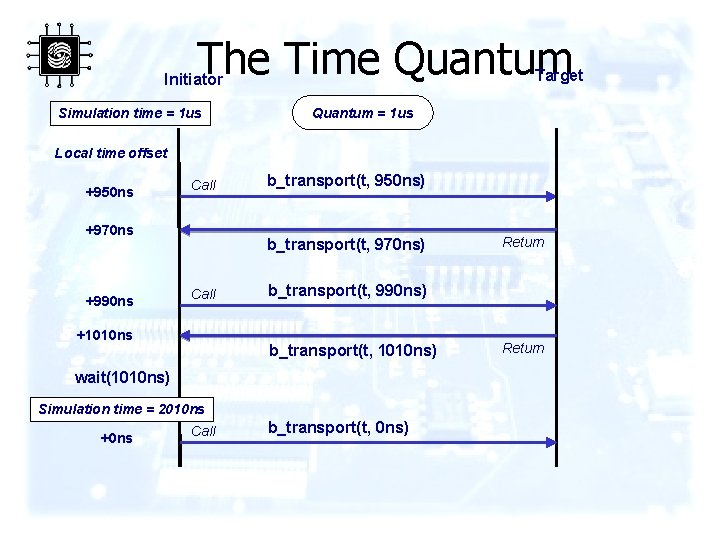

The Time Quantum Target Initiator Simulation time = 1 us Quantum = 1 us Local time offset +950 ns Call +970 ns +990 ns b_transport(t, 950 ns) b_transport(t, 970 ns) Call +1010 ns b_transport(t, 990 ns) b_transport(t, 1010 ns) wait(1010 ns) Simulation time = 2010 ns +0 ns 20 Call Return b_transport(t, 0 ns) Return

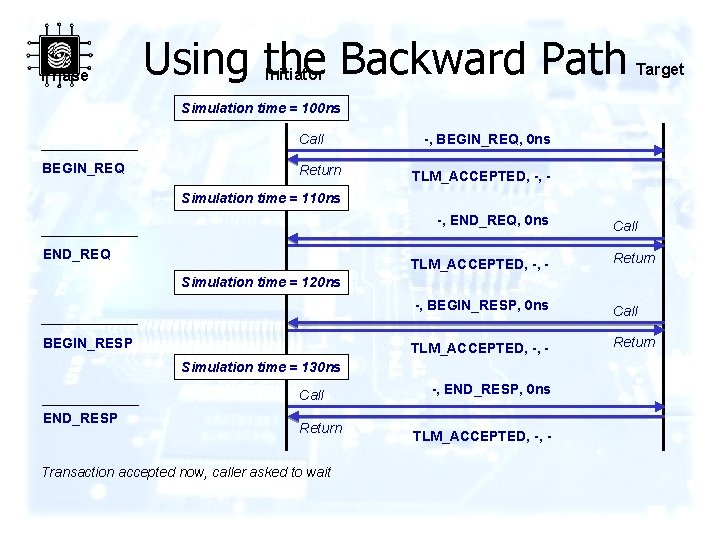

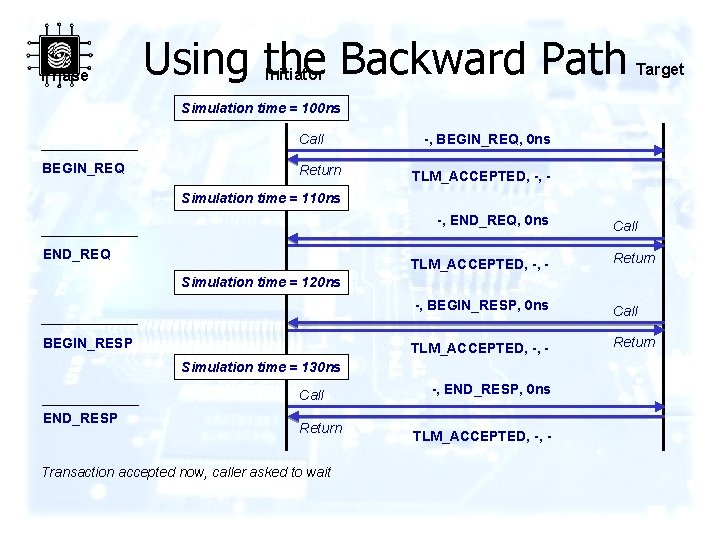

Phase Using the Backward Path Initiator Target Simulation time = 100 ns Call BEGIN_REQ Return -, BEGIN_REQ, 0 ns TLM_ACCEPTED, -, - Simulation time = 110 ns -, END_REQ, 0 ns END_REQ Call TLM_ACCEPTED, -, - Return -, BEGIN_RESP, 0 ns Call TLM_ACCEPTED, -, - Return Simulation time = 120 ns BEGIN_RESP Simulation time = 130 ns Call END_RESP Return Transaction accepted now, caller asked to wait 21 -, END_RESP, 0 ns TLM_ACCEPTED, -, -

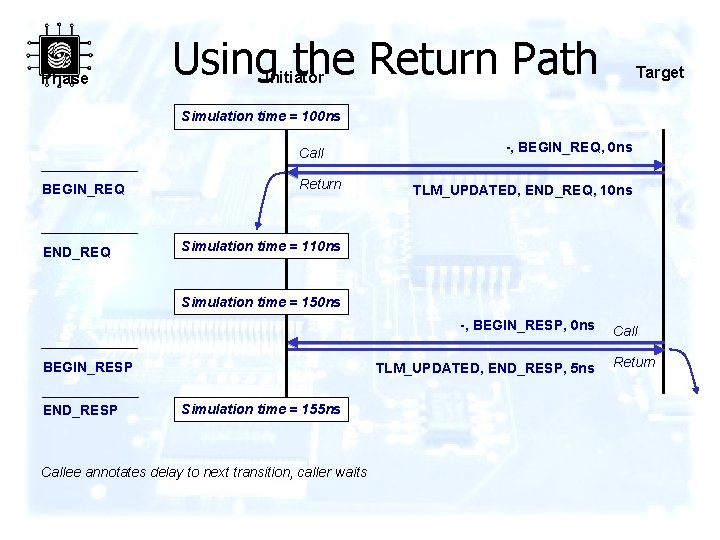

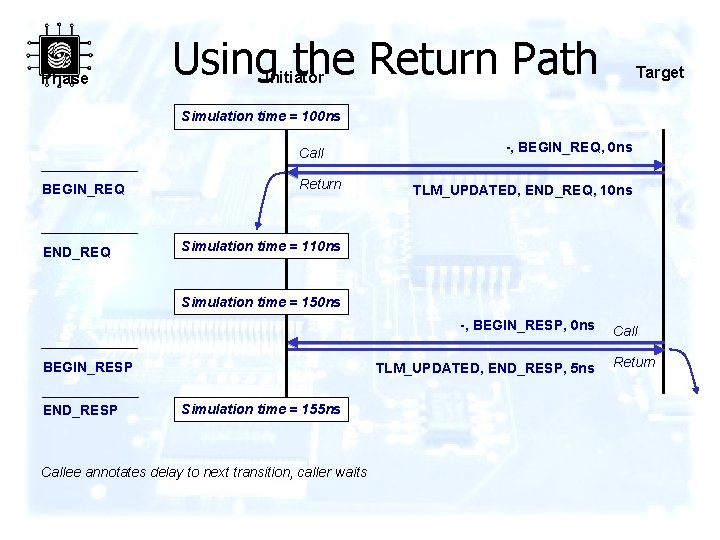

Phase Using the Return Path Target Initiator Simulation time = 100 ns Call BEGIN_REQ END_REQ Return -, BEGIN_REQ, 0 ns TLM_UPDATED, END_REQ, 10 ns Simulation time = 150 ns -, BEGIN_RESP, 0 ns BEGIN_RESP END_RESP TLM_UPDATED, END_RESP, 5 ns Simulation time = 155 ns Callee annotates delay to next transition, caller waits 22 Call Return

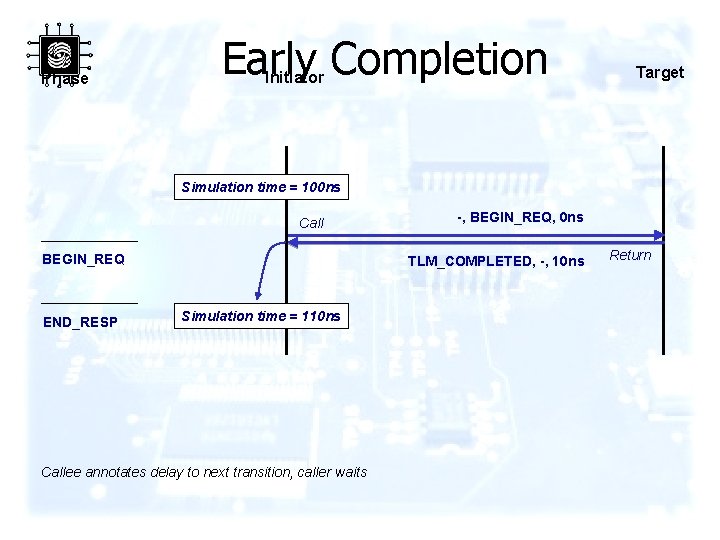

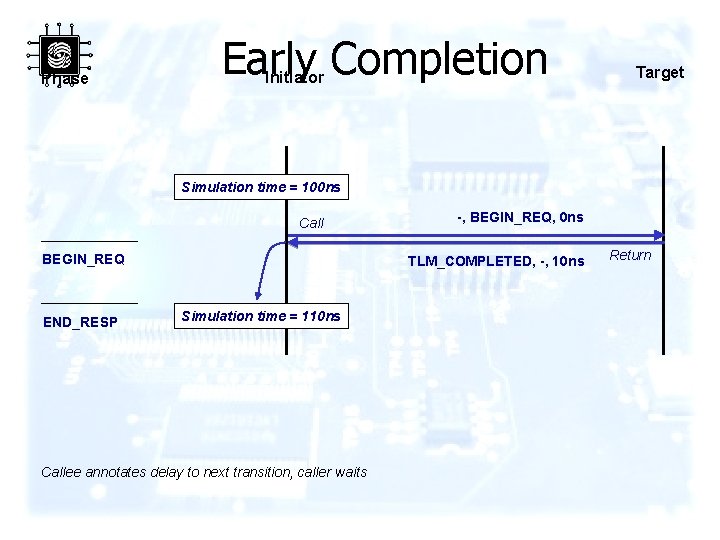

Phase Early Completion Initiator Target Simulation time = 100 ns Call BEGIN_REQ END_RESP TLM_COMPLETED, -, 10 ns Simulation time = 110 ns Callee annotates delay to next transition, caller waits 23 -, BEGIN_REQ, 0 ns Return

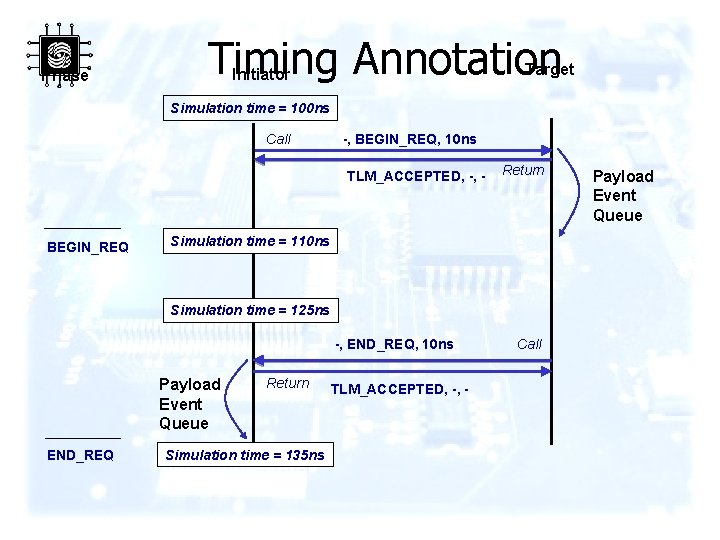

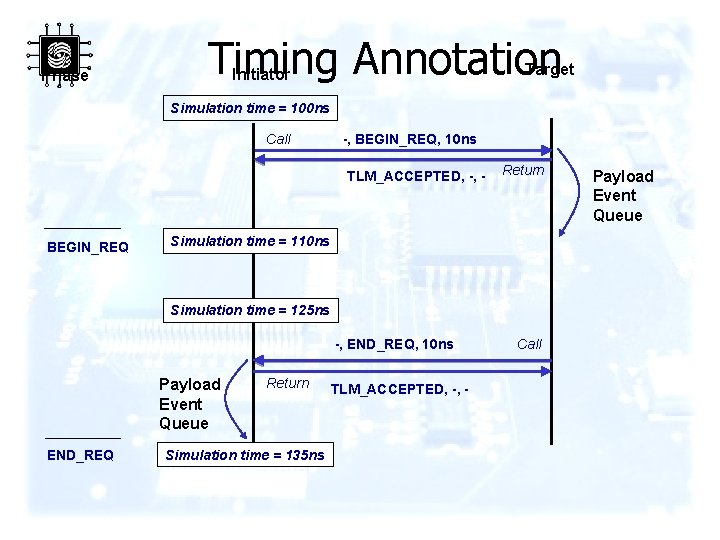

Phase Timing Annotation Target Initiator Simulation time = 100 ns Call -, BEGIN_REQ, 10 ns TLM_ACCEPTED, -, - BEGIN_REQ Return Simulation time = 110 ns Simulation time = 125 ns -, END_REQ, 10 ns Payload Event Queue END_REQ 24 Return Simulation time = 135 ns TLM_ACCEPTED, -, - Call Payload Event Queue

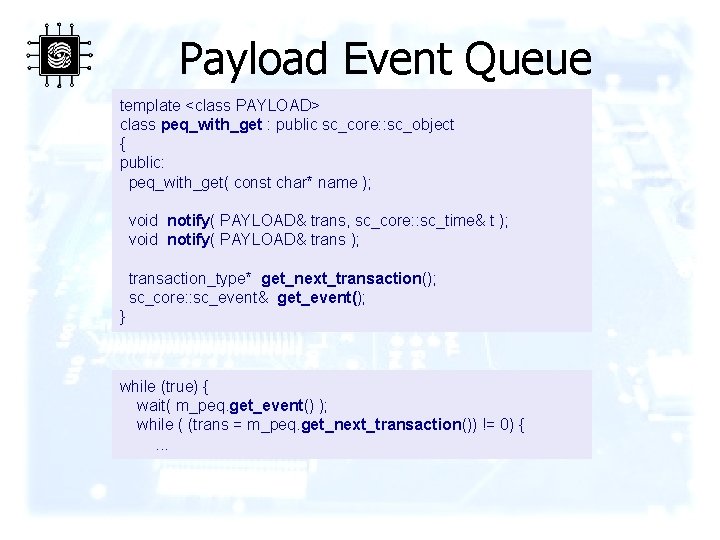

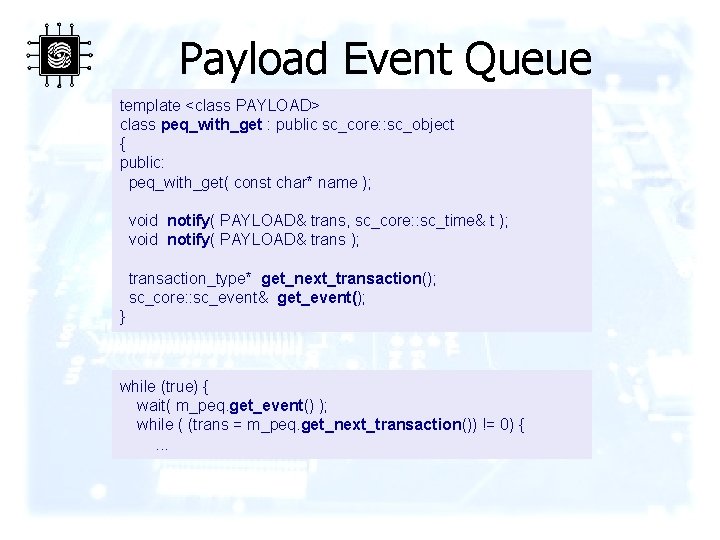

Payload Event Queue template <class PAYLOAD> class peq_with_get : public sc_core: : sc_object { public: peq_with_get( const char* name ); void notify( PAYLOAD& trans, sc_core: : sc_time& t ); void notify( PAYLOAD& trans ); transaction_type* get_next_transaction(); sc_core: : sc_event& get_event(); } while (true) { wait( m_peq. get_event() ); while ( (trans = m_peq. get_next_transaction()) != 0) {. . . 25

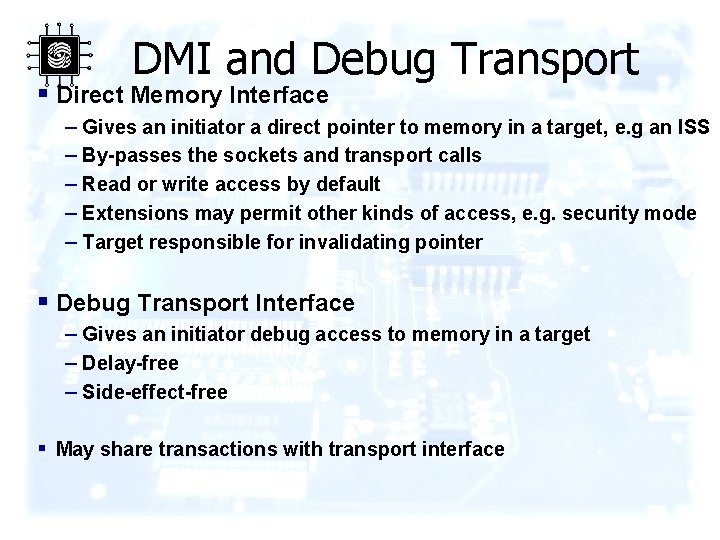

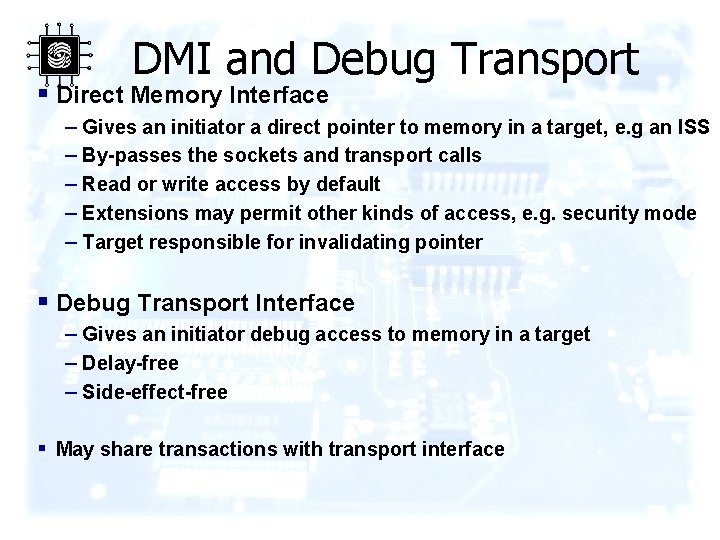

DMI and Debug Transport § Direct Memory Interface – Gives an initiator a direct pointer to memory in a target, e. g an ISS – By-passes the sockets and transport calls – Read or write access by default – Extensions may permit other kinds of access, e. g. security mode – Target responsible for invalidating pointer § Debug Transport Interface – Gives an initiator debug access to memory in a target – Delay-free – Side-effect-free § May share transactions with transport interface 26

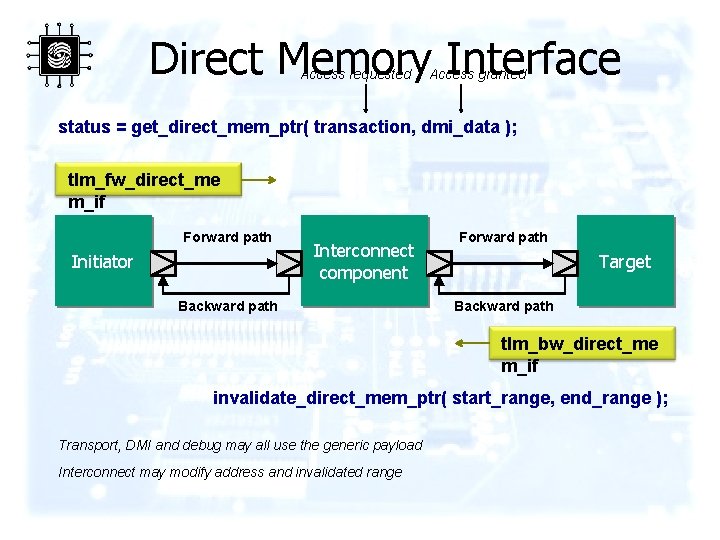

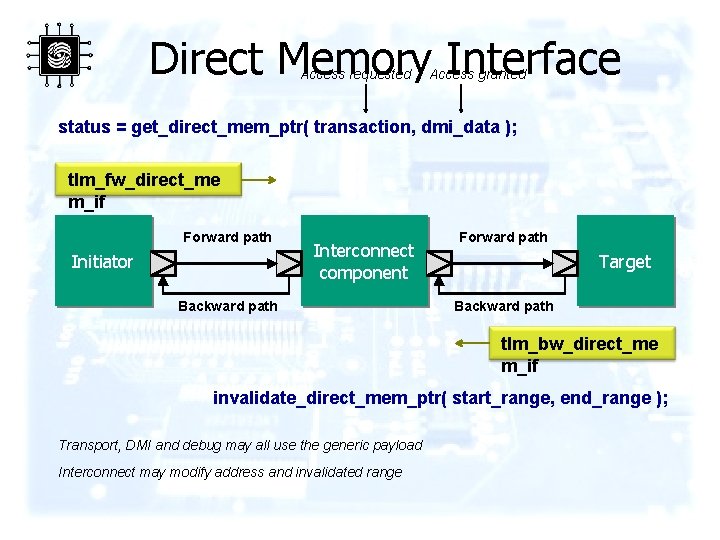

Direct Memory Interface Access requested Access granted status = get_direct_mem_ptr( transaction, dmi_data ); tlm_fw_direct_me m_if Forward path Initiator Interconnect component Backward path Forward path Target Backward path tlm_bw_direct_me m_if invalidate_direct_mem_ptr( start_range, end_range ); Transport, DMI and debug may all use the generic payload Interconnect may modify address and invalidated range 27

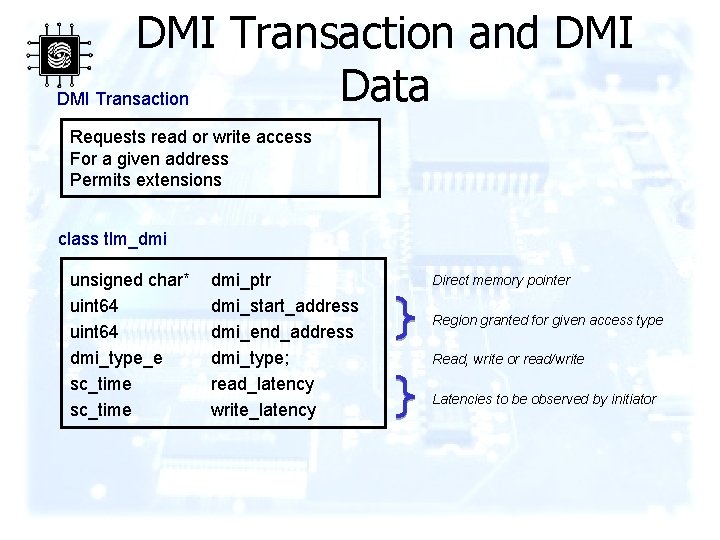

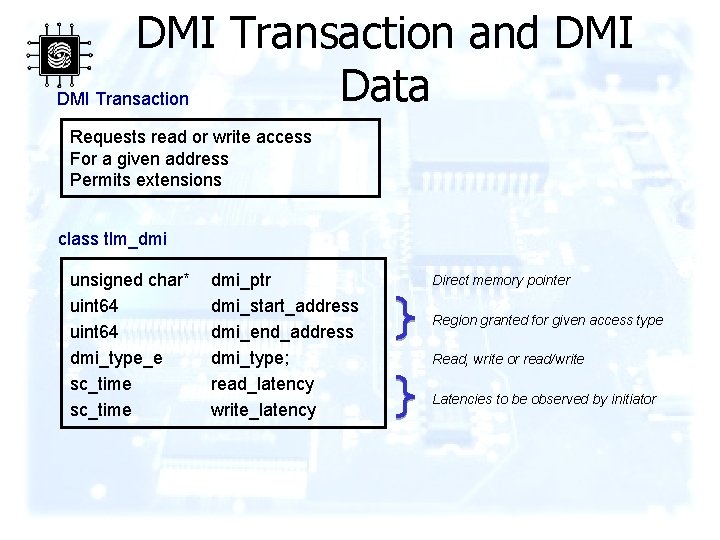

DMI Transaction and DMI Data DMI Transaction Requests read or write access For a given address Permits extensions class tlm_dmi unsigned char* uint 64 dmi_type_e sc_time 28 dmi_ptr dmi_start_address dmi_end_address dmi_type; read_latency write_latency Direct memory pointer Region granted for given access type Read, write or read/write Latencies to be observed by initiator

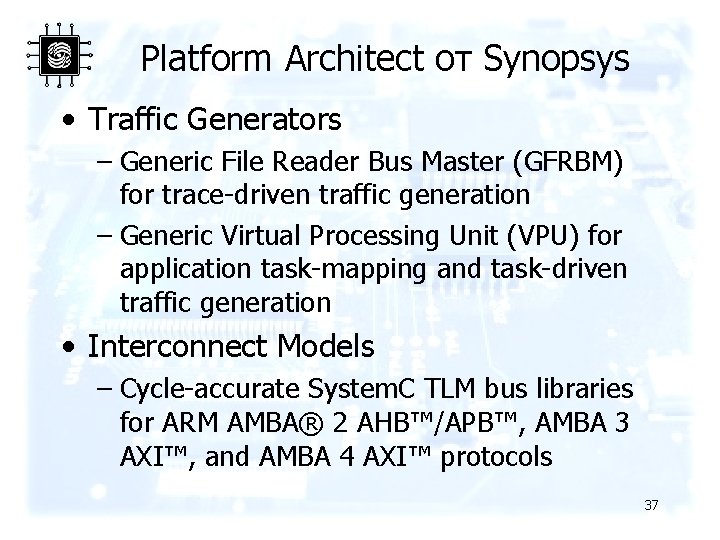

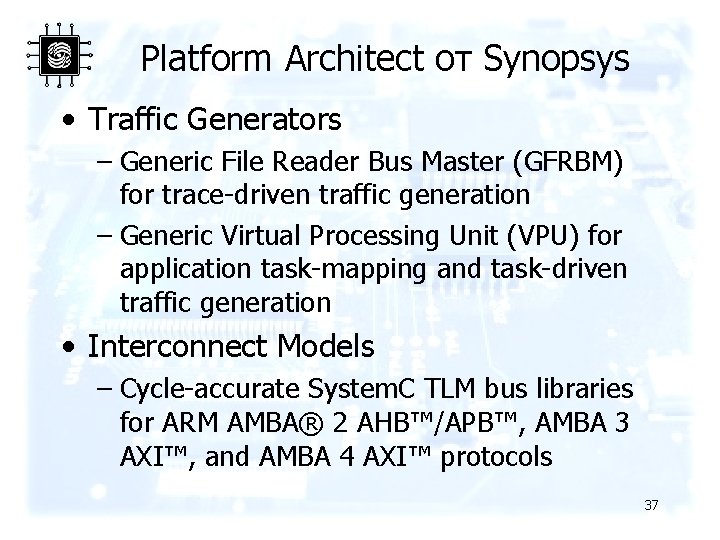

Platform Architect от Synopsys • Traffic Generators – Generic File Reader Bus Master (GFRBM) for trace-driven traffic generation – Generic Virtual Processing Unit (VPU) for application task-mapping and task-driven traffic generation • Interconnect Models – Cycle-accurate System. C TLM bus libraries for ARM AMBA® 2 AHB™/APB™, AMBA 3 AXI™, and AMBA 4 AXI™ protocols 37

Продолжение – Generic approximately-timed System. C TLM bus libraries for industry-standard IEEE 1666 -2011 System. C TLM-2. 0 protocols, plus support for the approximately-timed models available from Arteris® for the Arteris Flex. No. C™ Network on Chip (No. C) interconnect, which provide on-chip connectivity for AMBA® AXI™, AHB -Lite, APB™, and PIF protocols. 38

Продолжение • Memory Subsystem Models – Generic approximately-timed System. C TLM memory subsystem models for ARM AXI and IEEE-1666 2011 System. C TLM-2. 0 interfaces, including the Synopsys Design. Ware Enhanced Universal DDR Memory Controller (u. MCTL 2) – Cycle-accurate memory subsystem models are available for Platform Architect through HDL co-simulation with user-provided, third -party and Synopsys RTL memory controller IP 39

Продолжение • Processor Models – Cycle-accurate System. C TLM processor support packages (PSPs) are available for Tensilica and MIPS processor families, and through HDL co-simulation with userprovided RTL for ARM processor families. 40

Ссылки по System. C http: //www. asicworld. com/systemc/tutorial. html http: //accellera. org/downloads/standards/ ieee - бесплатно доступные стандарты IEEE в части System. C http: //www. ece. iastate. edu/~zambreno/cl asses/cpre 588/documents/Ros. Swa 05 A. pdf 41