Interfacing Processors and Peripherals Processor Interrupts Cache Memory

- Slides: 21

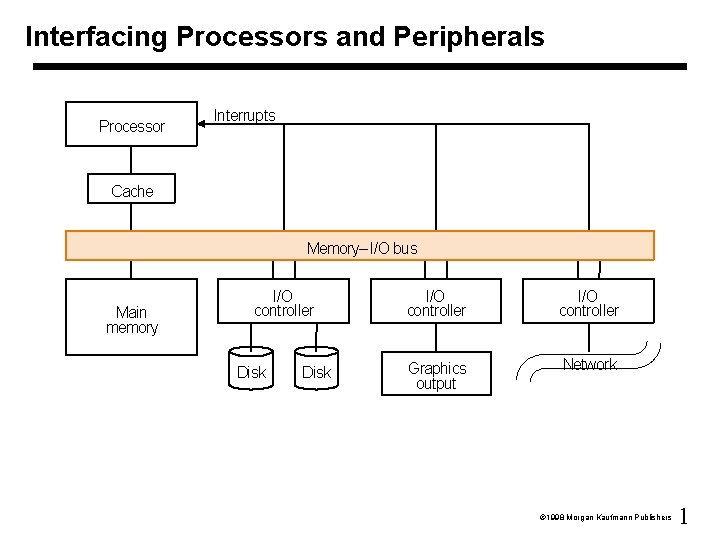

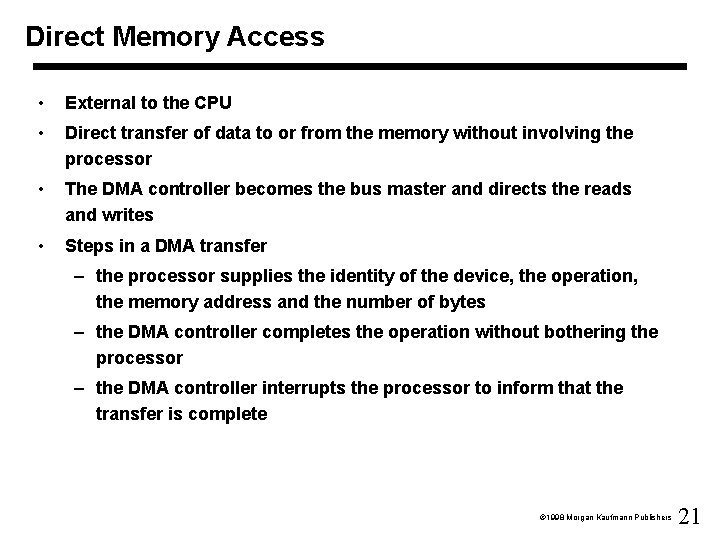

Interfacing Processors and Peripherals Processor Interrupts Cache Memory– I/O bus Main memory I/O controller Disk I/O controller Graphics output Network 1998 Morgan Kaufmann Publishers 1

I/O Devices 1998 Morgan Kaufmann Publishers 2

Input/Output • Very diverse devices – behaviour (i. e. , input vs. output) – partner (who is at the other end? ) – data rate • Important but neglected – difficulties in assessing and designing I/O systems have often relegated I/O to second class status 1998 Morgan Kaufmann Publishers 3

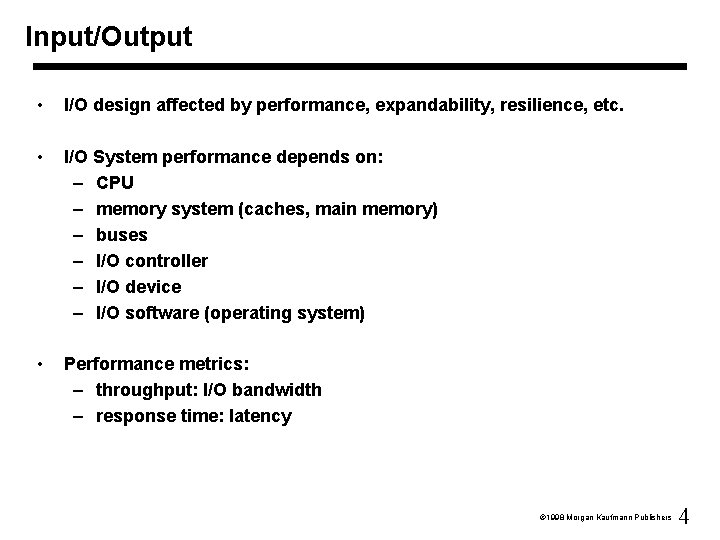

Input/Output • I/O design affected by performance, expandability, resilience, etc. • I/O System performance depends on: – CPU – memory system (caches, main memory) – buses – I/O controller – I/O device – I/O software (operating system) • Performance metrics: – throughput: I/O bandwidth – response time: latency 1998 Morgan Kaufmann Publishers 4

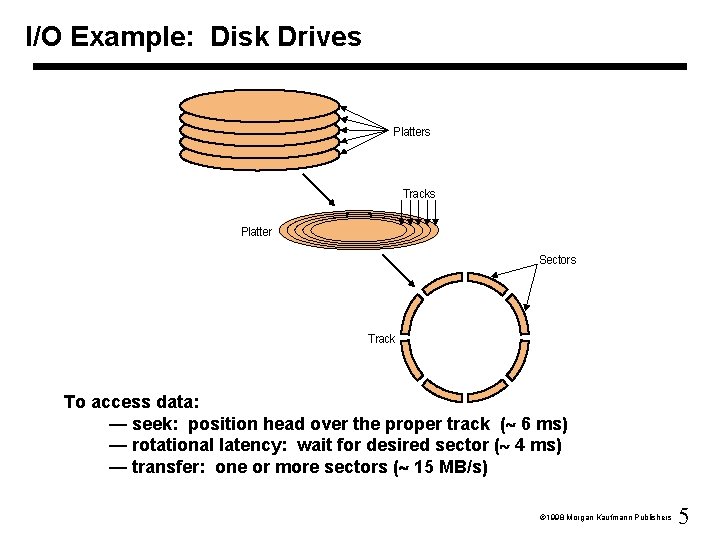

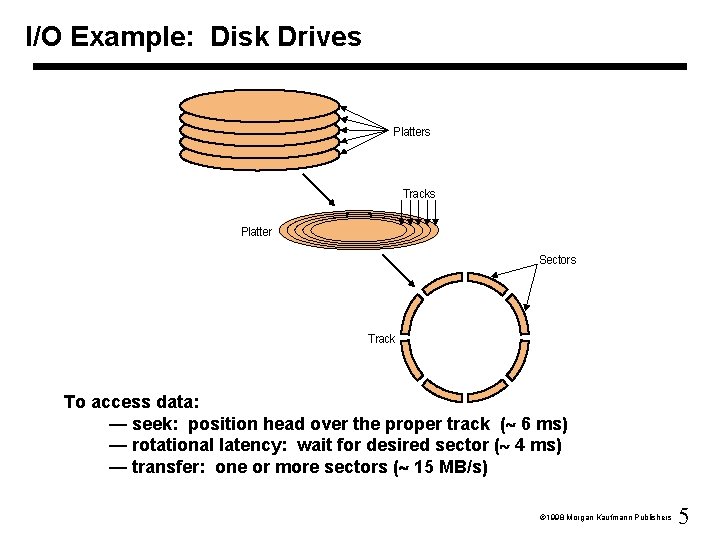

I/O Example: Disk Drives Platters Tracks Platter Sectors Track To access data: — seek: position head over the proper track ( 6 ms) — rotational latency: wait for desired sector ( 4 ms) — transfer: one or more sectors ( 15 MB/s) 1998 Morgan Kaufmann Publishers 5

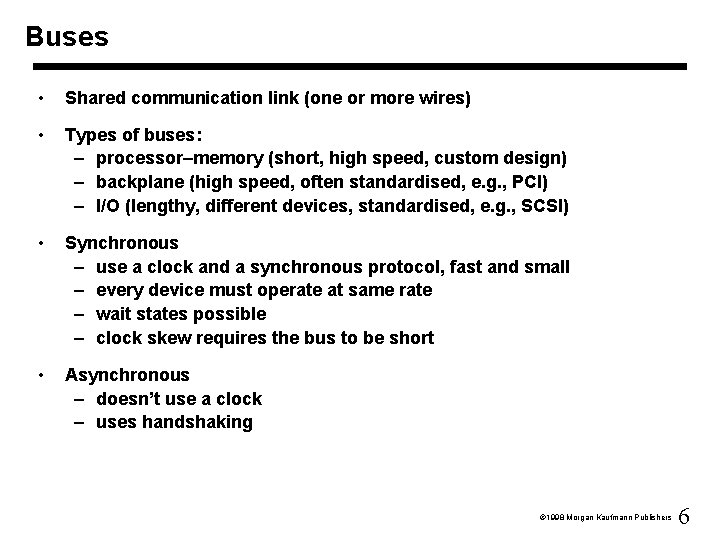

Buses • Shared communication link (one or more wires) • Types of buses: – processor–memory (short, high speed, custom design) – backplane (high speed, often standardised, e. g. , PCI) – I/O (lengthy, different devices, standardised, e. g. , SCSI) • Synchronous – use a clock and a synchronous protocol, fast and small – every device must operate at same rate – wait states possible – clock skew requires the bus to be short • Asynchronous – doesn’t use a clock – uses handshaking 1998 Morgan Kaufmann Publishers 6

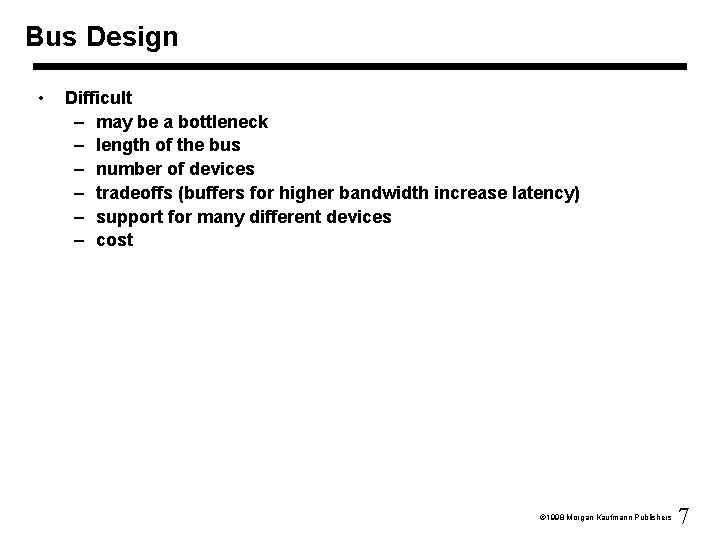

Bus Design • Difficult – may be a bottleneck – length of the bus – number of devices – tradeoffs (buffers for higher bandwidth increase latency) – support for many different devices – cost 1998 Morgan Kaufmann Publishers 7

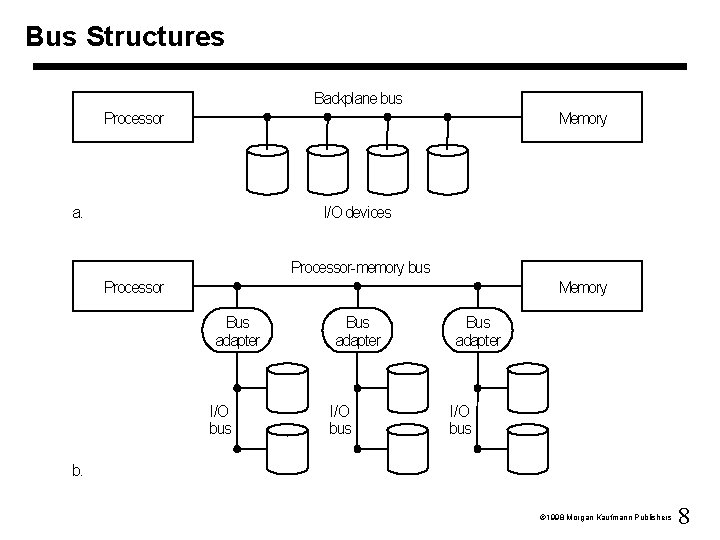

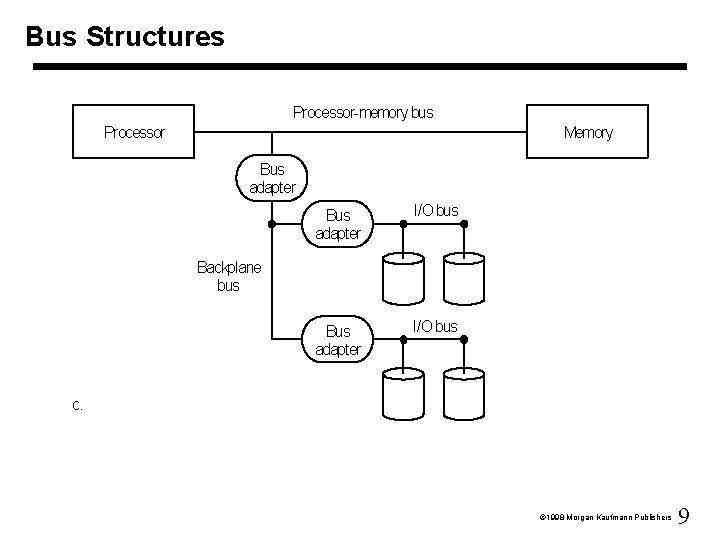

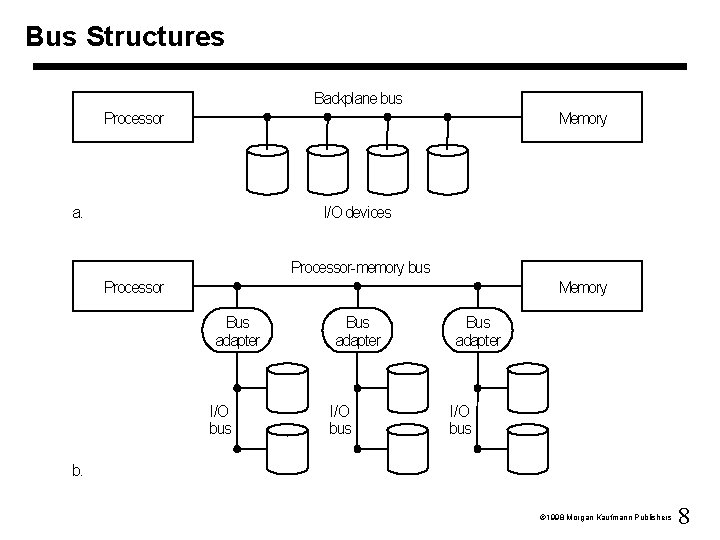

Bus Structures Backplane bus Processor Memory a. I/O devices Processor-memory bus Processor Memory Bus adapter I/O bus b. 1998 Morgan Kaufmann Publishers 8

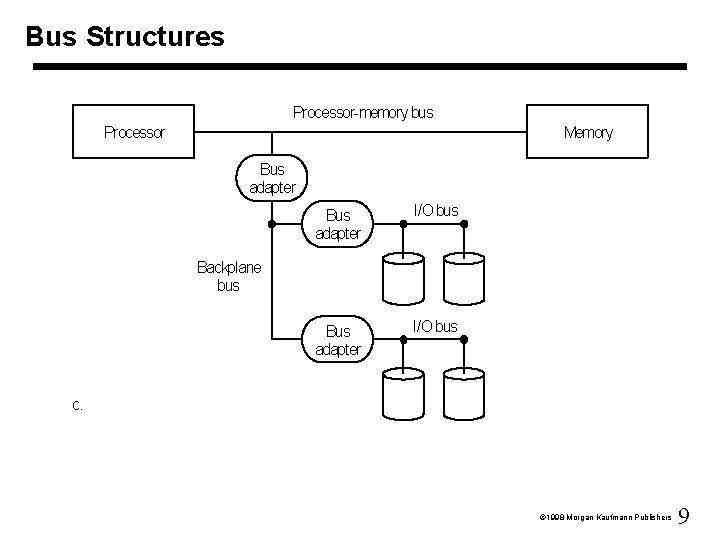

Bus Structures Processor-memory bus Processor Memory Bus adapter I/O bus Backplane bus c. 1998 Morgan Kaufmann Publishers 9

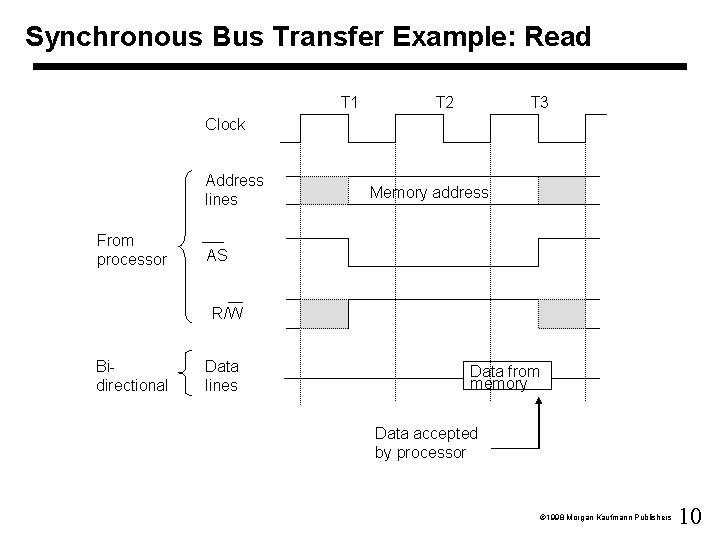

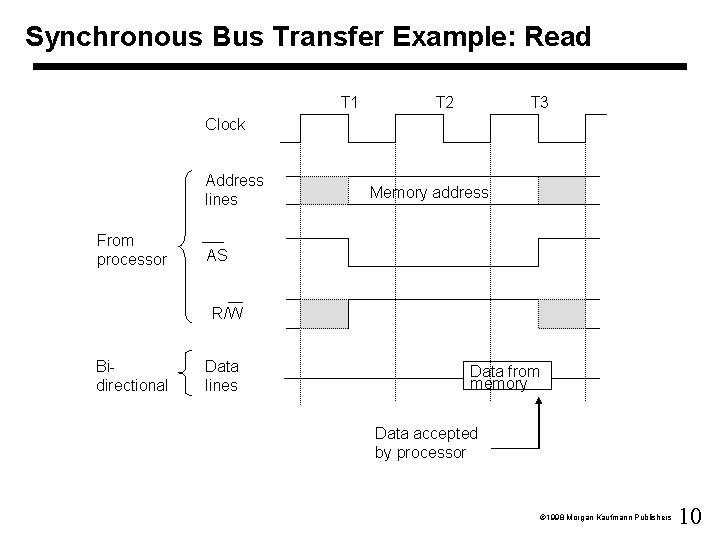

Synchronous Bus Transfer Example: Read T 1 T 2 T 3 Clock Address lines From processor Memory address AS R/W Bidirectional Data lines Data from memory Data accepted by processor 1998 Morgan Kaufmann Publishers 10

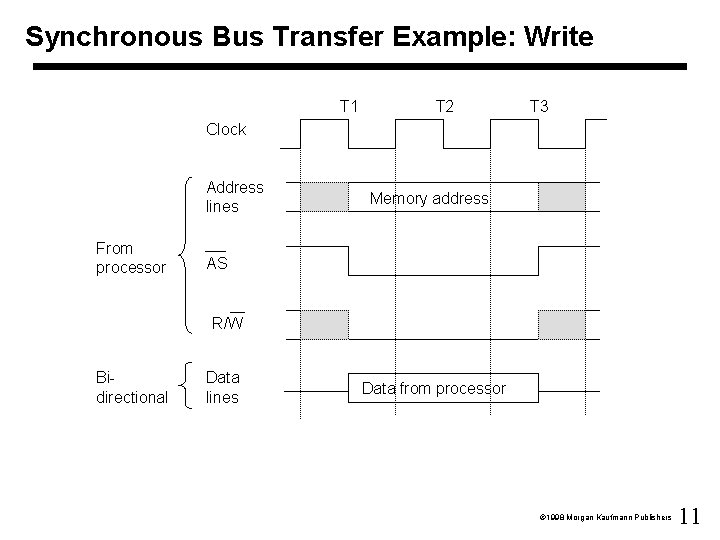

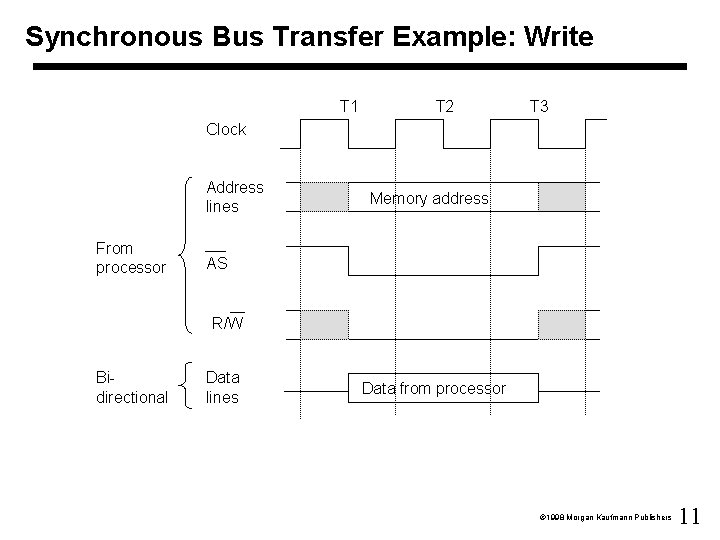

Synchronous Bus Transfer Example: Write T 1 T 2 T 3 Clock Address lines From processor Memory address AS R/W Bidirectional Data lines Data from processor 1998 Morgan Kaufmann Publishers 11

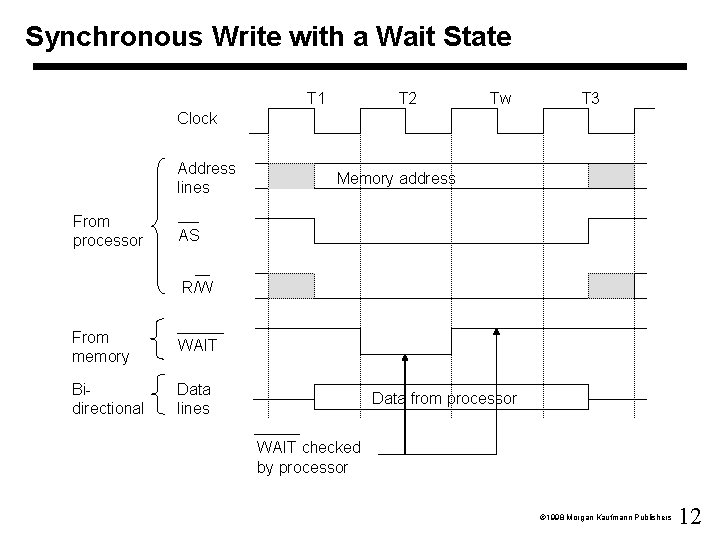

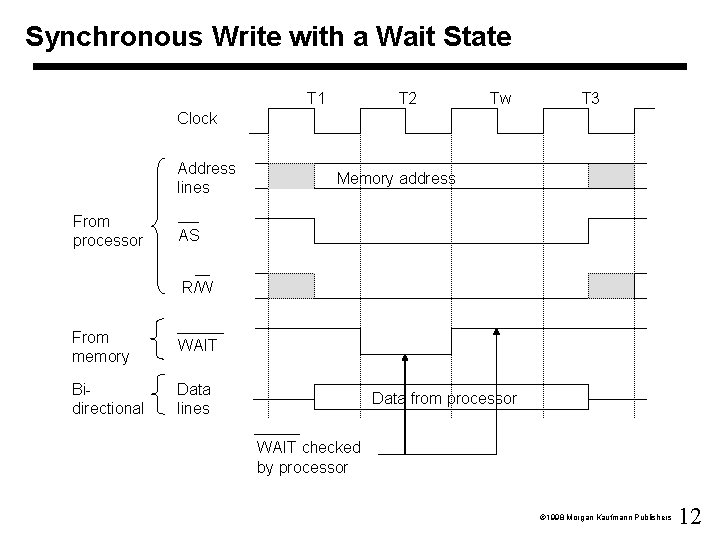

Synchronous Write with a Wait State T 1 T 2 Tw T 3 Clock Address lines From processor Memory address AS R/W From memory WAIT Bidirectional Data lines Data from processor WAIT checked by processor 1998 Morgan Kaufmann Publishers 12

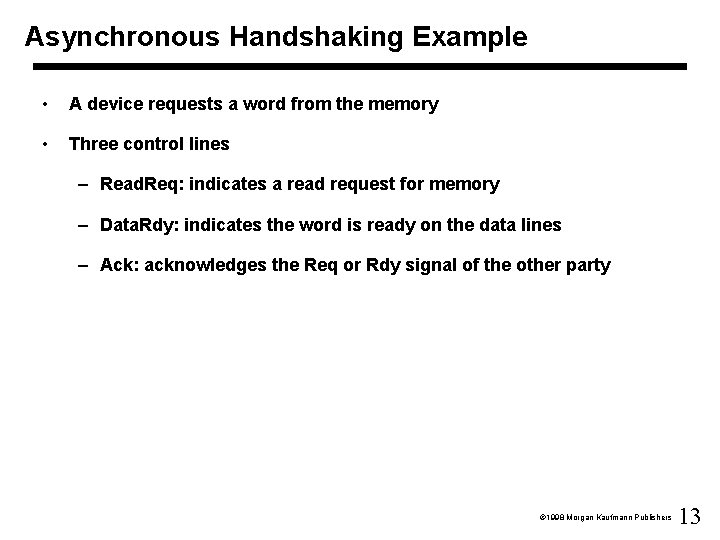

Asynchronous Handshaking Example • A device requests a word from the memory • Three control lines – Read. Req: indicates a read request for memory – Data. Rdy: indicates the word is ready on the data lines – Ack: acknowledges the Req or Rdy signal of the other party 1998 Morgan Kaufmann Publishers 13

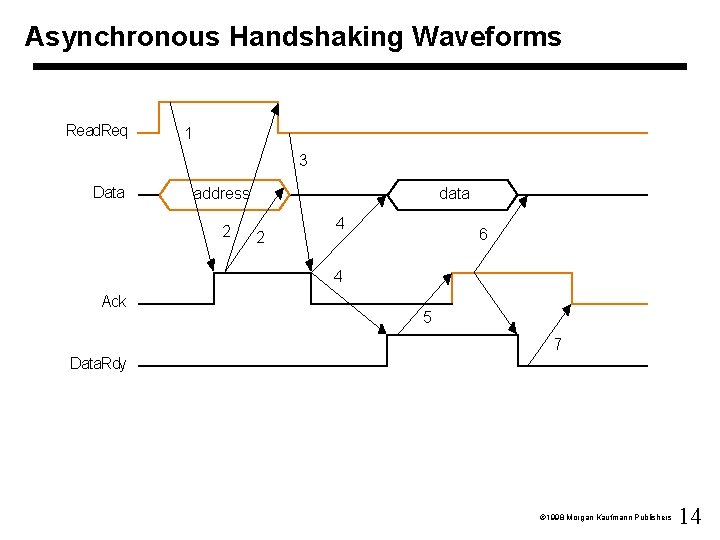

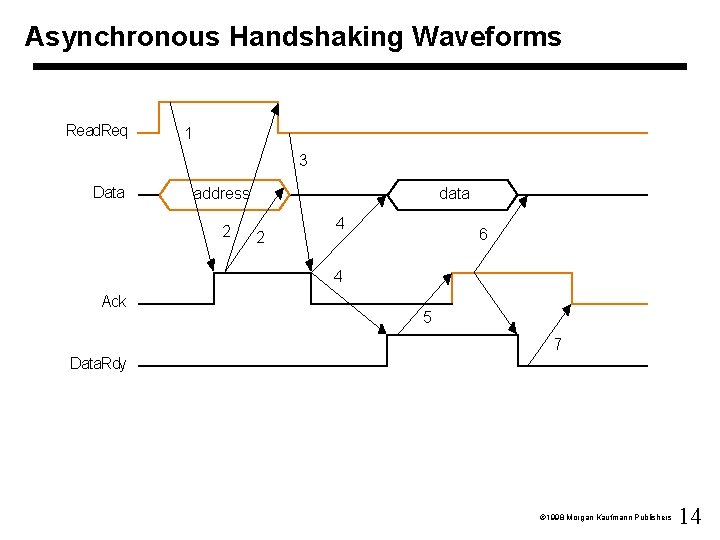

Asynchronous Handshaking Waveforms Read. Req 1 3 Data address 2 data 2 4 6 4 Ack 5 7 Data. Rdy 1998 Morgan Kaufmann Publishers 14

Controlling Bus Access • A bus master controls access to the bus – it initiates and controls all bus requests – the slave responds to requests • Single bus master – the processor • Multiple bus masters – bus arbitration 1998 Morgan Kaufmann Publishers 15

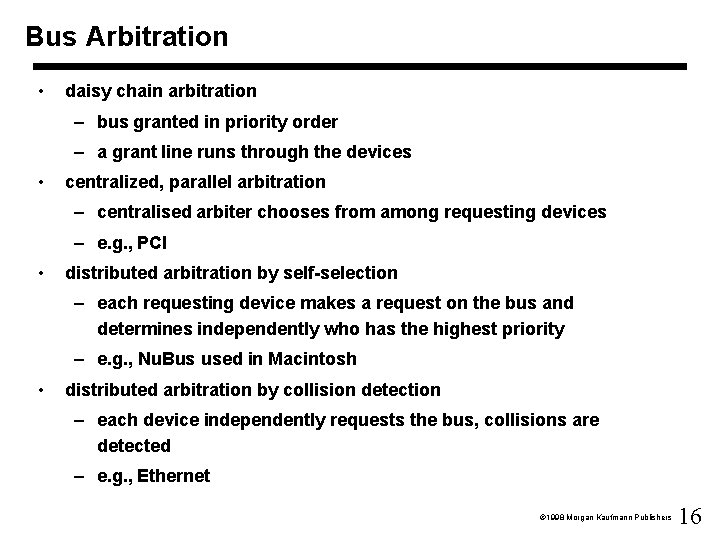

Bus Arbitration • daisy chain arbitration – bus granted in priority order – a grant line runs through the devices • centralized, parallel arbitration – centralised arbiter chooses from among requesting devices – e. g. , PCI • distributed arbitration by self-selection – each requesting device makes a request on the bus and determines independently who has the highest priority – e. g. , Nu. Bus used in Macintosh • distributed arbitration by collision detection – each device independently requests the bus, collisions are detected – e. g. , Ethernet 1998 Morgan Kaufmann Publishers 16

Operating system • Responsibilities of the OS arise from – I/O system is shared by multiple programs – I/O systems often use interrupts – low-level control of an I/O device is complex: concurrent events, detailed requirements • Functions the OS must provide – protection, by maintaining user rights – abstractions for accessing devices – interrupt handling – equitable access to shared I/O resources • Three types of communication – OS gives commands to the devices – devices notify the OS when operations are completed – data transfer between memory and an I/O device 1998 Morgan Kaufmann Publishers 17

Giving Commands to I/O Devices • Special I/O instructions specifying – device number – command word • Memory-mapped I/O – portions of the address space are assigned to I/O devices – those addresses are used by the control, status and data registers of the devices – reads and writes to those addresses are interpreted as commands to the I/O devices – user programs are prevented from issuing I/O operations directly 1998 Morgan Kaufmann Publishers 18

Communicating with the Processor • The OS needs to know when – the I/O device has completed an operation – the I/O operation has encounted an error • Methods – polling – interrupt-driven I/O • Polling – the I/O devices put information in status registers – the OS periodically checks the status registers – simple: the processor is totally in control and does all the work – consumes a lot of processor time 1998 Morgan Kaufmann Publishers 19

Communicating with the Processor • Interrupt-driven I/O – I/O interrupts are just like exceptions except: • an I/O interrupt is asynchronous • further information needs to be conveyed – interrupts indicate to the processor that an I/O device needs attention – user program progress is only halted but special hardware is needed to • send a request (device) • detect an interrupt (processor) • save the CPU state during the interrupt service routine (processor) 1998 Morgan Kaufmann Publishers 20

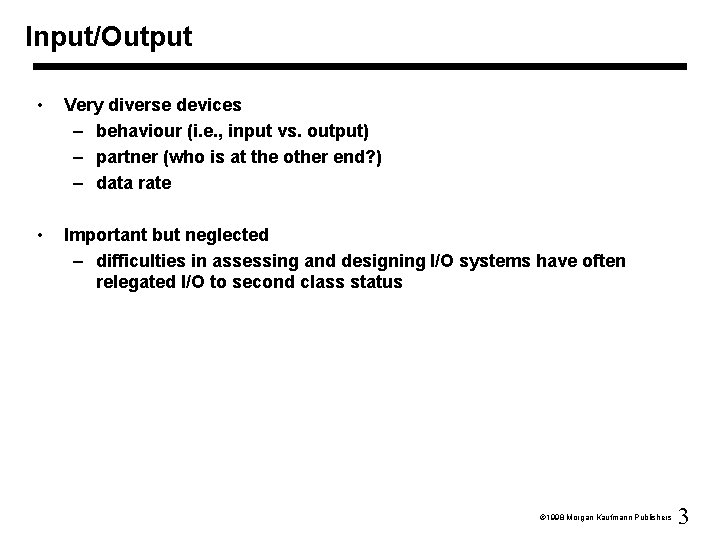

Direct Memory Access • External to the CPU • Direct transfer of data to or from the memory without involving the processor • The DMA controller becomes the bus master and directs the reads and writes • Steps in a DMA transfer – the processor supplies the identity of the device, the operation, the memory address and the number of bytes – the DMA controller completes the operation without bothering the processor – the DMA controller interrupts the processor to inform that the transfer is complete 1998 Morgan Kaufmann Publishers 21