Peripherals Enhanced FLASH New Peripherals Enhanced FLASH PIC

- Slides: 7

Peripherals & Enhanced FLASH New Peripherals Enhanced FLASH PIC 16 F 87 X and PIC 16 F 62 X © 1999 Microchip Technology Incorporated. All Rights Reserved. S 4525 A Peripherals & Enhanced FLASH 1

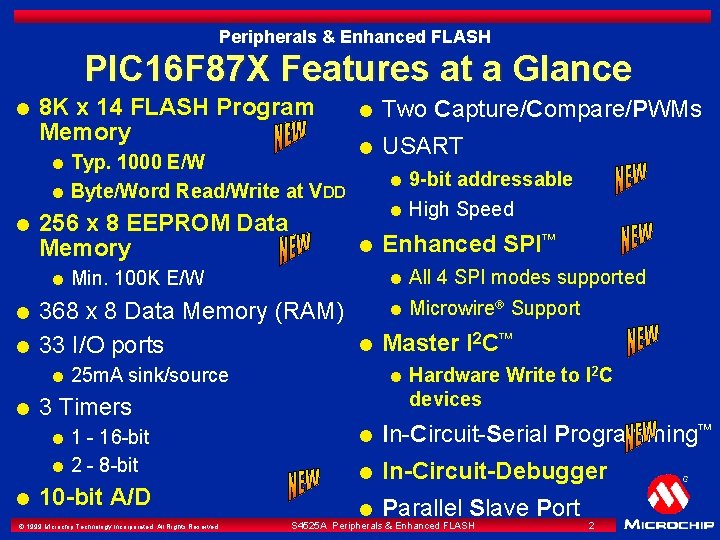

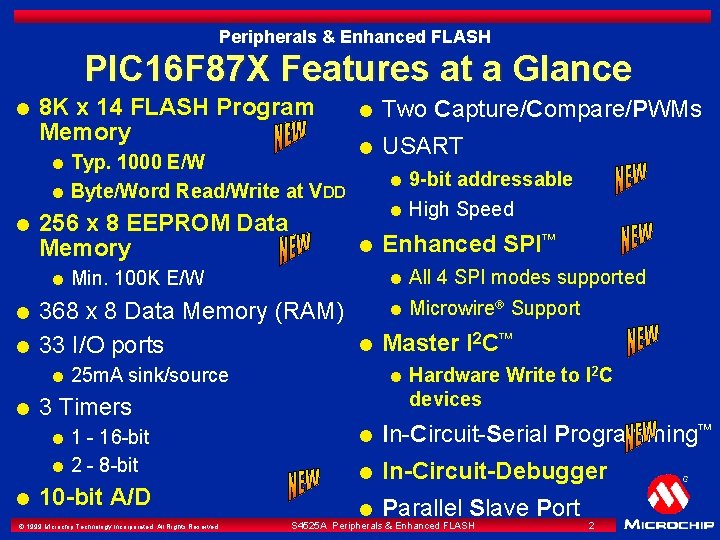

Peripherals & Enhanced FLASH PIC 16 F 87 X Features at a Glance l 8 K x 14 FLASH Program Memory l l l 256 x 8 EEPROM Data Memory l l USART Min. 100 K E/W l 25 m. A sink/source l 1 - 16 -bit 2 - 8 -bit 10 -bit A/D © 1999 Microchip Technology Incorporated. All Rights Reserved. l 9 -bit addressable l High Speed Enhanced SPIä l All 4 SPI modes supported l Microwire Support Master I 2 Cä l 3 Timers l l Two Capture/Compare/PWMs l 368 x 8 Data Memory (RAM) 33 I/O ports l l Typ. 1000 E/W Byte/Word Read/Write at VDD l Hardware Write to I 2 C devices l In-Circuit-Serial Programmingä l In-Circuit-Debugger l Parallel Slave Port S 4525 A Peripherals & Enhanced FLASH 2

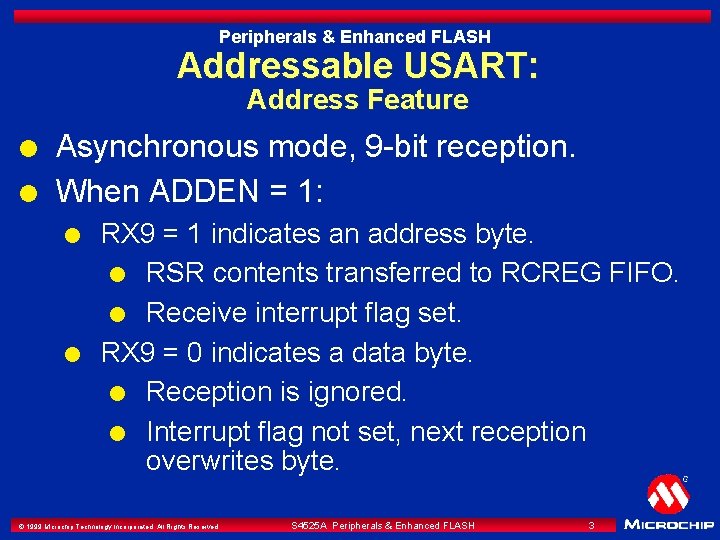

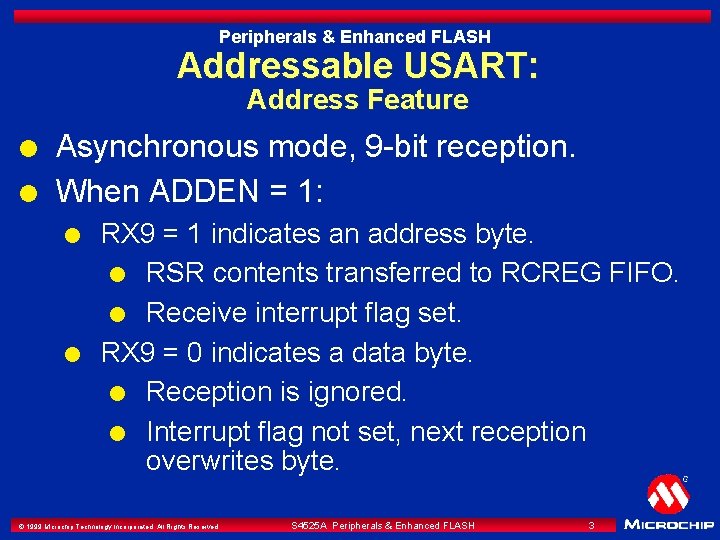

Peripherals & Enhanced FLASH Addressable USART: Address Feature l l Asynchronous mode, 9 -bit reception. When ADDEN = 1: l l RX 9 = 1 indicates an address byte. l RSR contents transferred to RCREG FIFO. l Receive interrupt flag set. RX 9 = 0 indicates a data byte. l Reception is ignored. l Interrupt flag not set, next reception overwrites byte. © 1999 Microchip Technology Incorporated. All Rights Reserved. S 4525 A Peripherals & Enhanced FLASH 3

Peripherals & Enhanced FLASH Addressable USART: Multi-Drop Serial Interface MASTER PIC 16 F 87 X or PIC 16 F 62 X 2 Wire RS-485 SLAVE 1 PIC 16 F 87 X or PIC 16 F 62 X © 1999 Microchip Technology Incorporated. All Rights Reserved. SLAVE 2 PIC 16 F 87 X or • • • PIC 16 F 62 X SLAVE N-1 SLAVE N PIC 16 F 87 X or PIC 16 F 62 X S 4525 A Peripherals & Enhanced FLASH 4

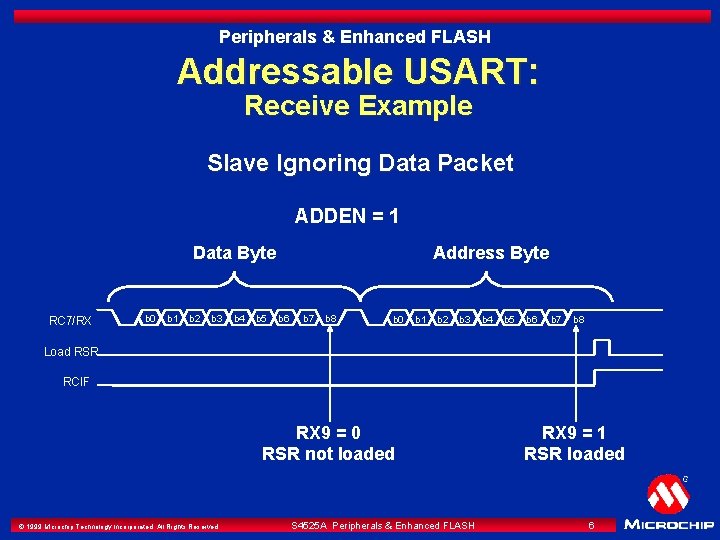

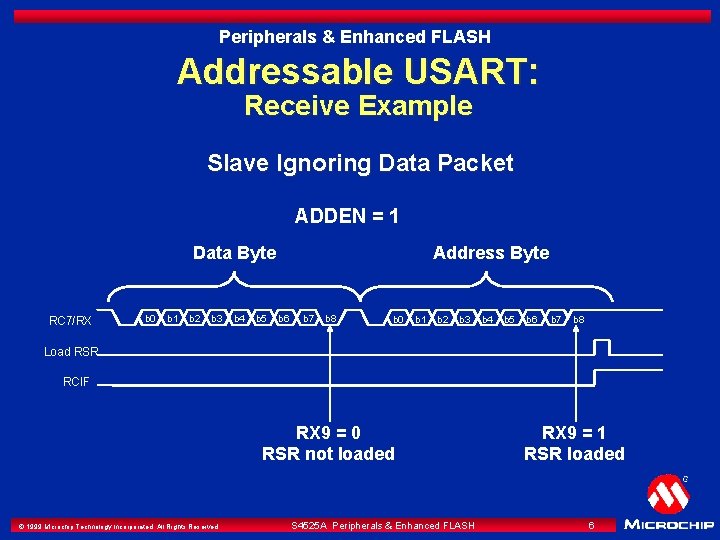

Peripherals & Enhanced FLASH Addressable USART: Receive Example Slave Ignoring Data Packet ADDEN = 1 Data Byte RC 7/RX b 0 b 1 b 2 b 3 b 4 b 5 Address Byte b 6 b 7 b 8 b 0 b 1 b 2 b 3 b 4 b 5 b 6 b 7 b 8 Load RSR RCIF RX 9 = 0 RSR not loaded © 1999 Microchip Technology Incorporated. All Rights Reserved. S 4525 A Peripherals & Enhanced FLASH RX 9 = 1 RSR loaded 6

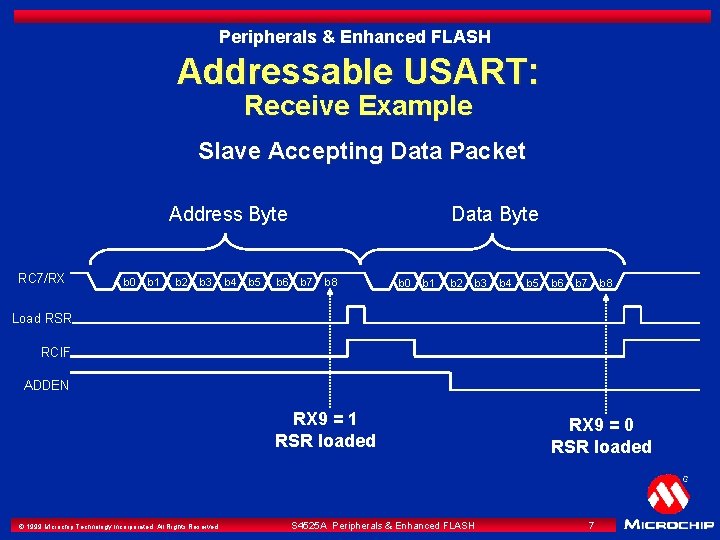

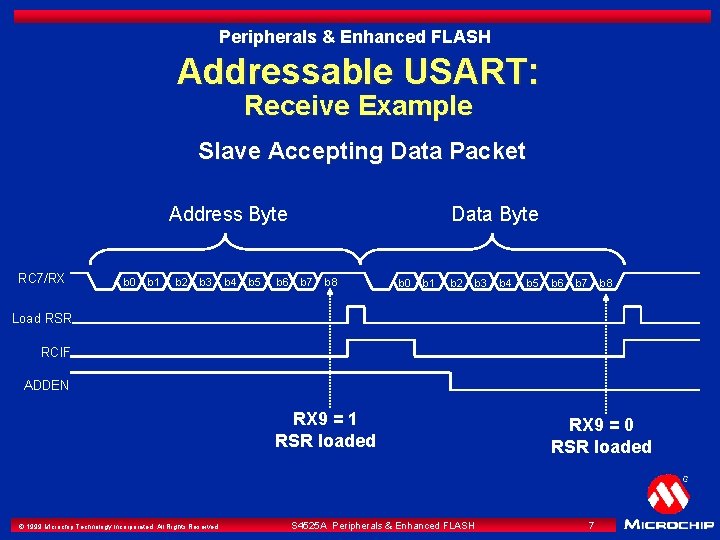

Peripherals & Enhanced FLASH Addressable USART: Receive Example Slave Accepting Data Packet Address Byte RC 7/RX b 0 b 1 b 2 b 3 b 4 b 5 b 6 Data Byte b 7 b 8 b 0 b 1 b 2 b 3 b 4 b 5 b 6 b 7 b 8 Load RSR RCIF ADDEN RX 9 = 1 RSR loaded © 1999 Microchip Technology Incorporated. All Rights Reserved. S 4525 A Peripherals & Enhanced FLASH RX 9 = 0 RSR loaded 7

Peripherals & Enhanced FLASH Addressable USART: Other Features l Dedicated Baud Rate Generator. l l l Does not utilize timer resources. Full duplex receive and transmit supported. Two deep receive buffer. Transmit is double buffer. High speed mode allows operation up to 1. 25 Mbaud. © 1999 Microchip Technology Incorporated. All Rights Reserved. S 4525 A Peripherals & Enhanced FLASH 8