PIC 18 Peripherals PIC 18 F 452458 Peripherals

![• • • CCP/PWM modules [2] I 2 C/SPI serial port USART [RS-232, • • • CCP/PWM modules [2] I 2 C/SPI serial port USART [RS-232,](https://slidetodoc.com/presentation_image_h/e15c56617450bfb1c85bc9c2f4ad52a9/image-3.jpg)

- Slides: 11

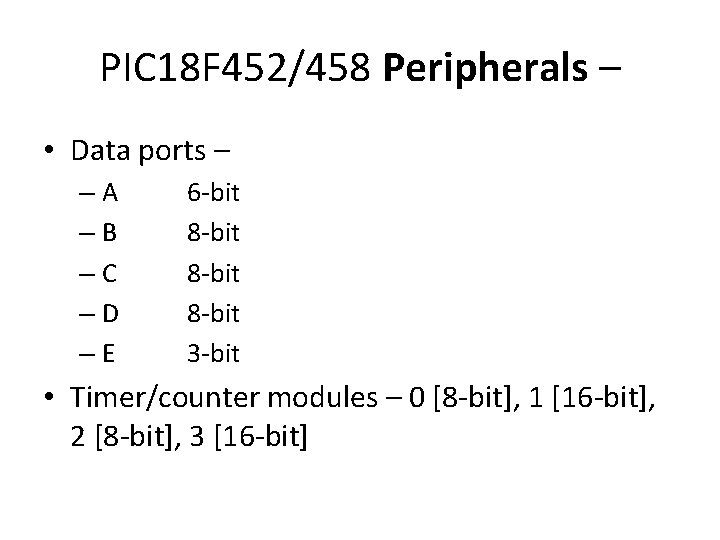

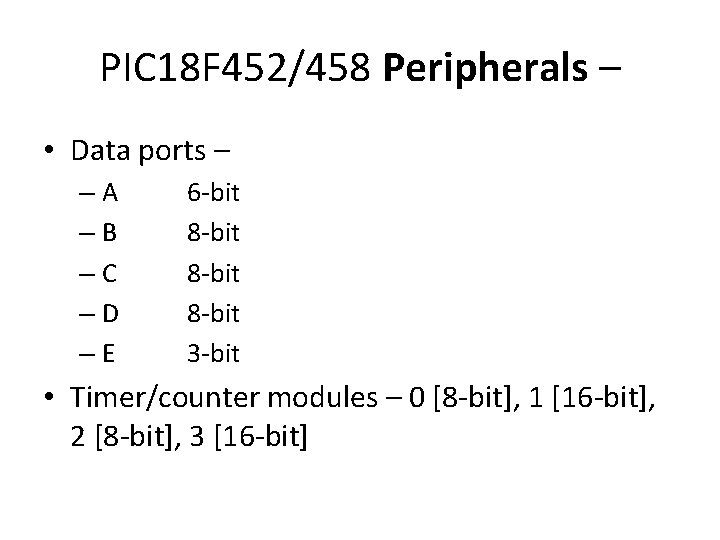

PIC 18 Peripherals

PIC 18 F 452/458 Peripherals – • Data ports – –A –B –C –D –E 6 -bit 8 -bit 3 -bit • Timer/counter modules – 0 [8 -bit], 1 [16 -bit], 2 [8 -bit], 3 [16 -bit]

![CCPPWM modules 2 I 2 CSPI serial port USART RS232 • • • CCP/PWM modules [2] I 2 C/SPI serial port USART [RS-232,](https://slidetodoc.com/presentation_image_h/e15c56617450bfb1c85bc9c2f4ad52a9/image-3.jpg)

• • • CCP/PWM modules [2] I 2 C/SPI serial port USART [RS-232, RS-485] ADC [10 -bit] with 10 way input multiplexer EEPROM [256 byte]

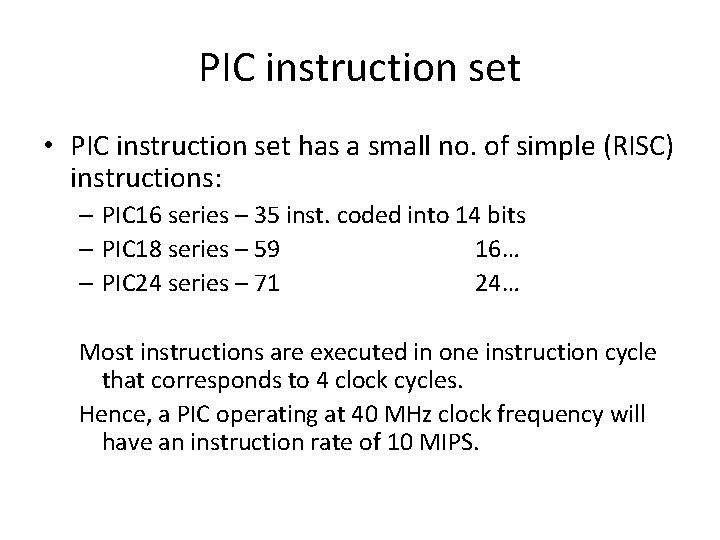

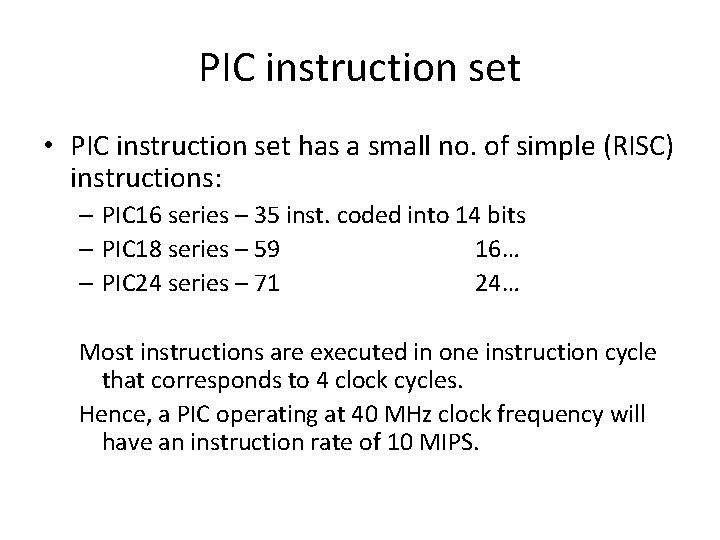

PIC instruction set • PIC instruction set has a small no. of simple (RISC) instructions: – PIC 16 series – 35 inst. coded into 14 bits – PIC 18 series – 59 16… – PIC 24 series – 71 24… Most instructions are executed in one instruction cycle that corresponds to 4 clock cycles. Hence, a PIC operating at 40 MHz clock frequency will have an instruction rate of 10 MIPS.

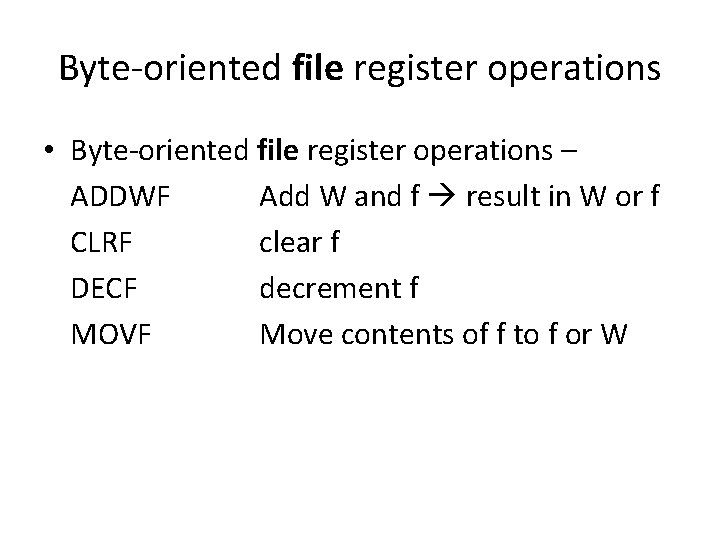

Byte-oriented file register operations • Byte-oriented file register operations – ADDWF Add W and f result in W or f CLRF clear f DECF decrement f MOVF Move contents of f to f or W

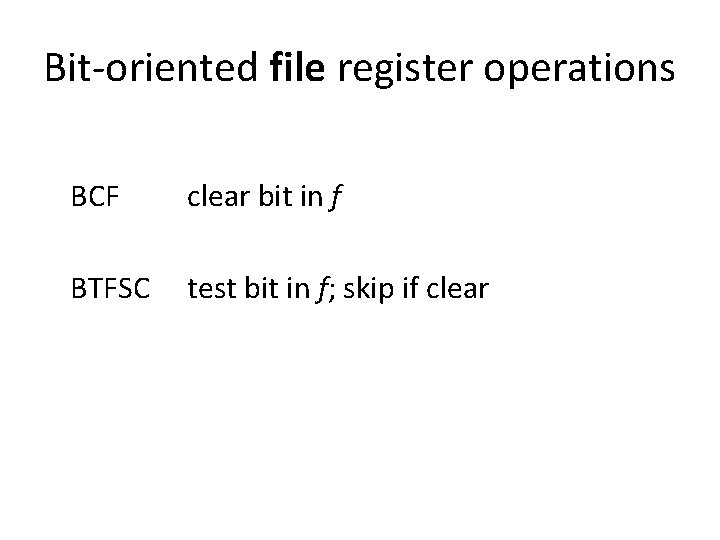

Bit-oriented file register operations BCF clear bit in f BTFSC test bit in f; skip if clear

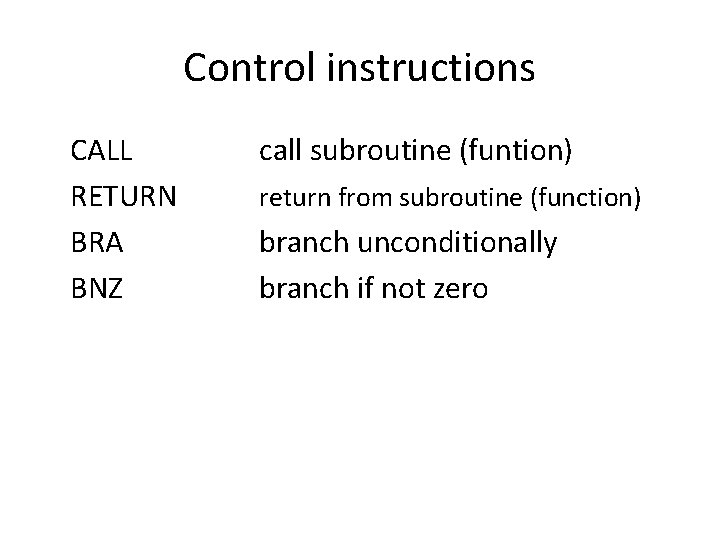

Control instructions CALL RETURN BRA BNZ call subroutine (funtion) return from subroutine (function) branch unconditionally branch if not zero

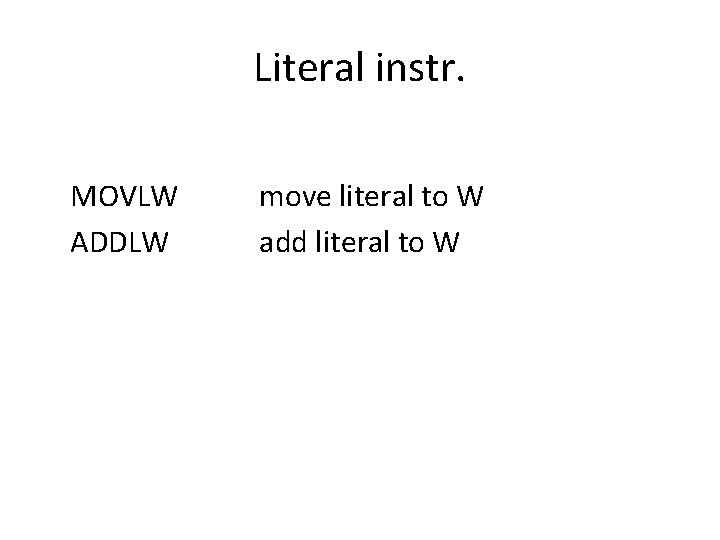

Literal instr. MOVLW ADDLW move literal to W add literal to W

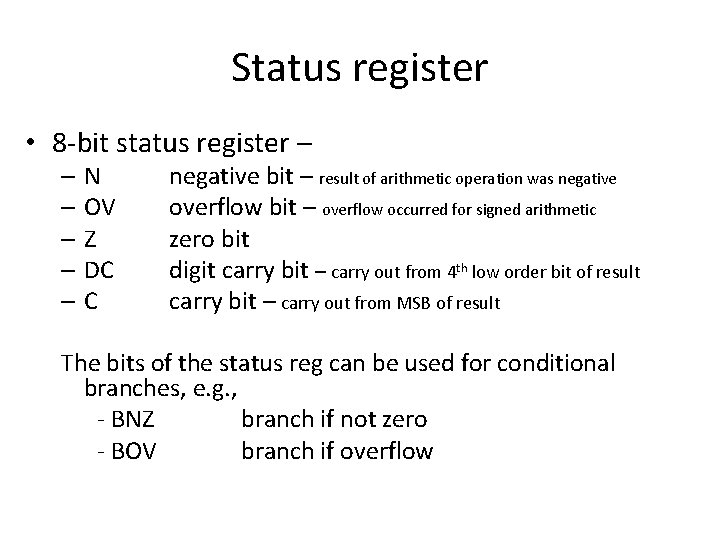

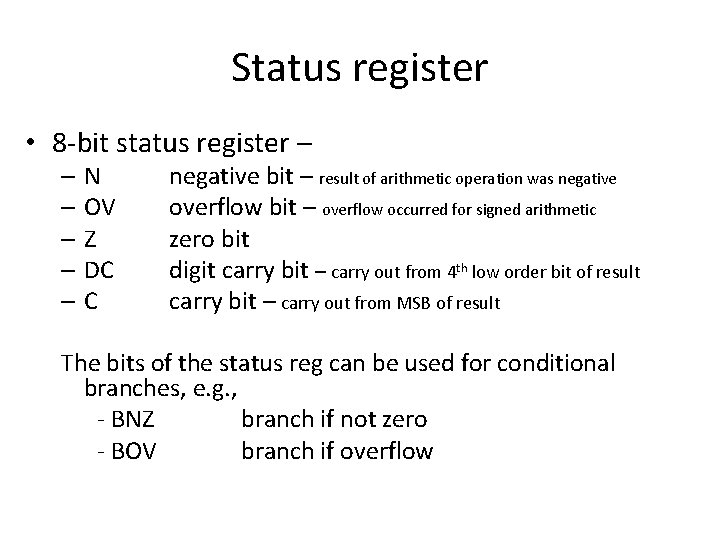

Status register • 8 -bit status register – –N – OV –Z – DC –C negative bit – result of arithmetic operation was negative overflow bit – overflow occurred for signed arithmetic zero bit digit carry bit – carry out from 4 th low order bit of result carry bit – carry out from MSB of result The bits of the status reg can be used for conditional branches, e. g. , - BNZ branch if not zero - BOV branch if overflow

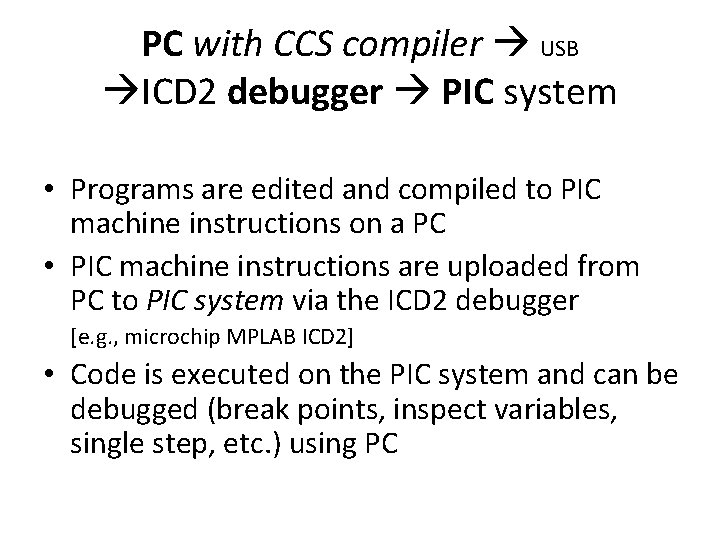

CCS PIC compiler • Compiler – high-level language prog to machine instructions for the target processor • Cross-compiler – is a compiler that runs on a processor that is different from the target processor • E. g. , CCS cross-compiler • Most embedded systems are now programmed using C/C++ lang.

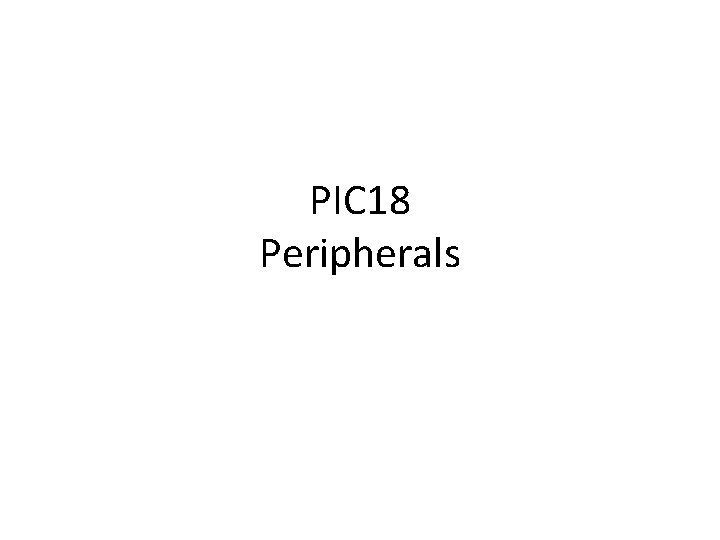

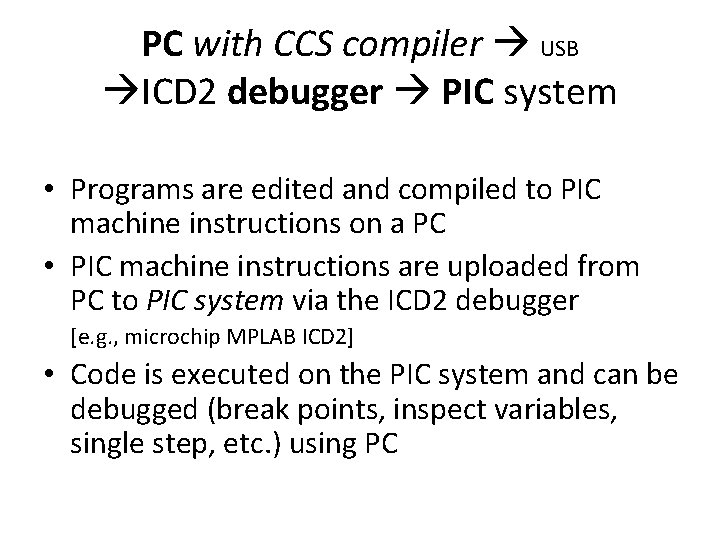

PC with CCS compiler USB ICD 2 debugger PIC system • Programs are edited and compiled to PIC machine instructions on a PC • PIC machine instructions are uploaded from PC to PIC system via the ICD 2 debugger [e. g. , microchip MPLAB ICD 2] • Code is executed on the PIC system and can be debugged (break points, inspect variables, single step, etc. ) using PC