Cache Memory Cache Memory Cache memory adalah memori

- Slides: 41

Cache Memory

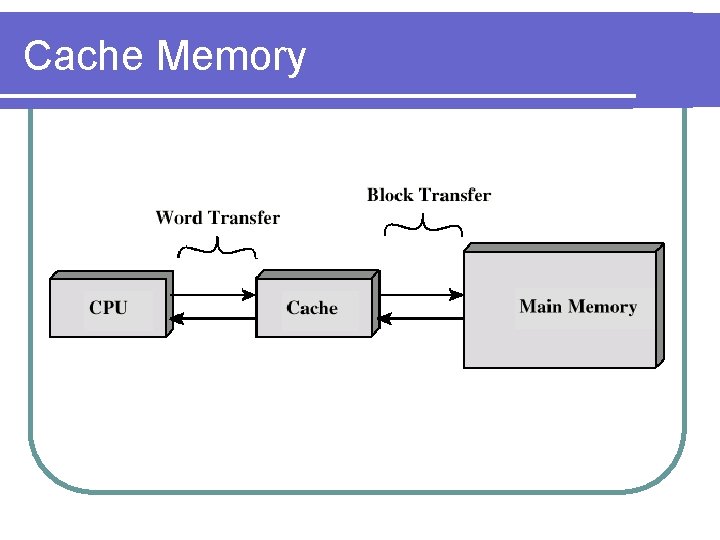

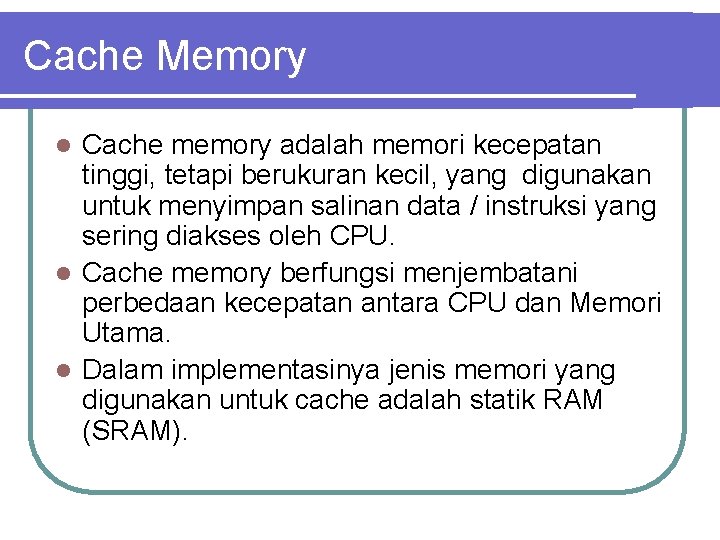

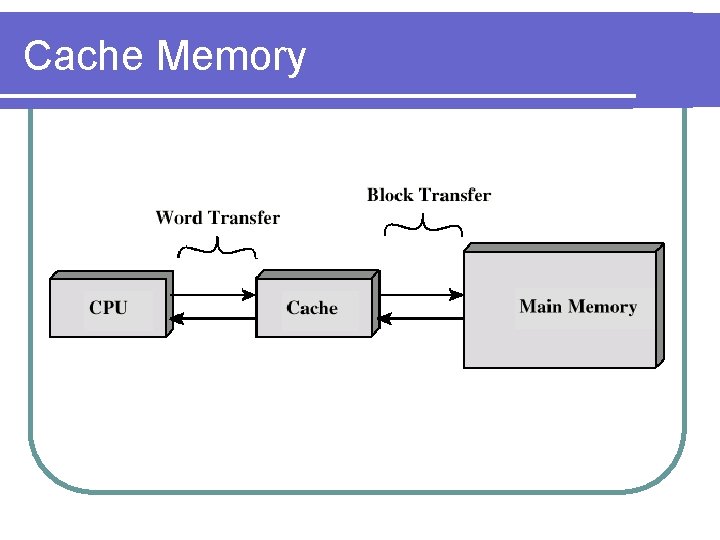

Cache Memory Cache memory adalah memori kecepatan tinggi, tetapi berukuran kecil, yang digunakan untuk menyimpan salinan data / instruksi yang sering diakses oleh CPU. l Cache memory berfungsi menjembatani perbedaan kecepatan antara CPU dan Memori Utama. l Dalam implementasinya jenis memori yang digunakan untuk cache adalah statik RAM (SRAM). l

Cache Memory

Operasi Cache l CPU meminta isi suatu lokasi memori l Memeriksa apakah data terdapat di cache l Jika ada di cache, ambil data dari cache (cepat) l Jika tidak ada di cache, copy isi memori ke cache dan kirimkan data yang diminta ke CPU (lambat).

Locality of Reference l Pada saat eksekusi program, memori cenderung membaca suatu cluster di memori. l Contoh : Loop

Cache Design l Ukuran cache l Pemetaan (Mapping Function) l Algoritma Penggantian (Replacement Algorithm) l Write Policy l Ukuran Blok l Jumlah Cache

Ukuran Cache l Kecepatan Semakin besar ukuran cache semakin cepat (sampai ukuran tertentu) l Apabila ukuran cache semakin besar, proses pengecekan cache lebih lama. l l Harga l Semakin besar cache, semakin mahal

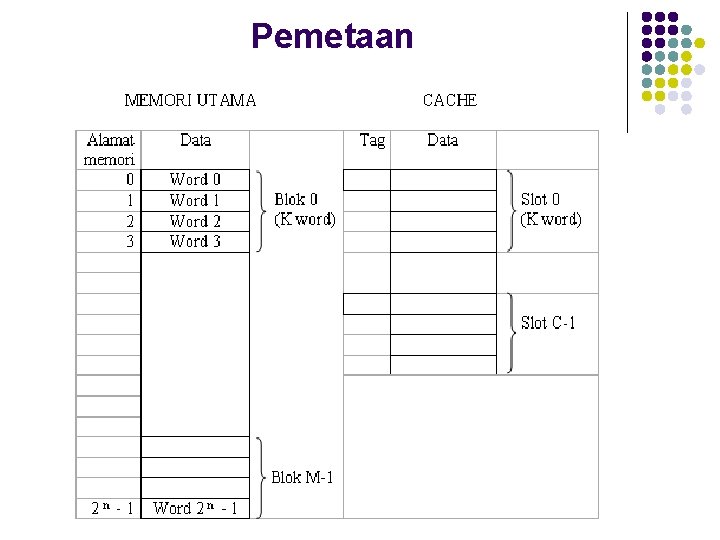

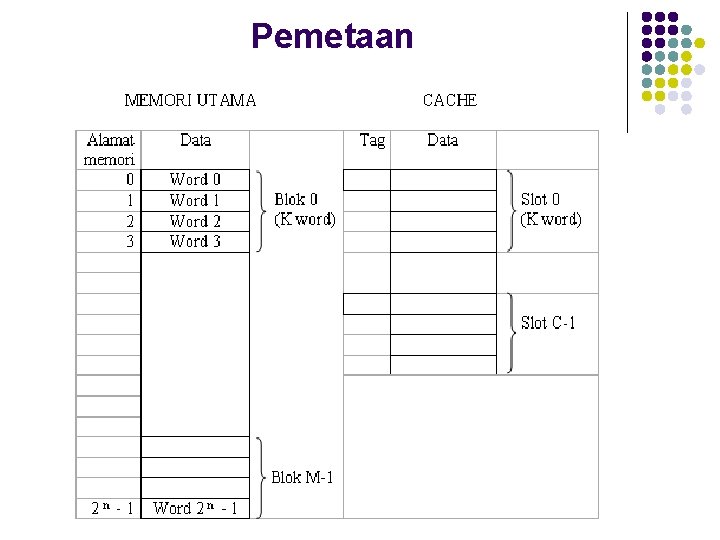

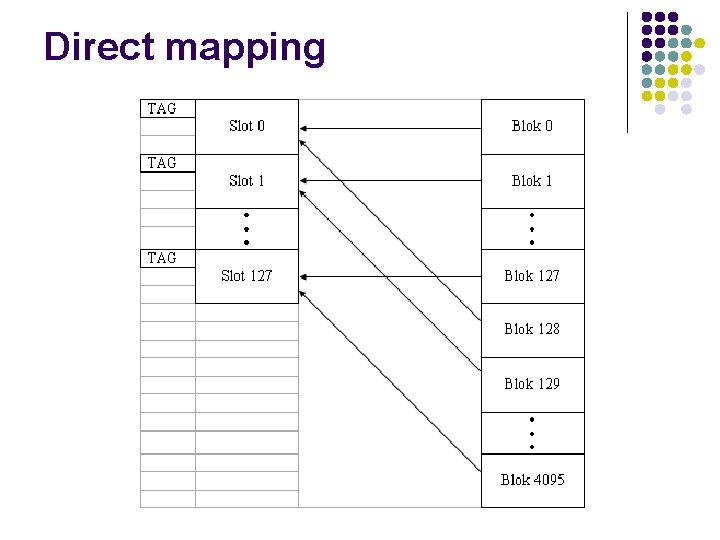

Pemetaan l Blok-blok memori utama akan dipetakan ke slot-slot cache. l Ukuran memori utama jauh lebih besar dari ukuran cache (C << M) sehingga tidak semua blok memori utama dapat ditempatkan pada cache. l Untuk itu diperlukan suatu cara untuk memetakan blok memori utama ke cache.

Pemetaan

Teknik Pemetaan Direct mapping l Fully associative mapping l Set associative mapping l

Teknik Pemetaan l Untuk menjelaskan teknik-teknik pemetaan ini digunakan data-data berikut : Ukuran memori utama = 216 word l Ukuran cache = 211 word. l Ukuran blok memori = ukuran slot cache = 16 word = 24 word. l Jumlah blok memori = 216 / 24 = 4096 blok l Jumlah slot cache = 211 / 24 = 128 slot. l

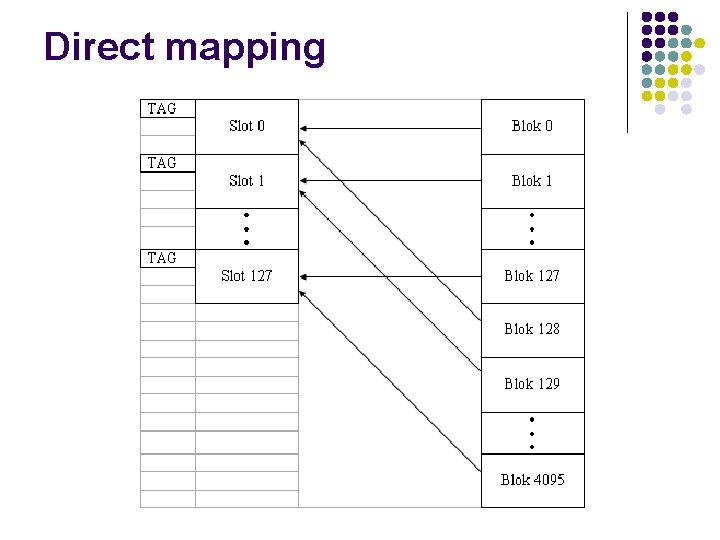

Direct mapping l Aturan pemetaannya: i = j modulus m di mana: l i = nomor slot cache l j = nomor blok memori utama l m = jumlah slot cache

Direct mapping

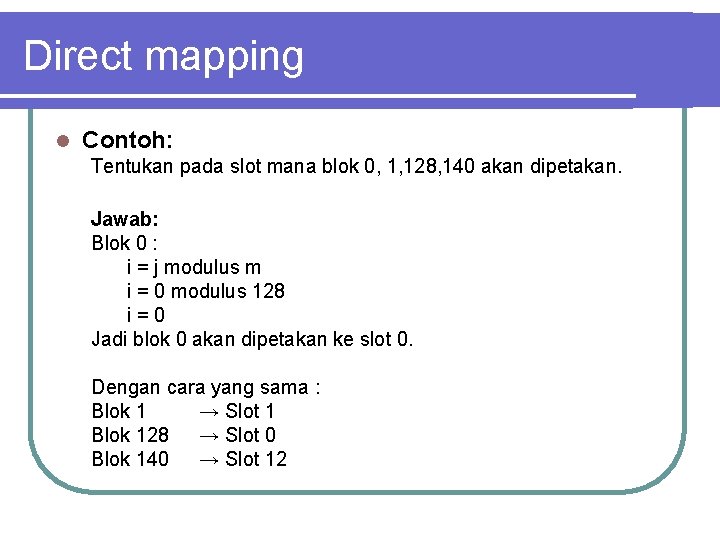

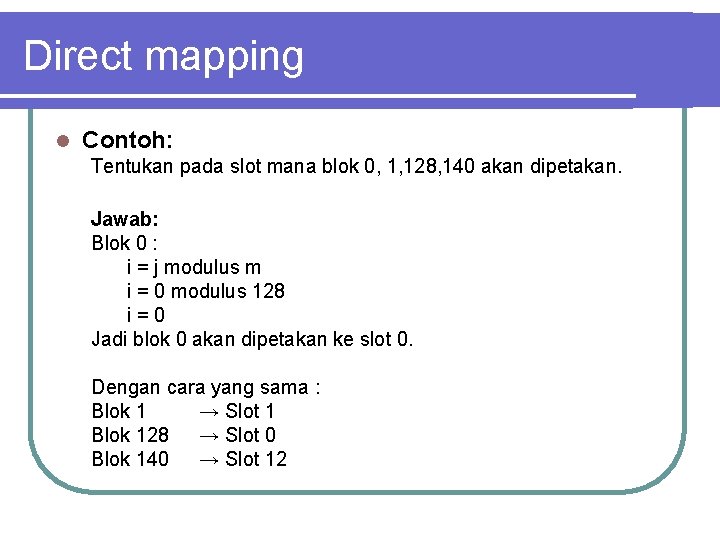

Direct mapping l Contoh: Tentukan pada slot mana blok 0, 1, 128, 140 akan dipetakan. Jawab: Blok 0 : i = j modulus m i = 0 modulus 128 i=0 Jadi blok 0 akan dipetakan ke slot 0. Dengan cara yang sama : Blok 1 → Slot 1 Blok 128 → Slot 0 Blok 140 → Slot 12

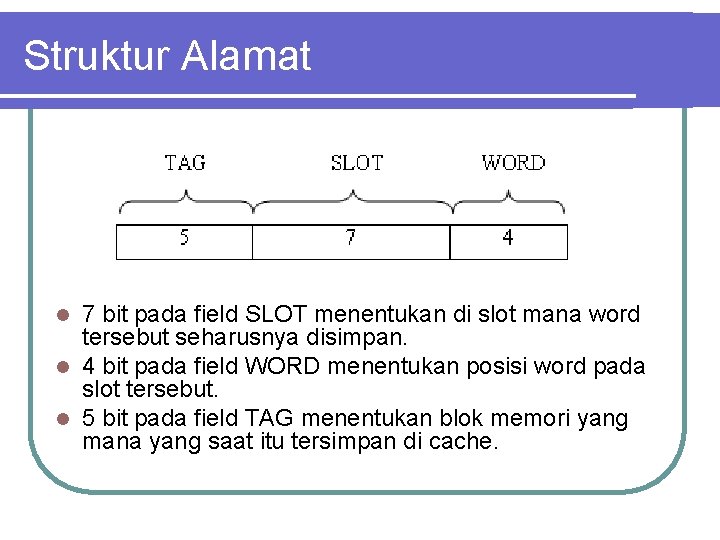

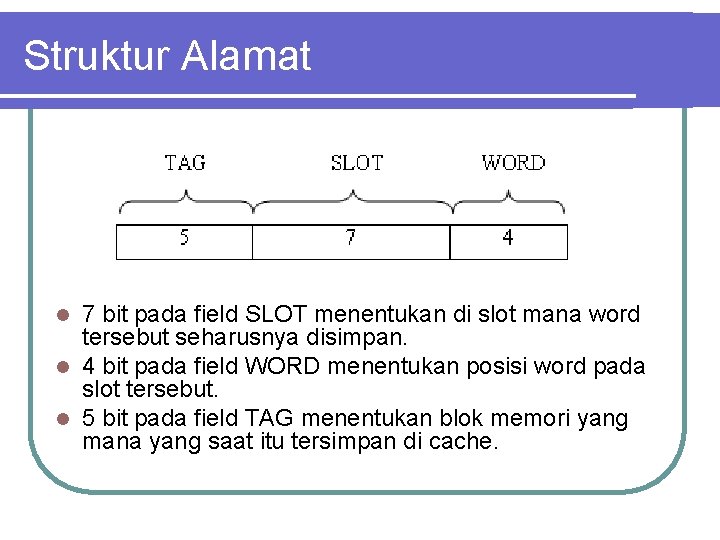

Struktur Alamat 7 bit pada field SLOT menentukan di slot mana word tersebut seharusnya disimpan. l 4 bit pada field WORD menentukan posisi word pada slot tersebut. l 5 bit pada field TAG menentukan blok memori yang mana yang saat itu tersimpan di cache. l

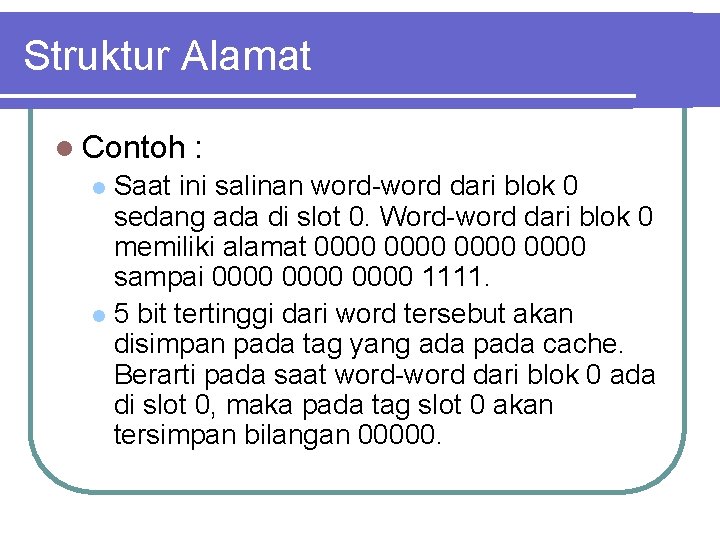

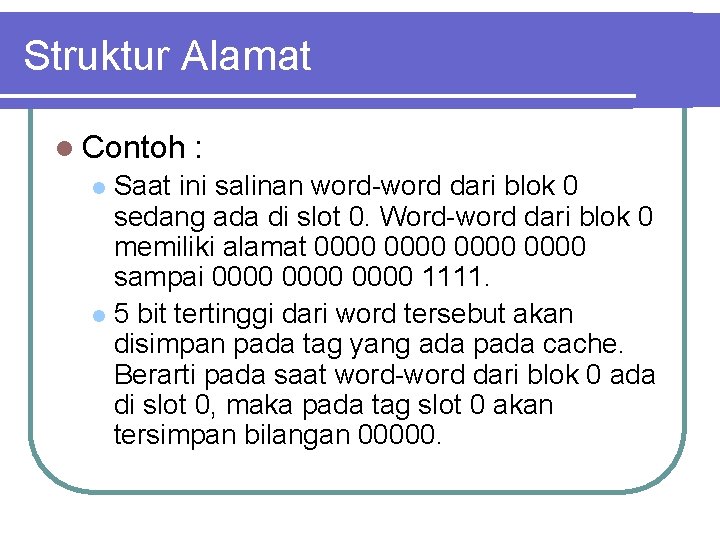

Struktur Alamat l Contoh : Saat ini salinan word-word dari blok 0 sedang ada di slot 0. Word-word dari blok 0 memiliki alamat 0000 sampai 0000 1111. l 5 bit tertinggi dari word tersebut akan disimpan pada tag yang ada pada cache. Berarti pada saat word-word dari blok 0 ada di slot 0, maka pada tag slot 0 akan tersimpan bilangan 00000. l

Struktur Alamat Misalkan CPU akan mengambil sebuah word dengan alamat 0000. l Maka yang pertama kali diproses adalah 7 bit pada field SLOT = 0000. l Ini berarti data tersebut seharusnya tersimpan pada slot 0. l Untuk memastikan apakah word tersebut ada pada slot 0, 5 bit tertinggi dari alamat tersebut (0000 0) dibandingkan dengan isi tag slot 0. Ternyata sama, kesimpulannya word tersebut ada di cache. l

Struktur Alamat Misalkan CPU akan mengambil sebuah word dengan alamat 1000 0000. l Maka yang pertama kali diproses adalah 7 bit pada field SLOT = 0000. l Ini berarti data tersebut seharusnya tersimpan pada slot 0. l Untuk memastikan apakah word tersebut ada pada slot 0, 5 bit tertinggi dari alamat tersebut (1000 0) dibandingkan dengan isi tag slot 0 (0000 0). Ternyata tidak sama, kesimpulannya word tersebut tidak ada di cache. l

Keuntungan & Kelemahan Direct Mapping Keuntungan teknik direct mapping adalah pada kesederhanaan proses pemetaannya. Selain itu pada saat proses pengecekan ada tidaknya word di cache hanya satu tag yang perlu dicek isinya. l Kelemahan teknik direct mapping adalah kurang fleksibel, sebuah blok harus dipetakan ke slot yang tetap, sehingga tidak bisa memanfaatkan slot yang kosong. l

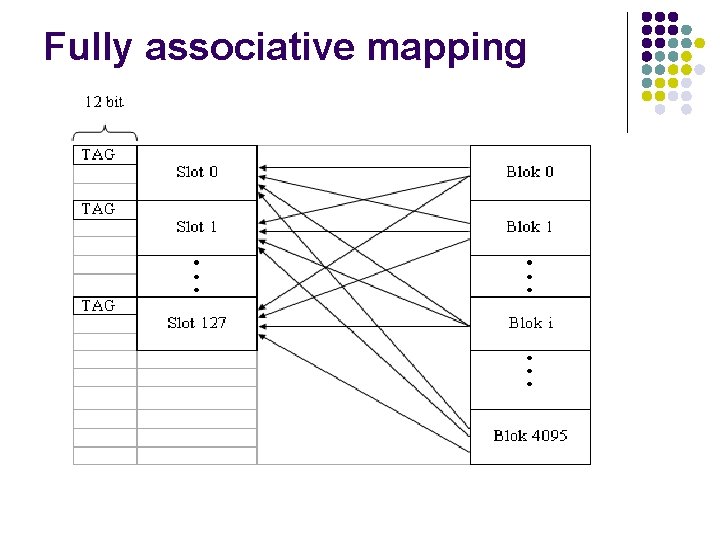

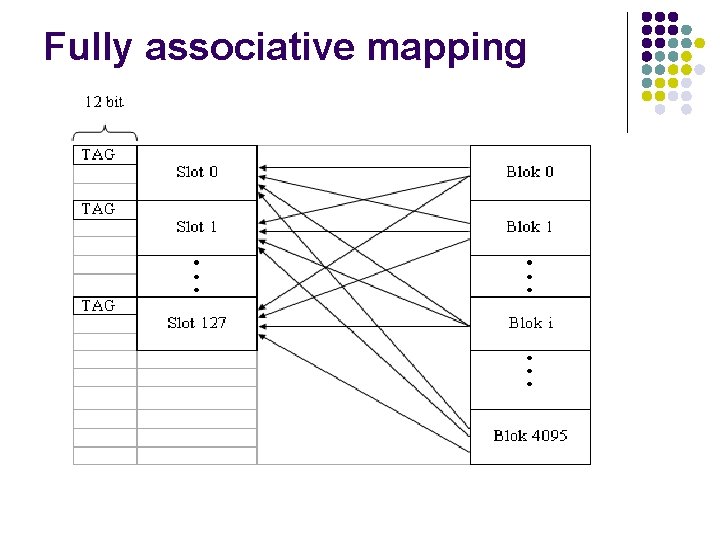

Fully associative mapping l Teknik ini digunakan untuk mengatasi ketidakfleksibelan teknik direct mapping. l Pada teknik ini setiap blok boleh dipetakan ke blok mana saja. Dengan cara ini pemetaan lebih fleksibel dan dapat memanfaatkan slot-slot yang kosong.

Fully associative mapping

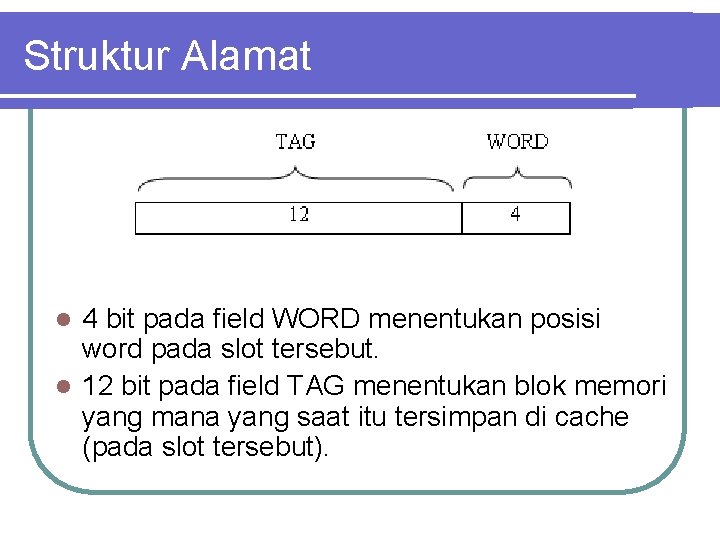

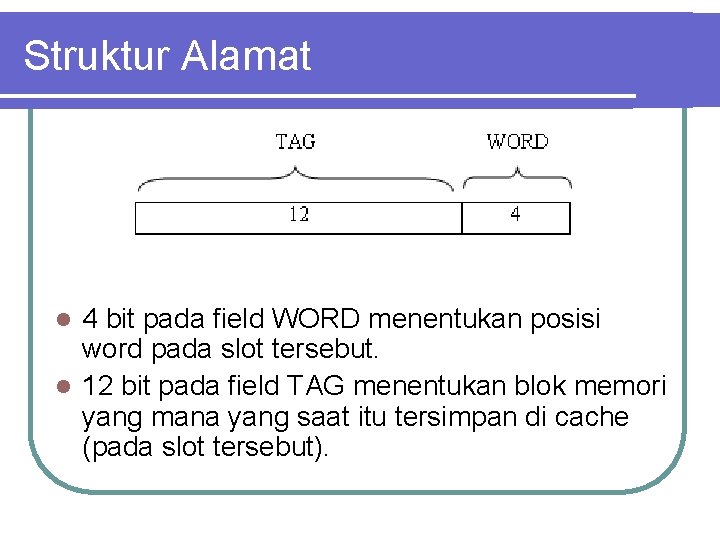

Struktur Alamat 4 bit pada field WORD menentukan posisi word pada slot tersebut. l 12 bit pada field TAG menentukan blok memori yang mana yang saat itu tersimpan di cache (pada slot tersebut). l

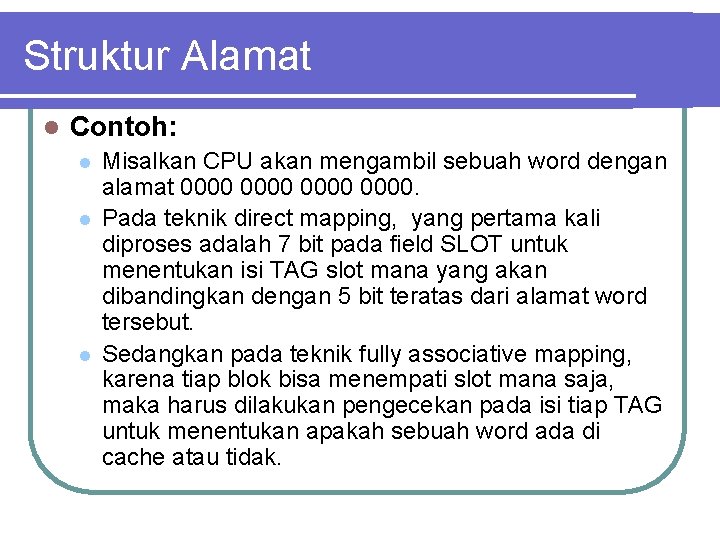

Struktur Alamat l Contoh: l l l Misalkan CPU akan mengambil sebuah word dengan alamat 0000. Pada teknik direct mapping, yang pertama kali diproses adalah 7 bit pada field SLOT untuk menentukan isi TAG slot mana yang akan dibandingkan dengan 5 bit teratas dari alamat word tersebut. Sedangkan pada teknik fully associative mapping, karena tiap blok bisa menempati slot mana saja, maka harus dilakukan pengecekan pada isi tiap TAG untuk menentukan apakah sebuah word ada di cache atau tidak.

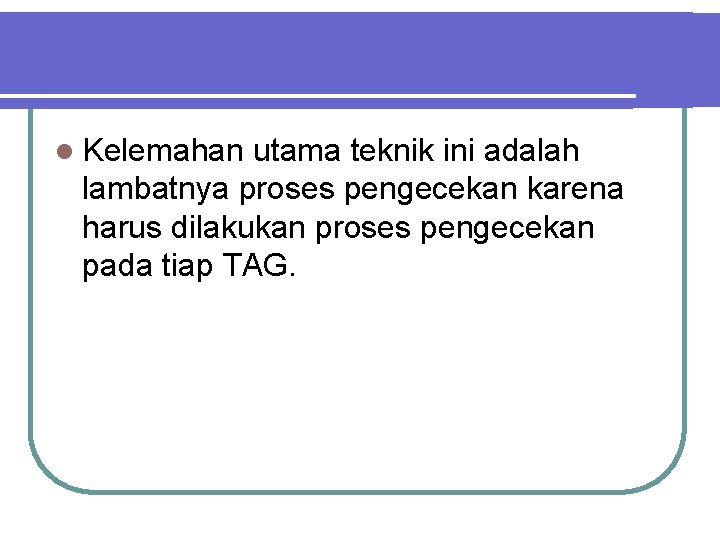

l Kelemahan utama teknik ini adalah lambatnya proses pengecekan karena harus dilakukan proses pengecekan pada tiap TAG.

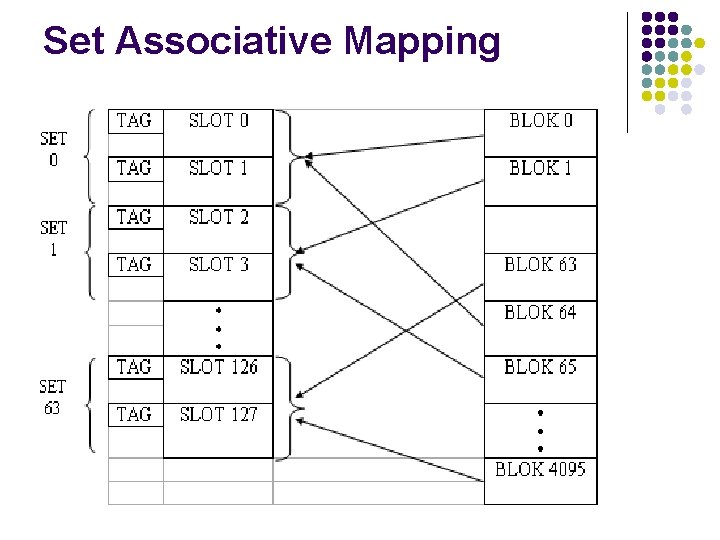

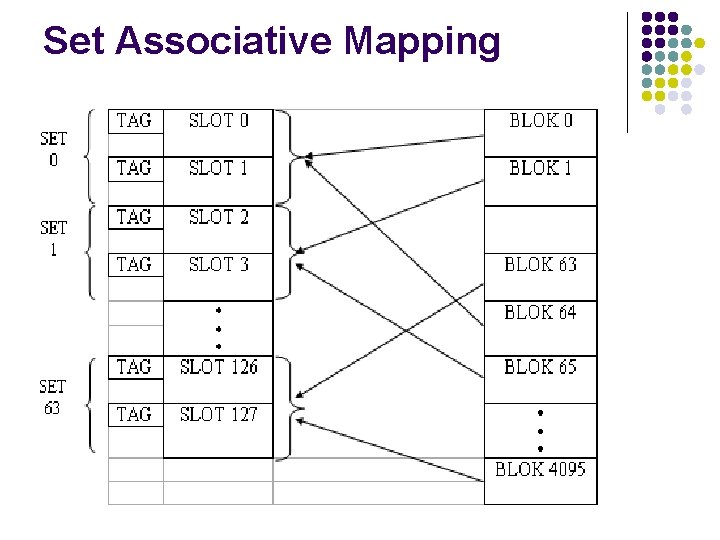

Set Associative Mapping l Teknik ini merupakan kombinasi kedua teknik sebelumnya. l Pada teknik ini beberapa slot dikelompokkan menjadi sebuah set. Ukuran tiap set dapat diatur. l Tiap blok harus dipetakan pada set tertentu, tetapi bebas dipetakan pada slot mana saja, yang merupakan anggota dari set tersebut.

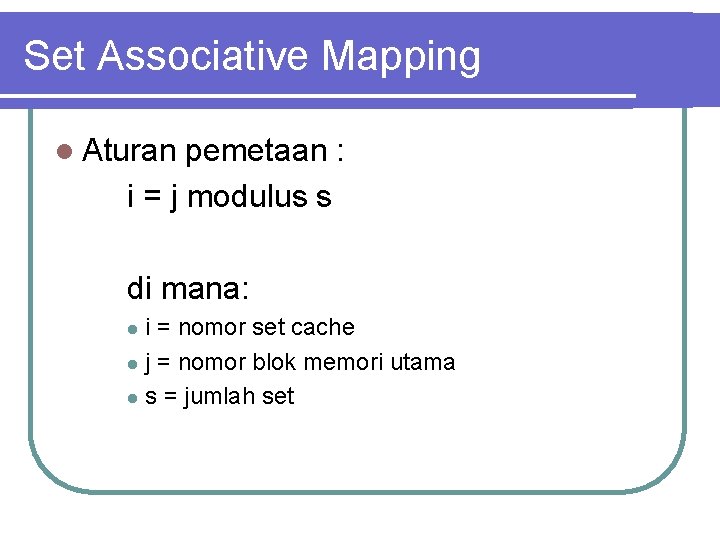

Set Associative Mapping l Aturan pemetaan : i = j modulus s di mana: i = nomor set cache l j = nomor blok memori utama l s = jumlah set l

Set Associative Mapping

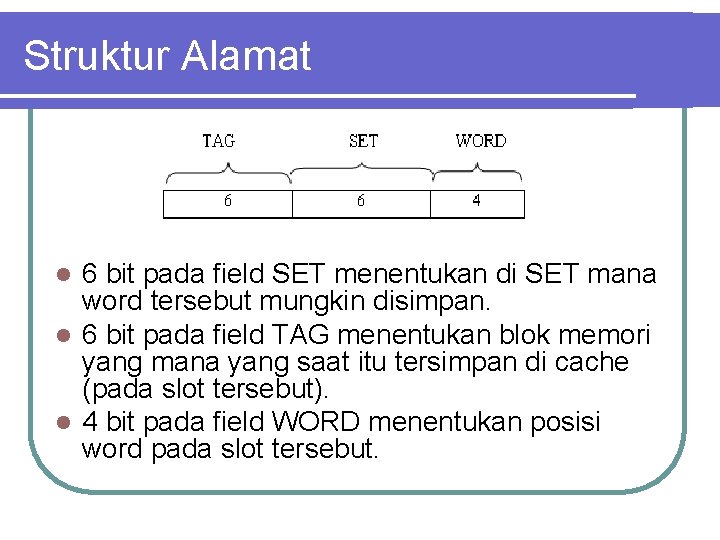

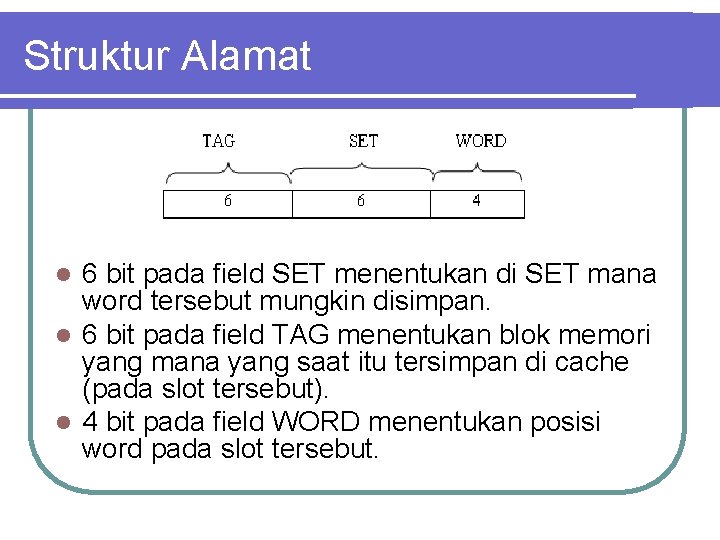

Struktur Alamat 6 bit pada field SET menentukan di SET mana word tersebut mungkin disimpan. l 6 bit pada field TAG menentukan blok memori yang mana yang saat itu tersimpan di cache (pada slot tersebut). l 4 bit pada field WORD menentukan posisi word pada slot tersebut. l

Struktur Alamat l l l Misalkan CPU akan mengambil sebuah word dengan alamat 1111 0000. Maka yang pertama kali diproses adalah 6 bit pada field SET = 00 0000. Ini berarti data tersebut mungkin tersimpan pada SET 0. Selanjutnya untuk mengetahui apakah word tersebut memang ada pada SET 0 atau tidak, 6 bit tertinggi dari alamat tersebut (1111 00) dibandingkan dengan isi tiap TAG yang ada pada SET 0. Jika ada yang sama, berarti word tersebut ada pada SET 0 pada slot yang isi TAG-nya sama dengan keenam bit tersebut. Jika tidak ada yang sama, berarti word tersebut tidak ada di cache dan harus diambil dari memori utama.

Keuntungan l Keuntungan teknik ini adalah lebih fleksibel dibanding dengan teknik direct mapping, tetapi juga proses pembandingan isi tagnya relatif lebih cepat dibanding teknik fully associative karena jumlah tag yang dibandingkan lebih sedikit.

Algoritma pergantian Pada teknik direct mapping, jika sebuah blok akan disalinkan ke sebuah slot dan slot tersebut sedang terisi, maka blok yang baru tersebut langsung akan menggantikan blok yang lama. l Pada teknik fully associative dan set associative mapping, jika sebuah blok akan disalinkan ke slot cache dan semua slot saat itu penuh, maka harus ditentukan isi slot mana yang harus diganti. Untuk itu diperlukan suatu algoritma penggantian. l

Algoritma pergantian l Algorima penggantian yang bisa digunakan adalah : First In First Out (FIFO) : mengganti blok yang paling lama menempati cache. l Least Recently Used (LRU) : mengganti blok yang paling lama tidak digunakan. l Least Frequently Used (LFU) : mengganti blok yang paling jarang digunakan. l Random : mengganti secara acak. l

Write Policy l Sebelum sebuah blok yang berada di dalam cache dapat diganti, harus diketahui apakah blok tersebut sudah diubah selama di cache atau tidak. l Bila belum diubah, blok lama dapat langsung ditindih. l Bila sudah diubah, maka isi memori utama harus diperbaharui.

Write Policy l Ada 2 write policy yang biasa digunakan, yaitu: Write Through l Write Back l

Write Through l Penulisan dilakukan pada cache dan juga memori utama l Akan menyebabkan banyak trafik l Memperlambat proses penulisan

Write Back l l l Pada awalnya, perubahan hanya dilakukan di cache. Sebuah bit akan diset apabila update terjadi. Pada saat blok akan diganti, penulisan pada memori hanya dilakukan apabila bit tersebut dalam keadaan diset. Setiap I/O harus mengakses langsung ke cache karena isi memori utama tidak valid. Rangkaian menjadi rumit.

Ukuran kinerja cache l Ukuran kinerja cache, dilihat berdasarkan miss ratio : l Hit ratio (HR) = Jumlah referensi yang mengacu pada cache / total jumlah referensi l Miss ratio (MR) = 1 - HR

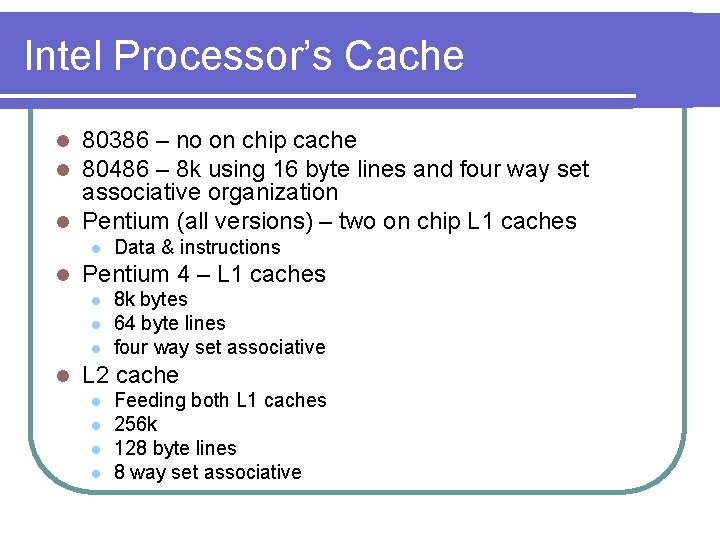

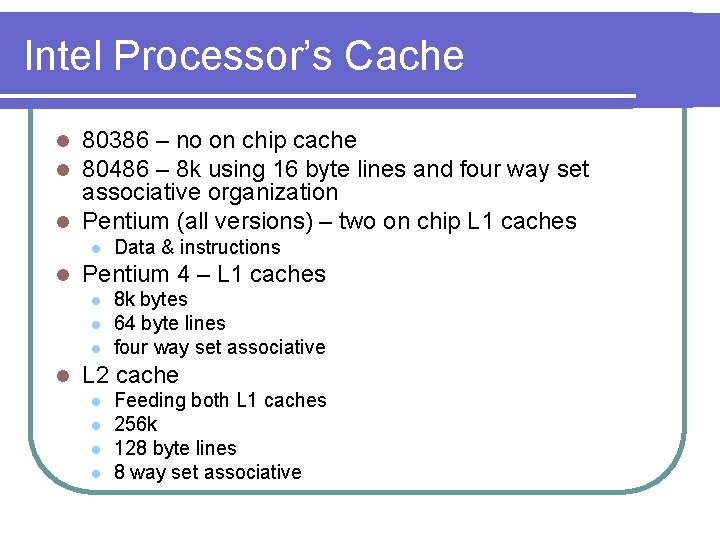

Intel Processor’s Cache 80386 – no on chip cache 80486 – 8 k using 16 byte lines and four way set associative organization l Pentium (all versions) – two on chip L 1 caches l l Pentium 4 – L 1 caches l l Data & instructions 8 k bytes 64 byte lines four way set associative L 2 cache l l Feeding both L 1 caches 256 k 128 byte lines 8 way set associative

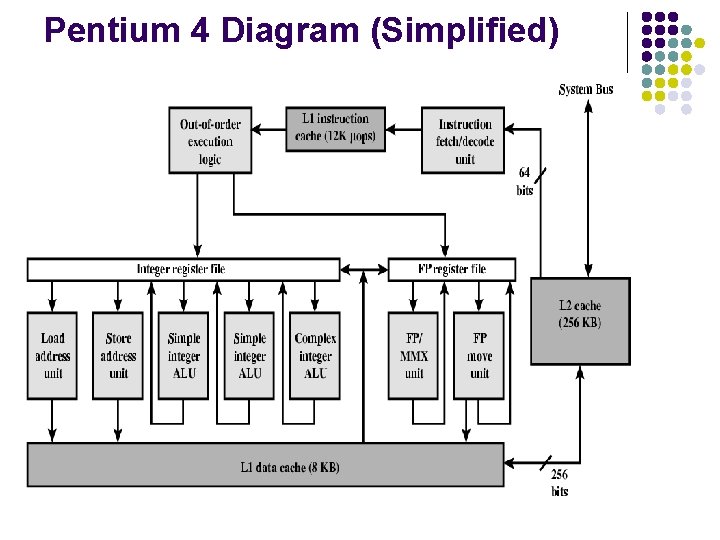

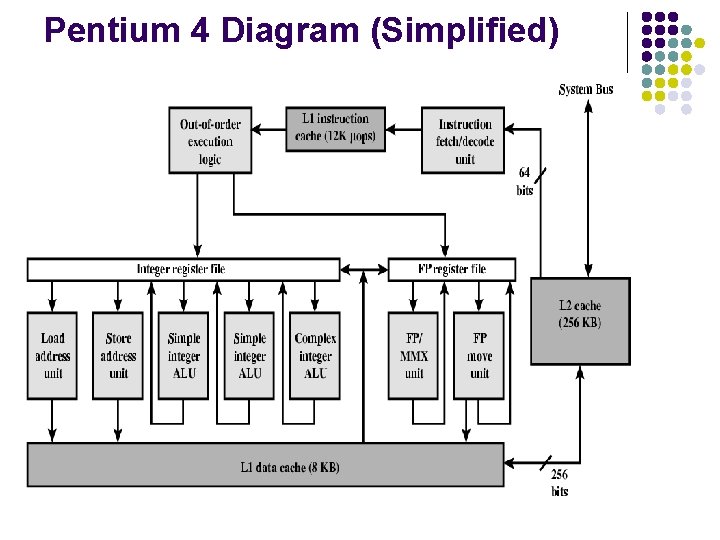

Pentium 4 Diagram (Simplified)

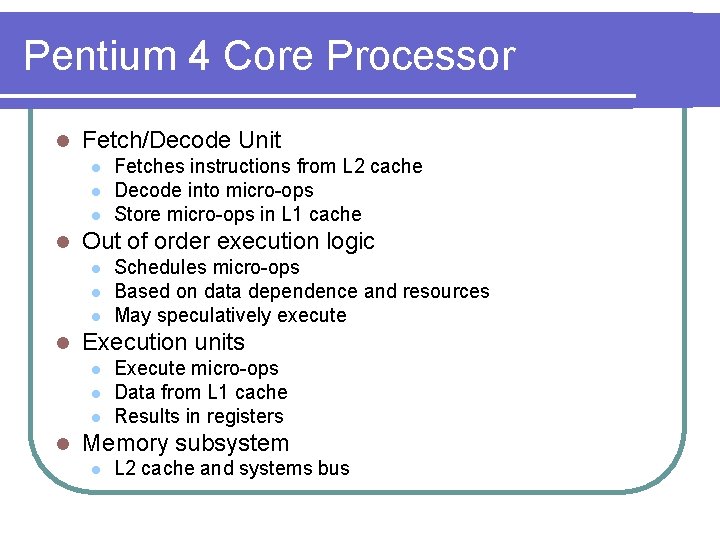

Pentium 4 Core Processor l Fetch/Decode Unit l l Out of order execution logic l l Schedules micro-ops Based on data dependence and resources May speculatively execute Execution units l l Fetches instructions from L 2 cache Decode into micro-ops Store micro-ops in L 1 cache Execute micro-ops Data from L 1 cache Results in registers Memory subsystem l L 2 cache and systems bus

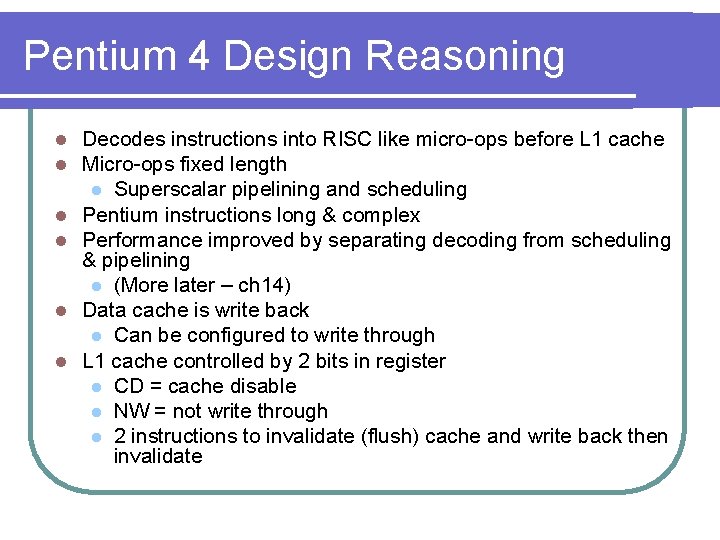

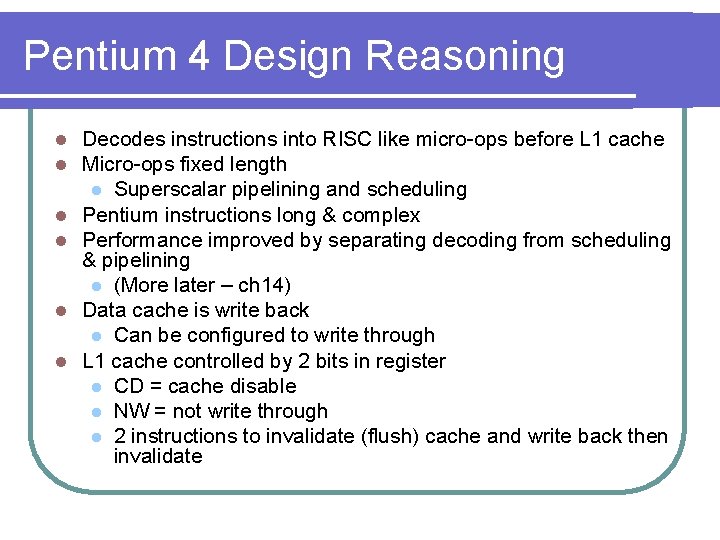

Pentium 4 Design Reasoning l l l Decodes instructions into RISC like micro-ops before L 1 cache Micro-ops fixed length l Superscalar pipelining and scheduling Pentium instructions long & complex Performance improved by separating decoding from scheduling & pipelining l (More later – ch 14) Data cache is write back l Can be configured to write through L 1 cache controlled by 2 bits in register l CD = cache disable l NW = not write through l 2 instructions to invalidate (flush) cache and write back then invalidate