Hardware Accelerator for Combinatorial Optimization Fujian Li Advisor

Hardware Accelerator for Combinatorial Optimization Fujian Li Advisor: Dr. Areibi

Case Study for Implementing Traveling Salesman Problem Key words: * Combinatorial problem * Heuristic method * Local Search * Simulated Annealing algorithm * Traveling Salesman Problem (TSP) * List representation

Combinatorial Problems l Combinatorial problems * Traveling Salesman Problem, Partitioning, . . . l Heuristic method Local Search, Simulated Annealing, Tabu Search, . . . * Not guarantee to find global optimum * Move through search space using local information to guide the move. * Time consuming

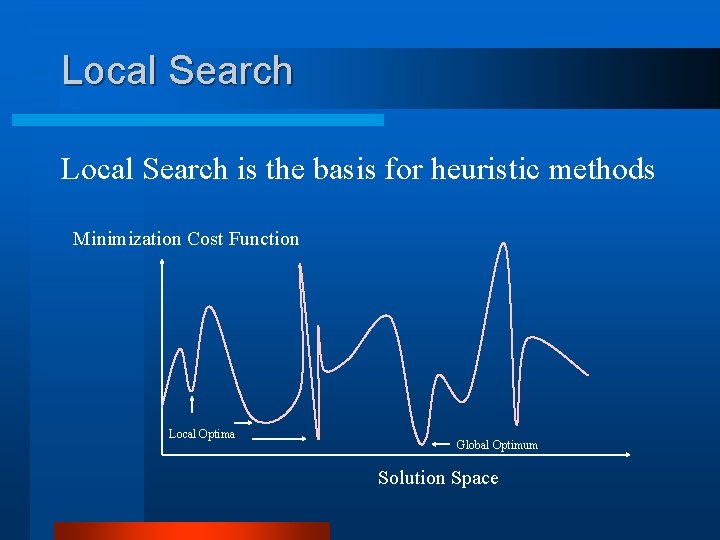

Local Search is the basis for heuristic methods Minimization Cost Function Local Optima Global Optimum Solution Space

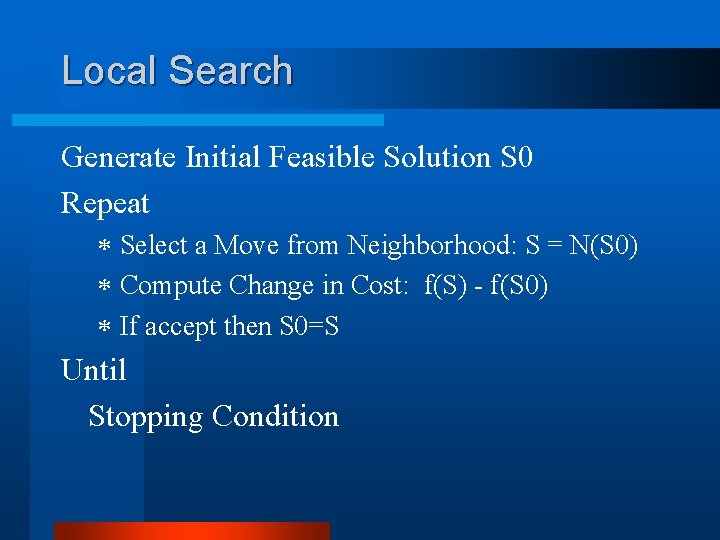

Local Search Generate Initial Feasible Solution S 0 Repeat * Select a Move from Neighborhood: S = N(S 0) * Compute Change in Cost: f(S) - f(S 0) * If accept then S 0=S Until Stopping Condition

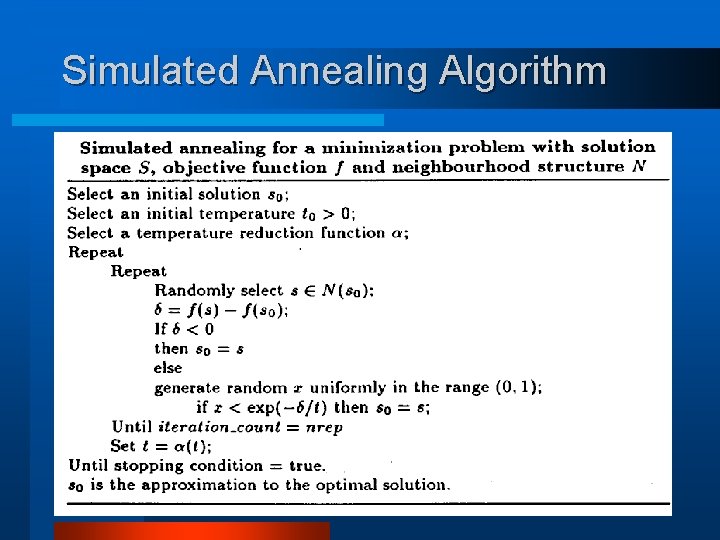

Simulated Annealing Algorithm

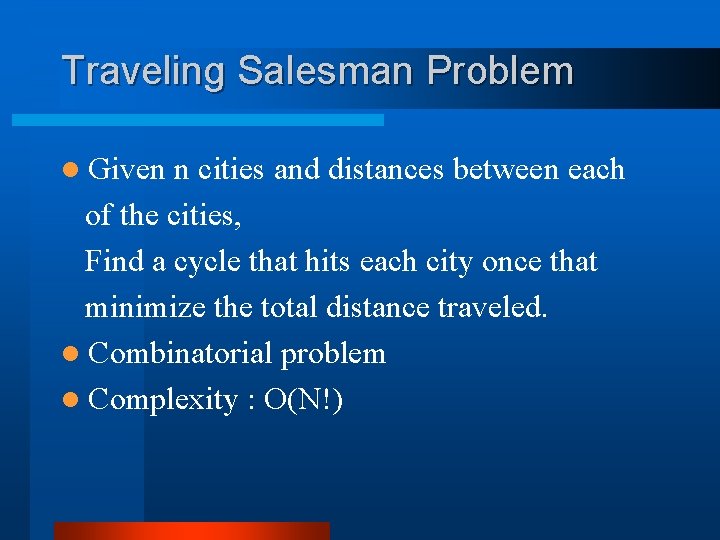

Traveling Salesman Problem l Given n cities and distances between each of the cities, Find a cycle that hits each city once that minimize the total distance traveled. l Combinatorial problem l Complexity : O(N!)

![Traveling Salesman Problem D[Xi, X(i-1)] Xi D[Xi, X(i+1)] X(i-1) X(i+1) X(j-1) D[Xj, X(j+1)] Xj Traveling Salesman Problem D[Xi, X(i-1)] Xi D[Xi, X(i+1)] X(i-1) X(i+1) X(j-1) D[Xj, X(j+1)] Xj](http://slidetodoc.com/presentation_image_h2/50d3623a323a0af8a3e8374aeb8c6fc9/image-8.jpg)

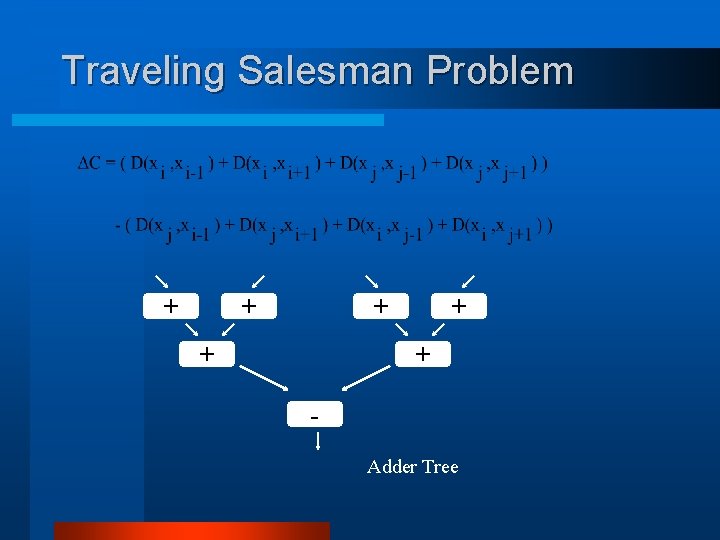

Traveling Salesman Problem D[Xi, X(i-1)] Xi D[Xi, X(i+1)] X(i-1) X(i+1) X(j-1) D[Xj, X(j+1)] Xj D[Xj, X(j-1)] Swap two cities to move through the solution space

Traveling Salesman Problem + + + Adder Tree

Implementation l List data structure is good for heuristic algorithms * Grow and shrink easily * Implement common operations easily • Move An item is moved from one list to the end of another list. • Swap Two items are swapped from the same or different lists. • Reposition The position of an item in a list is changed.

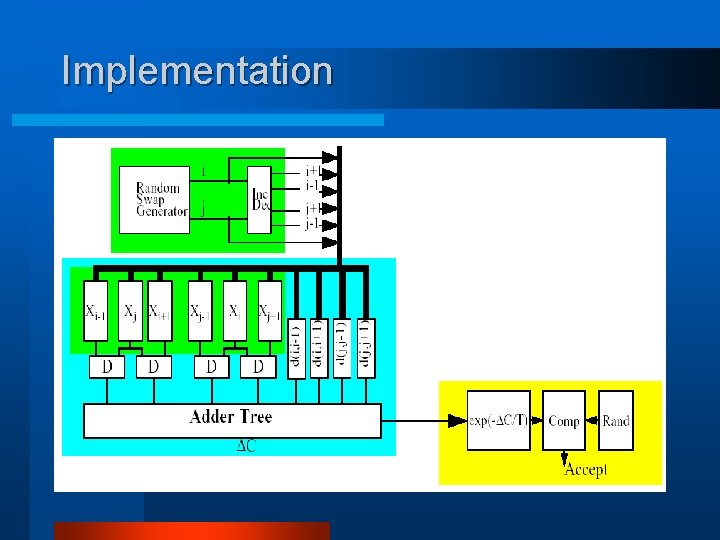

Implementation l Memory for storing solutions l A unit for generating a move l A unit for computing the change in cost l A unit for using Boltzmann equation

Implementation

Implementation l An Aptix Ap 4 reconfigurable logic board * Xilinx XC 4010 FPGAs, memory devices, . . . l FPGA for * A move generator * The adder tree * Update unit * Finite state machine. . .

Implementation l. A lookup table for Boltzmann equation * Exponential computation by FPGA is difficult * Contain the values of Boltzmann equation for different values of * The table is reloaded each time the temperature is changed

Implementation l FPGAs are not suitable for implementing large memories l Memory devices for * The multiple copies of the solution list * Distances

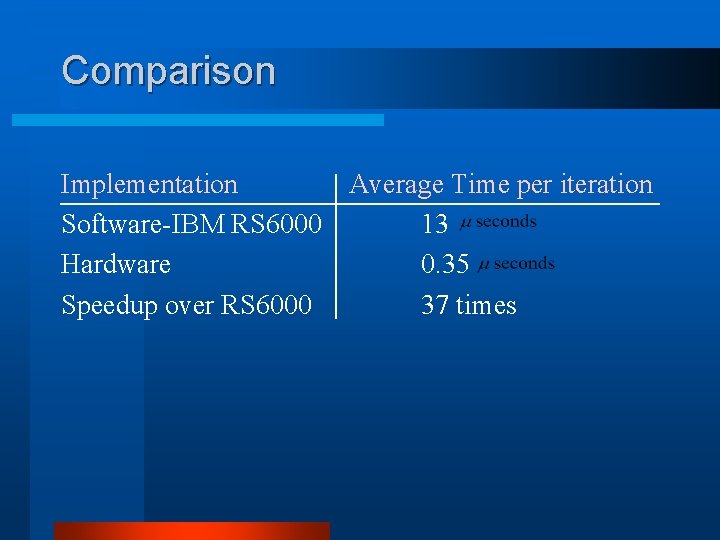

Comparison Implementation Average Time per iteration Software-IBM RS 6000 13 Hardware 0. 35 Speedup over RS 6000 37 times

Future Improvement l Pipeline scheme l Very high speed memory * Block RAM on FPGA l Interconnection on Aptix delay between devices

References 1. David Abramson Application Specific Computers for Combinatorial Optimization 2. David Abramson FPGA Based Custom Computing Machines for Irregular Problems 3. David Abramson A Very High Speed Architecture to Support Simulated Annealing

Thank You & Question?

Application of FPGA l Satisfied density and speed of FPGA l Efficient synthesis tools

- Slides: 20