Digital Design Lecture 7 Combinatorial Logic Combinatorial Logic

Digital Design Lecture 7 Combinatorial Logic

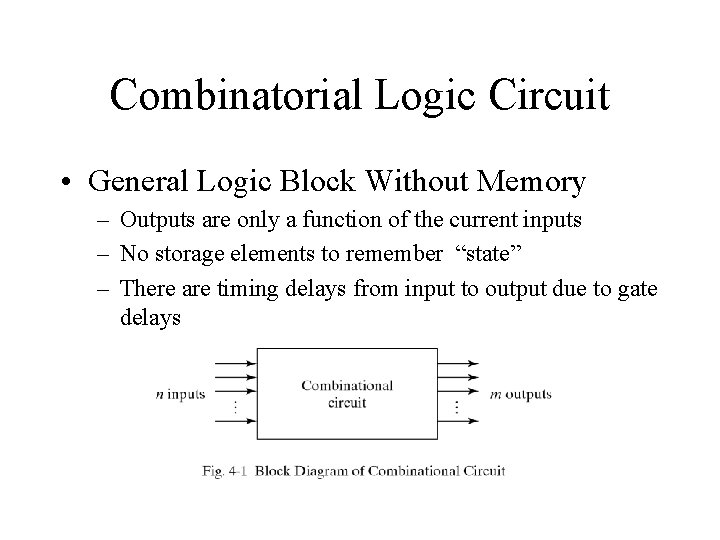

Combinatorial Logic Circuit • General Logic Block Without Memory – Outputs are only a function of the current inputs – No storage elements to remember “state” – There are timing delays from input to output due to gate delays

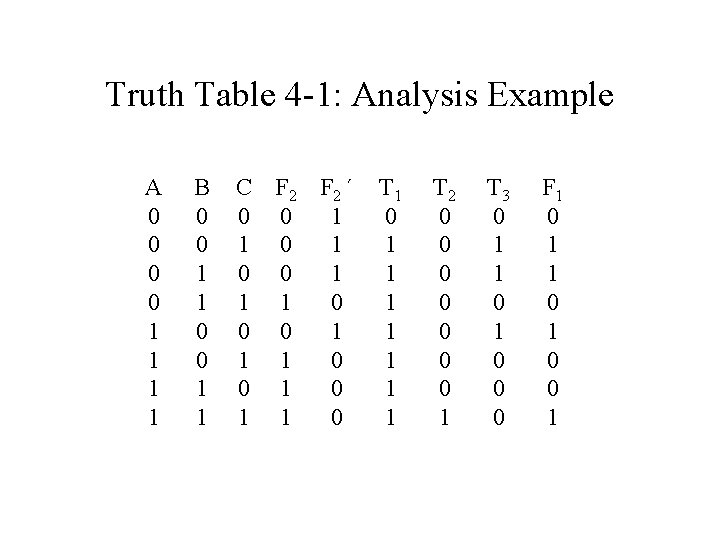

Analysis Example F 2 = AB + AC + BC T 1 = A + B + C T 2 = ABC T 3 = F 2´ T 1 F 1 = T 3 + T 2 Or F 1 = A´BC´ + A´B´C + AB´C´ + ABC

Truth Table 4 -1: Analysis Example A 0 0 1 1 B 0 0 1 1 C F 2 ´ 0 0 1 1 1 0 0 1 0 1 1 0 T 1 0 1 1 1 1 T 2 0 0 0 0 1 T 3 0 1 1 0 0 0 F 1 0 1 0 0 1

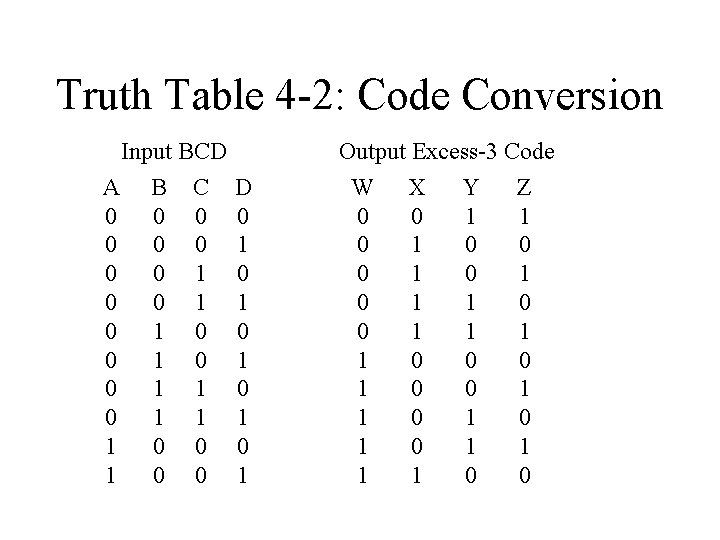

Truth Table 4 -2: Code Conversion Input BCD A B C 0 0 0 0 1 0 0 1 1 1 0 0 D 0 1 0 1 0 1 Output Excess-3 Code W X Y Z 0 0 1 1 0 0 0 1 0 1 1 0 0 0 1 1 0 1 0 1 1 0 0

Code Conversion Karnaugh Maps

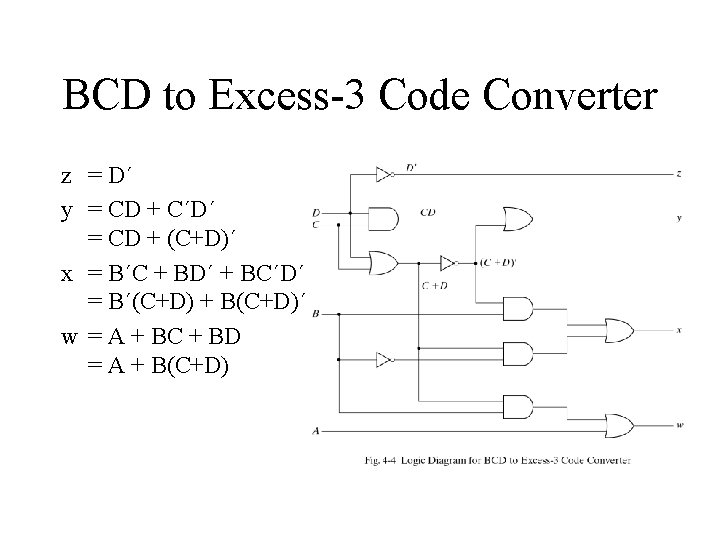

BCD to Excess-3 Code Converter z = D´ y = CD + C´D´ = CD + (C+D)´ x = B´C + BD´ + BC´D´ = B´(C+D) + B(C+D)´ w = A + BC + BD = A + B(C+D)

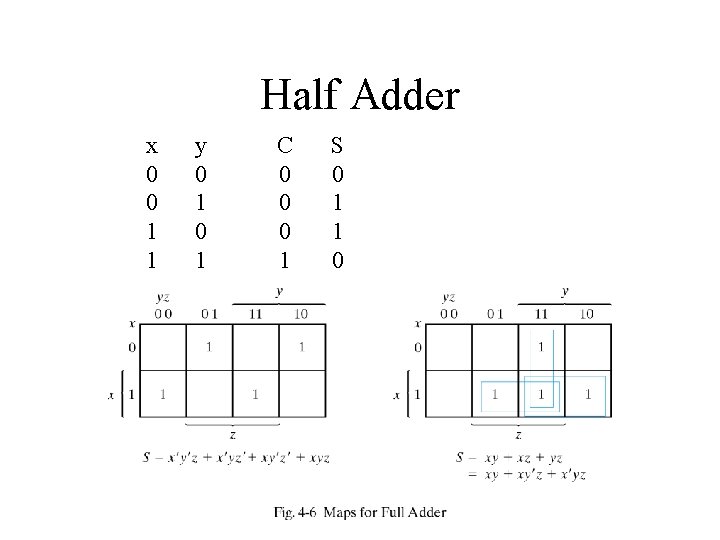

Half Adder x 0 0 1 1 y 0 1 C 0 0 0 1 S 0 1 1 0

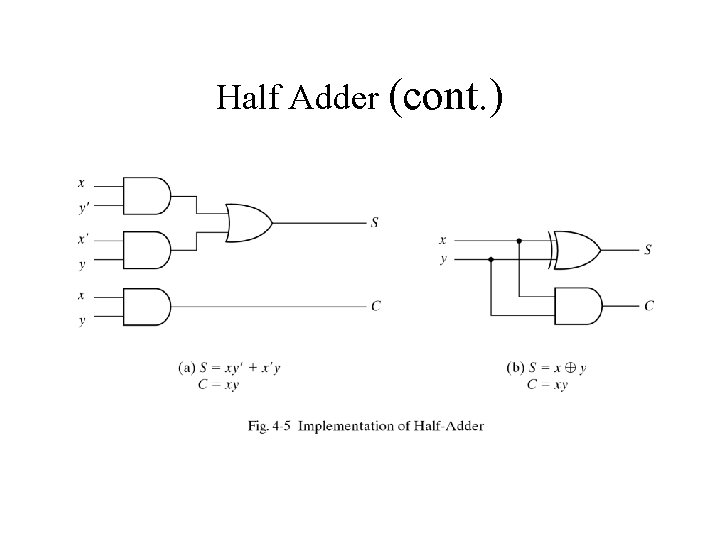

Half Adder (cont. )

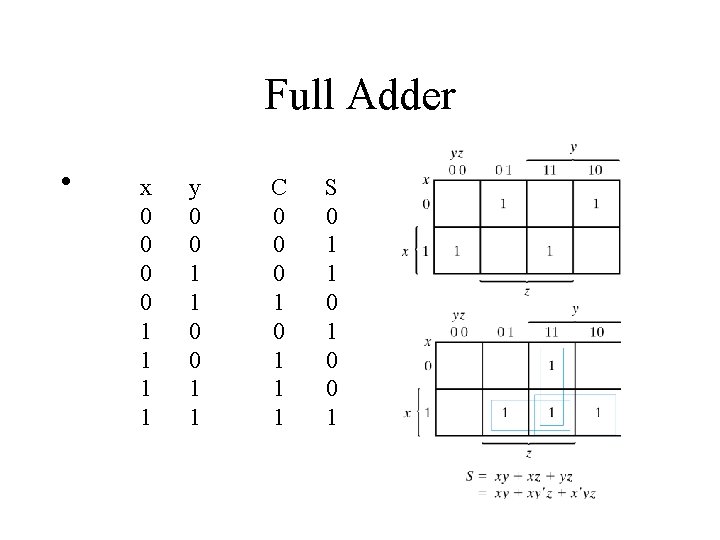

Full Adder • x 0 0 1 1 y 0 0 1 1 C 0 0 0 1 1 1 S 0 1 1 0 0 1

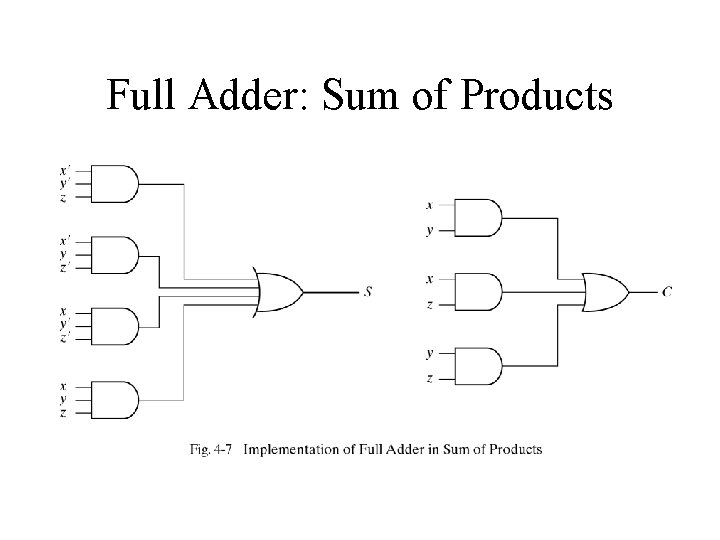

Full Adder: Sum of Products

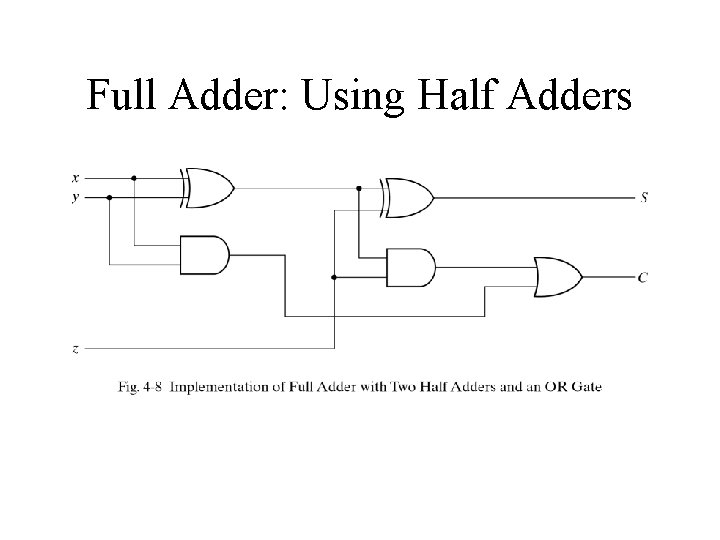

Full Adder: Using Half Adders

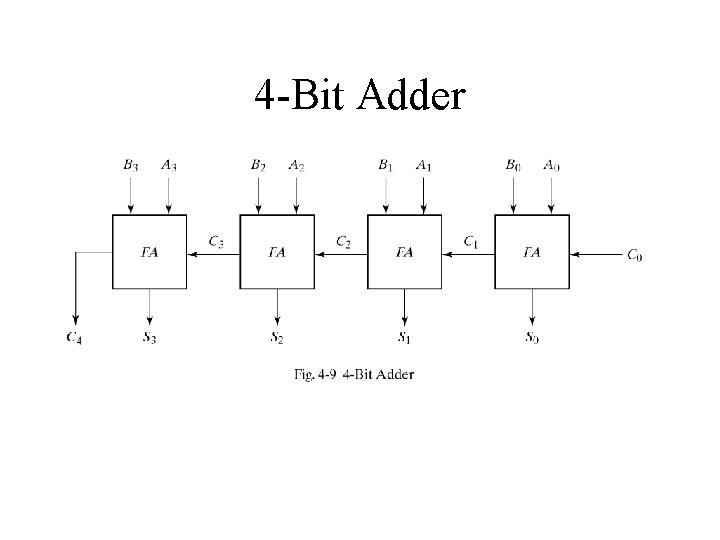

4 -Bit Adder

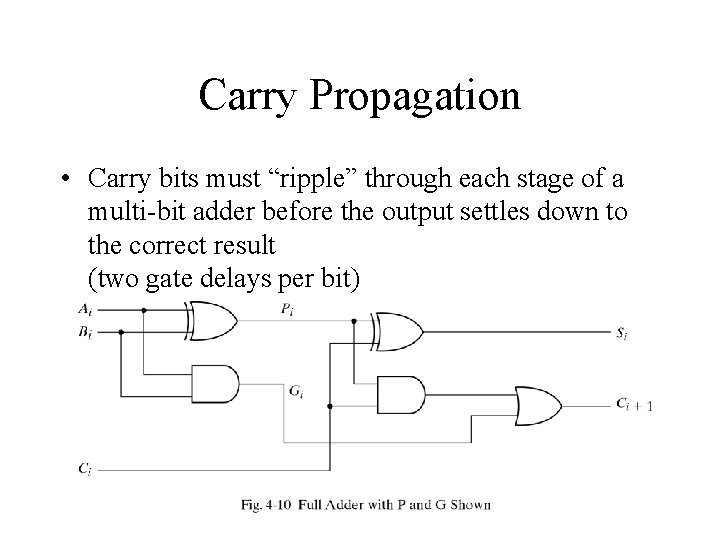

Carry Propagation • Carry bits must “ripple” through each stage of a multi-bit adder before the output settles down to the correct result (two gate delays per bit)

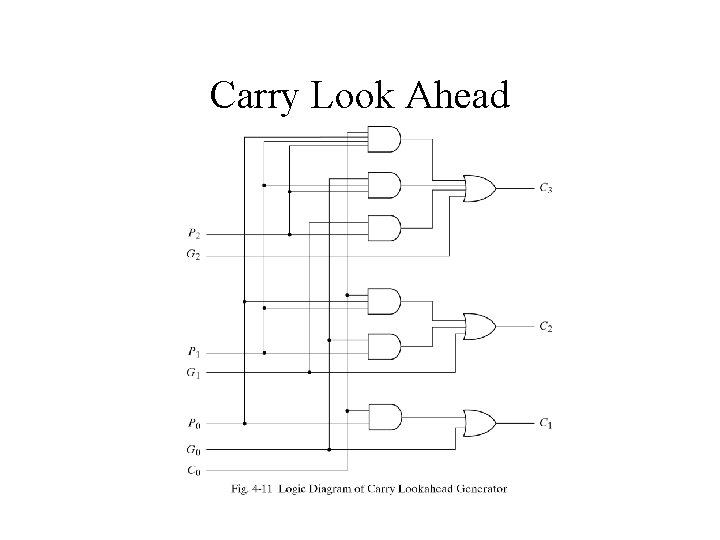

Carry Look Ahead

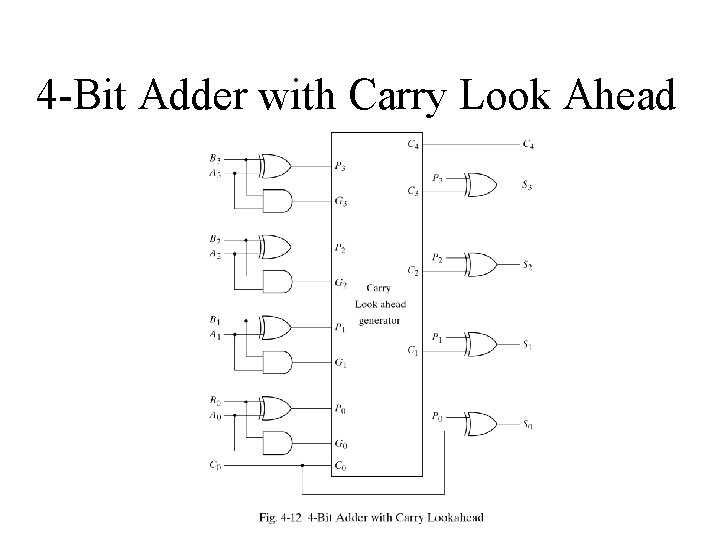

4 -Bit Adder with Carry Look Ahead

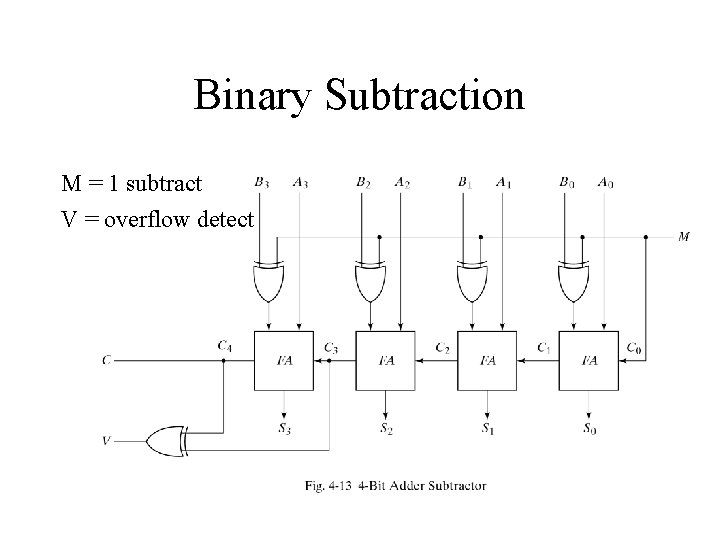

Binary Subtraction M = 1 subtract V = overflow detect

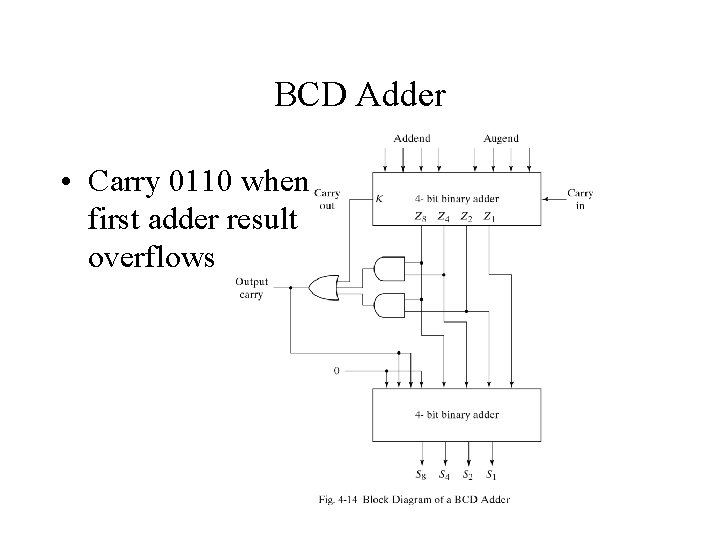

BCD Adder • Carry 0110 when first adder result overflows

- Slides: 18