EET105 Fall 2018 Digital Electronics Charles Rubenstein Ph

EET-105 – Fall 2018 Digital Electronics Charles Rubenstein, Ph. D. Adjunct Professor of Engineering Session 9: MON 10/01/18 /*/ FRI 09/28/18 Mon/Wed: 9: 25 am – 11: 15 am // Wed/Fri: 11: 40 am – 1: 30 pm Lupton Hall 247

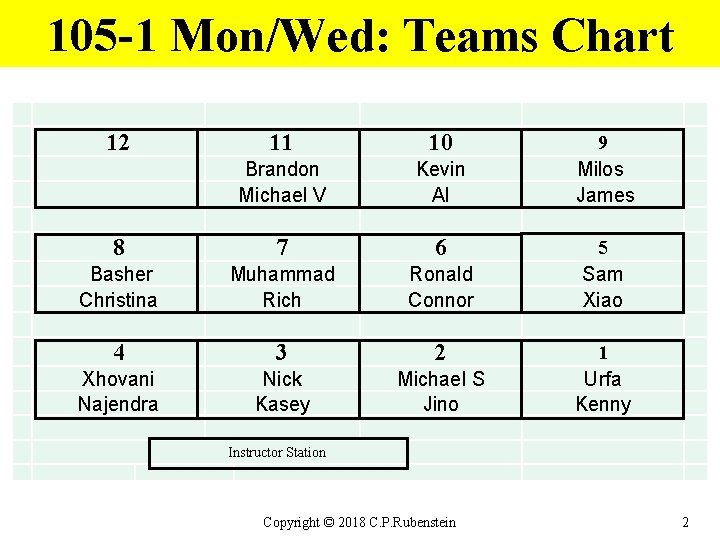

105 -1 Mon/Wed: Teams Chart 12 11 10 Brandon Michael V Kevin Al 8 7 6 Basher Christina Muhammad Rich Ronald Connor 4 3 2 Xhovani Najendra Nick Kasey Michael S Jino 9 Milos James 5 Sam Xiao 1 Urfa Kenny Instructor Station Copyright © 2018 C. P. Rubenstein 2

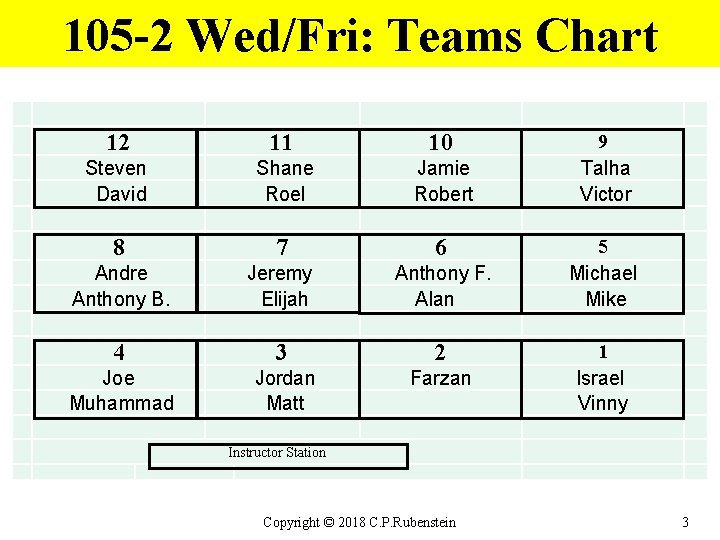

105 -2 Wed/Fri: Teams Chart 12 11 10 Steven David Shane Roel Jamie Robert 8 7 6 Andre Anthony B. Jeremy Elijah Anthony F. Alan 4 3 2 Joe Muhammad Jordan Matt Farzan 9 Talha Victor 5 Michael Mike 1 Israel Vinny Instructor Station Copyright © 2018 C. P. Rubenstein 3

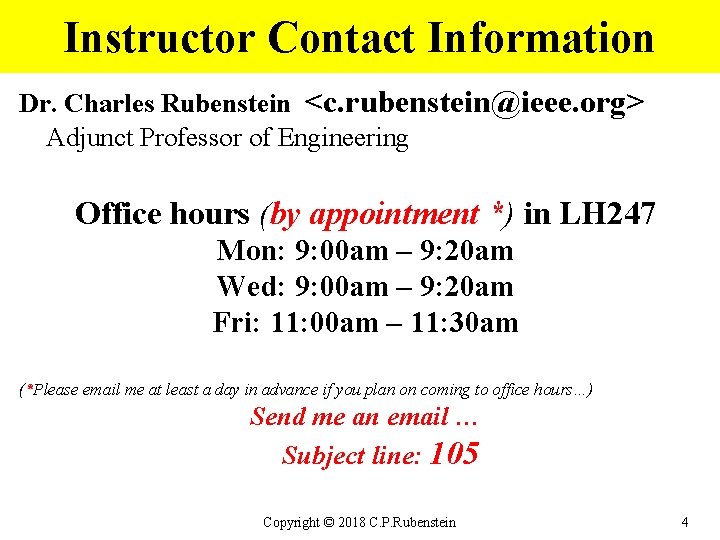

Instructor Contact Information Dr. Charles Rubenstein <c. rubenstein@ieee. org> Adjunct Professor of Engineering Office hours (by appointment *) in LH 247 Mon: 9: 00 am – 9: 20 am Wed: 9: 00 am – 9: 20 am Fri: 11: 00 am – 11: 30 am (*Please email me at least a day in advance if you plan on coming to office hours…) Send me an email … Subject line: 105 Copyright © 2018 C. P. Rubenstein 4

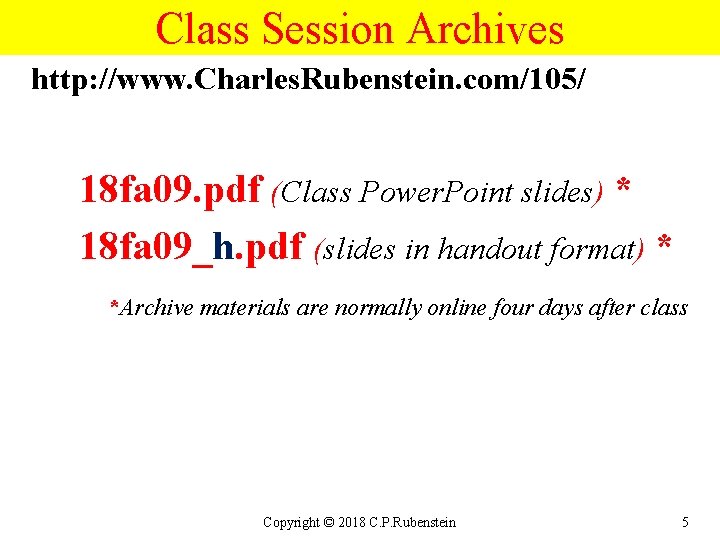

Class Session Archives http: //www. Charles. Rubenstein. com/105/ 18 fa 09. pdf (Class Power. Point slides) * 18 fa 09_h. pdf (slides in handout format) * *Archive materials are normally online four days after class Copyright © 2018 C. P. Rubenstein 5

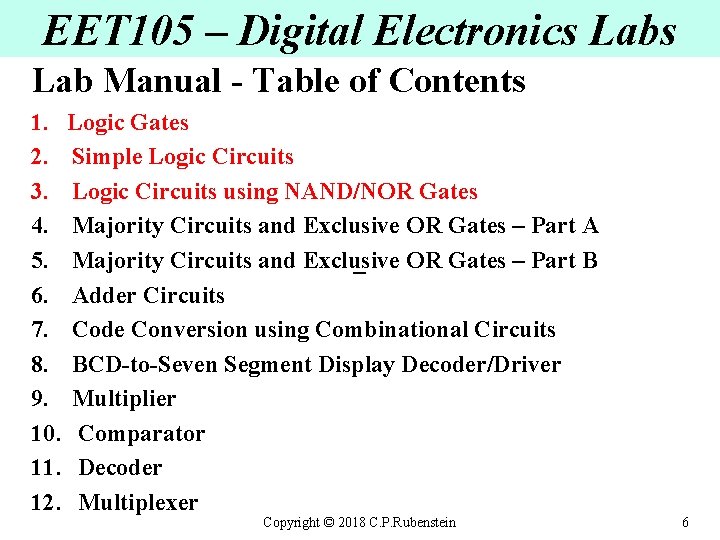

EET 105 – Digital Electronics Lab Manual - Table of Contents 1. Logic Gates 2. Simple Logic Circuits 3. Logic Circuits using NAND/NOR Gates 4. Majority Circuits and Exclusive OR Gates – Part A 5. Majority Circuits and Exclusive OR Gates – Part B – 6. Adder Circuits 7. Code Conversion using Combinational Circuits 8. BCD-to-Seven Segment Display Decoder/Driver 9. Multiplier 10. Comparator 11. Decoder 12. Multiplexer Copyright © 2018 C. P. Rubenstein 6

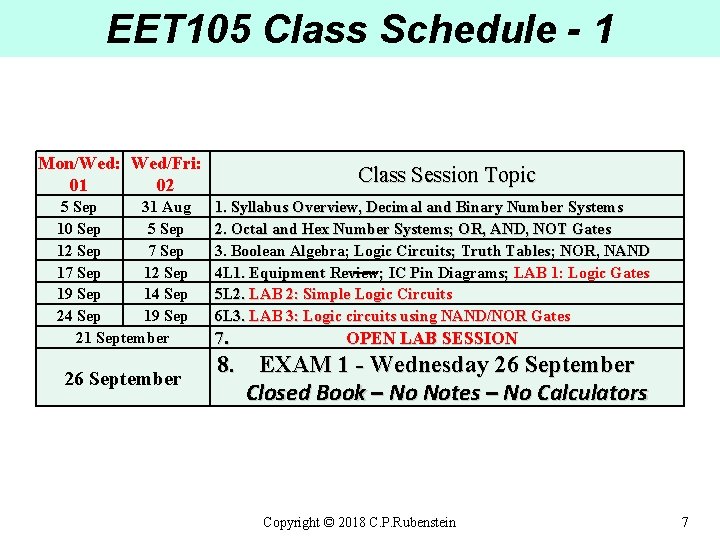

EET 105 Class Schedule - 1 Mon/Wed: Wed/Fri: 01 02 5 Sep 31 Aug 10 Sep 5 Sep 12 Sep 7 Sep 12 Sep 19 Sep 14 Sep 24 Sep 19 Sep 21 September 26 September Class Session Topic 1. Syllabus Overview, Decimal and Binary Number Systems 2. Octal and Hex Number Systems; OR, AND, NOT Gates 3. Boolean Algebra; Logic Circuits; Truth Tables; NOR, NAND 4 L 1. Equipment Review; –– IC Pin Diagrams; LAB 1: Logic Gates 5 L 2. LAB 2: Simple Logic Circuits 6 L 3. LAB 3: Logic circuits using NAND/NOR Gates 7. OPEN LAB SESSION 8. EXAM 1 - Wednesday 26 September Closed Book – No Notes – No Calculators Copyright © 2018 C. P. Rubenstein 7

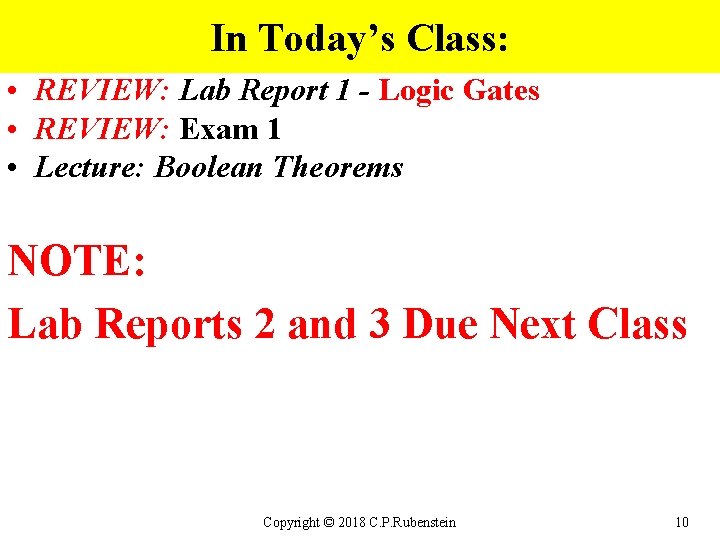

In Today’s Class: • REVIEW: Lab Report 1 - Logic Gates • REVIEW: Exam 1 • Lecture: Boolean Theorems NOTE: Lab Reports 2 and 3 Due Next Class Copyright © 2018 C. P. Rubenstein 10

Questions? Copyright © 2018 C. P. Rubenstein 11

Lab Report Structure Copyright © 2018 C. P. Rubenstein 12

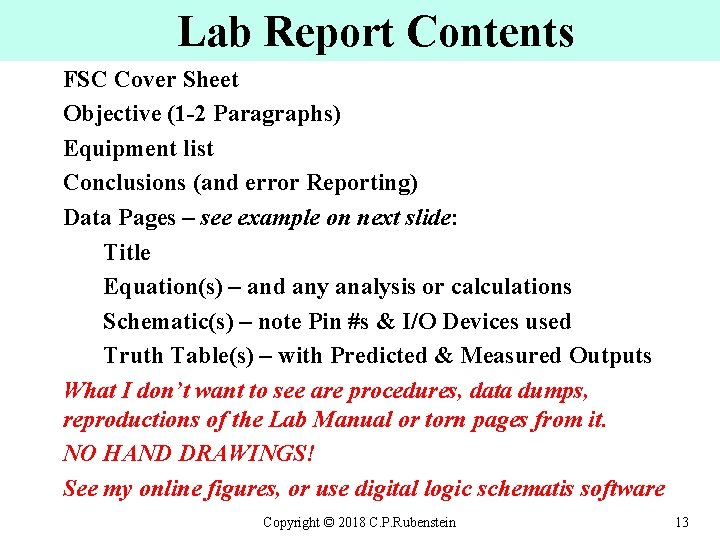

Lab Report Contents FSC Cover Sheet Objective (1 -2 Paragraphs) Equipment list Conclusions (and error Reporting) Data Pages – see example on next slide: Title Equation(s) – and any analysis or calculations Schematic(s) – note Pin #s & I/O Devices used Truth Table(s) – with Predicted & Measured Outputs What I don’t want to see are procedures, data dumps, reproductions of the Lab Manual or torn pages from it. NO HAND DRAWINGS! See my online figures, or use digital logic schematis software Copyright © 2018 C. P. Rubenstein 13

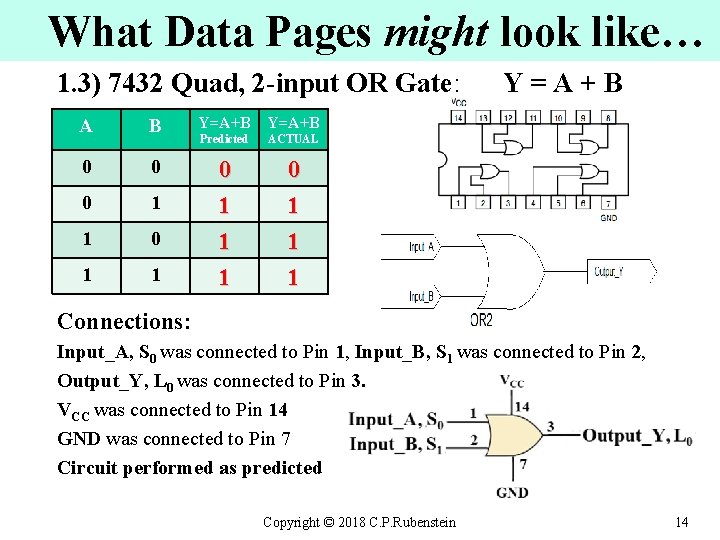

What Data Pages might look like… 1. 3) 7432 Quad, 2 -input OR Gate: A B Y=A+B Predicted ACTUAL 0 0 0 1 1 1 Y=A+B Connections: Input_A, S 0 was connected to Pin 1, Input_B, S 1 was connected to Pin 2, Output_Y, L 0 was connected to Pin 3. VCC was connected to Pin 14 GND was connected to Pin 7 Circuit performed as predicted Copyright © 2018 C. P. Rubenstein 14

Questions? Copyright © 2018 C. P. Rubenstein 15

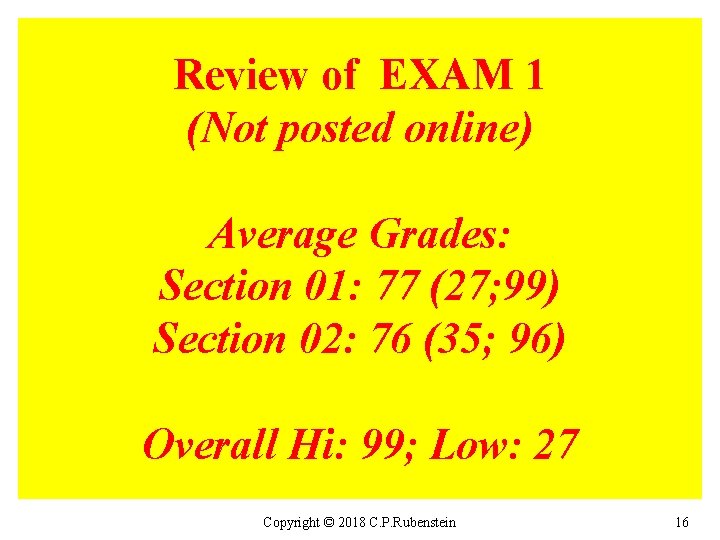

Review of EXAM 1 (Not posted online) Average Grades: Section 01: 77 (27; 99) Section 02: 76 (35; 96) Overall Hi: 99; Low: 27 Copyright © 2018 C. P. Rubenstein 16

Questions? Copyright © 2018 C. P. Rubenstein 17

About Integrated Circuits Copyright © 2018 C. P. Rubenstein 18

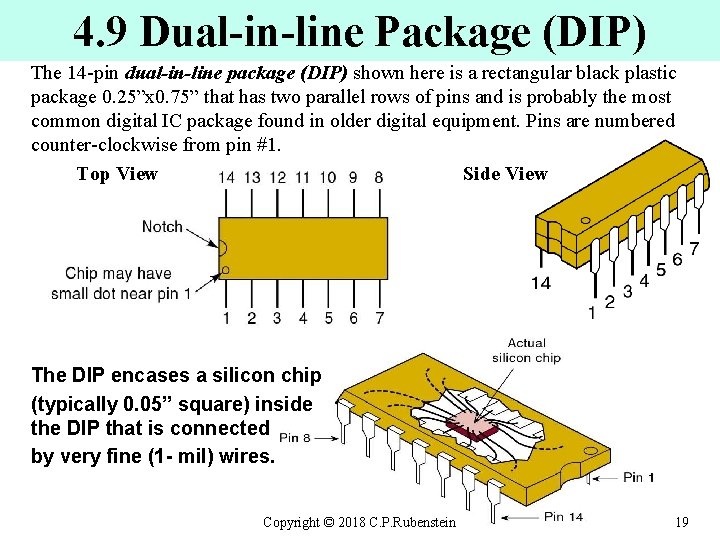

4. 9 Dual-in-line Package (DIP) The 14 -pin dual-in-line package (DIP) shown here is a rectangular black plastic package 0. 25”x 0. 75” that has two parallel rows of pins and is probably the most common digital IC package found in older digital equipment. Pins are numbered counter-clockwise from pin #1. Top View Side View The DIP encases a silicon chip (typically 0. 05” square) inside the DIP that is connected by very fine (1 - mil) wires. Copyright © 2018 C. P. Rubenstein 19

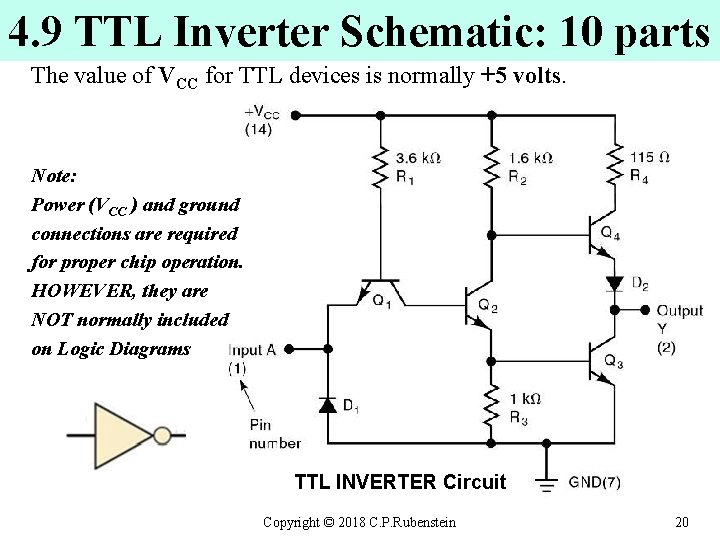

4. 9 TTL Inverter Schematic: 10 parts The value of VCC for TTL devices is normally +5 volts. Note: Power (VCC ) and ground connections are required for proper chip operation. HOWEVER, they are NOT normally included on Logic Diagrams TTL INVERTER Circuit Copyright © 2018 C. P. Rubenstein 20

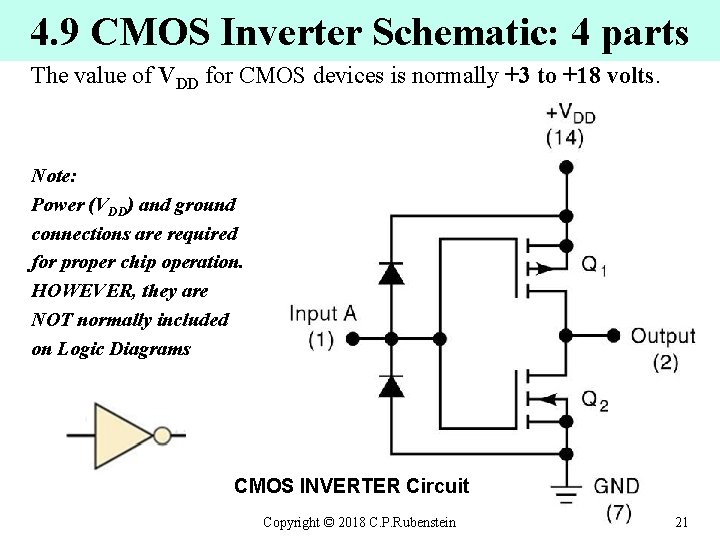

4. 9 CMOS Inverter Schematic: 4 parts The value of VDD for CMOS devices is normally +3 to +18 volts. Note: Power (VDD) and ground connections are required for proper chip operation. HOWEVER, they are NOT normally included on Logic Diagrams CMOS INVERTER Circuit Copyright © 2018 C. P. Rubenstein 21

Chapter 3 Boolean and De. Morgan’s Theorems Equivalent Logic Gates Copyright © 2018 C. P. Rubenstein 22

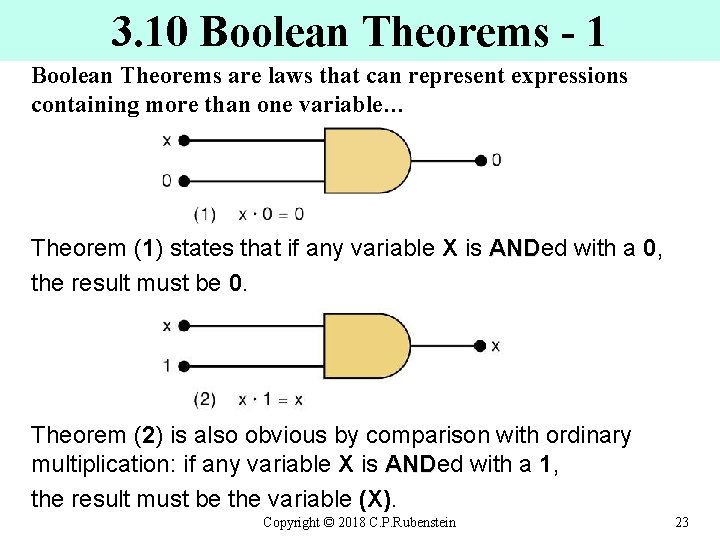

3. 10 Boolean Theorems - 1 Boolean Theorems are laws that can represent expressions containing more than one variable… Theorem (1) states that if any variable X is ANDed AND with a 0, the result must be 0. Theorem (2) is also obvious by comparison with ordinary multiplication: if any variable X is ANDed AND with a 1, the result must be the variable (X). Copyright © 2018 C. P. Rubenstein 23

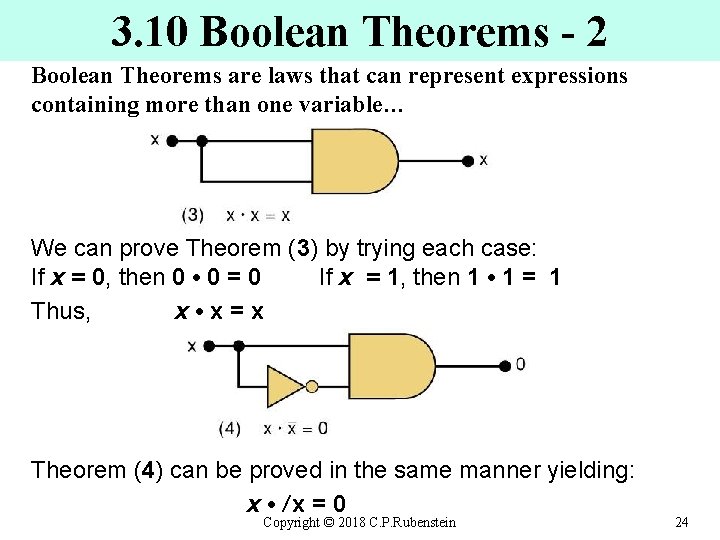

3. 10 Boolean Theorems - 2 Boolean Theorems are laws that can represent expressions containing more than one variable… We can prove Theorem (3) by trying each case: If x = 0, then 0 • 0 = 0 If x = 1, then 1 • 1 = 1 Thus, x • x=x Theorem (4) can be proved in the same manner yielding: x • /x = 0 Copyright © 2018 C. P. Rubenstein 24

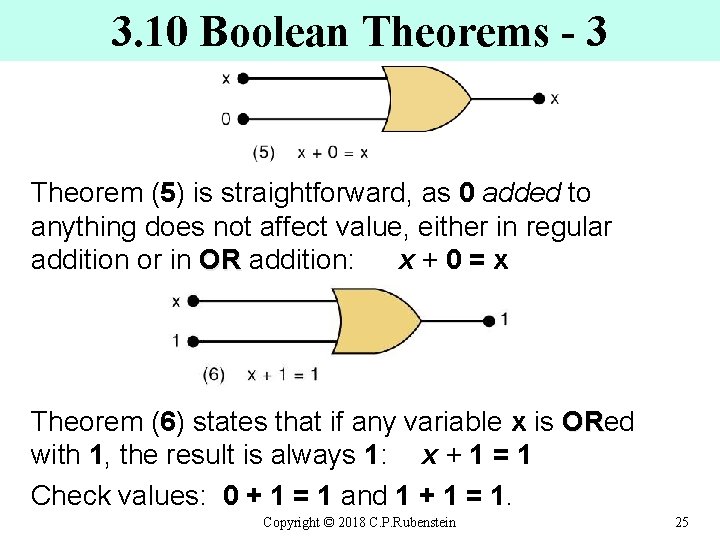

3. 10 Boolean Theorems - 3 Theorem (5) is straightforward, as 0 added to anything does not affect value, either in regular addition or in OR addition: x+0=x Theorem (6) states that if any variable x is ORed OR with 1, the result is always 1: x + 1 = 1 Check values: 0 + 1 = 1 and 1 + 1 = 1. Copyright © 2018 C. P. Rubenstein 25

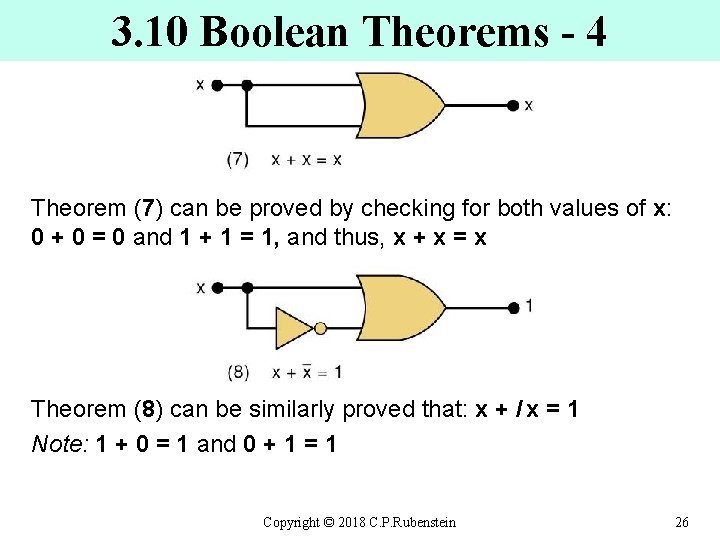

3. 10 Boolean Theorems - 4 Theorem (7) can be proved by checking for both values of x: 0 + 0 = 0 and 1 + 1 = 1, and thus, x + x = x Theorem (8) can be similarly proved that: x + / x = 1 Note: 1 + 0 = 1 and 0 + 1 = 1 Copyright © 2018 C. P. Rubenstein 26

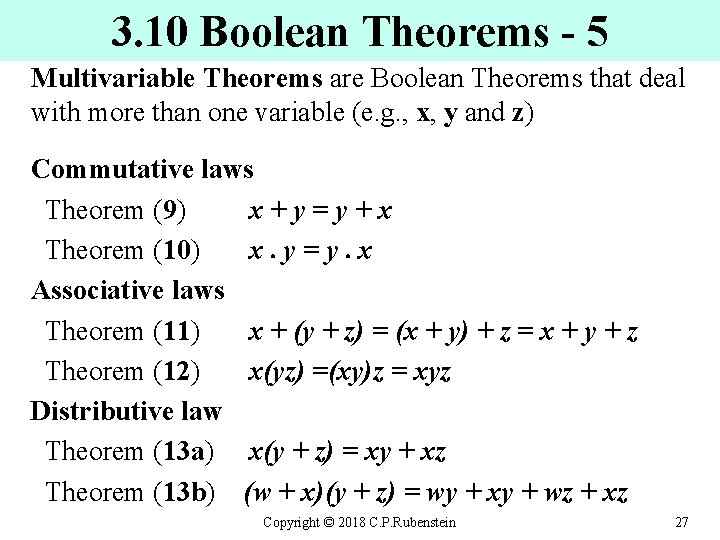

3. 10 Boolean Theorems - 5 Multivariable Theorems are Boolean Theorems that deal with more than one variable (e. g. , x, y and z) Commutative laws Theorem (9) x+y=y+x Theorem (10) x y=y x Associative laws Theorem (11) x + (y + z) = (x + y) + z = x + y + z Theorem (12) x(yz) =(xy)z = xyz Distributive law Theorem (13 a) x(y + z) = xy + xz Theorem (13 b) (w + x)(y + z) = wy + xy + wz + xz ● ● Copyright © 2018 C. P. Rubenstein 27

Any Questions? Send me an email … c. rubenstein@ieee. org Copyright © 2018 C. P. Rubenstein 28

End Copyright © 2018 C. P. Rubenstein 29

- Slides: 27