EET105 Fall 2018 Digital Electronics Charles Rubenstein Ph

EET-105 – Fall 2018 Digital Electronics Charles Rubenstein, Ph. D. Adjunct Professor of Engineering Session 5 Lab 2: WED 09/19/18 /*/ FRI 09/14/18 Mon/Wed: 9: 25 am – 11: 15 am // Wed/Fri: 11: 40 am – 1: 30 pm Lupton Hall 247 1

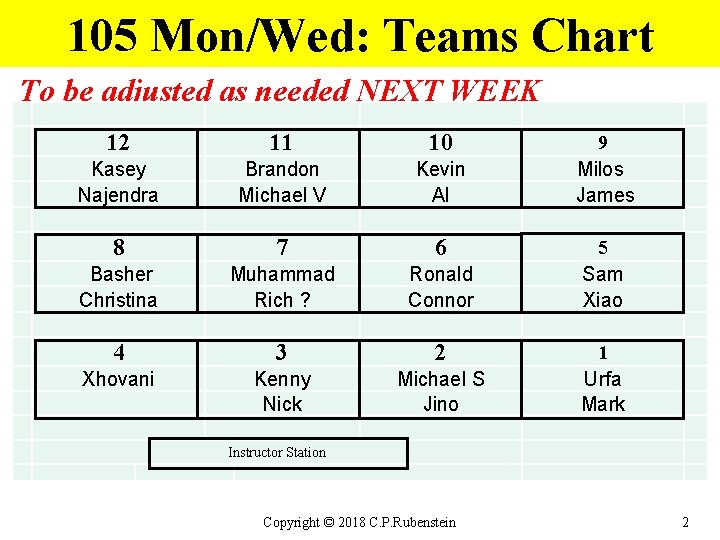

105 Mon/Wed: Teams Chart To be adjusted as needed NEXT WEEK 12 11 10 Kasey Najendra Brandon Michael V Kevin Al 8 7 6 Basher Christina Muhammad Rich ? Ronald Connor 4 3 2 Xhovani Kenny Nick Michael S Jino 9 Milos James 5 Sam Xiao 1 Urfa Mark Instructor Station Copyright © 2018 C. P. Rubenstein 2

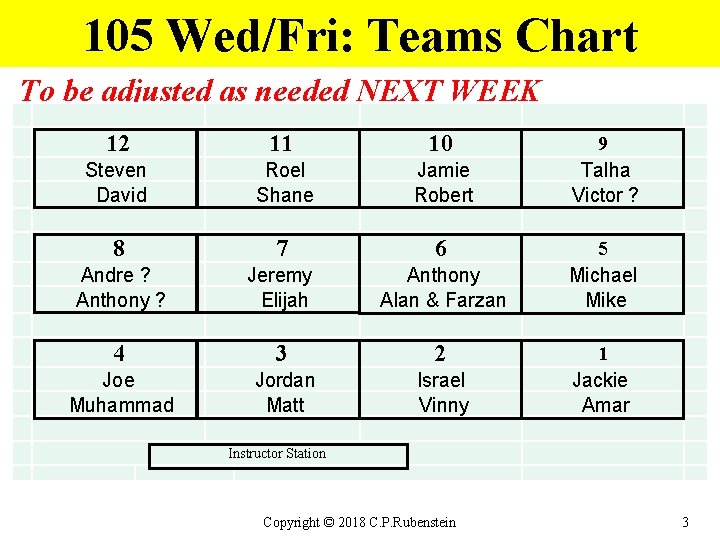

105 Wed/Fri: Teams Chart To be adjusted as needed NEXT WEEK 12 11 10 Steven David Roel Shane Jamie Robert 8 7 6 Andre ? Anthony ? Jeremy Elijah Anthony Alan & Farzan 4 3 2 Joe Muhammad Jordan Matt Israel Vinny 9 Talha Victor ? 5 Michael Mike 1 Jackie Amar Instructor Station Copyright © 2018 C. P. Rubenstein 3

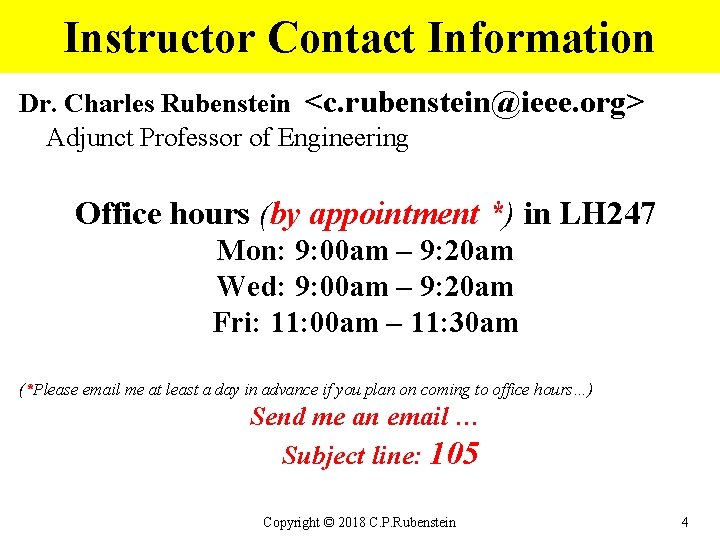

Instructor Contact Information Dr. Charles Rubenstein <c. rubenstein@ieee. org> Adjunct Professor of Engineering Office hours (by appointment *) in LH 247 Mon: 9: 00 am – 9: 20 am Wed: 9: 00 am – 9: 20 am Fri: 11: 00 am – 11: 30 am (*Please email me at least a day in advance if you plan on coming to office hours…) Send me an email … Subject line: 105 Copyright © 2018 C. P. Rubenstein 4

** World Maker Faire – NY ** For the seventh year, Dr. Rubenstein will be coordinating the IEEE (Sponsored by Region 1, IEEE-USA, EAB and The IET) at the Booth World Maker Faire New York NY Hall of Science - Queens, NY Saturday-Sunday 22 -23 September 2018 Copyright © 2018 C. P. Rubenstein 5

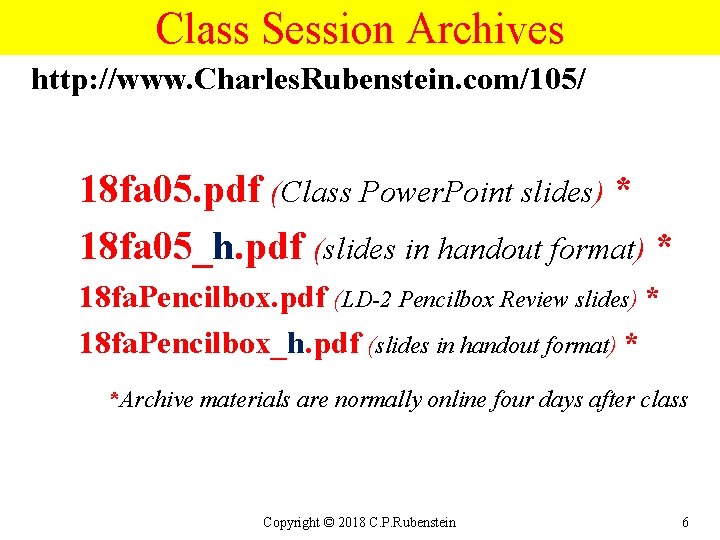

Class Session Archives http: //www. Charles. Rubenstein. com/105/ 18 fa 05. pdf (Class Power. Point slides) * 18 fa 05_h. pdf (slides in handout format) * 18 fa. Pencilbox. pdf (LD-2 Pencilbox Review slides) * 18 fa. Pencilbox_h. pdf (slides in handout format) * *Archive materials are normally online four days after class Copyright © 2018 C. P. Rubenstein 6

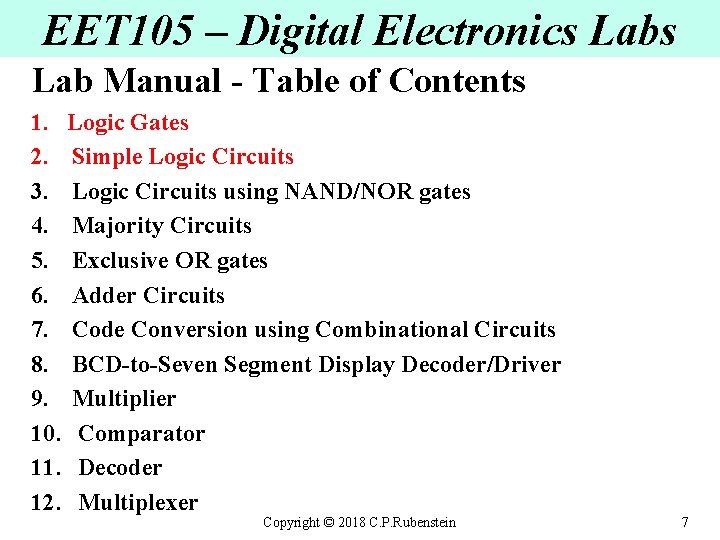

EET 105 – Digital Electronics Lab Manual - Table of Contents 1. Logic Gates 2. Simple Logic Circuits 3. Logic Circuits using NAND/NOR gates 4. Majority Circuits 5. Exclusive OR gates 6. Adder Circuits 7. Code Conversion using Combinational Circuits 8. BCD-to-Seven Segment Display Decoder/Driver 9. Multiplier 10. Comparator 11. Decoder 12. Multiplexer Copyright © 2018 C. P. Rubenstein 7

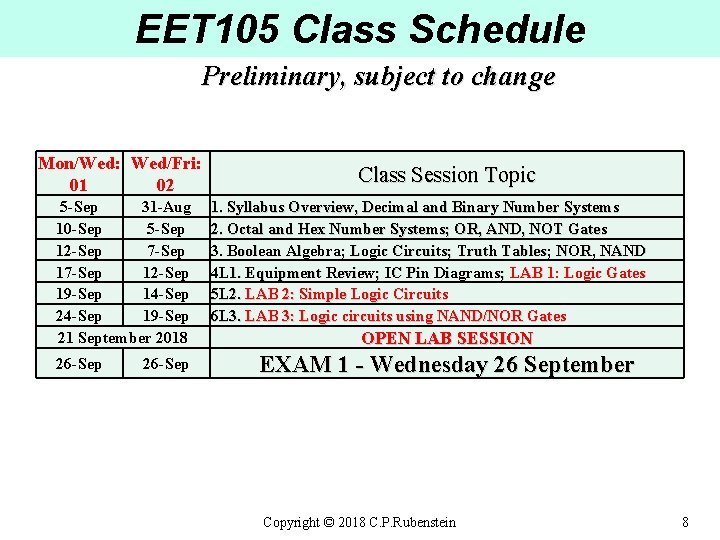

EET 105 Class Schedule Preliminary, subject to change Mon/Wed: Wed/Fri: 01 02 5 -Sep 31 -Aug 10 -Sep 5 -Sep 12 -Sep 7 -Sep 12 -Sep 19 -Sep 14 -Sep 24 -Sep 19 -Sep 21 September 2018 26 -Sep Class Session Topic 1. Syllabus Overview, Decimal and Binary Number Systems 2. Octal and Hex Number Systems; OR, AND, NOT Gates 3. Boolean Algebra; Logic Circuits; Truth Tables; NOR, NAND 4 L 1. Equipment Review; IC Pin Diagrams; LAB 1: Logic Gates 5 L 2. LAB 2: Simple Logic Circuits 6 L 3. LAB 3: Logic circuits using NAND/NOR Gates OPEN LAB SESSION EXAM 1 - Wednesday 26 September Copyright © 2018 C. P. Rubenstein 8

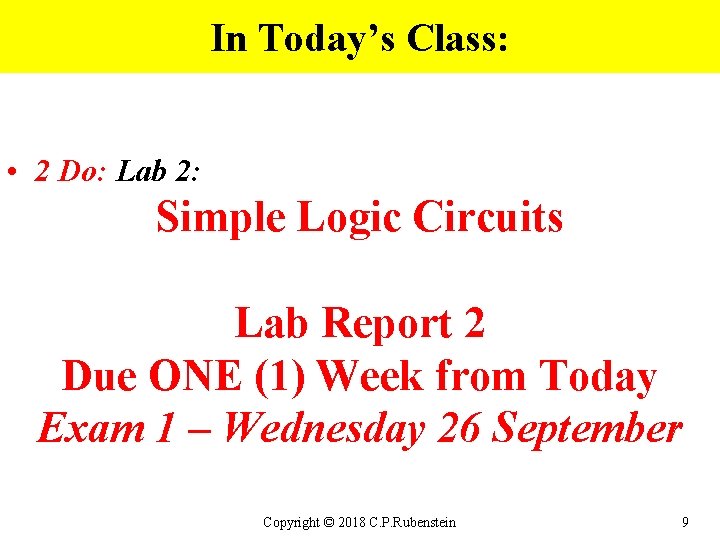

In Today’s Class: • 2 Do: Lab 2: Simple Logic Circuits Lab Report 2 Due ONE (1) Week from Today Exam 1 – Wednesday 26 September Copyright © 2018 C. P. Rubenstein 9

Questions? Copyright © 2018 C. P. Rubenstein 10

EET 105 Digital Electronics Lab 2 Simple Logic Circuits Copyright © 2018 C. P. Rubenstein 11

EET 105 Digital Electronics Lab 2 Simple Logic Circuits Copyright © 2018 C. P. Rubenstein 12

Lab 2 – Simple Logic Circuits Objective: To familiarize the student with the setup of simple logic circuits and verify the logic they perform. To allow students to learn simple Boolean theorems. Equipment: The ‘Pencilbox’ Digital Trainer, and several Ics. Procedure: 2. 1: BEFORE coming to the Lab. . You should have predicted the result of the Figure 1 logic circuit and verify the result by using the digital trainer. Copyright © 2018 C. P. Rubenstein 13

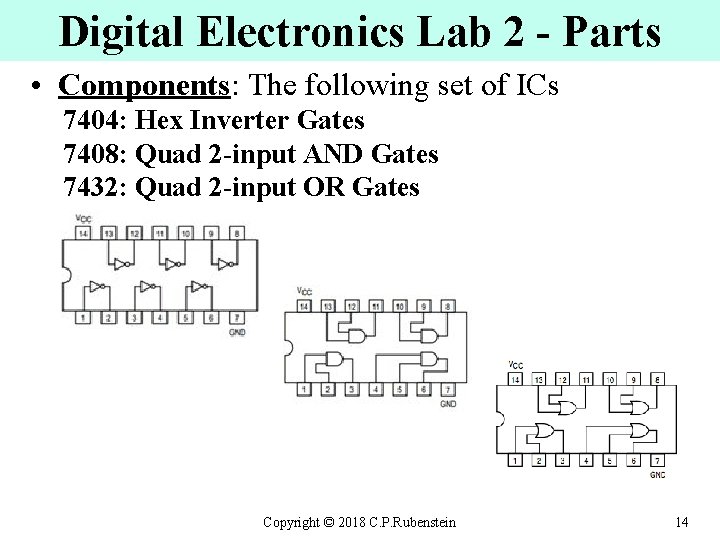

Digital Electronics Lab 2 - Parts • Components: The following set of ICs 7404: Hex Inverter Gates 7408: Quad 2 -input AND Gates 7432: Quad 2 -input OR Gates Copyright © 2018 C. P. Rubenstein 14

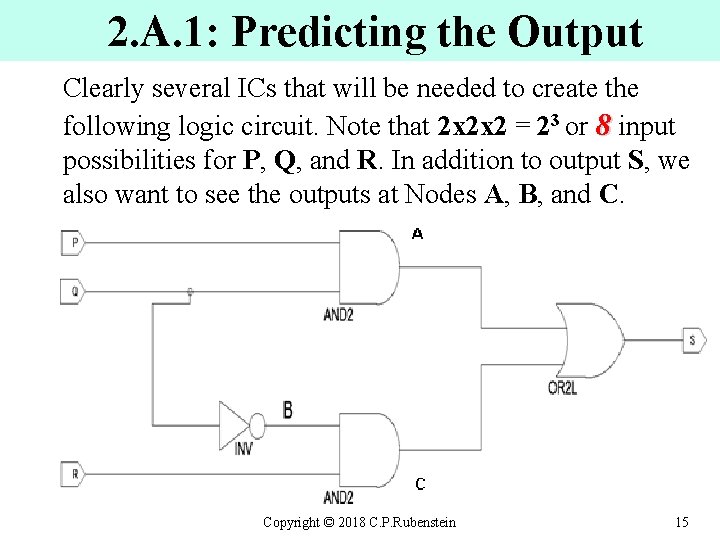

2. A. 1: Predicting the Output Clearly several ICs that will be needed to create the following logic circuit. Note that 2 x 2 x 2 = 23 or 8 input possibilities for P, Q, and R. In addition to output S, we also want to see the outputs at Nodes A, B, and C. Copyright © 2018 C. P. Rubenstein 15

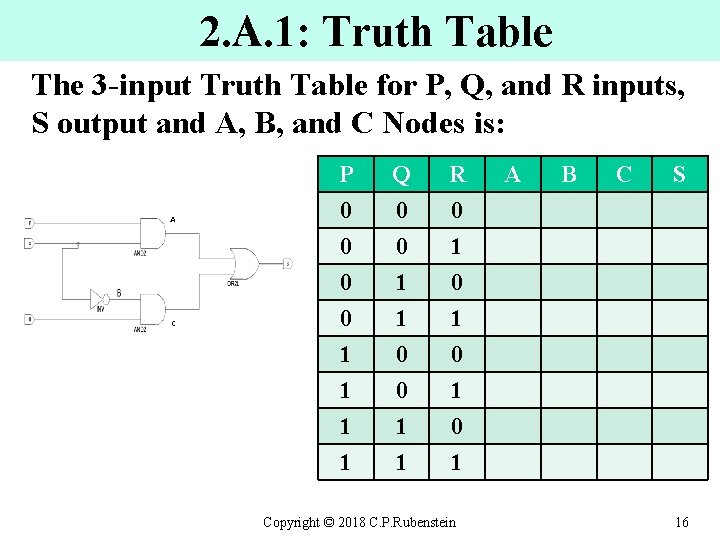

2. A. 1: Truth Table The 3 -input Truth Table for P, Q, and R inputs, S output and A, B, and C Nodes is: P 0 0 0 Q 0 0 1 R 0 1 0 0 1 1 1 0 1 Copyright © 2018 C. P. Rubenstein A B C S 16

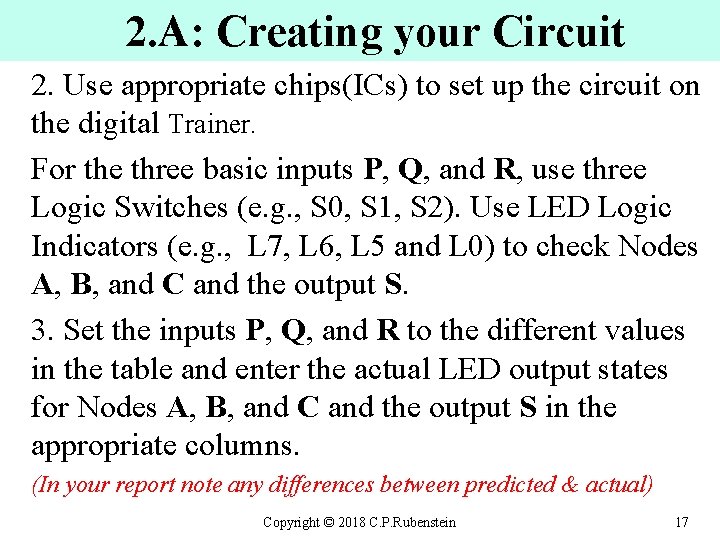

2. A: Creating your Circuit 2. Use appropriate chips(ICs) to set up the circuit on the digital Trainer. For the three basic inputs P, Q, and R, use three Logic Switches (e. g. , S 0, S 1, S 2). Use LED Logic Indicators (e. g. , L 7, L 6, L 5 and L 0) to check Nodes A, B, and C and the output S. 3. Set the inputs P, Q, and R to the different values in the table and enter the actual LED output states for Nodes A, B, and C and the output S in the appropriate columns. (In your report note any differences between predicted & actual) Copyright © 2018 C. P. Rubenstein 17

2. B: Drawing Logic Circuits NOTE: Whenever we work with integrated circuits we MUST remember that they need Vcc and ground power supply connections to function properly. HOWEVER – we typically do NOT note the power connections on the logic diagrams – they are presumed! Copyright © 2018 C. P. Rubenstein 18

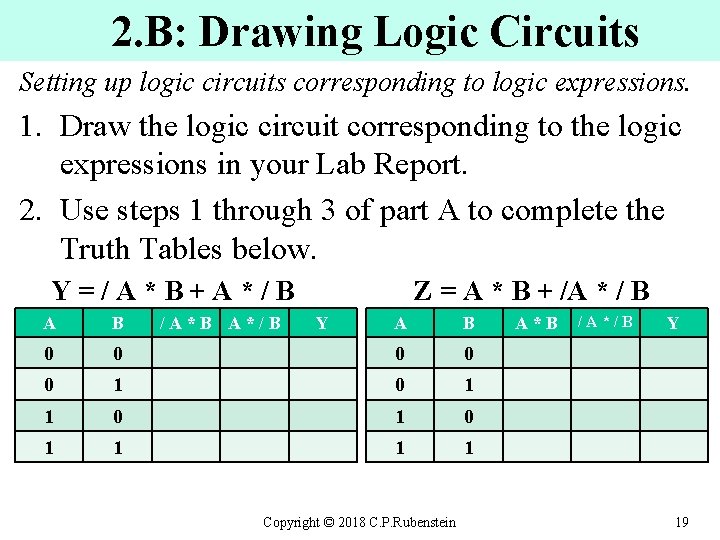

2. B: Drawing Logic Circuits Setting up logic circuits corresponding to logic expressions. 1. Draw the logic circuit corresponding to the logic expressions in your Lab Report. 2. Use steps 1 through 3 of part A to complete the Truth Tables below. Y=/A*B+A*/B A B 0 /A*B A*/B Z = A * B + /A * / B Y A B 0 0 1 0 1 0 1 1 Copyright © 2018 C. P. Rubenstein A*B /A*/B Y 19

Any Questions? Send me an email … c. rubenstein@ieee. org Copyright © 2018 C. P. Rubenstein 20

End Copyright © 2018 C. P. Rubenstein 21

- Slides: 21