ECE 551 Digital System Design Synthesis Lecture Set

- Slides: 27

ECE 551: Digital System Design & Synthesis Lecture Set 12 12. 1: Introduction to VHDL (Separate File) 12. 2: VHDL versus Verilog 05/05/2003 1

ECE 551 - Digital System Design & Synthesis Lecture 12. 2 - VHDL versus Verilog Overview q Background q Comparison Space § Capability § Compilation § Data Types § Design Reuse § Ease of Learning § Error- Checking § Forward and Backward Annotation 05/05/2003 2

ECE 551 - Digital System Design & Synthesis Lecture 12. 2 - VHDL versus Verilog Overview q Comparison § § § § Space (Continued) High-Level Constructs Language Extensions Libraries Low-Level Constructs Managing Large Designs Operators Parameterized Models 05/05/2003 3

ECE 551 - Digital System Design & Synthesis Lecture 12. 2 - VHDL versus Verilog Overview Comparison Space (Continued) § § § Procedures and Tasks Readability Structural Replication Testbenches Verboseness q Comparison Summary q Algorithmic and RTL Level Examples 05/05/2003 4

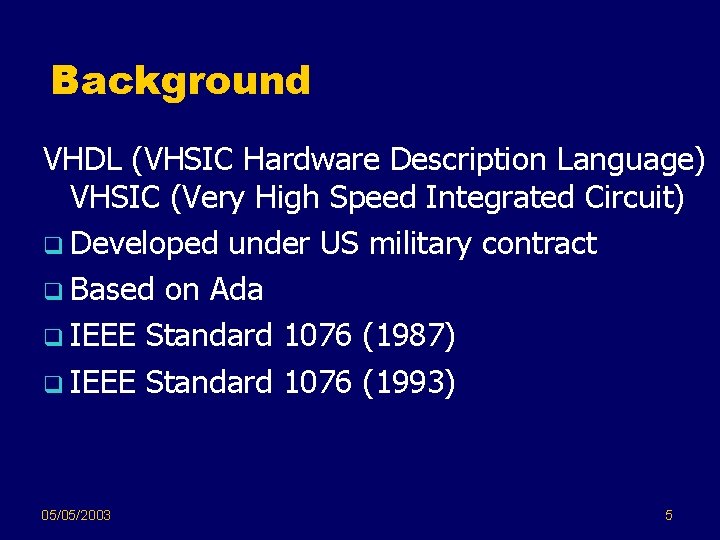

Background VHDL (VHSIC Hardware Description Language) VHSIC (Very High Speed Integrated Circuit) q Developed under US military contract q Based on Ada q IEEE Standard 1076 (1987) q IEEE Standard 1076 (1993) 05/05/2003 5

Background Verilog q Developed by Gateway Design Automation in 1983 q Based on C and Ada q Originally an interpretive language q Gateway bought by Cadence in 1989 q Put in public domain in 1990 q IEEE Standard 1364 -1995 q IEEE Standard 1364 -2001 05/05/2003 6

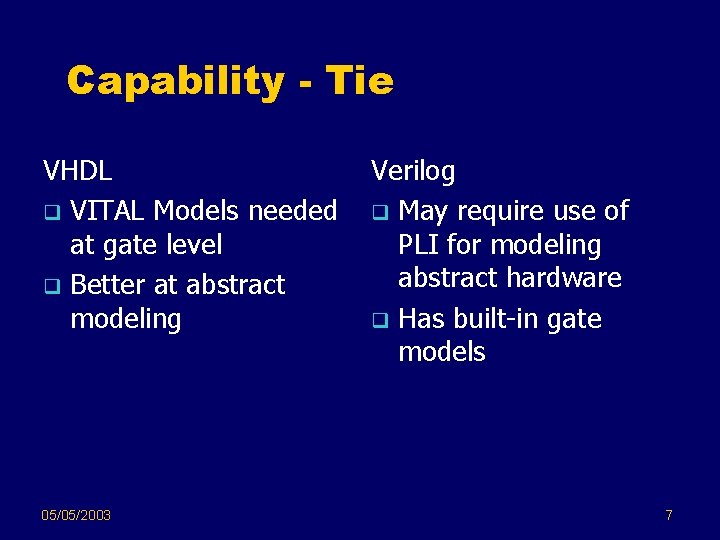

Capability - Tie VHDL q VITAL Models needed at gate level q Better at abstract modeling 05/05/2003 Verilog q May require use of PLI for modeling abstract hardware q Has built-in gate models 7

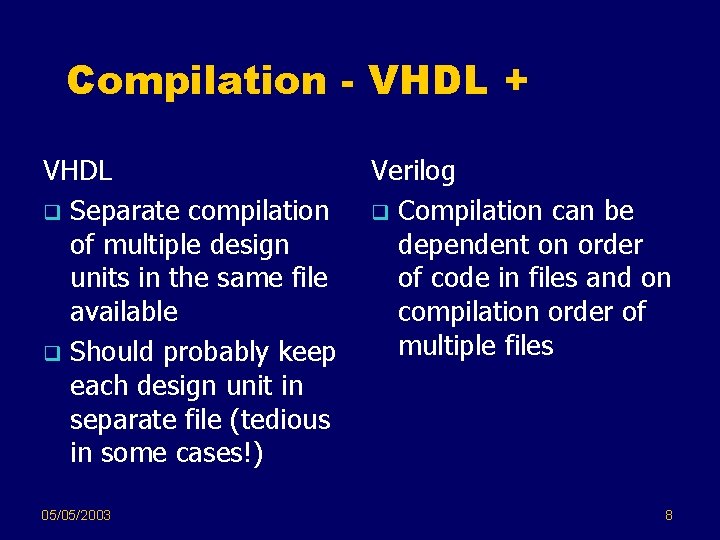

Compilation - VHDL + VHDL q Separate compilation of multiple design units in the same file available q Should probably keep each design unit in separate file (tedious in some cases!) 05/05/2003 Verilog q Compilation can be dependent on order of code in files and on compilation order of multiple files 8

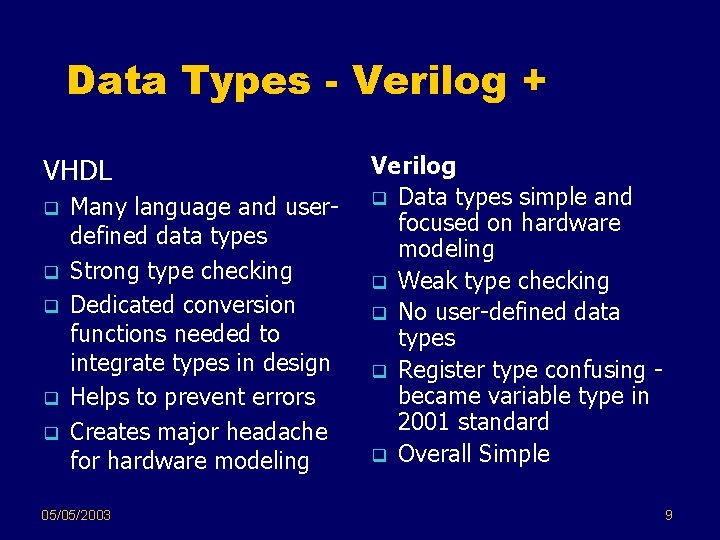

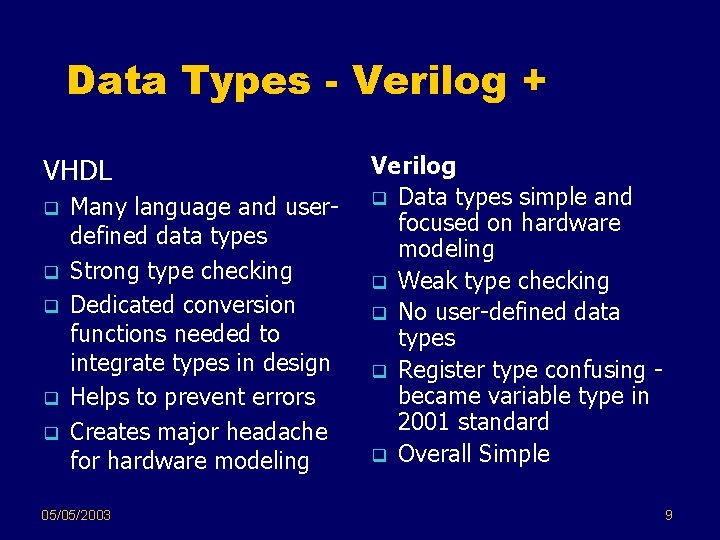

Data Types - Verilog + VHDL q q q Many language and userdefined data types Strong type checking Dedicated conversion functions needed to integrate types in design Helps to prevent errors Creates major headache for hardware modeling 05/05/2003 Verilog q Data types simple and focused on hardware modeling q Weak type checking q No user-defined data types q Register type confusing became variable type in 2001 standard q Overall Simple 9

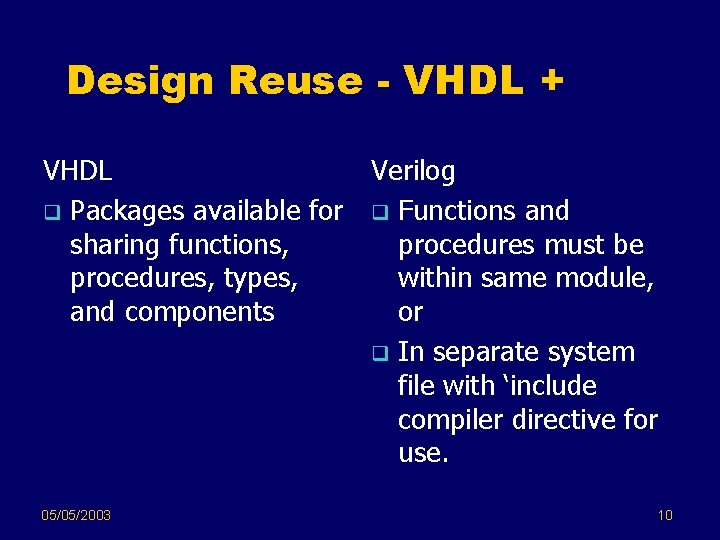

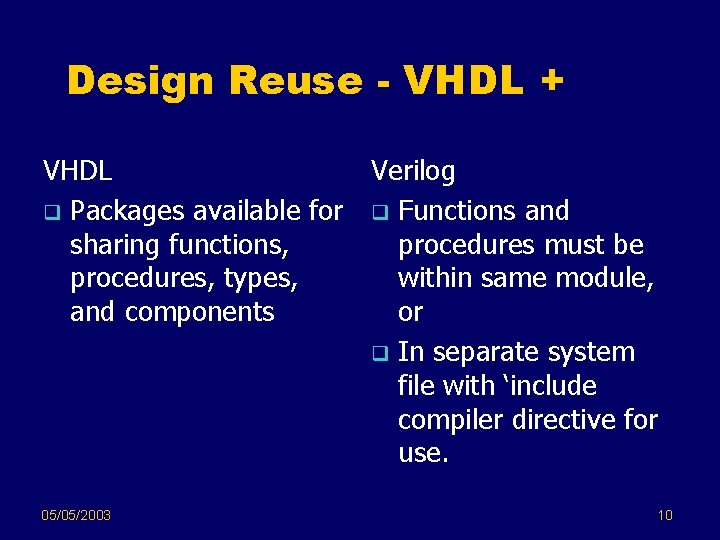

Design Reuse - VHDL + VHDL Verilog q Packages available for q Functions and sharing functions, procedures must be procedures, types, within same module, and components or q In separate system file with ‘include compiler directive for use. 05/05/2003 10

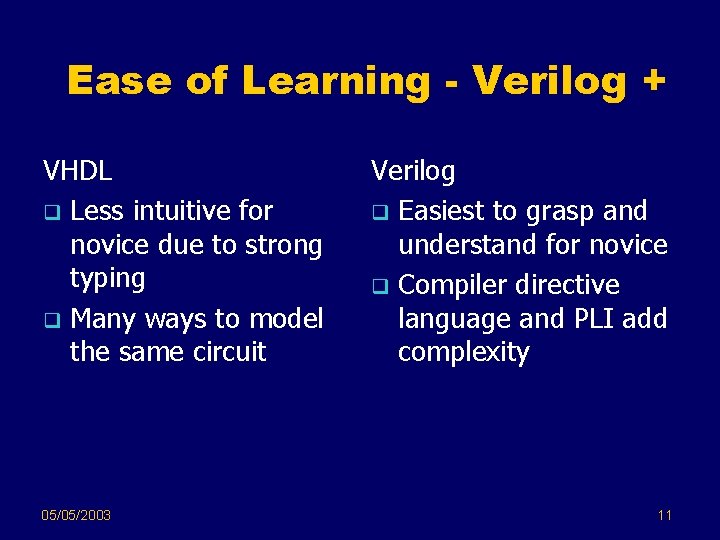

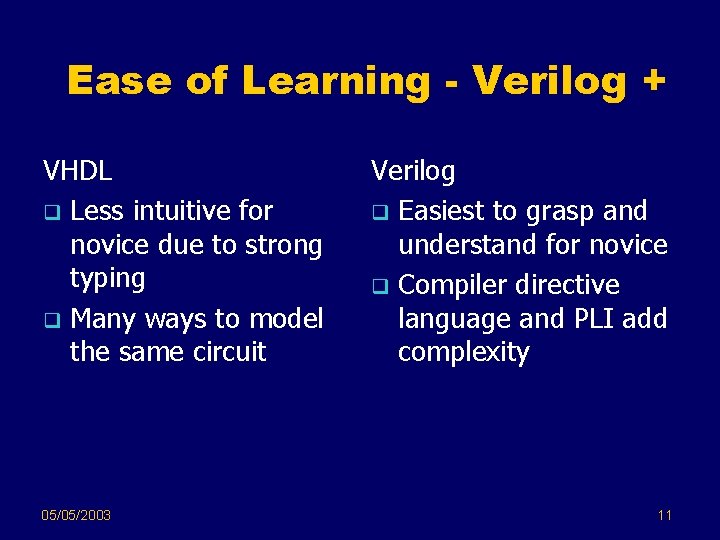

Ease of Learning - Verilog + VHDL q Less intuitive for novice due to strong typing q Many ways to model the same circuit 05/05/2003 Verilog q Easiest to grasp and understand for novice q Compiler directive language and PLI add complexity 11

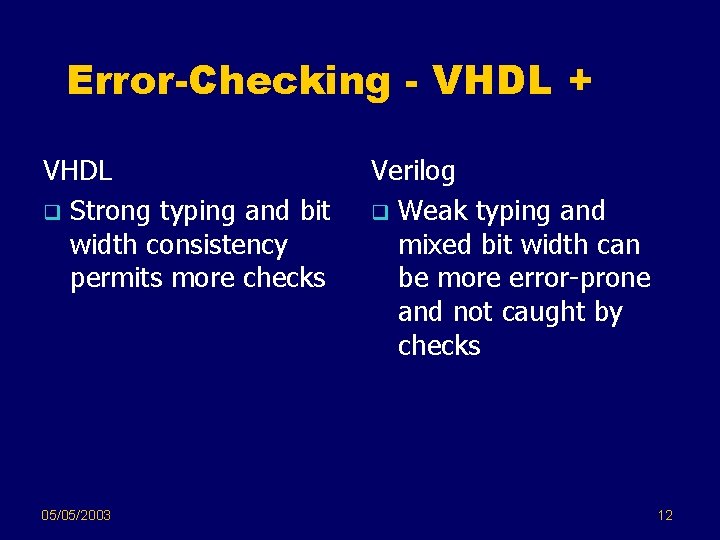

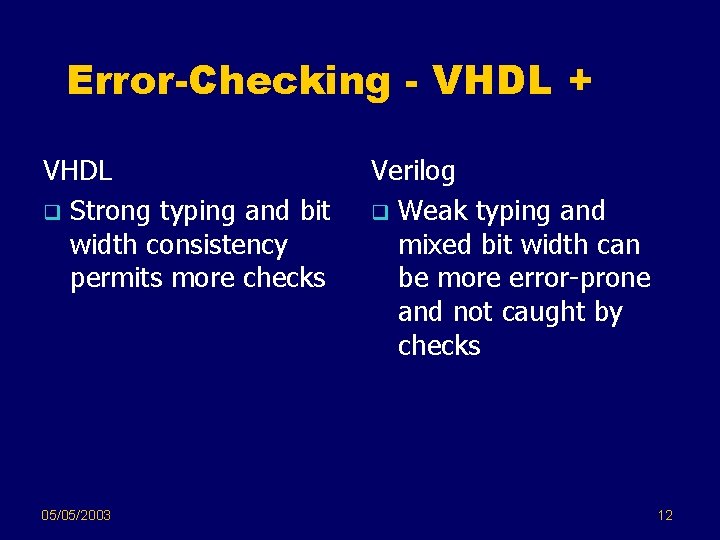

Error-Checking - VHDL + VHDL q Strong typing and bit width consistency permits more checks 05/05/2003 Verilog q Weak typing and mixed bit width can be more error-prone and not caught by checks 12

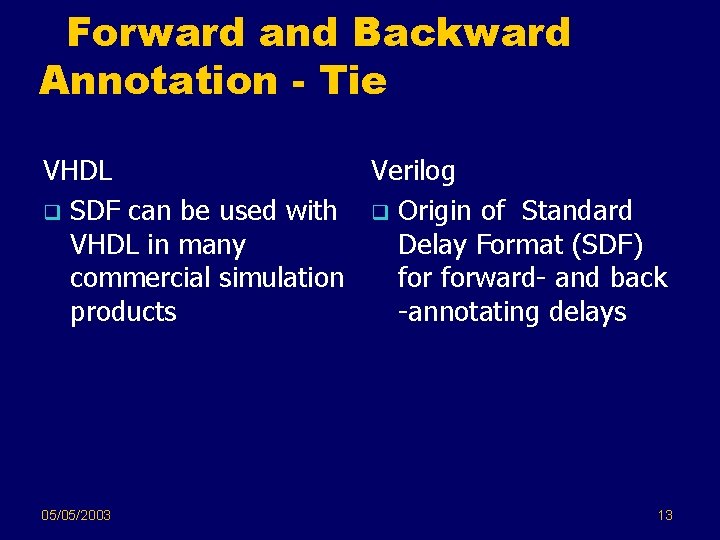

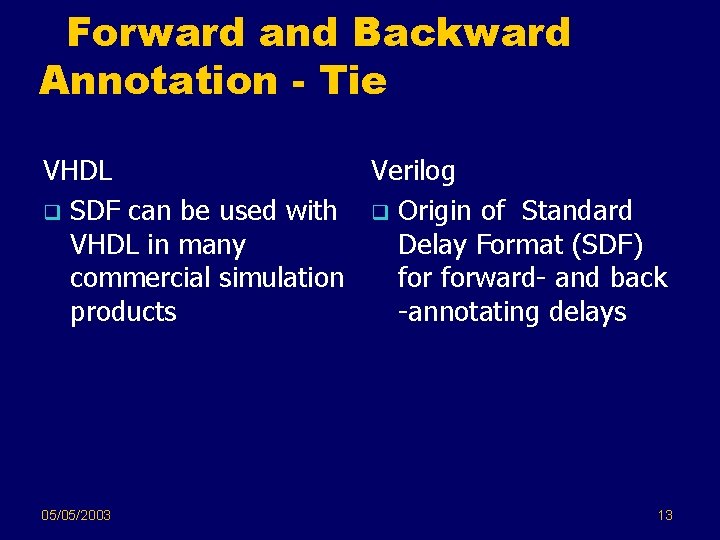

Forward and Backward Annotation - Tie VHDL Verilog q SDF can be used with q Origin of Standard VHDL in many Delay Format (SDF) commercial simulation forward- and back products -annotating delays 05/05/2003 13

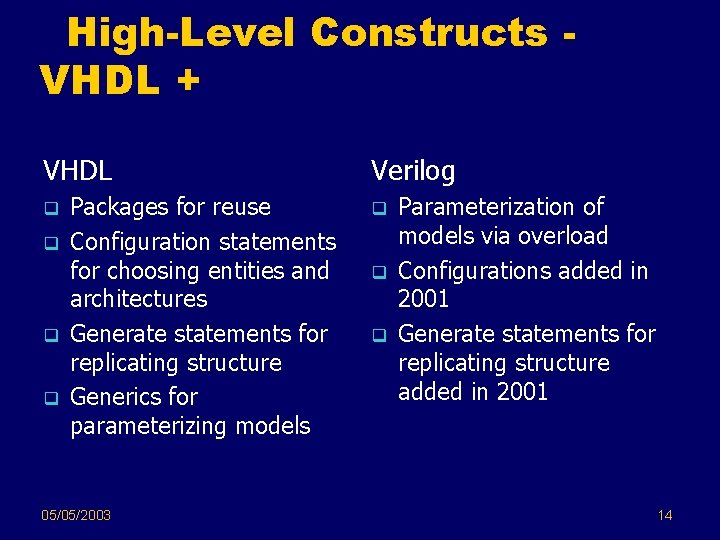

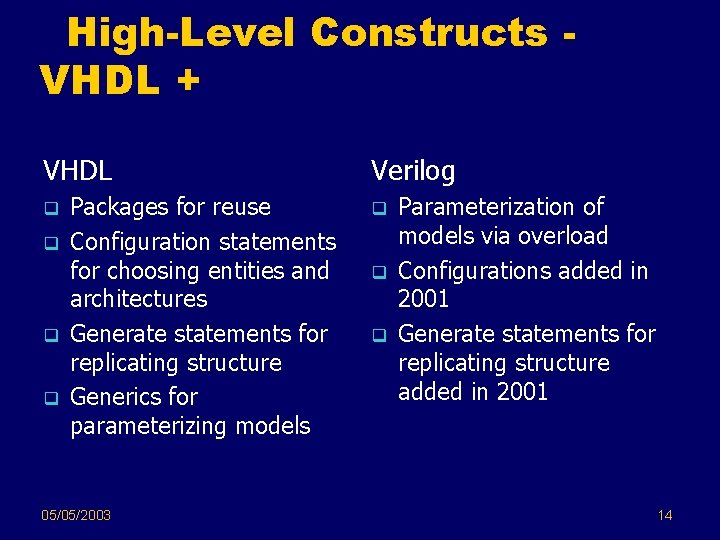

High-Level Constructs VHDL + VHDL q q Packages for reuse Configuration statements for choosing entities and architectures Generate statements for replicating structure Generics for parameterizing models 05/05/2003 Verilog q q q Parameterization of models via overload Configurations added in 2001 Generate statements for replicating structure added in 2001 14

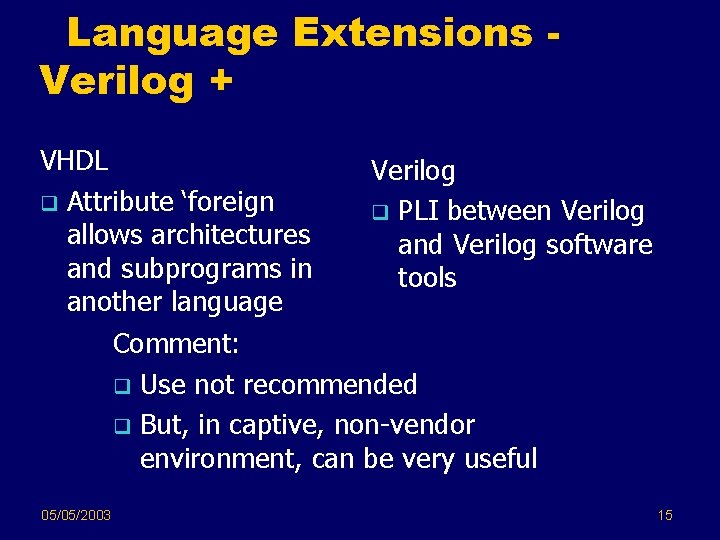

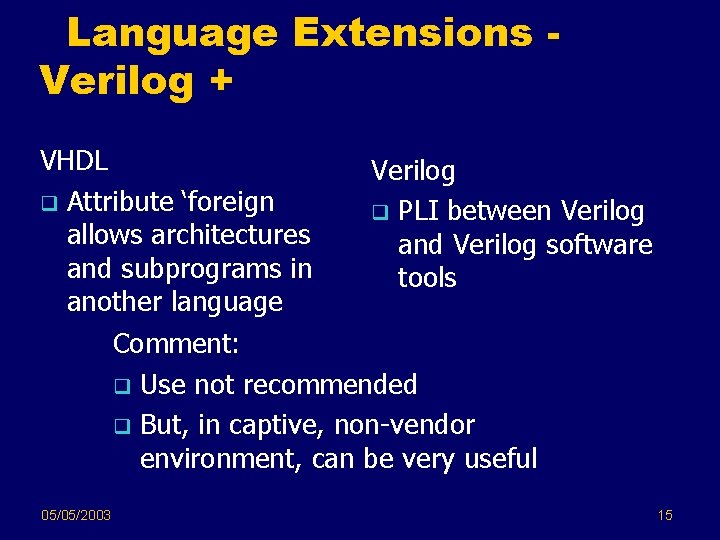

Language Extensions Verilog + VHDL Verilog q Attribute ‘foreign q PLI between Verilog allows architectures and Verilog software and subprograms in tools another language Comment: q Use not recommended q But, in captive, non-vendor environment, can be very useful 05/05/2003 15

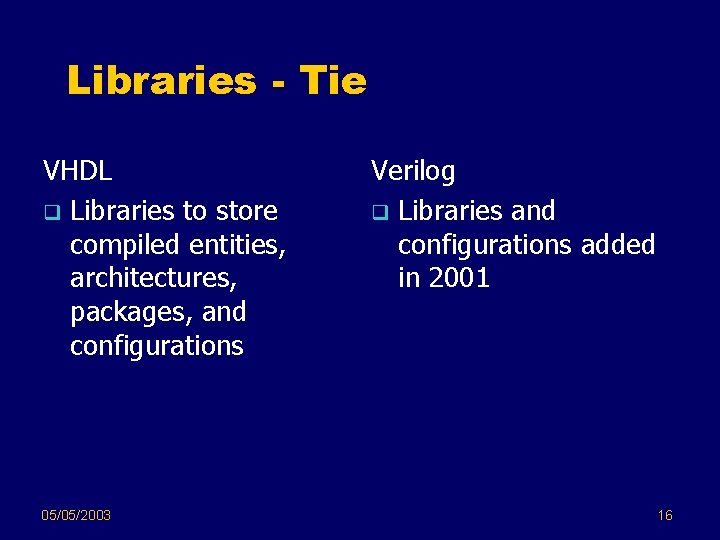

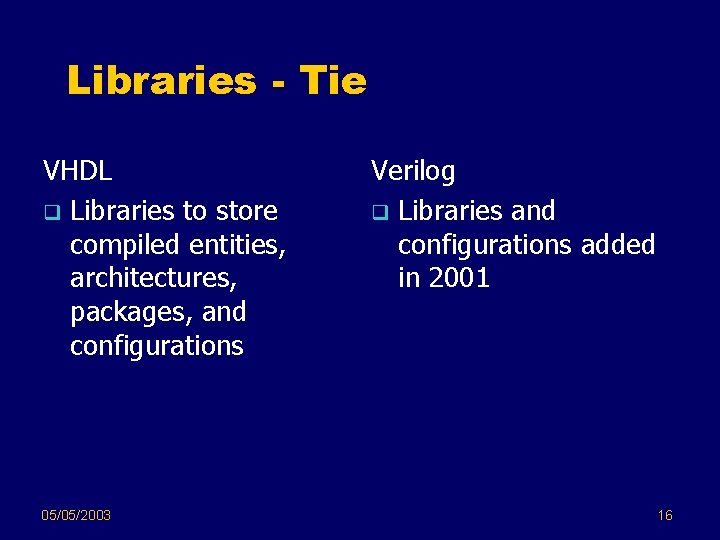

Libraries - Tie VHDL q Libraries to store compiled entities, architectures, packages, and configurations 05/05/2003 Verilog q Libraries and configurations added in 2001 16

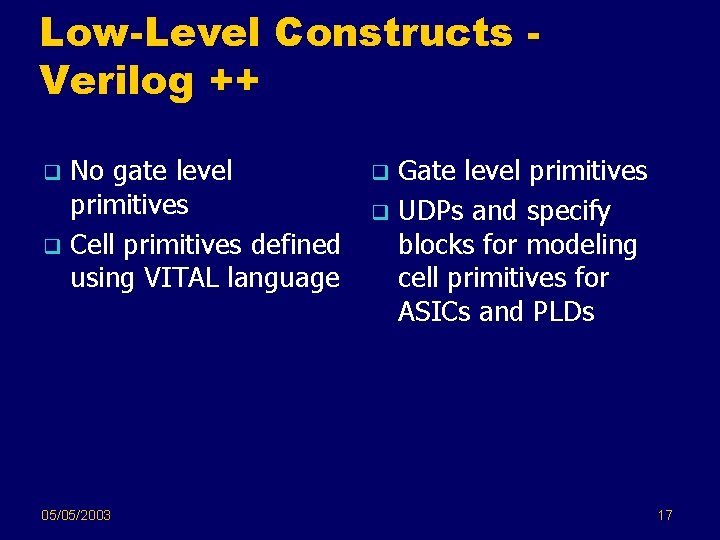

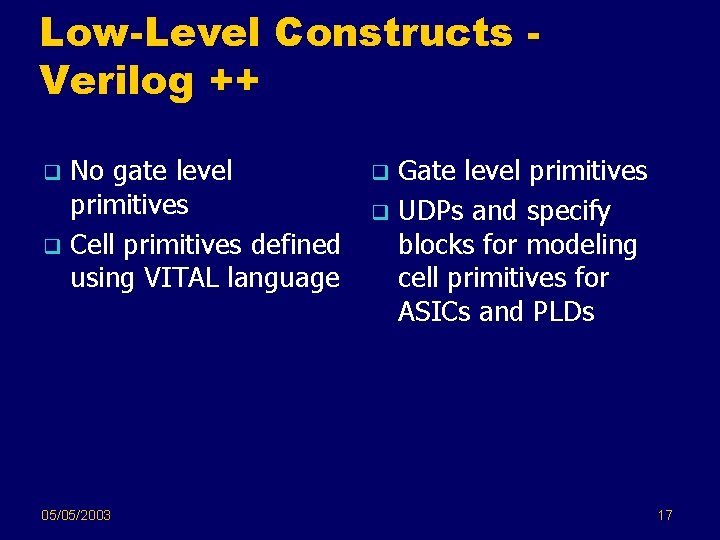

Low-Level Constructs Verilog ++ No gate level primitives q Cell primitives defined using VITAL language q 05/05/2003 Gate level primitives q UDPs and specify blocks for modeling cell primitives for ASICs and PLDs q 17

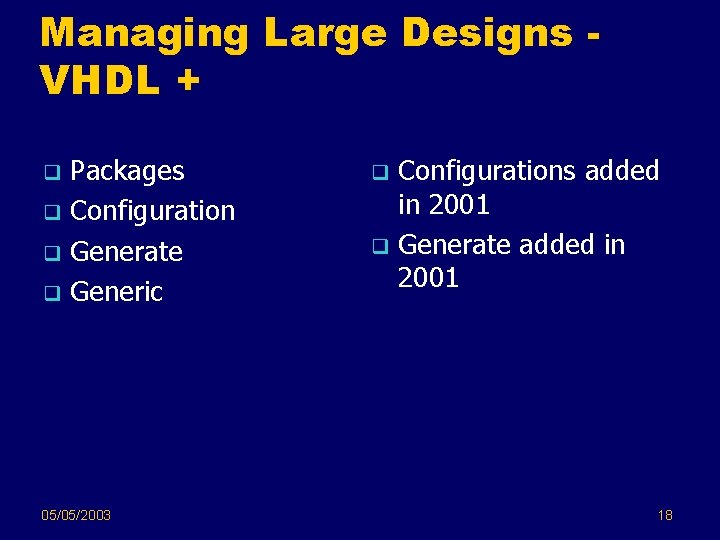

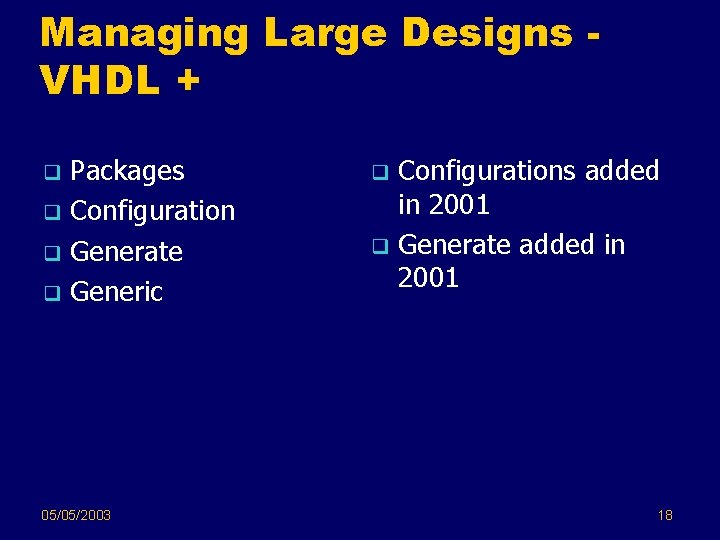

Managing Large Designs VHDL + Packages q Configuration q Generate q Generic q 05/05/2003 Configurations added in 2001 q Generate added in 2001 q 18

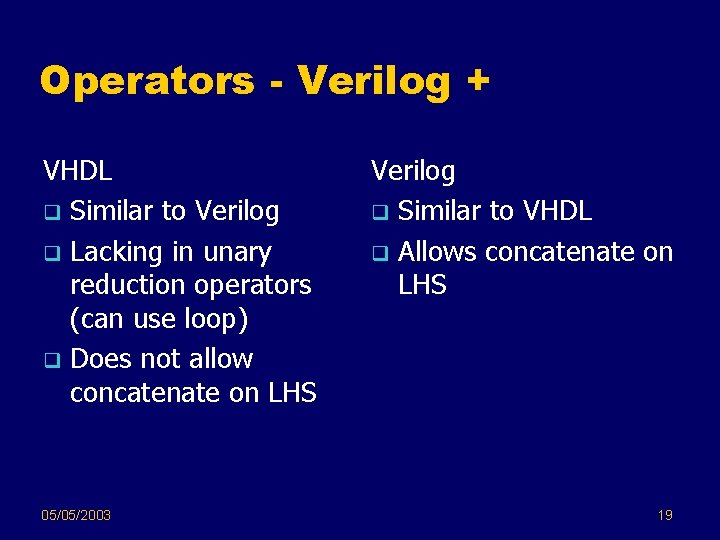

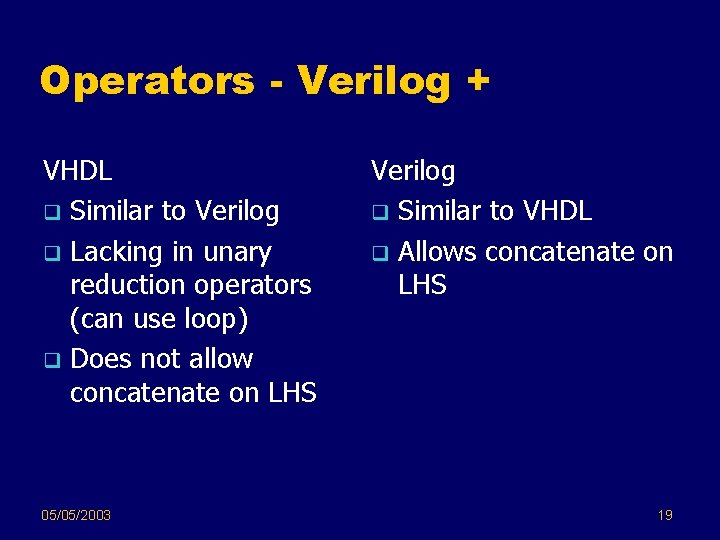

Operators - Verilog + VHDL q Similar to Verilog q Lacking in unary reduction operators (can use loop) q Does not allow concatenate on LHS 05/05/2003 Verilog q Similar to VHDL q Allows concatenate on LHS 19

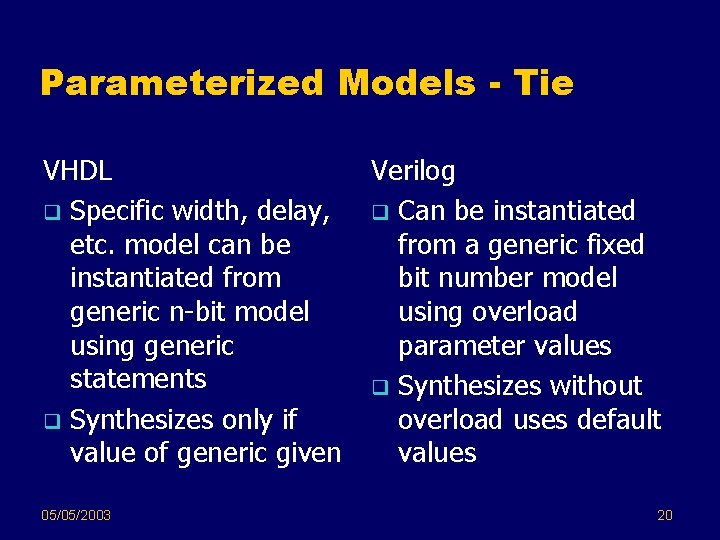

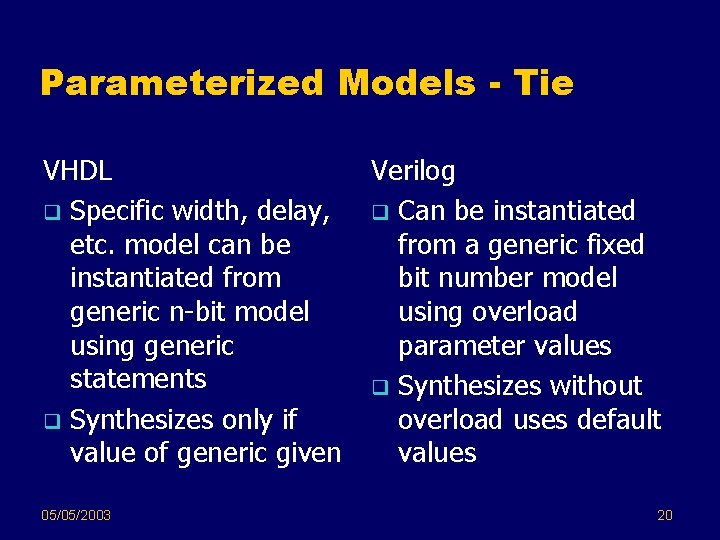

Parameterized Models - Tie VHDL q Specific width, delay, etc. model can be instantiated from generic n-bit model using generic statements q Synthesizes only if value of generic given 05/05/2003 Verilog q Can be instantiated from a generic fixed bit number model using overload parameter values q Synthesizes without overload uses default values 20

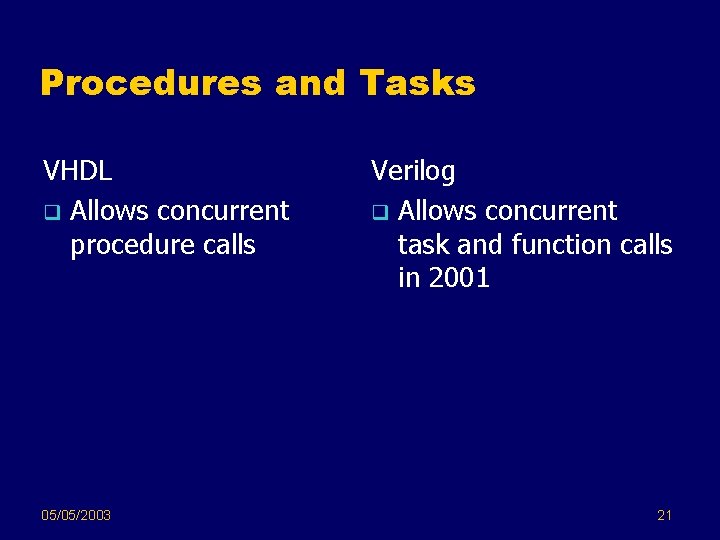

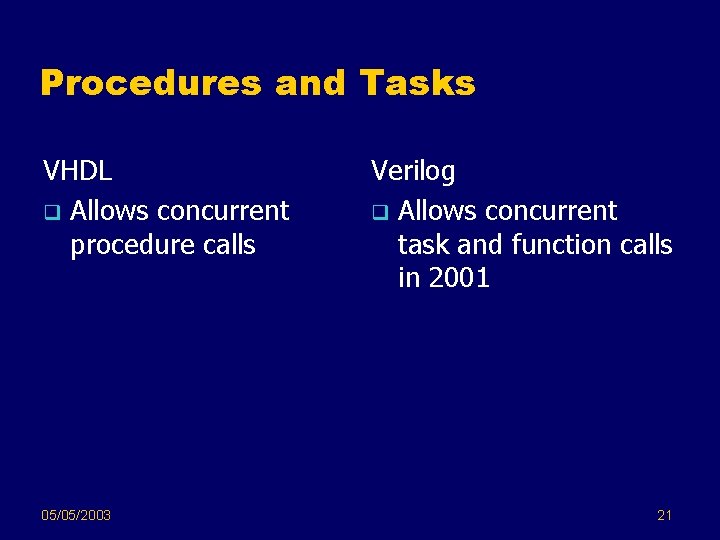

Procedures and Tasks VHDL q Allows concurrent procedure calls 05/05/2003 Verilog q Allows concurrent task and function calls in 2001 21

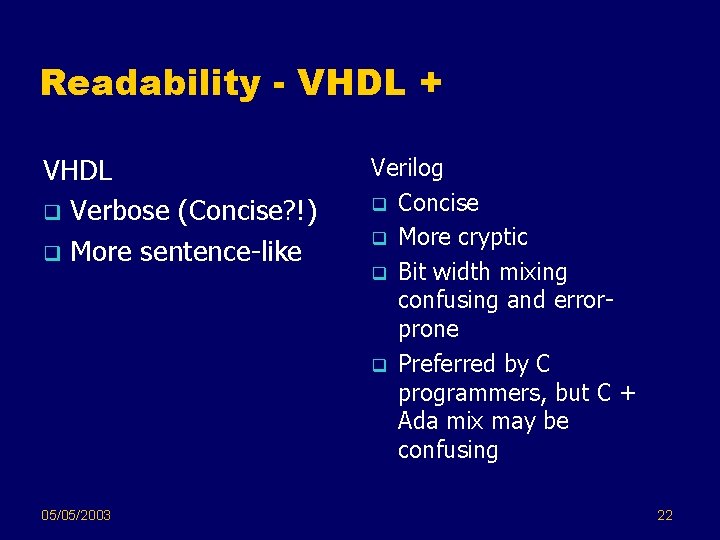

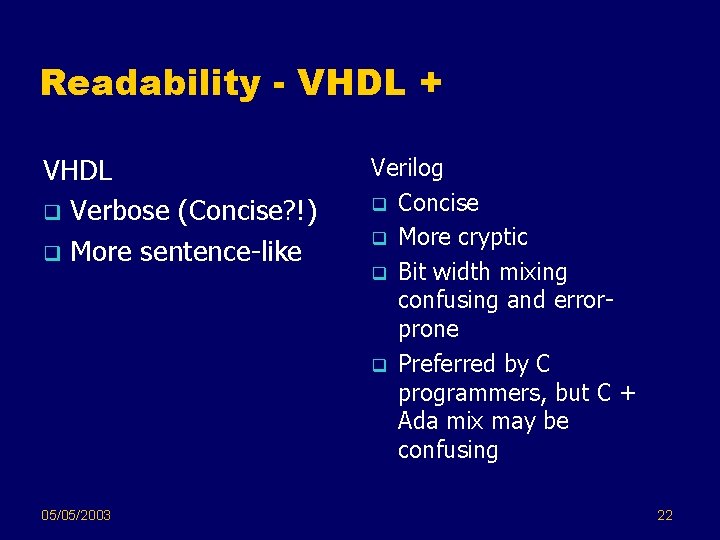

Readability - VHDL + VHDL q Verbose (Concise? !) q More sentence-like 05/05/2003 Verilog q Concise q More cryptic q Bit width mixing confusing and errorprone q Preferred by C programmers, but C + Ada mix may be confusing 22

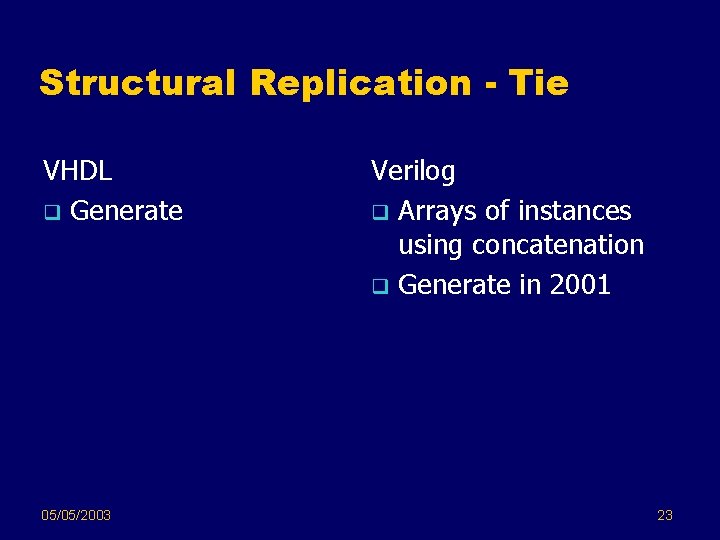

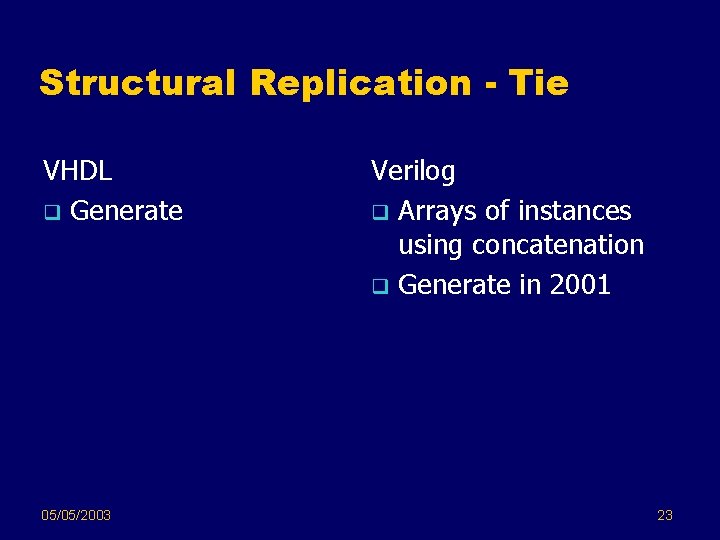

Structural Replication - Tie VHDL q Generate 05/05/2003 Verilog q Arrays of instances using concatenation q Generate in 2001 23

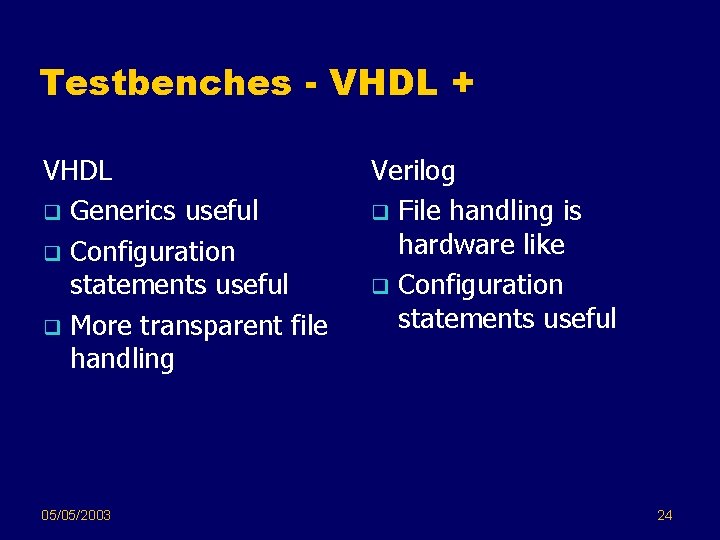

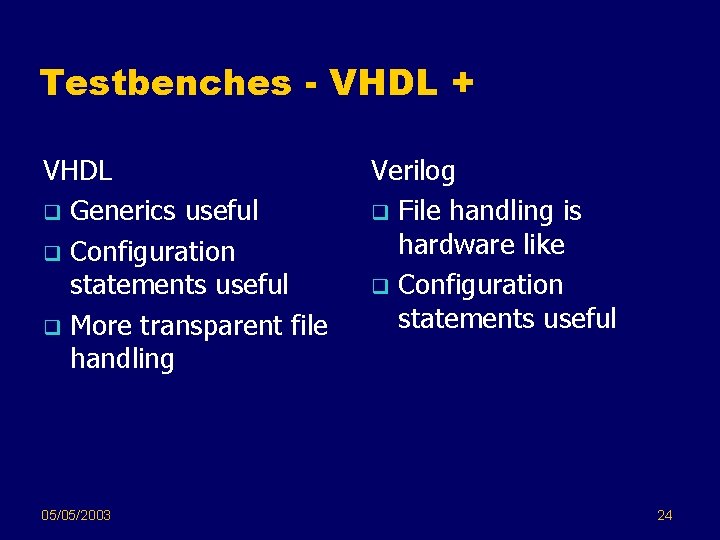

Testbenches - VHDL + VHDL q Generics useful q Configuration statements useful q More transparent file handling 05/05/2003 Verilog q File handling is hardware like q Configuration statements useful 24

Verboseness - Verilog ++ VHDL q Requires defined and matching data types q 1987 required components q Overall - verbose and often longer code 05/05/2003 Verilog q Less explicit type modeling q Overall - less verbose and often much shorter 25

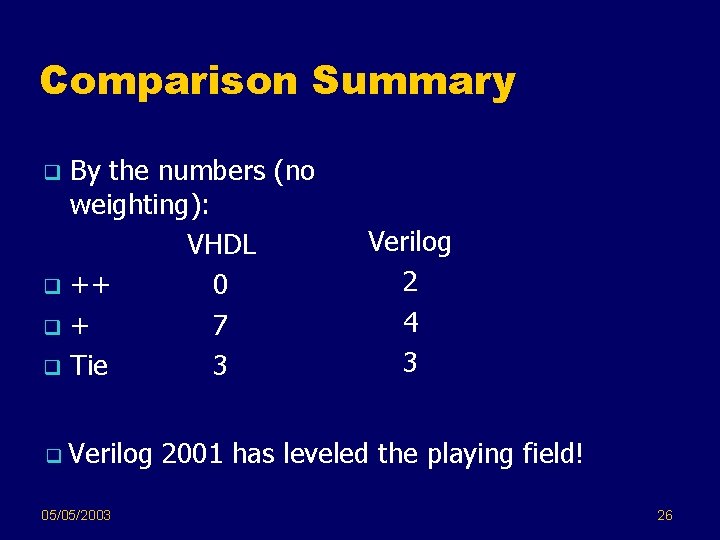

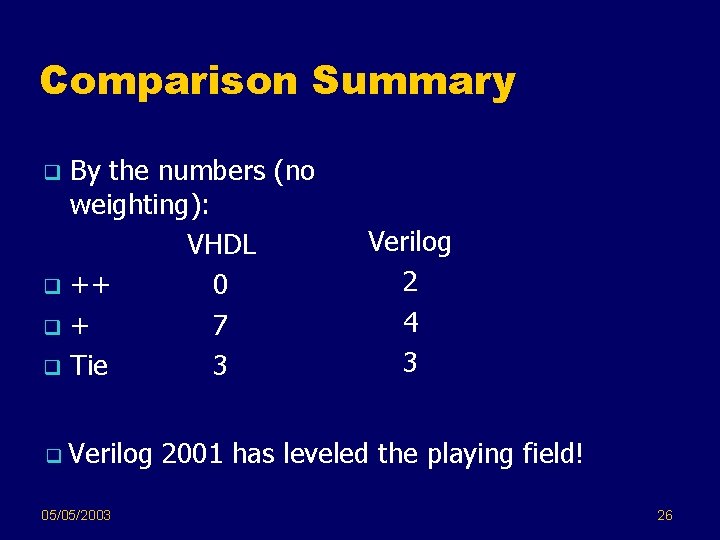

Comparison Summary By the numbers (no weighting): VHDL q ++ 0 q+ 7 q Tie 3 q q Verilog 05/05/2003 Verilog 2 4 3 2001 has leveled the playing field! 26

Comparative Examples q Algorithmic Level § See D. J. Smith paper q RTL Level § See D. J. Smith paper 05/05/2003 27