ECE 551 Digital System Design Synthesis Lecture Set

- Slides: 21

ECE 551: Digital System Design & Synthesis Lecture Set 10 10. 1: Functional & Timing Verification 10. 2: Faults & Testing 04/21/2003 1

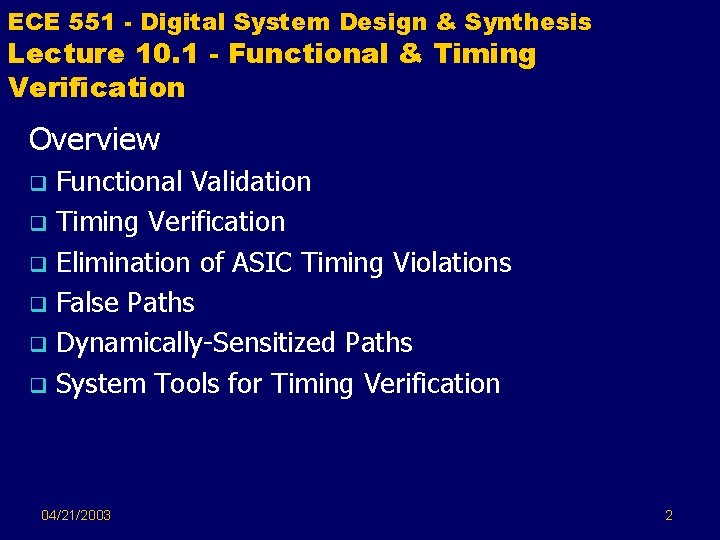

ECE 551 - Digital System Design & Synthesis Lecture 10. 1 - Functional & Timing Verification Overview Functional Validation q Timing Verification q Elimination of ASIC Timing Violations q False Paths q Dynamically-Sensitized Paths q System Tools for Timing Verification q 04/21/2003 2

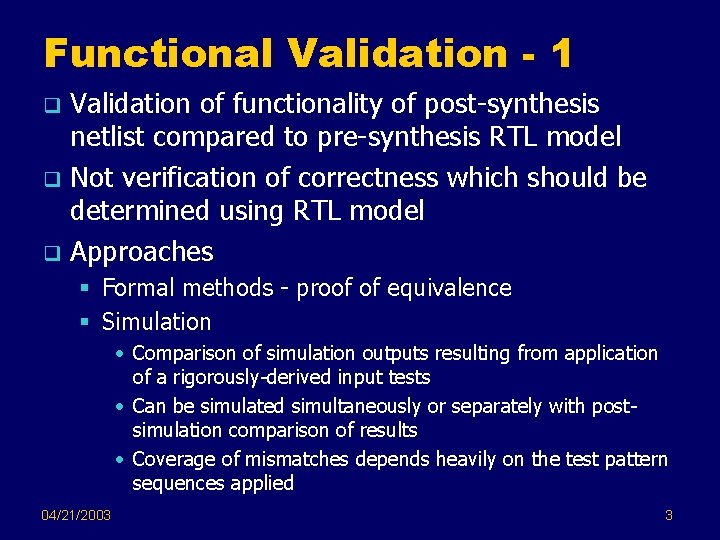

Functional Validation - 1 Validation of functionality of post-synthesis netlist compared to pre-synthesis RTL model q Not verification of correctness which should be determined using RTL model q Approaches q § Formal methods - proof of equivalence § Simulation • Comparison of simulation outputs resulting from application of a rigorously-derived input tests • Can be simulated simultaneously or separately with postsimulation comparison of results • Coverage of mismatches depends heavily on the test pattern sequences applied 04/21/2003 3

Functional Validation - 2 q Simulation Mismatch § RTL model is delay-free; gate-level model contains propagation delays. • Mismatch may be due to improperly written RTL model or due to the speed of the synthesized circuit • Code modification, re-synthesis, and/or change in target specifications may be necessary to resolve. § The RTL description contains races between assignment of one or more variables, improperly used blocking assignments, or asynchronous logic § Don’t care conditions in the RTL model become “care” conditions in the gate-level model 04/21/2003 4

Timing Verification q Dynamic Timing Analysis - Simulation q Static Timing Analysis - Signal path analysis q Timing Specifications q Pragmatics: Factors that Affect Timing 04/21/2003 5

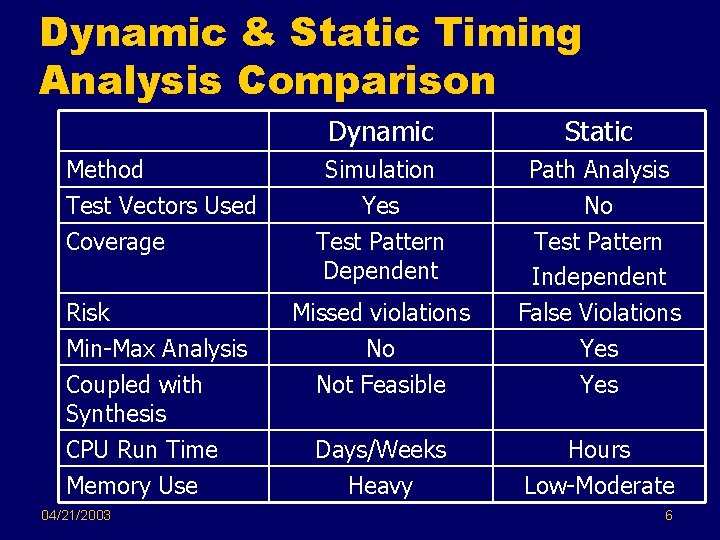

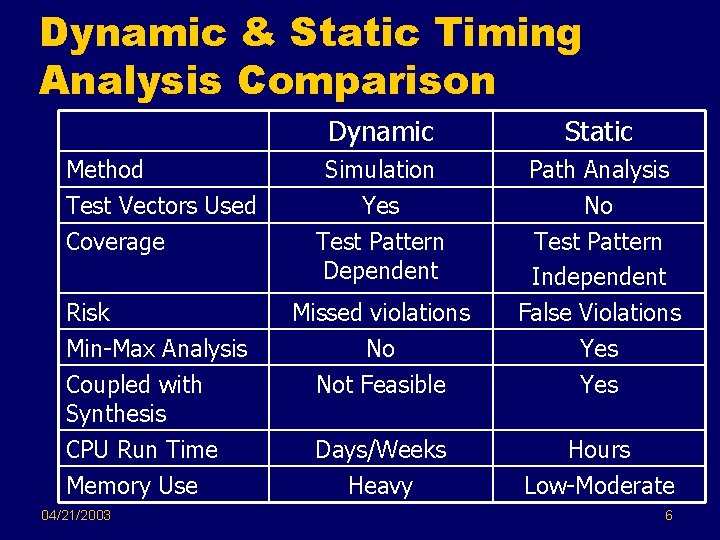

Dynamic & Static Timing Analysis Comparison Dynamic Static Method Test Vectors Used Coverage Simulation Yes Test Pattern Dependent Path Analysis No Test Pattern Independent Risk Min-Max Analysis Coupled with Synthesis Missed violations No Not Feasible False Violations Yes Days/Weeks Heavy Hours Low-Moderate CPU Run Time Memory Use 04/21/2003 6

Dynamic Timing Analysis - 1 q Coverage of timing violations dependent on effectiveness of applied test vectors q Vectors are not just static, but also involve one or more changing inputs q For the simplest timing model, pairs of vectors are required q In sequential circuits, to achieve a “vector pair” internally may require a long sequence of vectors on the external ports 04/21/2003 7

Dynamic Timing Analysis - 2 q q How are effective test patterns produced? Critical path concept - longest delay path through a circuit - requires consideration of flip-flop propagation delays, flip-flop setup times, delays to inputs from flipflops and delays from outputs to flip-flops per prior discussion Elimination of one critical path may simply produce others until timing constraints are meet - thus a set of many paths may need to be considered How are critical paths identified? § Ad Hoc § Using timing analysis! 04/21/2003 8

Dynamic Timing Analysis - 3 Critical path determination may be very difficult since it can be dependent on applied values q Once path determined, need to “sensitize” the output of the path to an input change q Requires fixing of “off path” values according to controlling input patterns on gates q Can be made very complex due to reconvergent fanout paths q More complex when using t. PHL and t. PLH values due to changes in delay based on inversion control on the path q Example of complex DTA case q 04/21/2003 9

Static Timing Analysis - 1 Creates directed, acyclic graph (DAG) of circuit by abstracting the topology of the net list q Implicitly analyzes all possible paths to determine critical delay path q Example of simple STA case (no slide) q But there are issues re accuracy q § Problems of multiple paths with the same entry and exit points due to reconvergent fan-out § Complexity introduced by t. PHL and t. PLH values § Issue of false paths - paths through the DAG down which no signal can propagate from input to output 04/21/2003 10

Static Timing Analysis - 2 q Requires introduction of functional information: § Dealing with multiple paths with same entry and exit point § Dealing with t. PHL and t. PLH and inversions on path q Requires user assistance § Dealing with false paths q Example 04/21/2003 of complex STA case (no slide) 11

Timing Specifications q Already covered in Synthesis Constraints lecture (9. 1) 04/21/2003 12

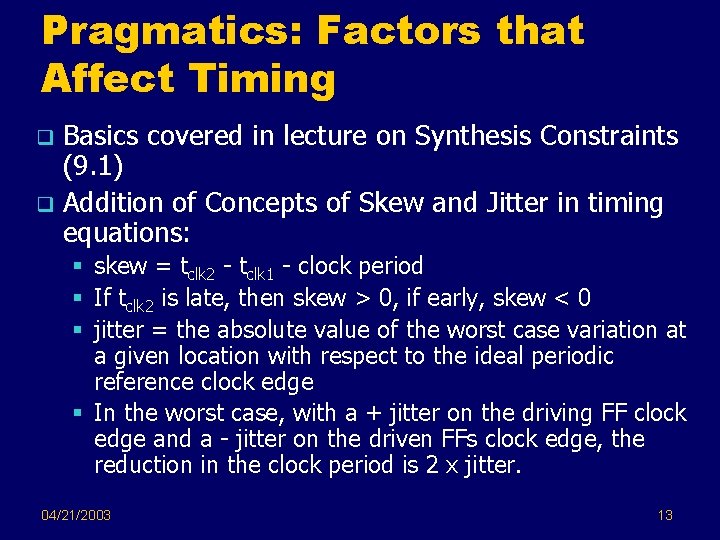

Pragmatics: Factors that Affect Timing Basics covered in lecture on Synthesis Constraints (9. 1) q Addition of Concepts of Skew and Jitter in timing equations: q § skew = tclk 2 - tclk 1 - clock period § If tclk 2 is late, then skew > 0, if early, skew < 0 § jitter = the absolute value of the worst case variation at a given location with respect to the ideal periodic reference clock edge § In the worst case, with a + jitter on the driving FF clock edge and a - jitter on the driven FFs clock edge, the reduction in the clock period is 2 x jitter. 04/21/2003 13

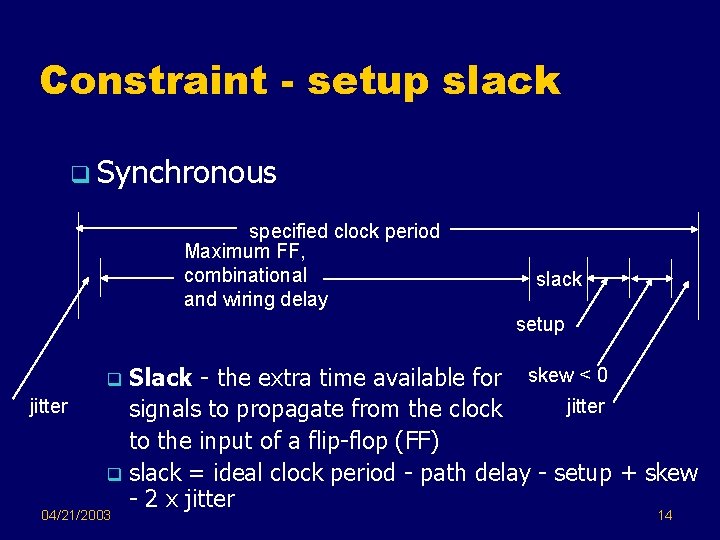

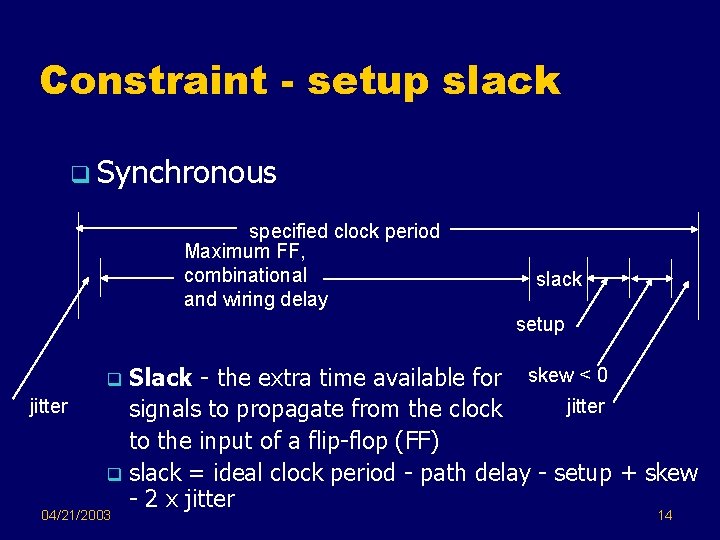

Constraint - setup slack q Synchronous specified clock period Maximum FF, combinational and wiring delay slack setup Slack - the extra time available for skew < 0 jitter signals to propagate from the clock to the input of a flip-flop (FF) q slack = ideal clock period - path delay - setup + skew - 2 x jitter q jitter 04/21/2003 14

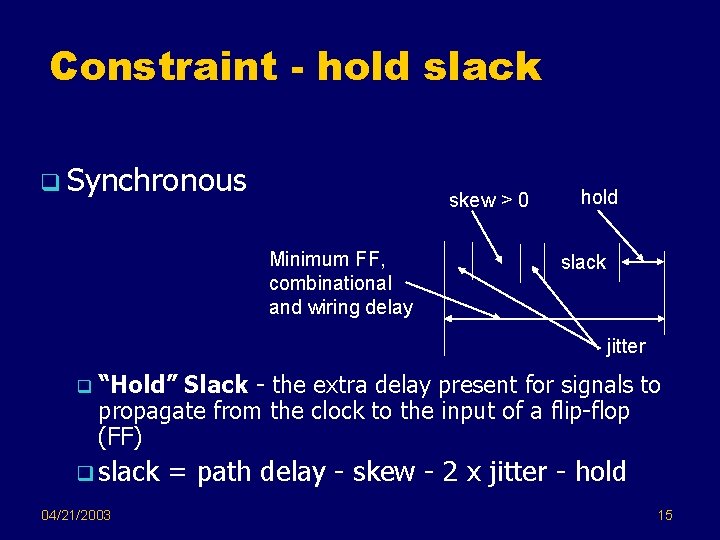

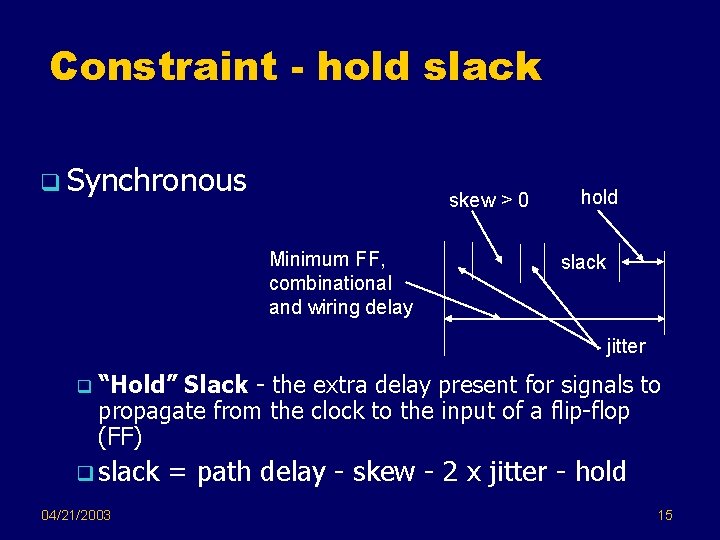

Constraint - hold slack q Synchronous skew > 0 Minimum FF, combinational and wiring delay hold slack jitter q “Hold” Slack - the extra delay present for signals to propagate from the clock to the input of a flip-flop (FF) q slack 04/21/2003 = path delay - skew - 2 x jitter - hold 15

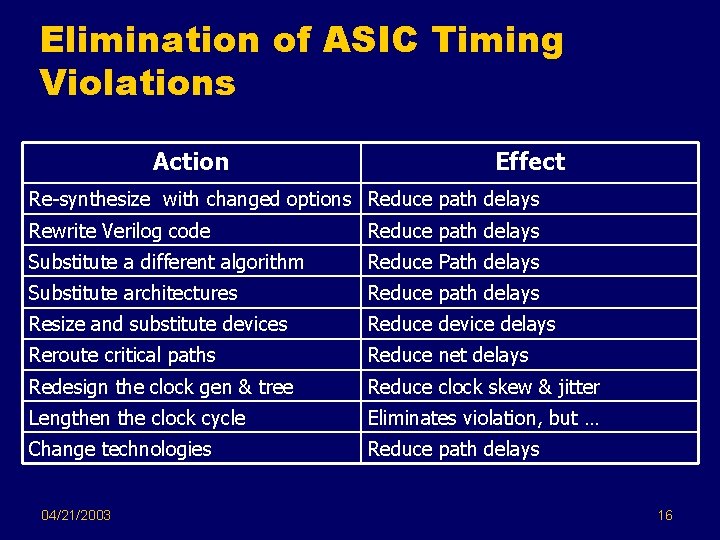

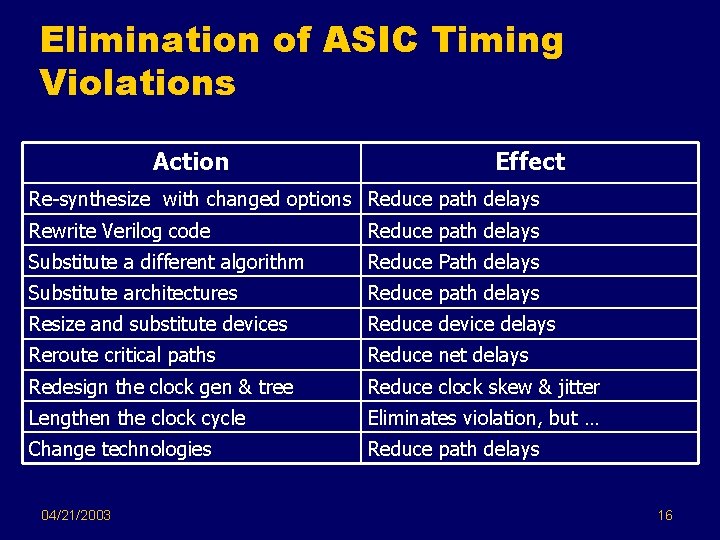

Elimination of ASIC Timing Violations Action Effect Re-synthesize with changed options Reduce path delays Rewrite Verilog code Reduce path delays Substitute a different algorithm Reduce Path delays Substitute architectures Reduce path delays Resize and substitute devices Reduce device delays Reroute critical paths Reduce net delays Redesign the clock gen & tree Reduce clock skew & jitter Lengthen the clock cycle Eliminates violation, but … Change technologies Reduce path delays 04/21/2003 16

False Paths q See Figure 11 -18 in Text q See Figure 11 -20 in Text 04/21/2003 17

Dynamically Sensitized Paths q Will be missed by static timing analyzer q May or may not be handle by simulation depending on inputs q Example 04/21/2003 18

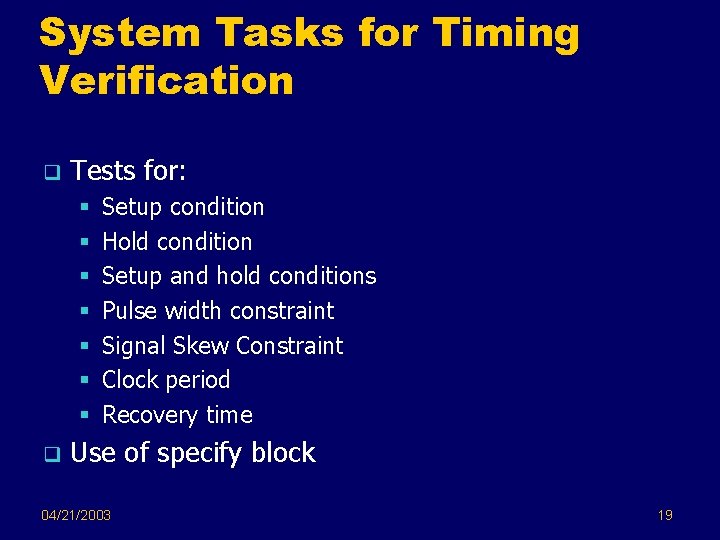

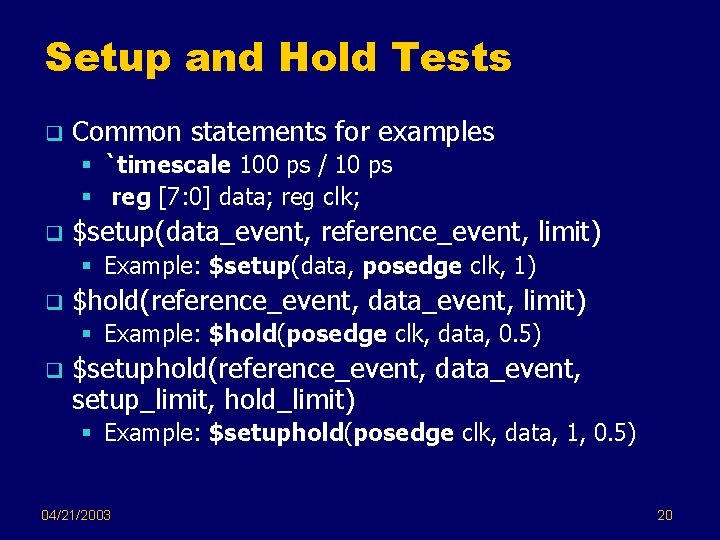

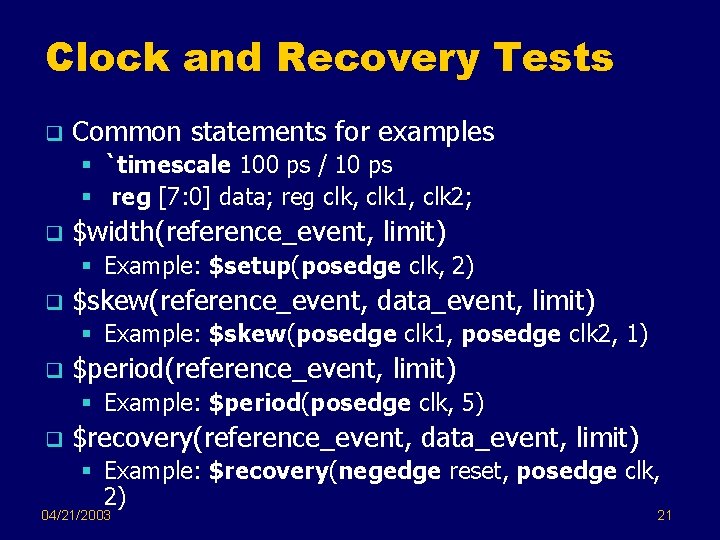

System Tasks for Timing Verification q Tests for: § § § § q Setup condition Hold condition Setup and hold conditions Pulse width constraint Signal Skew Constraint Clock period Recovery time Use of specify block 04/21/2003 19

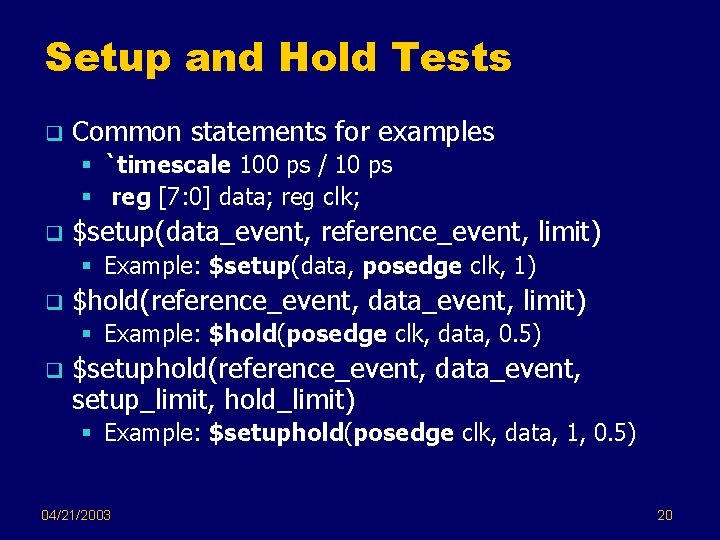

Setup and Hold Tests q Common statements for examples § `timescale 100 ps / 10 ps § reg [7: 0] data; reg clk; q $setup(data_event, reference_event, limit) § Example: $setup(data, posedge clk, 1) q $hold(reference_event, data_event, limit) § Example: $hold(posedge clk, data, 0. 5) q $setuphold(reference_event, data_event, setup_limit, hold_limit) § Example: $setuphold(posedge clk, data, 1, 0. 5) 04/21/2003 20

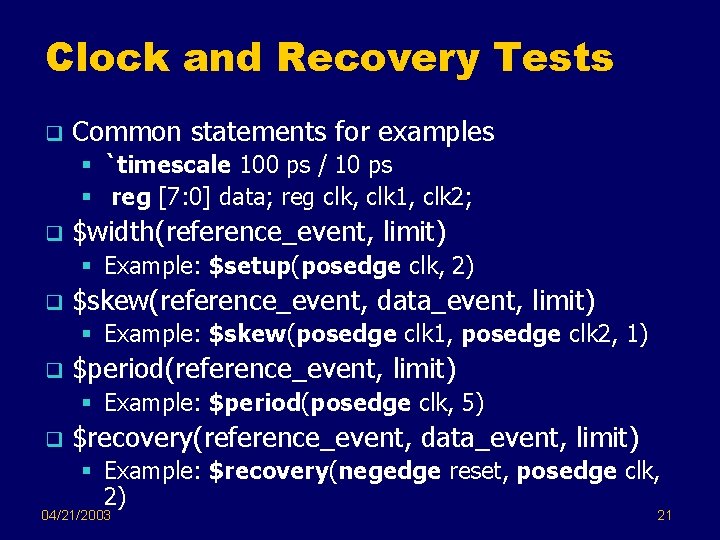

Clock and Recovery Tests q Common statements for examples § `timescale 100 ps / 10 ps § reg [7: 0] data; reg clk, clk 1, clk 2; q $width(reference_event, limit) § Example: $setup(posedge clk, 2) q $skew(reference_event, data_event, limit) § Example: $skew(posedge clk 1, posedge clk 2, 1) q $period(reference_event, limit) § Example: $period(posedge clk, 5) q $recovery(reference_event, data_event, limit) § Example: $recovery(negedge reset, posedge clk, 2) 04/21/2003 21