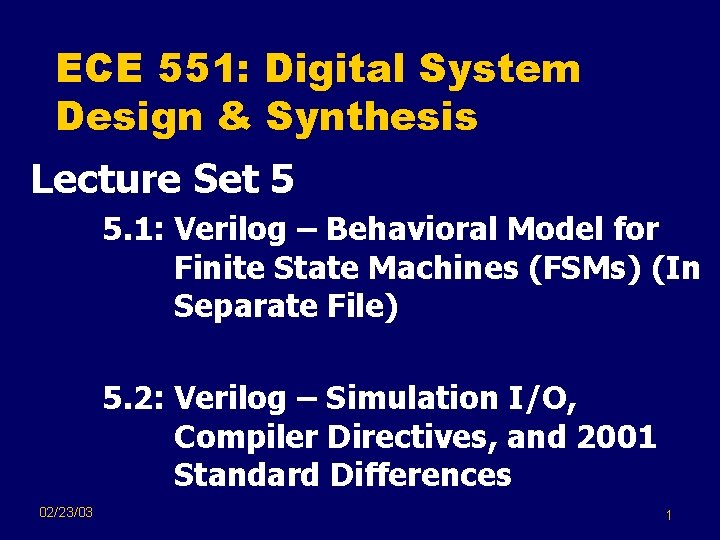

ECE 551 Digital System Design Synthesis Lecture Set

- Slides: 23

ECE 551: Digital System Design & Synthesis Lecture Set 5 5. 1: Verilog – Behavioral Model for Finite State Machines (FSMs) (In Separate File) 5. 2: Verilog – Simulation I/O, Compiler Directives, and 2001 Standard Differences 02/23/03 1

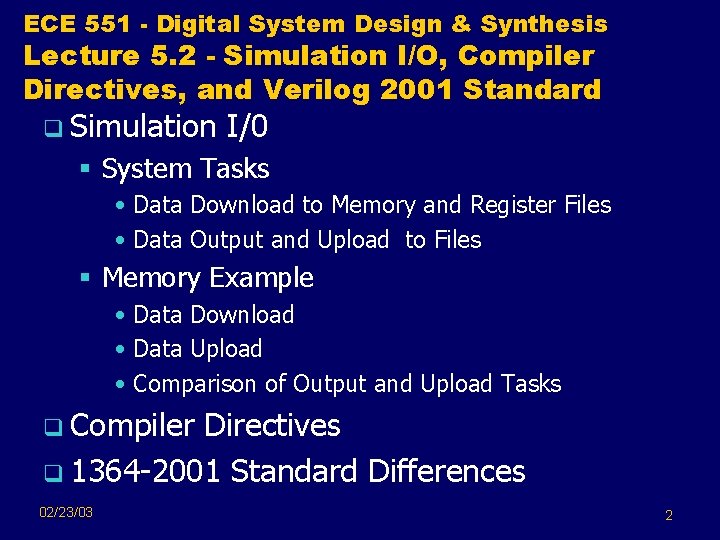

ECE 551 - Digital System Design & Synthesis Lecture 5. 2 - Simulation I/O, Compiler Directives, and Verilog 2001 Standard q Simulation I/0 § System Tasks • Data Download to Memory and Register Files • Data Output and Upload to Files § Memory Example • Data Download • Data Upload • Comparison of Output and Upload Tasks q Compiler Directives q 1364 -2001 Standard Differences 02/23/03 2

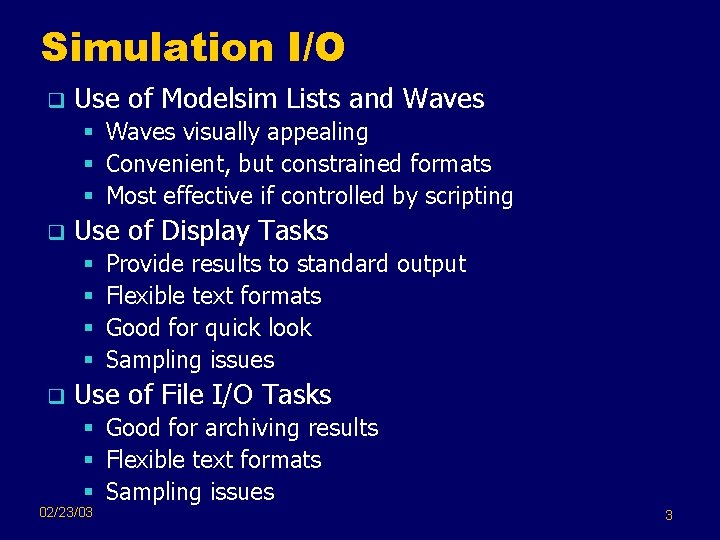

Simulation I/O q Use of Modelsim Lists and Waves § Waves visually appealing § Convenient, but constrained formats § Most effective if controlled by scripting q Use of Display Tasks § § q Provide results to standard output Flexible text formats Good for quick look Sampling issues Use of File I/O Tasks § Good for archiving results § Flexible text formats § Sampling issues 02/23/03 3

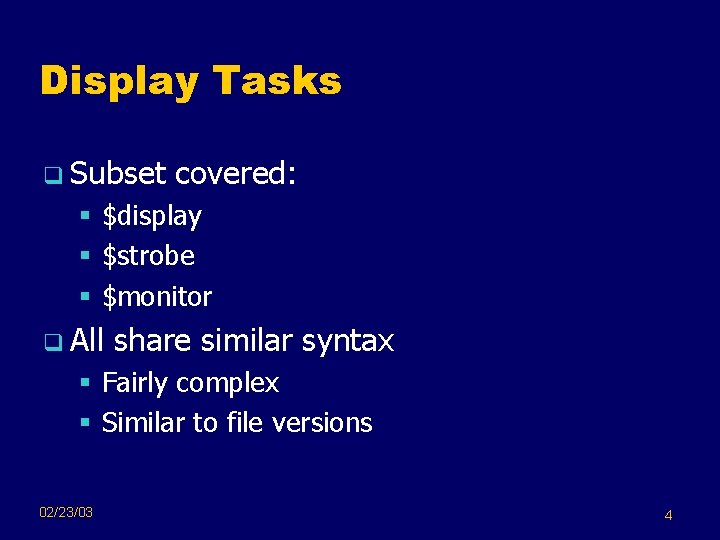

Display Tasks q Subset covered: § $display § $strobe § $monitor q All share similar syntax § Fairly complex § Similar to file versions 02/23/03 4

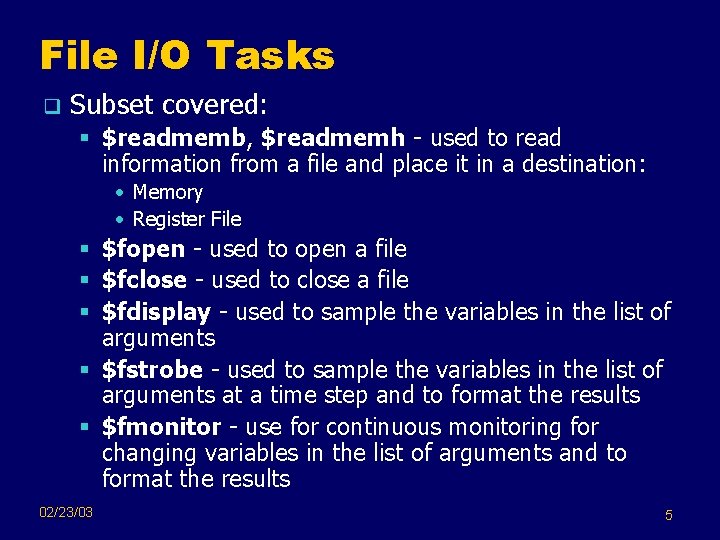

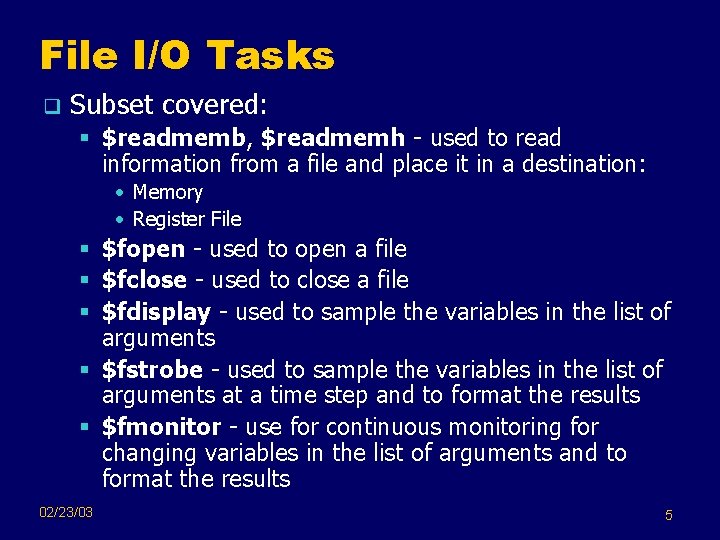

File I/O Tasks q Subset covered: § $readmemb, $readmemh - used to read information from a file and place it in a destination: • Memory • Register File § $fopen - used to open a file § $fclose - used to close a file § $fdisplay - used to sample the variables in the list of arguments § $fstrobe - used to sample the variables in the list of arguments at a time step and to format the results § $fmonitor - use for continuous monitoring for changing variables in the list of arguments and to format the results 02/23/03 5

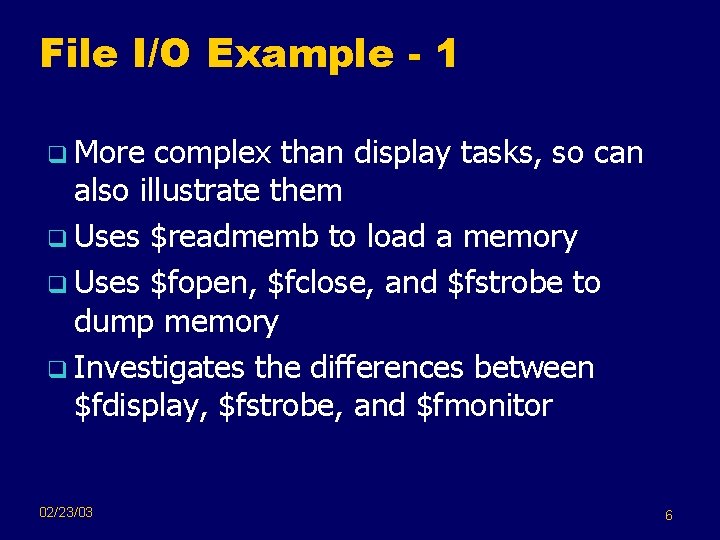

File I/O Example - 1 q More complex than display tasks, so can also illustrate them q Uses $readmemb to load a memory q Uses $fopen, $fclose, and $fstrobe to dump memory q Investigates the differences between $fdisplay, $fstrobe, and $fmonitor 02/23/03 6

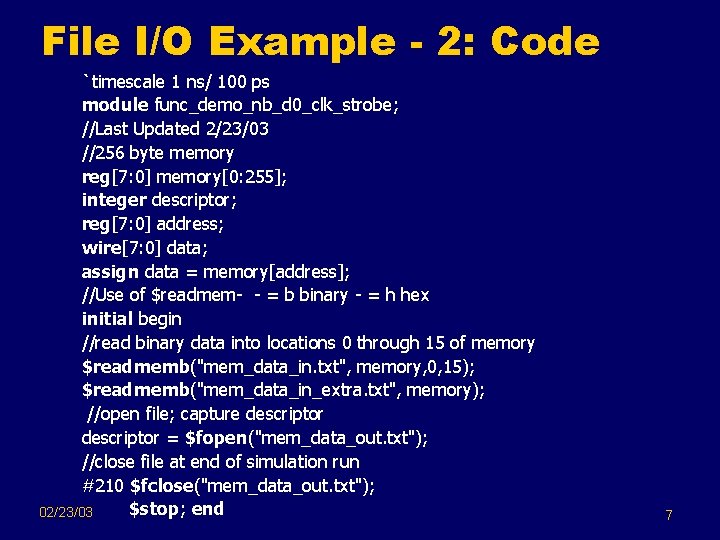

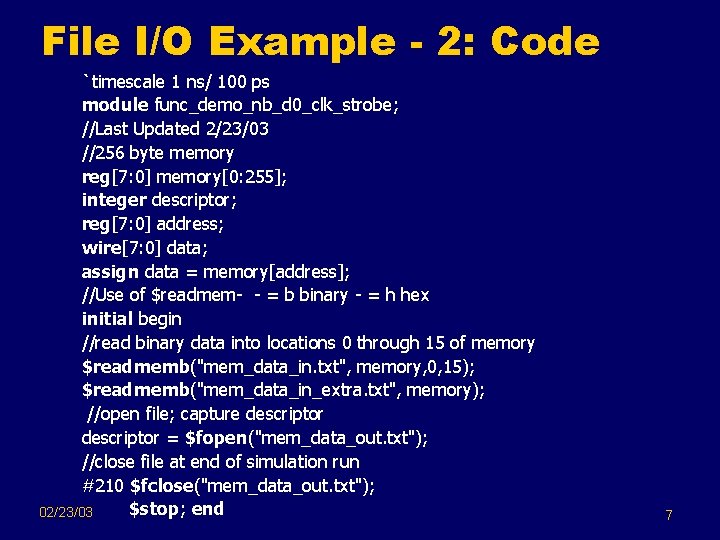

File I/O Example - 2: Code `timescale 1 ns/ 100 ps module func_demo_nb_d 0_clk_strobe; //Last Updated 2/23/03 //256 byte memory reg[7: 0] memory[0: 255]; integer descriptor; reg[7: 0] address; wire[7: 0] data; assign data = memory[address]; //Use of $readmem- - = b binary - = h hex initial begin //read binary data into locations 0 through 15 of memory $readmemb("mem_data_in. txt", memory, 0, 15); $readmemb("mem_data_in_extra. txt", memory); //open file; capture descriptor = $fopen("mem_data_out. txt"); //close file at end of simulation run #210 $fclose("mem_data_out. txt"); $stop; end 02/23/03 7

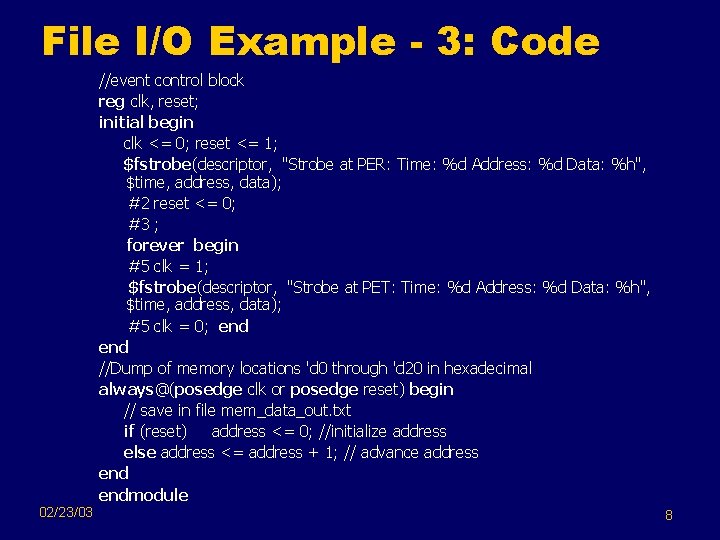

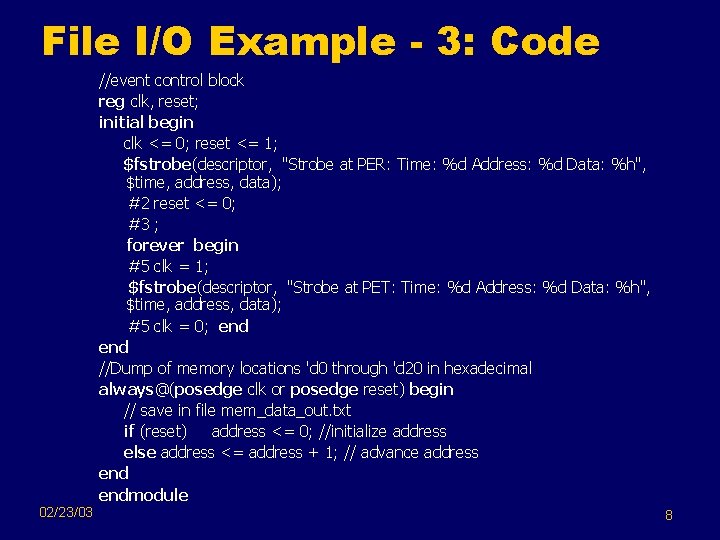

File I/O Example - 3: Code //event control block reg clk, reset; initial begin clk <= 0; reset <= 1; $fstrobe(descriptor, "Strobe at PER: Time: %d Address: %d Data: %h", $time, address, data); #2 reset <= 0; #3 ; forever begin #5 clk = 1; $fstrobe(descriptor, "Strobe at PET: Time: %d Address: %d Data: %h", $time, address, data); #5 clk = 0; end //Dump of memory locations 'd 0 through 'd 20 in hexadecimal always@(posedge clk or posedge reset) begin // save in file mem_data_out. txt if (reset) address <= 0; //initialize address else address <= address + 1; // advance address endmodule 02/23/03 8

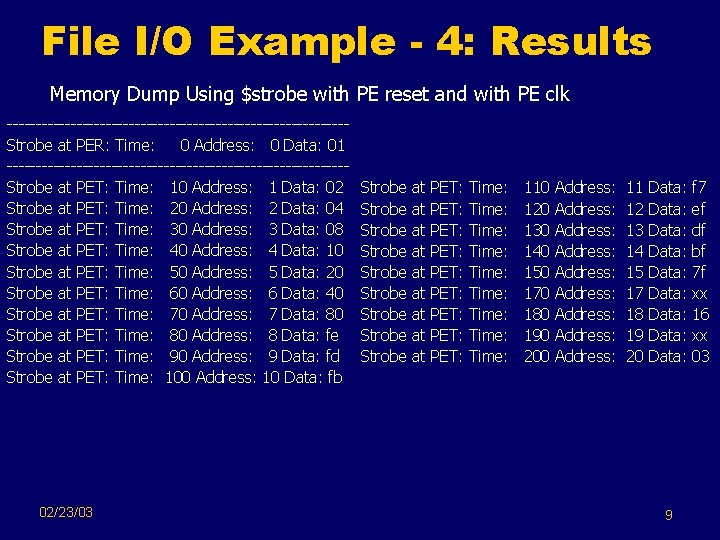

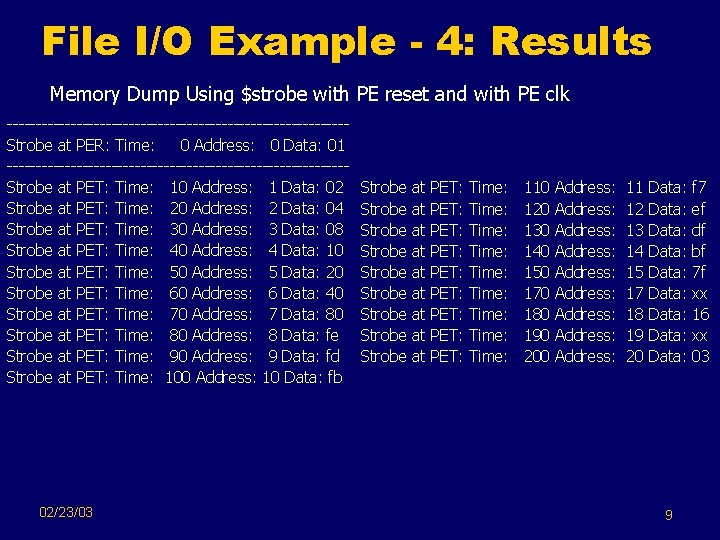

File I/O Example - 4: Results Memory Dump Using $strobe with PE reset and with PE clk -----------------------------Strobe at PER: Time: 0 Address: 0 Data: 01 -----------------------------Strobe at PET: Time: 10 Address: 1 Data: 02 Strobe at PET: Time: 20 Address: 2 Data: 04 Strobe at PET: Time: 30 Address: 3 Data: 08 Strobe at PET: Time: 40 Address: 4 Data: 10 Strobe at PET: Time: 50 Address: 5 Data: 20 Strobe at PET: Time: 60 Address: 6 Data: 40 Strobe at PET: Time: 70 Address: 7 Data: 80 Strobe at PET: Time: 80 Address: 8 Data: fe Strobe at PET: Time: 90 Address: 9 Data: fd Strobe at PET: Time: 100 Address: 10 Data: fb 02/23/03 Strobe Strobe Strobe at at at PET: PET: PET: Time: Time: Time: 110 120 130 140 150 170 180 190 200 Address: Address: Address: 11 12 13 14 15 17 18 19 20 Data: Data: Data: 9 f 7 ef df bf 7 f xx 16 xx 03

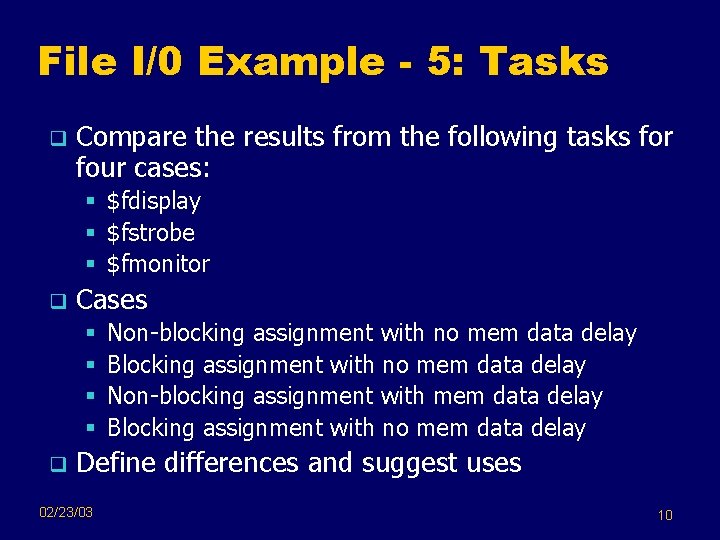

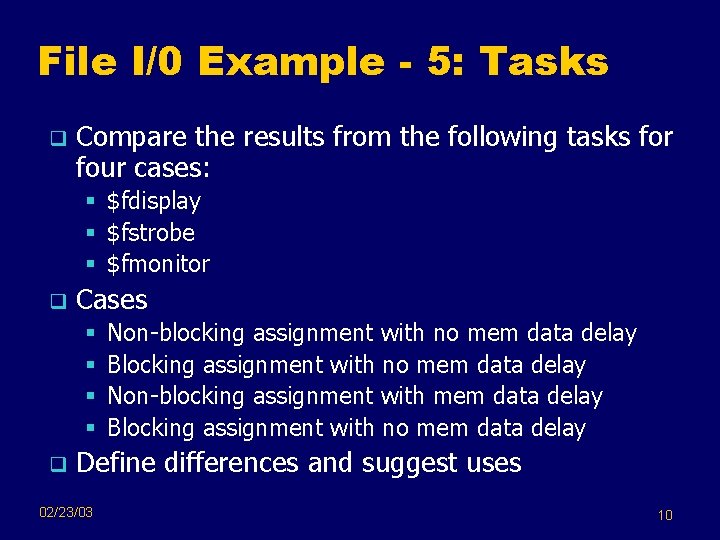

File I/0 Example - 5: Tasks q Compare the results from the following tasks for four cases: § $fdisplay § $fstrobe § $fmonitor q Cases § § q Non-blocking assignment with no mem data delay Blocking assignment with no mem data delay Non-blocking assignment with mem data delay Blocking assignment with no mem data delay Define differences and suggest uses 02/23/03 10

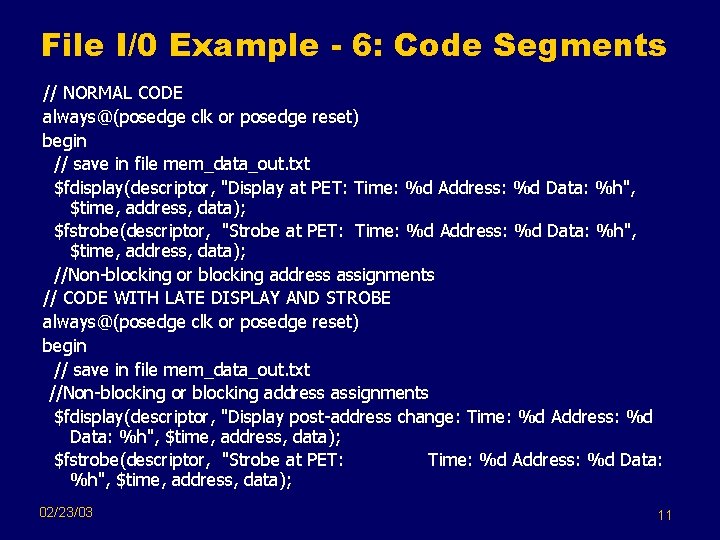

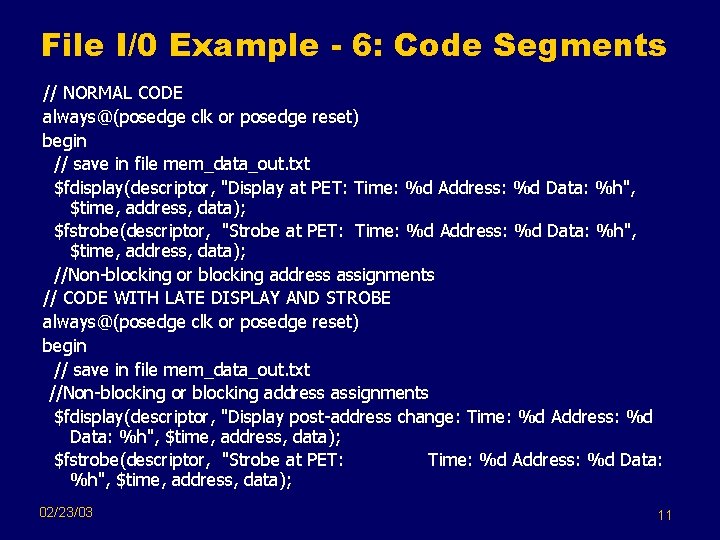

File I/0 Example - 6: Code Segments // NORMAL CODE always@(posedge clk or posedge reset) begin // save in file mem_data_out. txt $fdisplay(descriptor, "Display at PET: Time: %d Address: %d Data: %h", $time, address, data); $fstrobe(descriptor, "Strobe at PET: Time: %d Address: %d Data: %h", $time, address, data); //Non-blocking or blocking address assignments // CODE WITH LATE DISPLAY AND STROBE always@(posedge clk or posedge reset) begin // save in file mem_data_out. txt //Non-blocking or blocking address assignments $fdisplay(descriptor, "Display post-address change: Time: %d Address: %d Data: %h", $time, address, data); $fstrobe(descriptor, "Strobe at PET: Time: %d Address: %d Data: %h", $time, address, data); 02/23/03 11

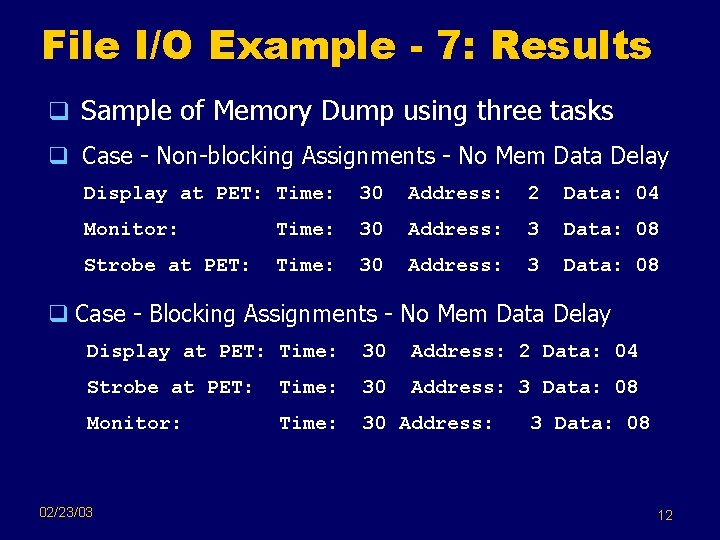

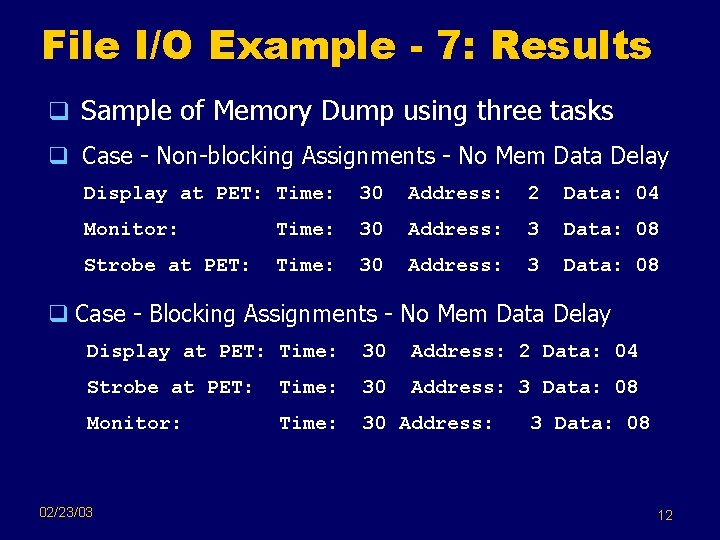

File I/O Example - 7: Results q Sample of Memory Dump using three tasks q Case - Non-blocking Assignments - No Mem Data Delay Display at PET: Time: 30 Address: 2 Data: 04 Monitor: Time: 30 Address: 3 Data: 08 Strobe at PET: Time: 30 Address: 3 Data: 08 q Case - Blocking Assignments - No Mem Data Delay Display at PET: Time: 30 Address: 2 Data: 04 Strobe at PET: Time: 30 Address: 3 Data: 08 Monitor: Time: 30 Address: 02/23/03 3 Data: 08 12

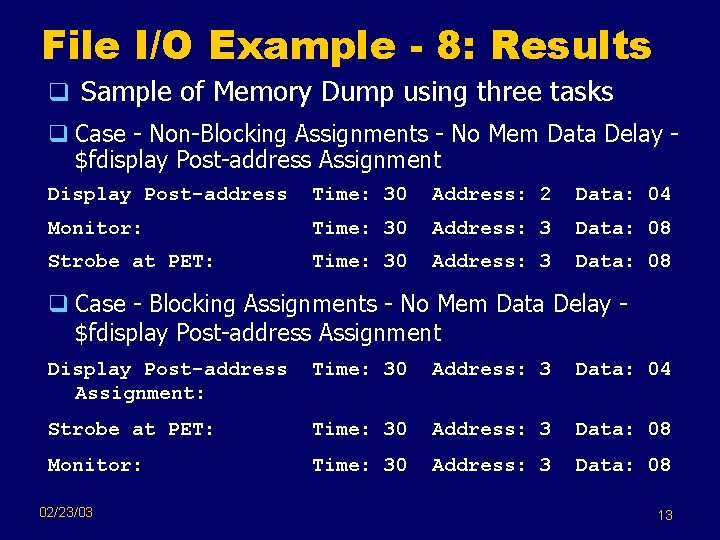

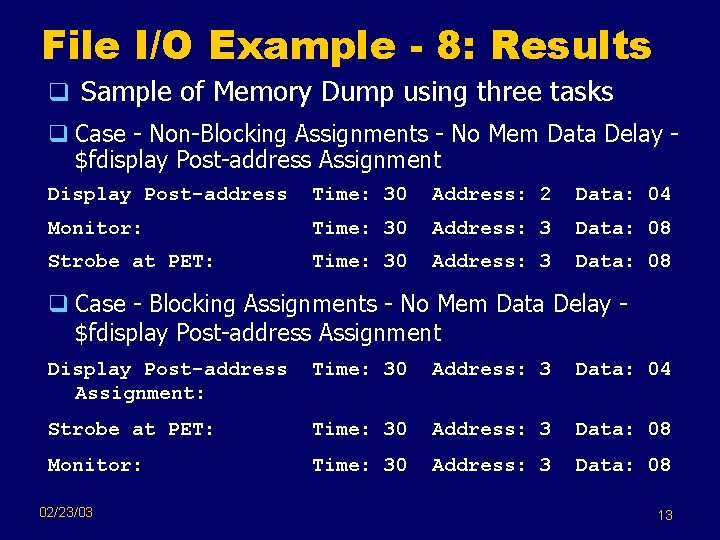

File I/O Example - 8: Results q Sample of Memory Dump using three tasks q Case - Non-Blocking Assignments - No Mem Data Delay $fdisplay Post-address Assignment Display Post-address Time: 30 Address: 2 Data: 04 Monitor: Time: 30 Address: 3 Data: 08 Strobe at PET: Time: 30 Address: 3 Data: 08 q Case - Blocking Assignments - No Mem Data Delay $fdisplay Post-address Assignment Display Post-address Assignment: Time: 30 Address: 3 Data: 04 Strobe at PET: Time: 30 Address: 3 Data: 08 Monitor: Time: 30 Address: 3 Data: 08 02/23/03 13

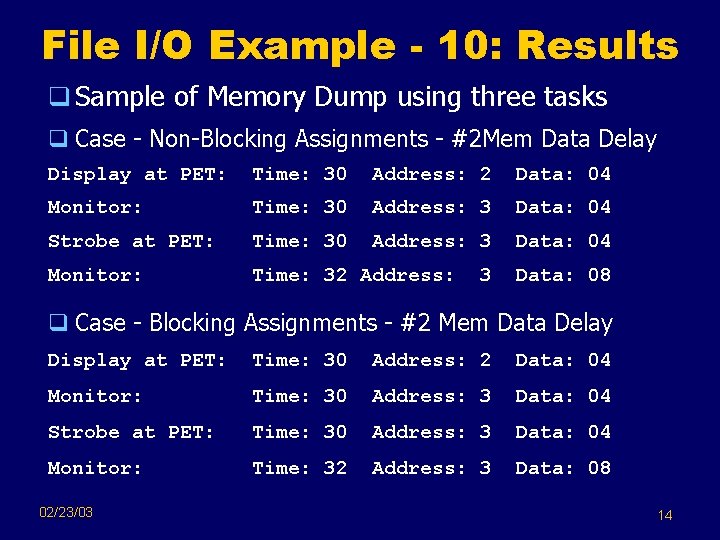

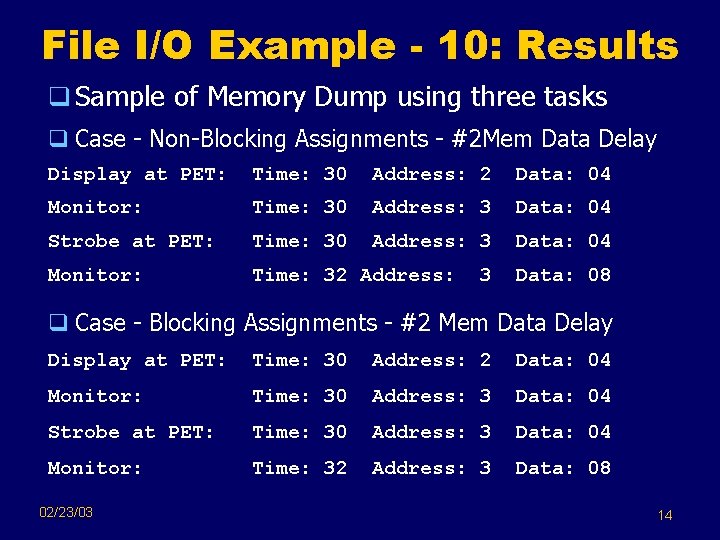

File I/O Example - 10: Results q Sample of Memory Dump using three tasks q Case - Non-Blocking Assignments - #2 Mem Data Delay Display at PET: Time: 30 Address: 2 Data: 04 Monitor: Time: 30 Address: 3 Data: 04 Strobe at PET: Time: 30 Address: 3 Data: 04 Monitor: Time: 32 Address: 3 Data: 08 q Case - Blocking Assignments - #2 Mem Data Delay Display at PET: Time: 30 Address: 2 Data: 04 Monitor: Time: 30 Address: 3 Data: 04 Strobe at PET: Time: 30 Address: 3 Data: 04 Monitor: Time: 32 Address: 3 Data: 08 02/23/03 14

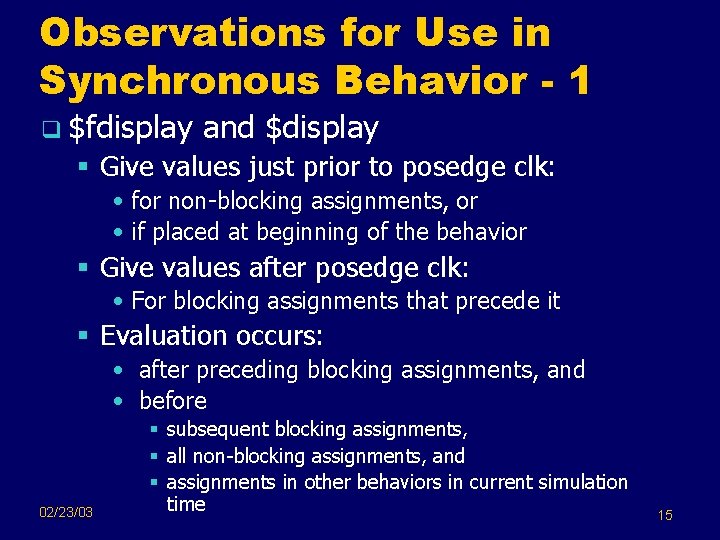

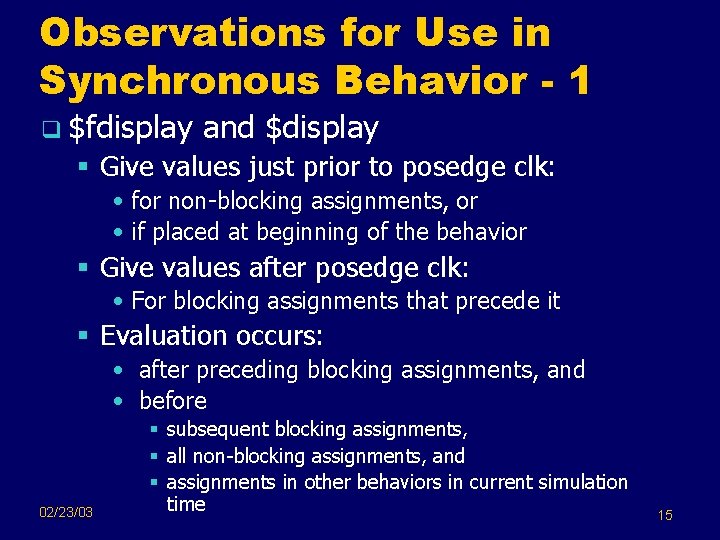

Observations for Use in Synchronous Behavior - 1 q $fdisplay and $display § Give values just prior to posedge clk: • for non-blocking assignments, or • if placed at beginning of the behavior § Give values after posedge clk: • For blocking assignments that precede it § Evaluation occurs: • after preceding blocking assignments, and • before 02/23/03 § subsequent blocking assignments, § all non-blocking assignments, and § assignments in other behaviors in current simulation time 15

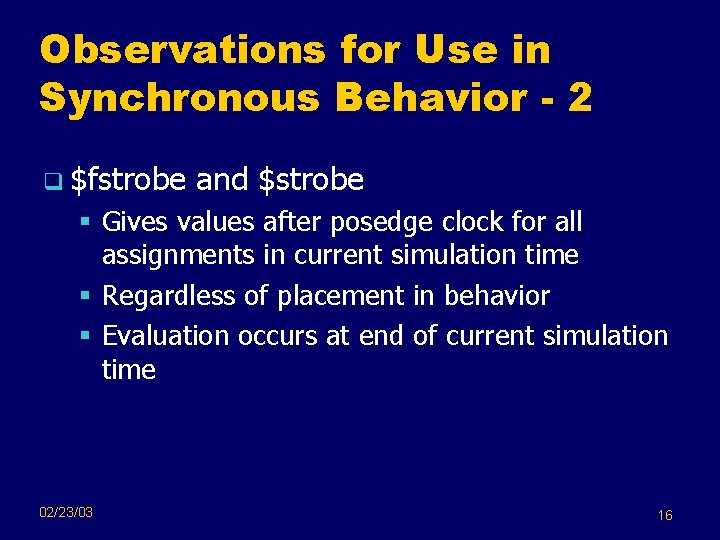

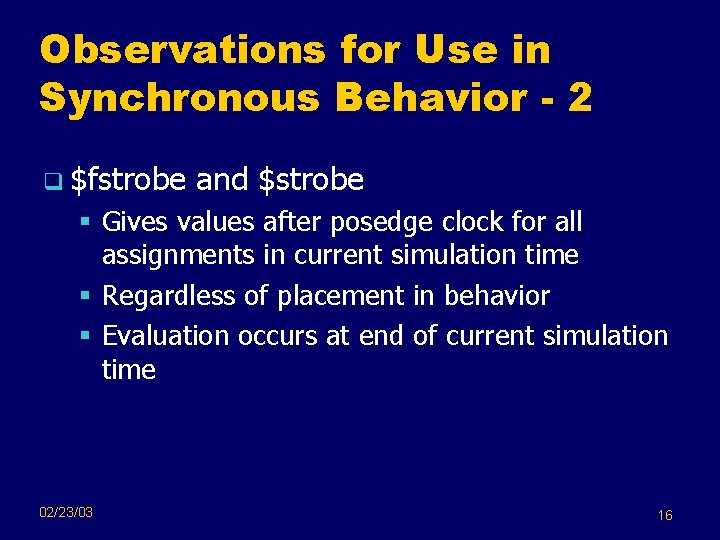

Observations for Use in Synchronous Behavior - 2 q $fstrobe and $strobe § Gives values after posedge clock for all assignments in current simulation time § Regardless of placement in behavior § Evaluation occurs at end of current simulation time 02/23/03 16

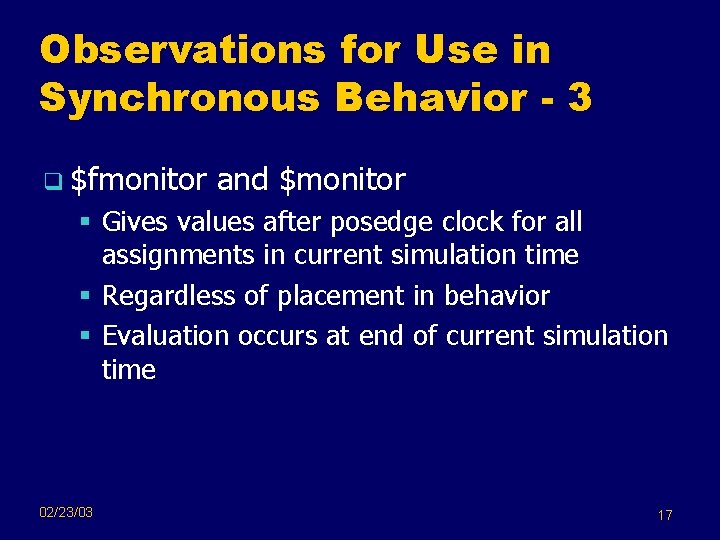

Observations for Use in Synchronous Behavior - 3 q $fmonitor and $monitor § Gives values after posedge clock for all assignments in current simulation time § Regardless of placement in behavior § Evaluation occurs at end of current simulation time 02/23/03 17

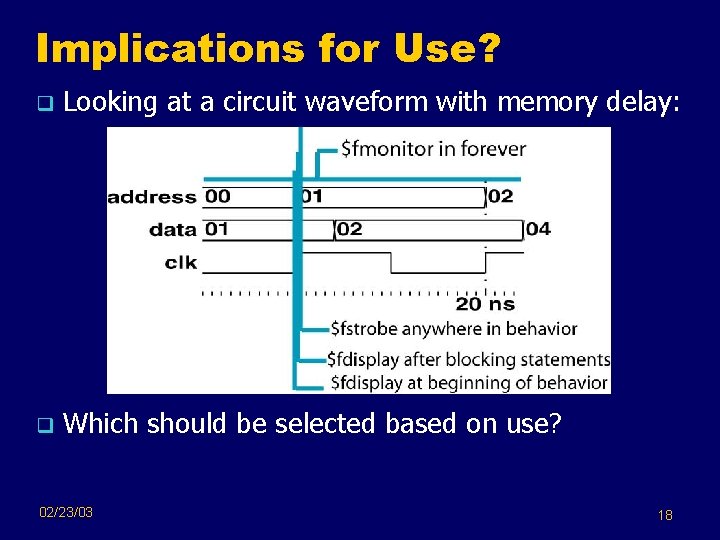

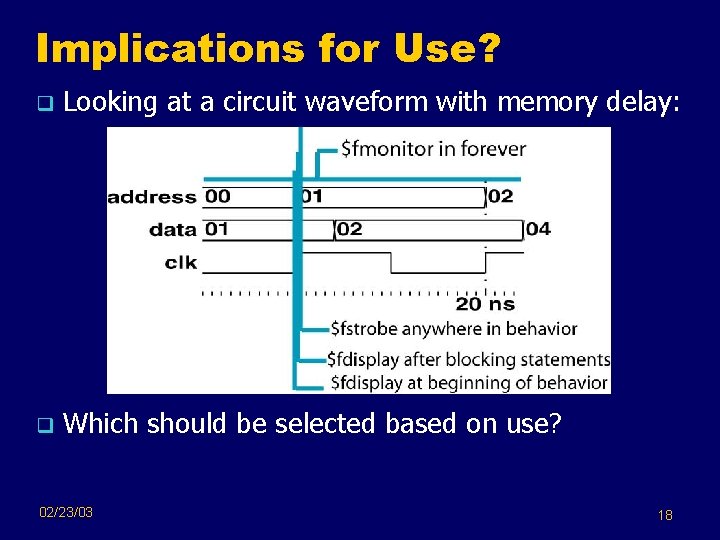

Implications for Use? q Looking at a circuit waveform with memory delay: q Which should be selected based on use? 02/23/03 18

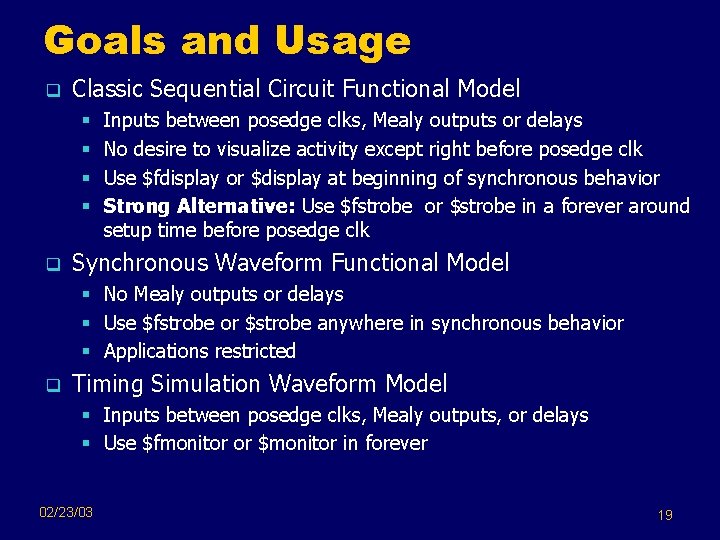

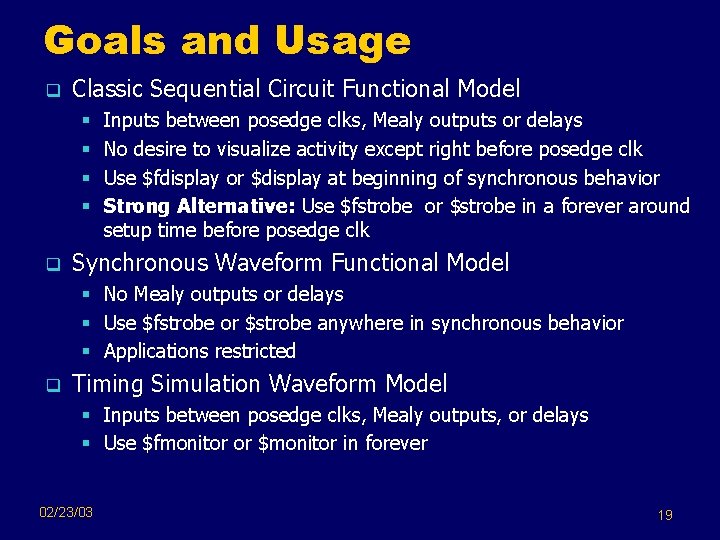

Goals and Usage q Classic Sequential Circuit Functional Model § § q Inputs between posedge clks, Mealy outputs or delays No desire to visualize activity except right before posedge clk Use $fdisplay or $display at beginning of synchronous behavior Strong Alternative: Use $fstrobe or $strobe in a forever around setup time before posedge clk Synchronous Waveform Functional Model § No Mealy outputs or delays § Use $fstrobe or $strobe anywhere in synchronous behavior § Applications restricted q Timing Simulation Waveform Model § Inputs between posedge clks, Mealy outputs, or delays § Use $fmonitor or $monitor in forever 02/23/03 19

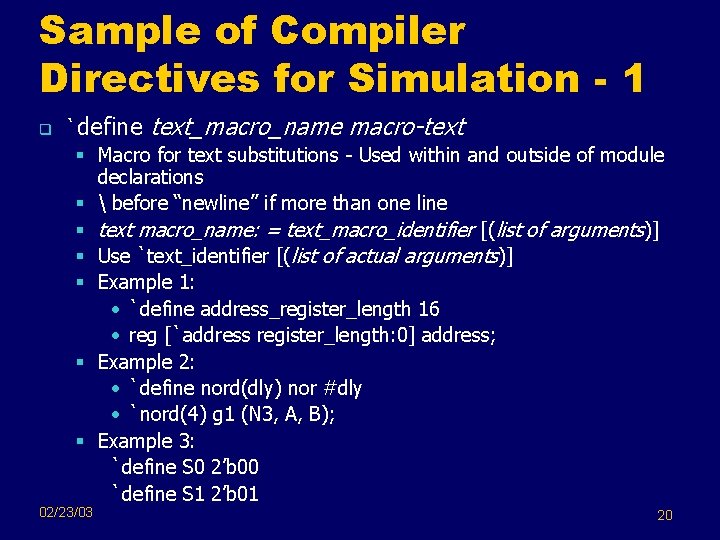

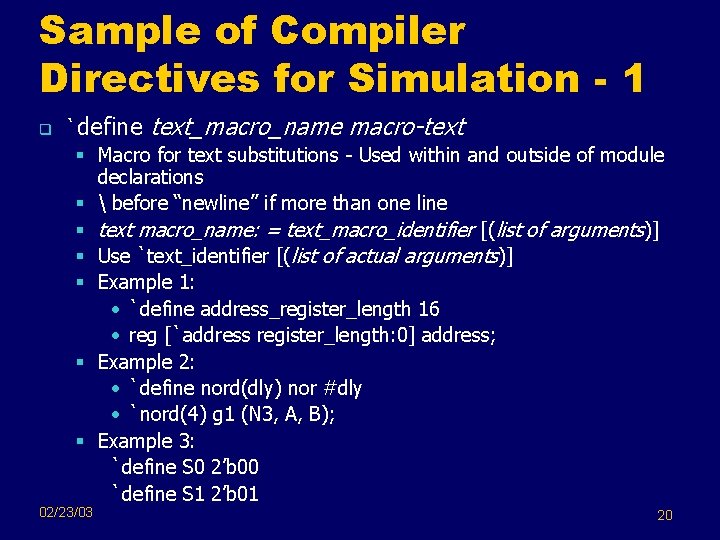

Sample of Compiler Directives for Simulation - 1 q `define text_macro_name macro-text § Macro for text substitutions - Used within and outside of module declarations § before “newline” if more than one line § text macro_name: = text_macro_identifier [(list of arguments)] § Use `text_identifier [(list of actual arguments)] § Example 1: • `define address_register_length 16 • reg [`address register_length: 0] address; § Example 2: • `define nord(dly) nor #dly • `nord(4) g 1 (N 3, A, B); § Example 3: `define S 0 2’b 00 `define S 1 2’b 01 02/23/03 20

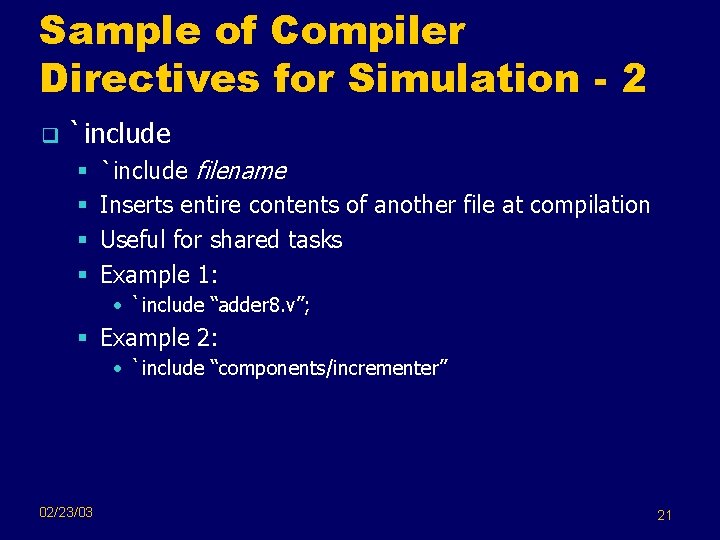

Sample of Compiler Directives for Simulation - 2 q `include § § `include filename Inserts entire contents of another file at compilation Useful for shared tasks Example 1: • `include “adder 8. v”; § Example 2: • `include “components/incrementer” 02/23/03 21

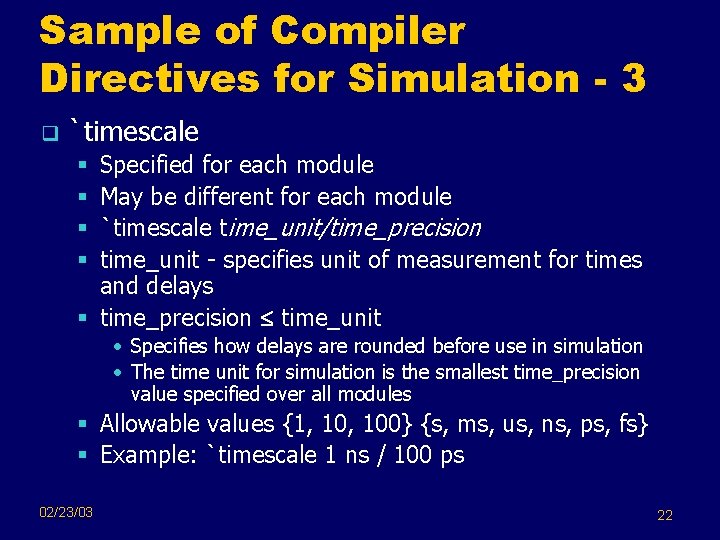

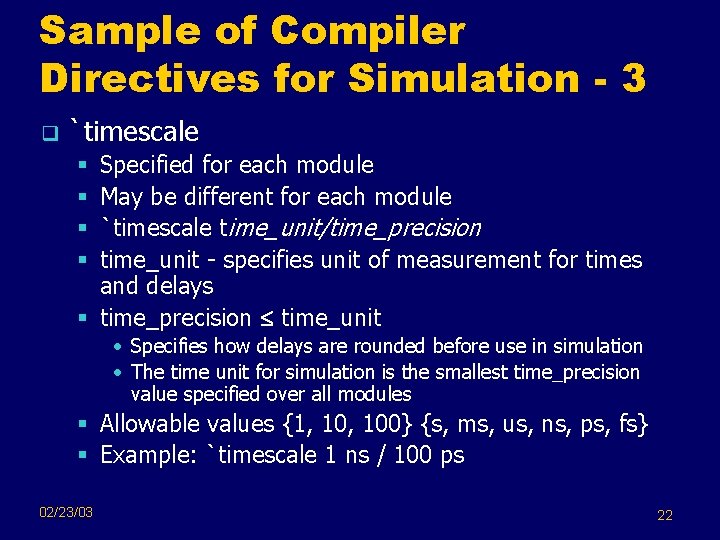

Sample of Compiler Directives for Simulation - 3 q `timescale Specified for each module May be different for each module `timescale time_unit/time_precision time_unit - specifies unit of measurement for times and delays § time_precision time_unit § § • Specifies how delays are rounded before use in simulation • The time unit for simulation is the smallest time_precision value specified over all modules § Allowable values {1, 100} {s, ms, us, ns, ps, fs} § Example: `timescale 1 ns / 100 ps 02/23/03 22

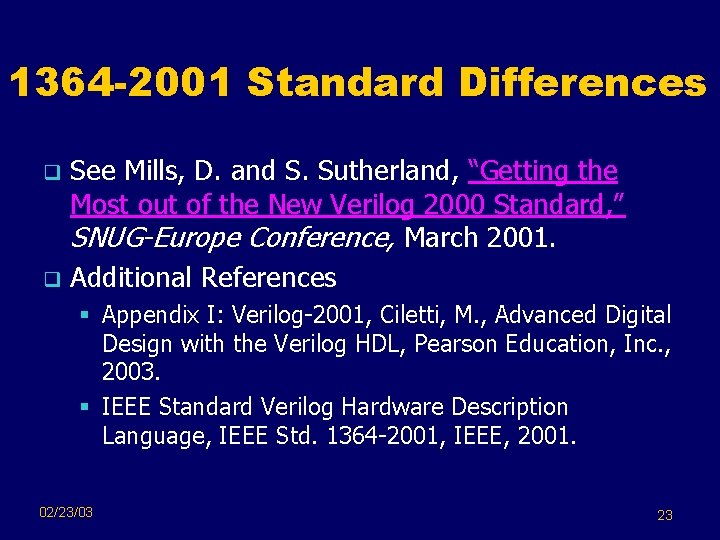

1364 -2001 Standard Differences See Mills, D. and S. Sutherland, “Getting the Most out of the New Verilog 2000 Standard, ” SNUG-Europe Conference, March 2001. q Additional References q § Appendix I: Verilog-2001, Ciletti, M. , Advanced Digital Design with the Verilog HDL, Pearson Education, Inc. , 2003. § IEEE Standard Verilog Hardware Description Language, IEEE Std. 1364 -2001, IEEE, 2001. 02/23/03 23