ECE 232 Hardware Organization and Design Part 6

- Slides: 21

ECE 232: Hardware Organization and Design Part 6: MIPS Instructions II http: //www. ecs. umass. edu/ece 232/ Adapted from Computer Organization and Design, Patterson & Hennessy, UCB

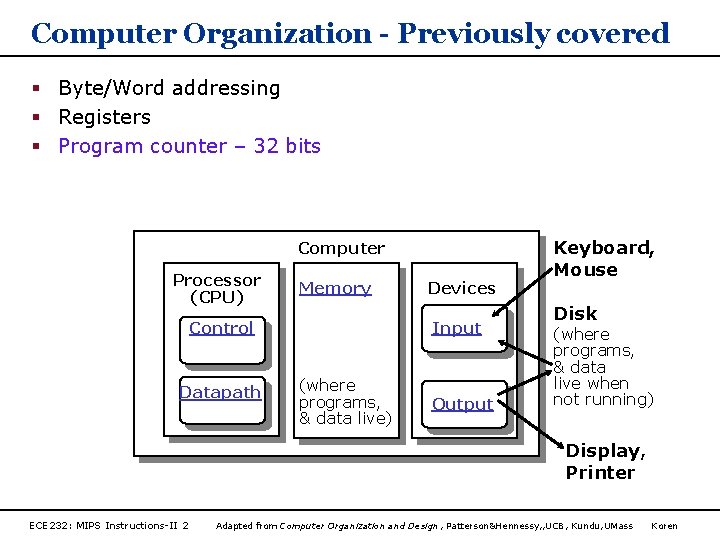

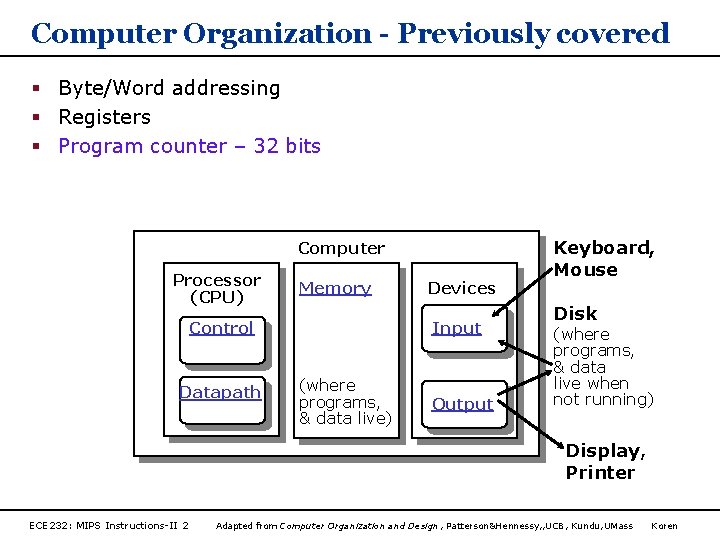

Computer Organization - Previously covered § Byte/Word addressing § Registers § Program counter – 32 bits Computer Processor (CPU) Memory Control Datapath Devices Input (where programs, & data live) Output Keyboard, Mouse Disk (where programs, & data live when not running) Display, Printer ECE 232: MIPS Instructions-II 2 Adapted from Computer Organization and Design, Patterson&Hennessy, , UCB, Kundu, UMass Koren

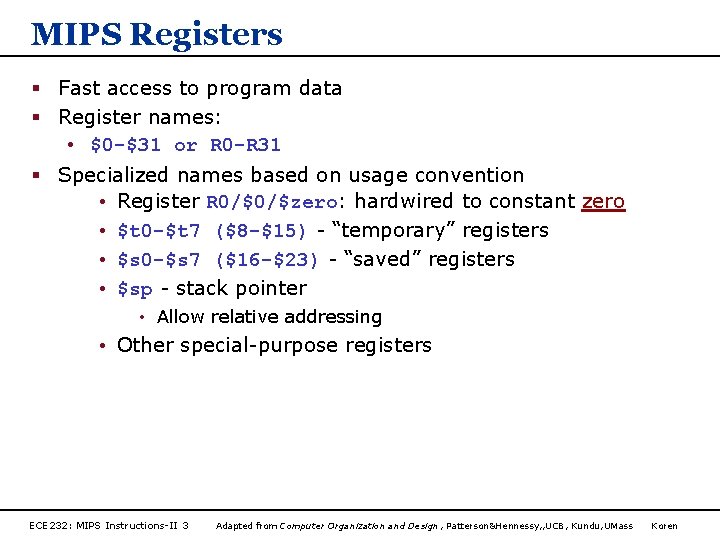

MIPS Registers § Fast access to program data § Register names: • $0 -$31 or R 0 -R 31 § Specialized names based on usage convention • Register R 0/$0/$zero: hardwired to constant zero • $t 0 -$t 7 ($8 -$15) - “temporary” registers • $s 0 -$s 7 ($16 -$23) - “saved” registers • $sp - stack pointer • Allow relative addressing • Other special-purpose registers ECE 232: MIPS Instructions-II 3 Adapted from Computer Organization and Design, Patterson&Hennessy, , UCB, Kundu, UMass Koren

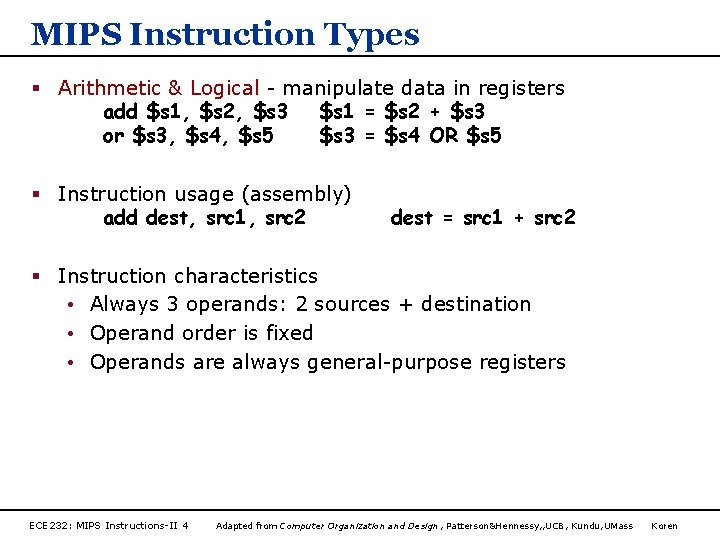

MIPS Instruction Types § Arithmetic & Logical - manipulate data in registers add $s 1, $s 2, $s 3 $s 1 = $s 2 + $s 3 or $s 3, $s 4, $s 5 $s 3 = $s 4 OR $s 5 § Instruction usage (assembly) add dest, src 1, src 2 dest = src 1 + src 2 § Instruction characteristics • Always 3 operands: 2 sources + destination • Operand order is fixed • Operands are always general-purpose registers ECE 232: MIPS Instructions-II 4 Adapted from Computer Organization and Design, Patterson&Hennessy, , UCB, Kundu, UMass Koren

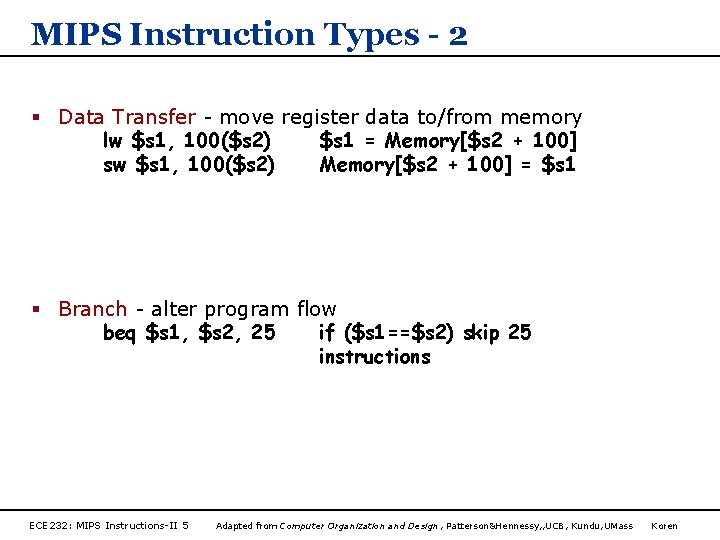

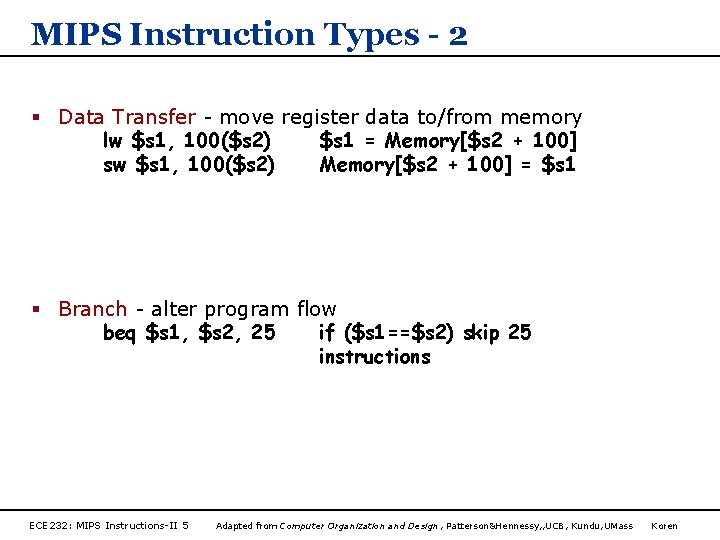

MIPS Instruction Types - 2 § Data Transfer - move register data to/from memory lw $s 1, 100($s 2) $s 1 = Memory[$s 2 + 100] sw $s 1, 100($s 2) Memory[$s 2 + 100] = $s 1 § Branch - alter program flow beq $s 1, $s 2, 25 if ($s 1==$s 2) skip 25 instructions ECE 232: MIPS Instructions-II 5 Adapted from Computer Organization and Design, Patterson&Hennessy, , UCB, Kundu, UMass Koren

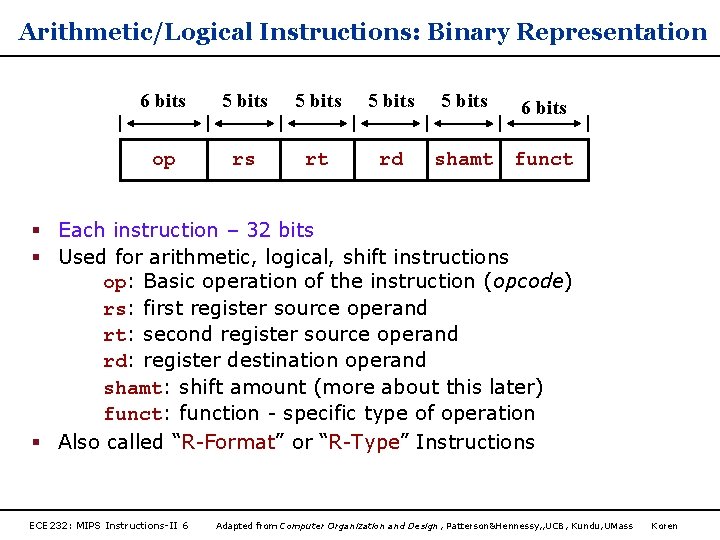

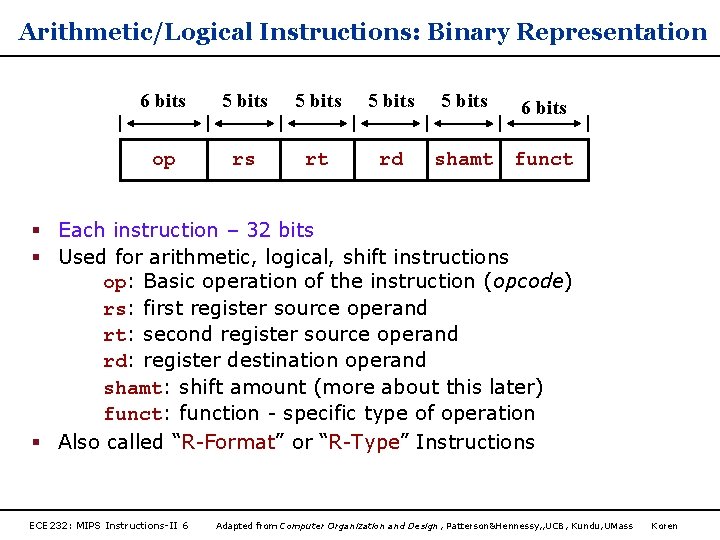

Arithmetic/Logical Instructions: Binary Representation 6 bits 5 bits 6 bits op rs rt rd shamt funct § Each instruction – 32 bits § Used for arithmetic, logical, shift instructions op: Basic operation of the instruction (opcode) rs: first register source operand rt: second register source operand rd: register destination operand shamt: shift amount (more about this later) funct: function - specific type of operation § Also called “R-Format” or “R-Type” Instructions ECE 232: MIPS Instructions-II 6 Adapted from Computer Organization and Design, Patterson&Hennessy, , UCB, Kundu, UMass Koren

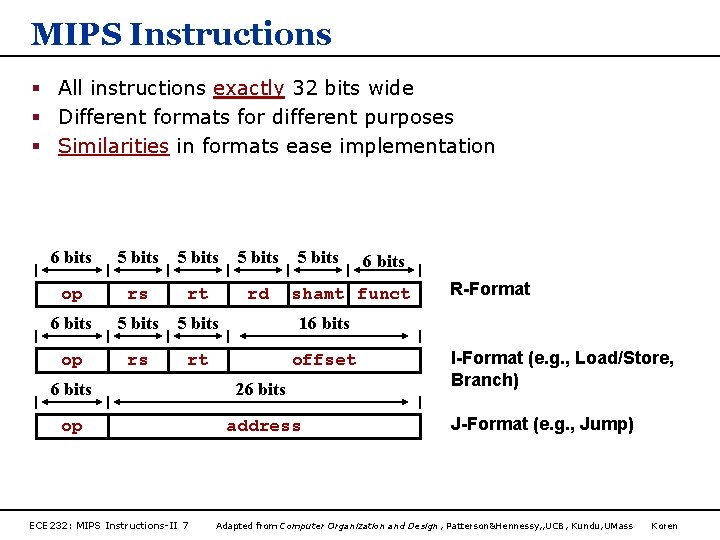

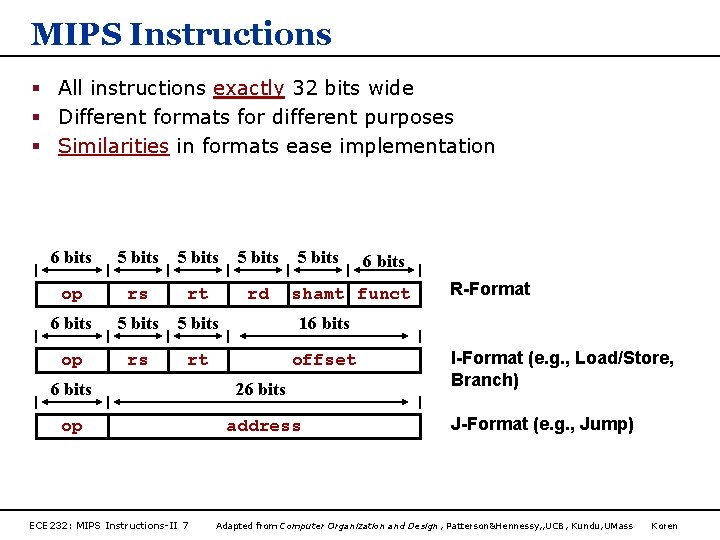

MIPS Instructions § All instructions exactly 32 bits wide § Different formats for different purposes § Similarities in formats ease implementation 6 bits 5 bits op rs rt rd 6 bits 5 bits 16 bits op rs rt offset shamt funct 6 bits 26 bits op address ECE 232: MIPS Instructions-II 7 6 bits R-Format I-Format (e. g. , Load/Store, Branch) J-Format (e. g. , Jump) Adapted from Computer Organization and Design, Patterson&Hennessy, , UCB, Kundu, UMass Koren

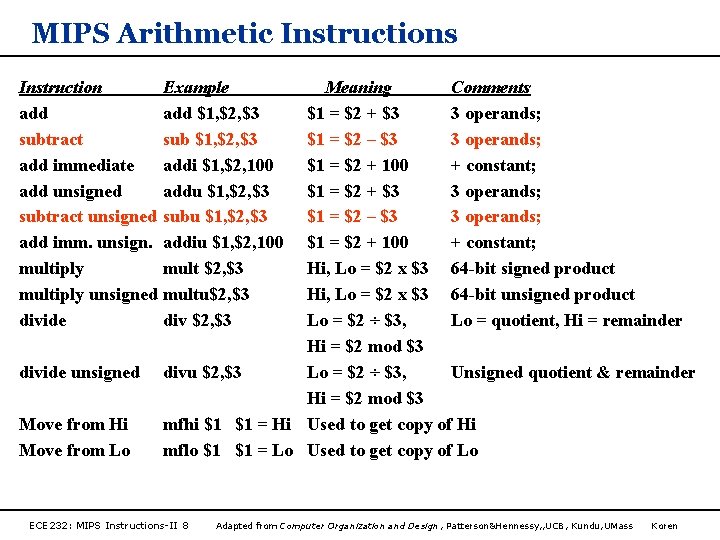

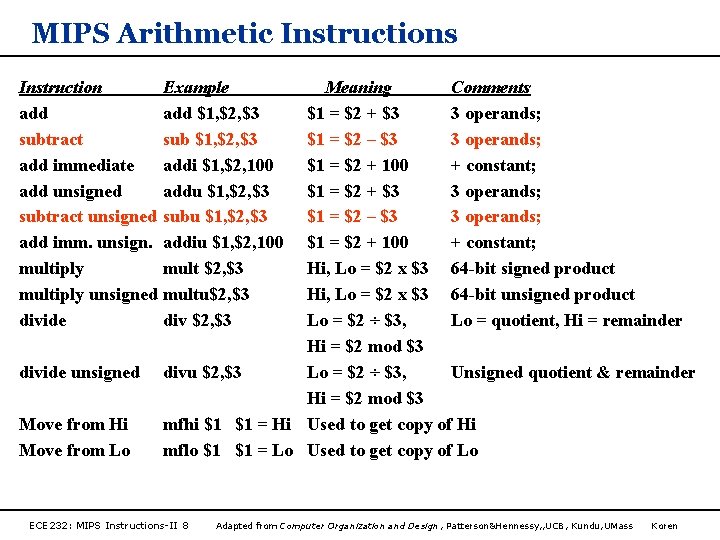

MIPS Arithmetic Instructions Instruction add subtract add immediate add unsigned subtract unsigned add imm. unsign. multiply unsigned divide unsigned Move from Hi Move from Lo Example add $1, $2, $3 sub $1, $2, $3 addi $1, $2, 100 addu $1, $2, $3 subu $1, $2, $3 addiu $1, $2, 100 mult $2, $3 multu$2, $3 div $2, $3 Meaning Comments $1 = $2 + $3 3 operands; $1 = $2 – $3 3 operands; $1 = $2 + 100 + constant; Hi, Lo = $2 x $3 64 -bit signed product Hi, Lo = $2 x $3 64 -bit unsigned product Lo = $2 ÷ $3, Lo = quotient, Hi = remainder Hi = $2 mod $3 divu $2, $3 Lo = $2 ÷ $3, Unsigned quotient & remainder Hi = $2 mod $3 mfhi $1 $1 = Hi Used to get copy of Hi mflo $1 $1 = Lo Used to get copy of Lo ECE 232: MIPS Instructions-II 8 Adapted from Computer Organization and Design, Patterson&Hennessy, , UCB, Kundu, UMass Koren

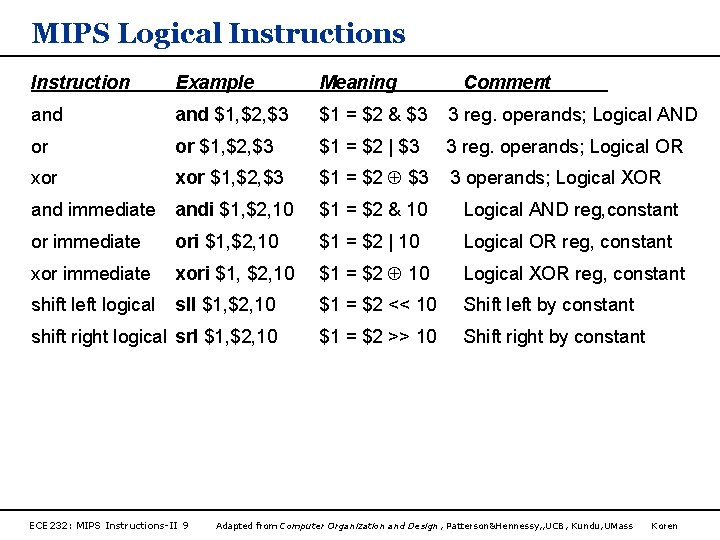

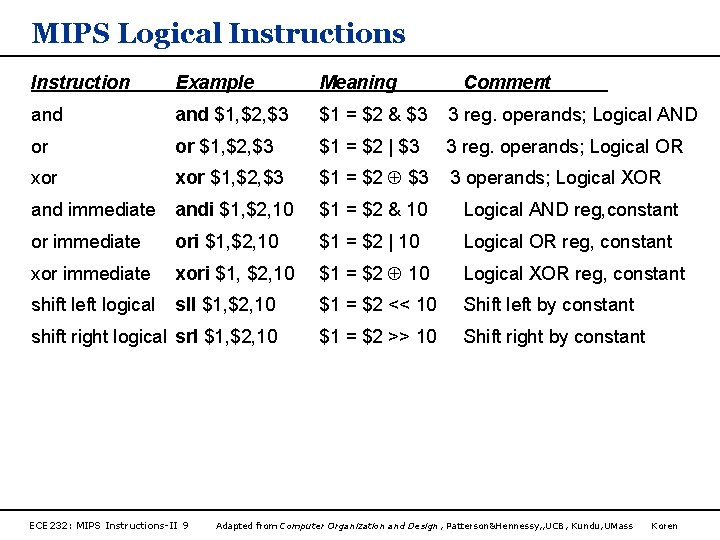

MIPS Logical Instructions Instruction Example Meaning and $1, $2, $3 $1 = $2 & $3 3 reg. operands; Logical AND or or $1, $2, $3 $1 = $2 | $3 3 reg. operands; Logical OR xor $1, $2, $3 $1 = $2 Å $3 3 operands; Logical XOR and immediate andi $1, $2, 10 $1 = $2 & 10 Logical AND reg, constant or immediate ori $1, $2, 10 $1 = $2 | 10 Logical OR reg, constant xor immediate xori $1, $2, 10 $1 = $2 Å 10 Logical XOR reg, constant shift left logical sll $1, $2, 10 $1 = $2 << 10 Shift left by constant shift right logical srl $1, $2, 10 $1 = $2 >> 10 Shift right by constant ECE 232: MIPS Instructions-II 9 Comment Adapted from Computer Organization and Design, Patterson&Hennessy, , UCB, Kundu, UMass Koren

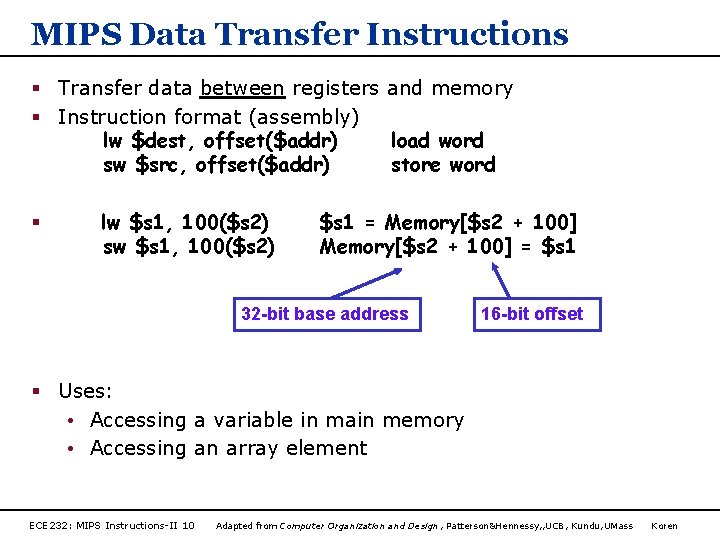

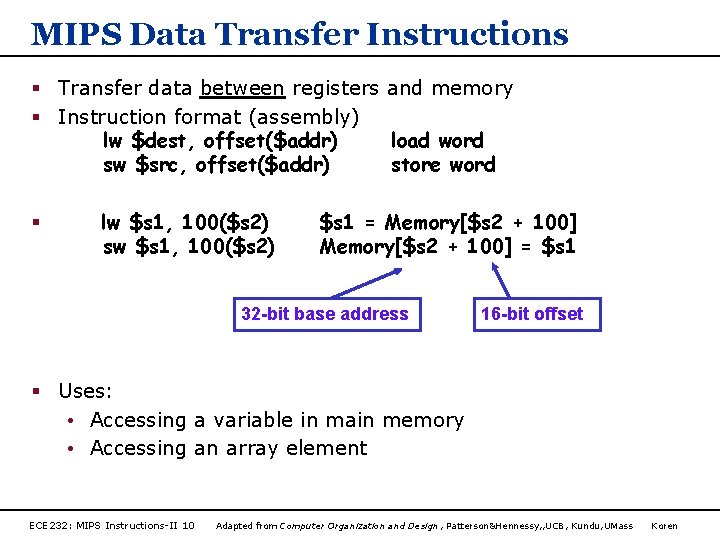

MIPS Data Transfer Instructions § Transfer data between registers and memory § Instruction format (assembly) lw $dest, offset($addr) load word sw $src, offset($addr) store word § lw $s 1, 100($s 2) sw $s 1, 100($s 2) $s 1 = Memory[$s 2 + 100] = $s 1 32 -bit base address 16 -bit offset § Uses: • Accessing a variable in main memory • Accessing an array element ECE 232: MIPS Instructions-II 10 Adapted from Computer Organization and Design, Patterson&Hennessy, , UCB, Kundu, UMass Koren

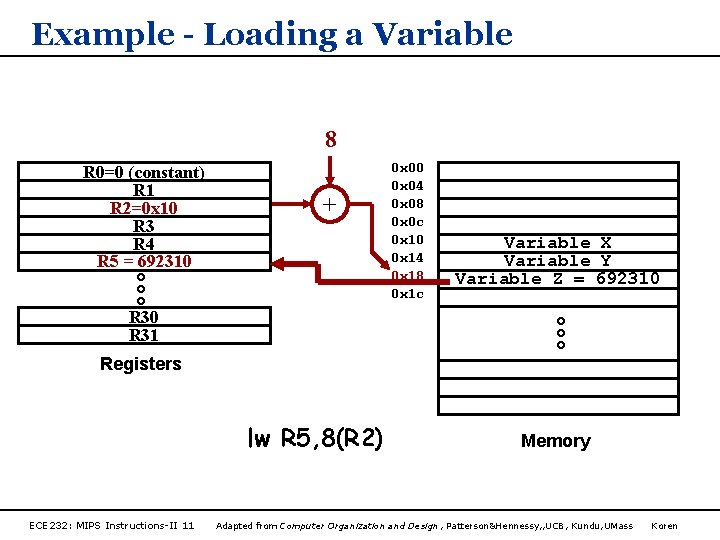

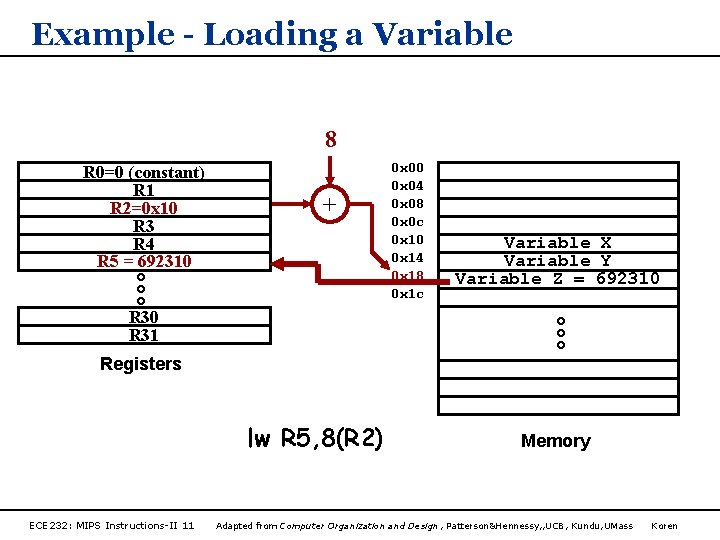

Example - Loading a Variable 8 R 0=0 (constant) R 1 R 2=0 x 10 R 3 R 4 R 5 = 692310 + 0 x 00 0 x 04 0 x 08 0 x 0 c 0 x 10 0 x 14 0 x 18 0 x 1 c Variable X Variable Y Variable Z = 692310 R 31 Registers lw R 5, 8(R 2) ECE 232: MIPS Instructions-II 11 Memory Adapted from Computer Organization and Design, Patterson&Hennessy, , UCB, Kundu, UMass Koren

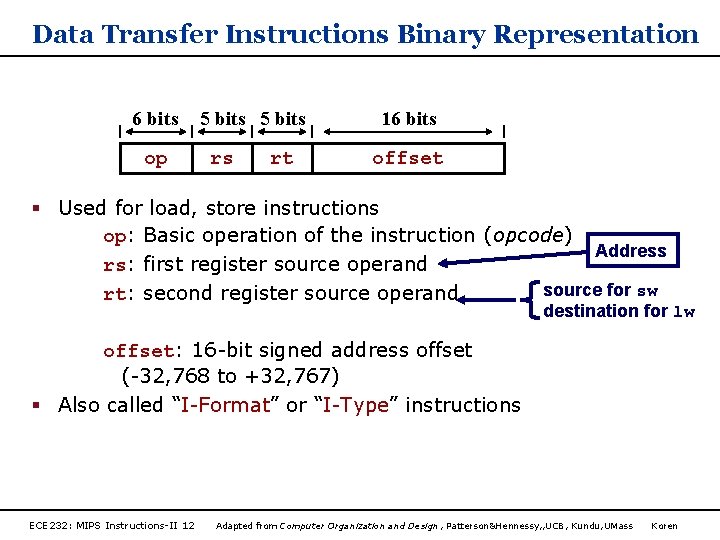

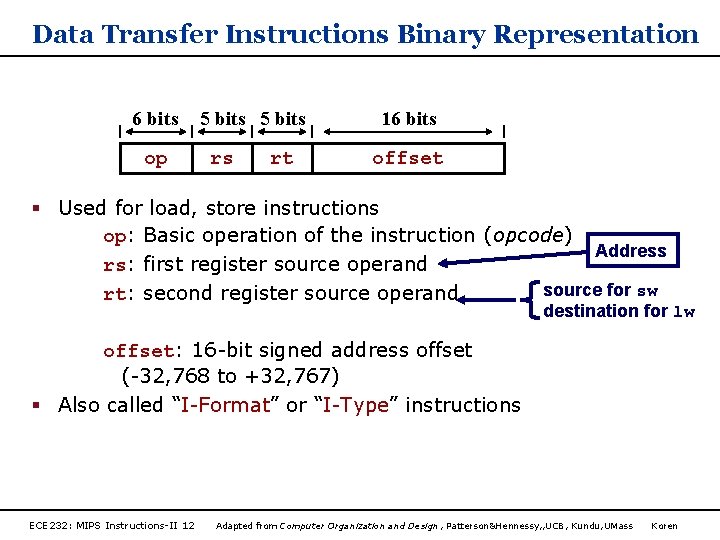

Data Transfer Instructions Binary Representation 6 bits op 5 bits rs rt 16 bits offset § Used for load, store instructions op: Basic operation of the instruction (opcode) Address rs: first register source operand source for sw rt: second register source operand destination for lw offset: 16 -bit signed address offset (-32, 768 to +32, 767) § Also called “I-Format” or “I-Type” instructions ECE 232: MIPS Instructions-II 12 Adapted from Computer Organization and Design, Patterson&Hennessy, , UCB, Kundu, UMass Koren

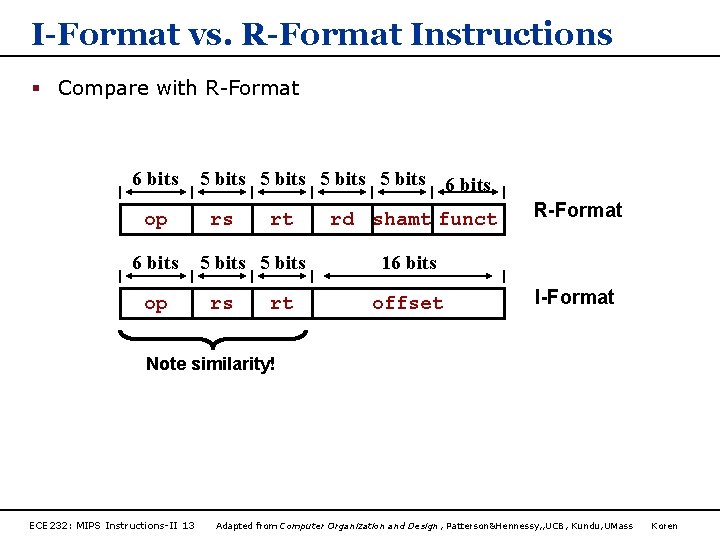

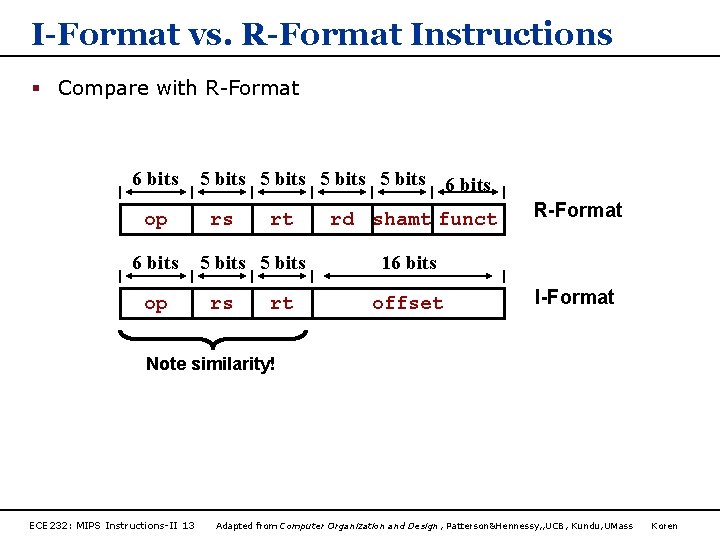

I-Format vs. R-Format Instructions § Compare with R-Format 6 bits op 5 bits 6 bits rs rt 5 bits rs rt rd shamt funct R-Format 16 bits offset I-Format Note similarity! ECE 232: MIPS Instructions-II 13 Adapted from Computer Organization and Design, Patterson&Hennessy, , UCB, Kundu, UMass Koren

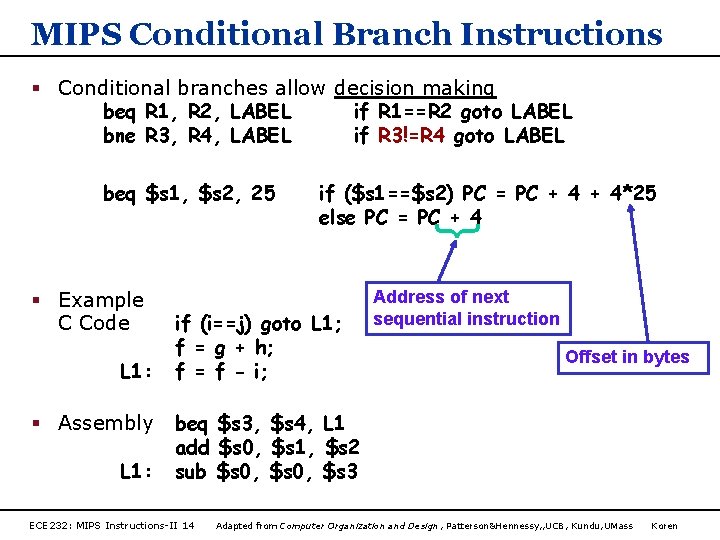

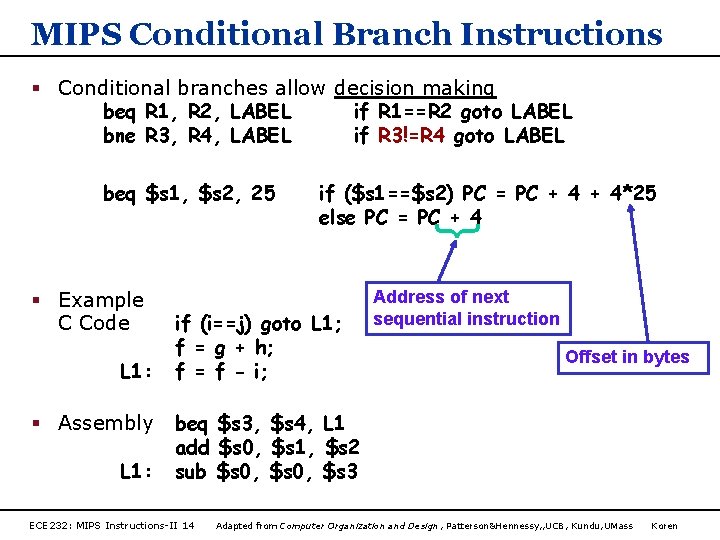

MIPS Conditional Branch Instructions § Conditional branches allow decision making beq R 1, R 2, LABEL if R 1==R 2 goto LABEL bne R 3, R 4, LABEL if R 3!=R 4 goto LABEL if ($s 1==$s 2) PC = PC + 4*25 else PC = PC + 4 { beq $s 1, $s 2, 25 § Example C Code L 1: § Assembly L 1: if (i==j) goto L 1; f = g + h; f = f - i; Address of next sequential instruction Offset in bytes beq $s 3, $s 4, L 1 add $s 0, $s 1, $s 2 sub $s 0, $s 3 ECE 232: MIPS Instructions-II 14 Adapted from Computer Organization and Design, Patterson&Hennessy, , UCB, Kundu, UMass Koren

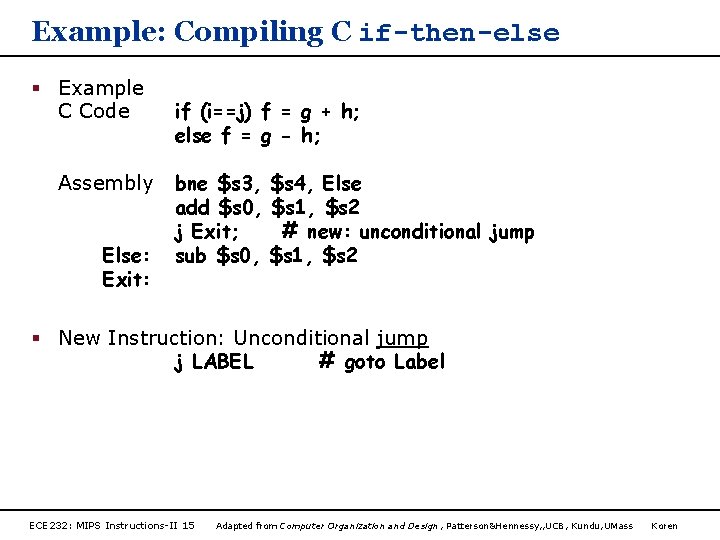

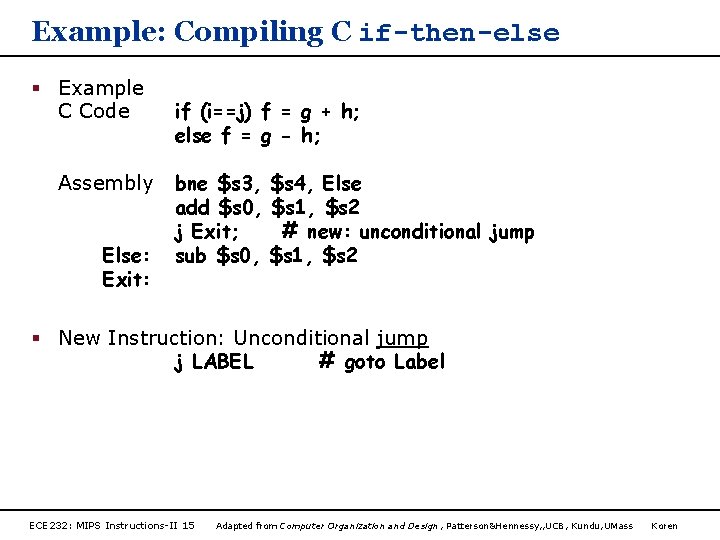

Example: Compiling C if-then-else § Example C Code Assembly Else: Exit: if (i==j) f = g + h; else f = g - h; bne $s 3, add $s 0, j Exit; sub $s 0, $s 4, Else $s 1, $s 2 # new: unconditional jump $s 1, $s 2 § New Instruction: Unconditional jump j LABEL # goto Label ECE 232: MIPS Instructions-II 15 Adapted from Computer Organization and Design, Patterson&Hennessy, , UCB, Kundu, UMass Koren

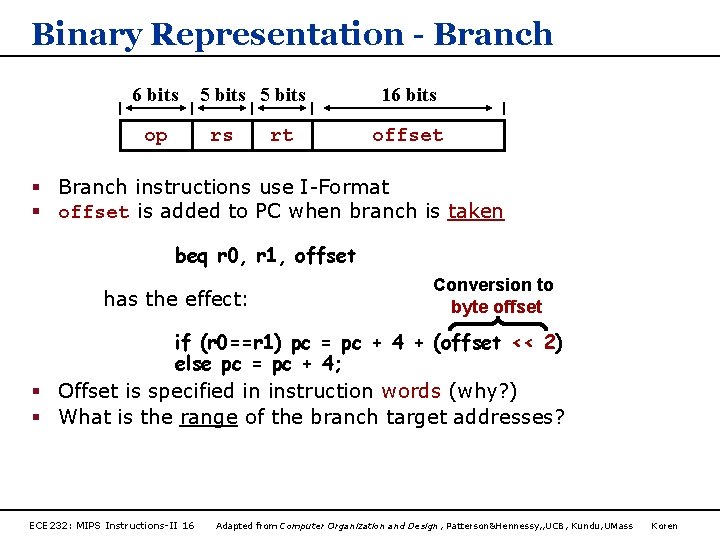

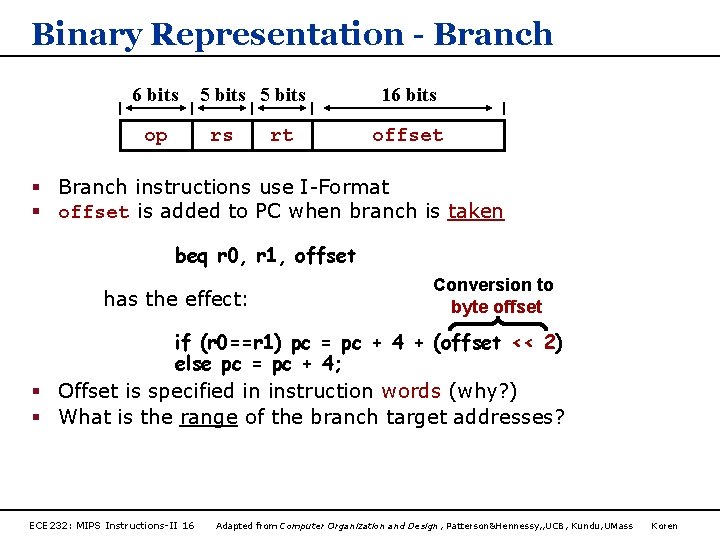

Binary Representation - Branch 6 bits op 5 bits rs rt 16 bits offset § Branch instructions use I-Format § offset is added to PC when branch is taken beq r 0, r 1, offset has the effect: Conversion to byte offset if (r 0==r 1) pc = pc + 4 + (offset << 2) else pc = pc + 4; § Offset is specified in instruction words (why? ) § What is the range of the branch target addresses? ECE 232: MIPS Instructions-II 16 Adapted from Computer Organization and Design, Patterson&Hennessy, , UCB, Kundu, UMass Koren

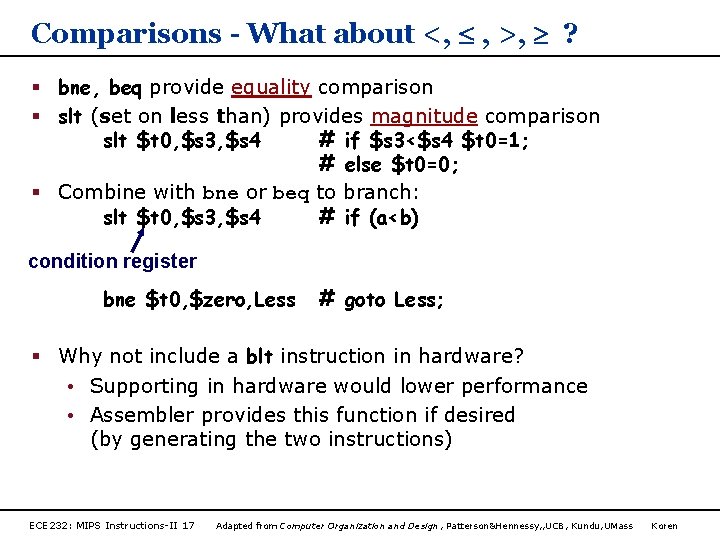

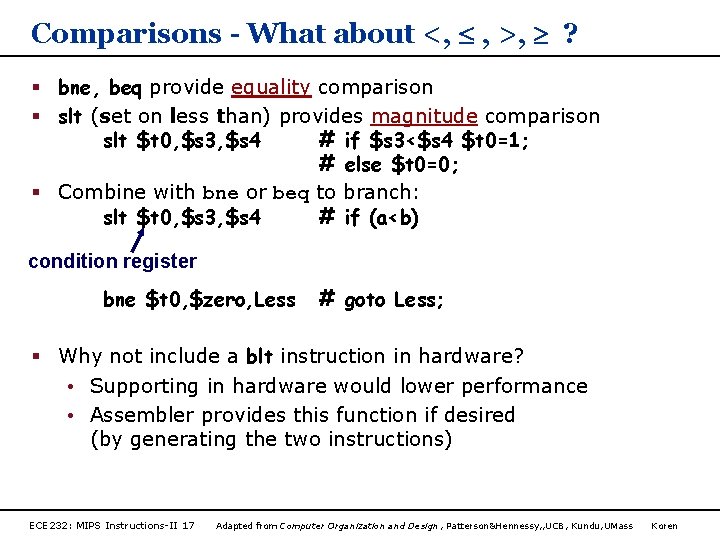

Comparisons - What about <, , >, ? § bne, beq provide equality comparison § slt (set on less than) provides magnitude comparison slt $t 0, $s 3, $s 4 # if $s 3<$s 4 $t 0=1; # else $t 0=0; § Combine with bne or beq to branch: slt $t 0, $s 3, $s 4 # if (a<b) condition register bne $t 0, $zero, Less # goto Less; § Why not include a blt instruction in hardware? • Supporting in hardware would lower performance • Assembler provides this function if desired (by generating the two instructions) ECE 232: MIPS Instructions-II 17 Adapted from Computer Organization and Design, Patterson&Hennessy, , UCB, Kundu, UMass Koren

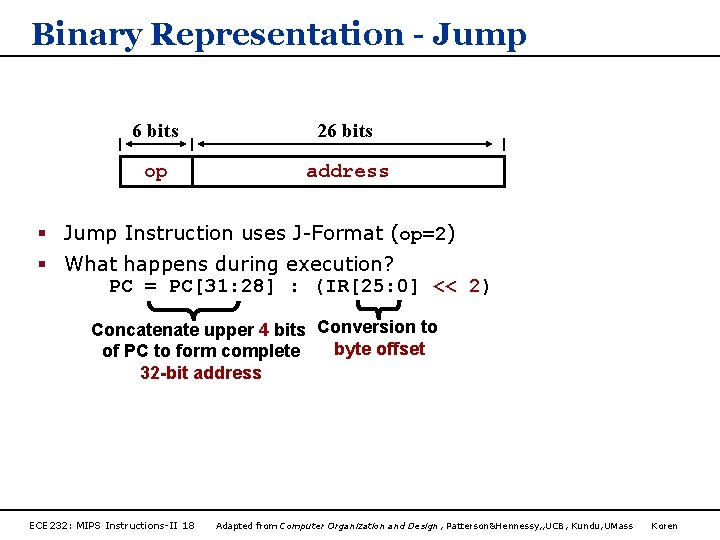

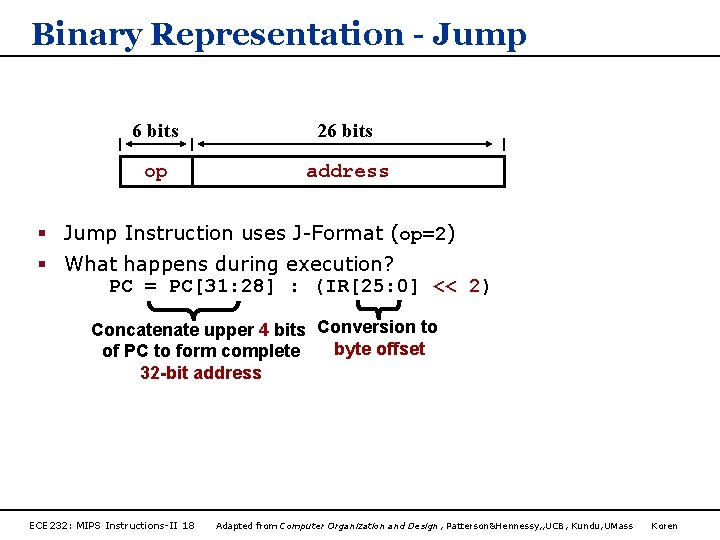

Binary Representation - Jump 6 bits 26 bits op address § Jump Instruction uses J-Format (op=2) § What happens during execution? PC = PC[31: 28] : (IR[25: 0] << 2) Concatenate upper 4 bits Conversion to byte offset of PC to form complete 32 -bit address ECE 232: MIPS Instructions-II 18 Adapted from Computer Organization and Design, Patterson&Hennessy, , UCB, Kundu, UMass Koren

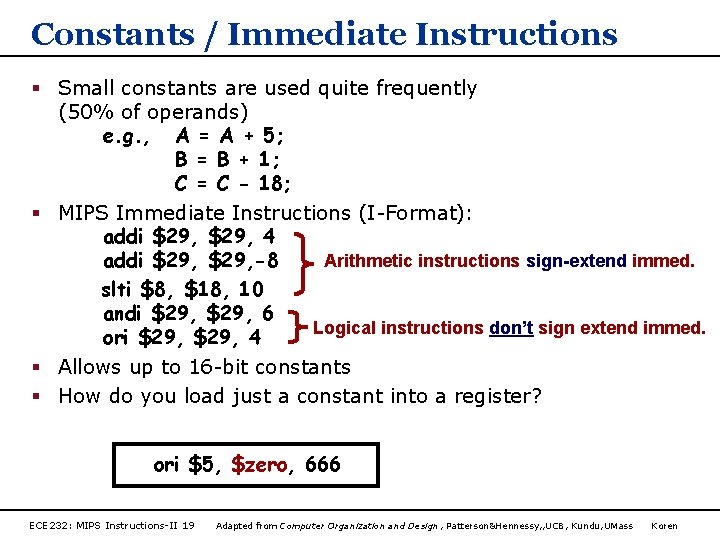

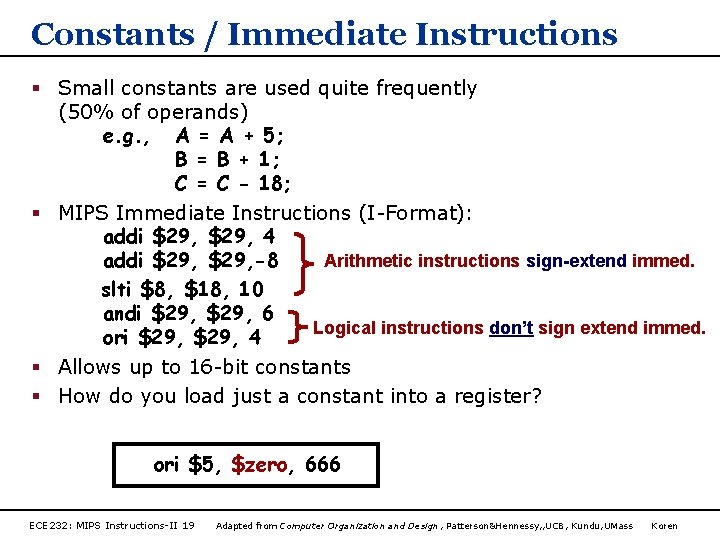

Constants / Immediate Instructions § Small constants are used quite frequently (50% of operands) e. g. , A = A + 5; B = B + 1; C = C - 18; § MIPS Immediate Instructions (I-Format): addi $29, 4 Arithmetic instructions sign-extend immed. addi $29, -8 slti $8, $18, 10 andi $29, 6 Logical instructions don’t sign extend immed. ori $29, 4 § Allows up to 16 -bit constants § How do you load just a constant into a register? ori $5, $zero, 666 ECE 232: MIPS Instructions-II 19 Adapted from Computer Organization and Design, Patterson&Hennessy, , UCB, Kundu, UMass Koren

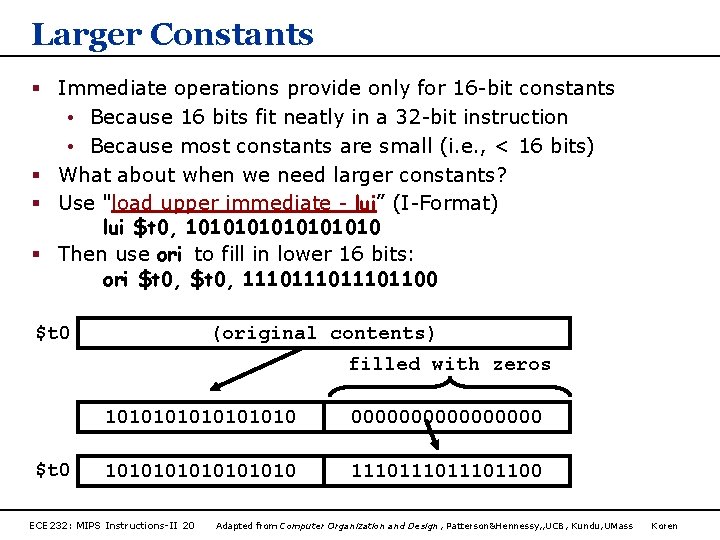

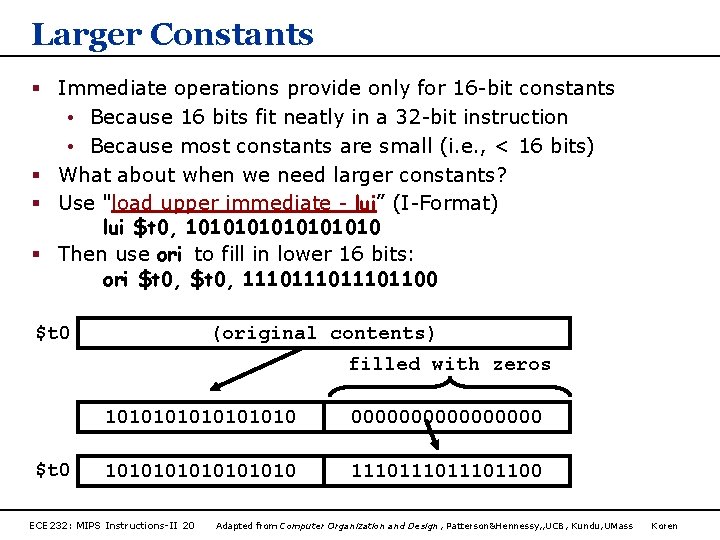

Larger Constants § Immediate operations provide only for 16 -bit constants • Because 16 bits fit neatly in a 32 -bit instruction • Because most constants are small (i. e. , < 16 bits) § What about when we need larger constants? § Use "load upper immediate - lui” (I-Format) lui $t 0, 10101010 § Then use ori to fill in lower 16 bits: ori $t 0, 111011101100 (original contents) $t 0 filled with zeros $t 0 10101010 00000000 10101010 111011101100 00000000 ECE 232: MIPS Instructions-II 20 Adapted from Computer Organization and Design, Patterson&Hennessy, , UCB, Kundu, UMass Koren

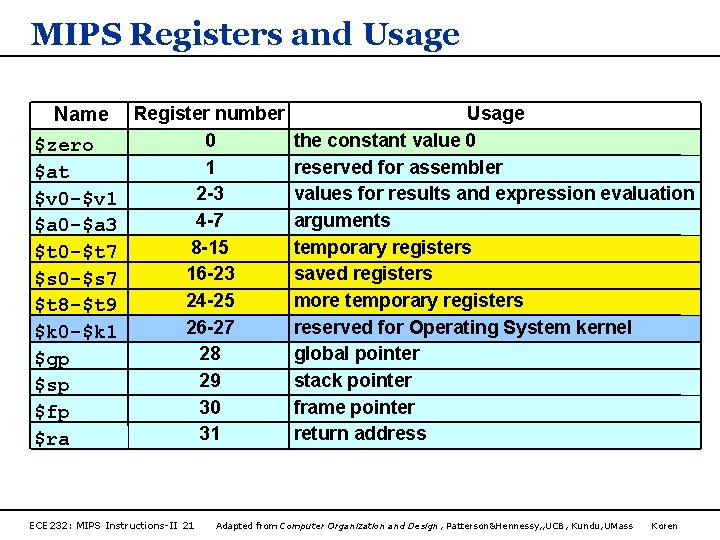

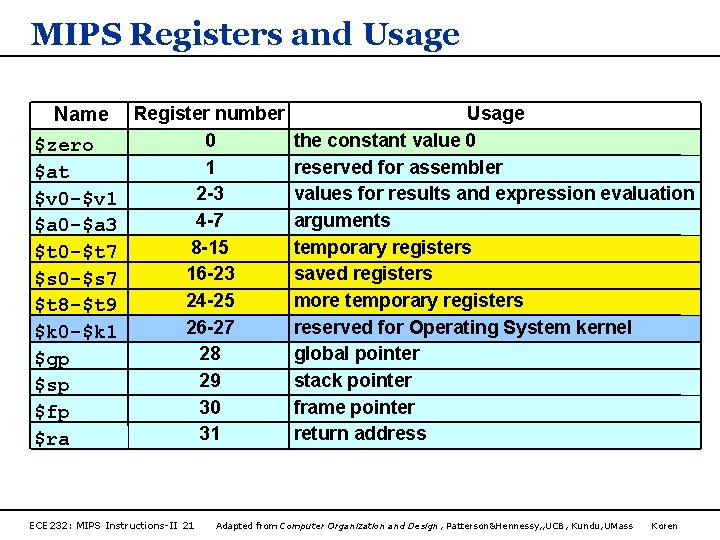

MIPS Registers and Usage Name Register number 0 $zero 1 $at 2 -3 $v 0 -$v 1 4 -7 $a 0 -$a 3 8 -15 $t 0 -$t 7 16 -23 $s 0 -$s 7 24 -25 $t 8 -$t 9 26 -27 $k 0 -$k 1 28 $gp 29 $sp 30 $fp 31 $ra ECE 232: MIPS Instructions-II 21 Usage the constant value 0 reserved for assembler values for results and expression evaluation arguments temporary registers saved registers more temporary registers reserved for Operating System kernel global pointer stack pointer frame pointer return address Adapted from Computer Organization and Design, Patterson&Hennessy, , UCB, Kundu, UMass Koren