CS 61 C Finishing the Datapath Subtract Multiple

CS 61 C Finishing the Datapath: Subtract, Multiple, Divide Lecture 21 April 14, 1999 Dave Patterson (http. cs. berkeley. edu/~patterson) www-inst. eecs. berkeley. edu/~cs 61 c/schedule. html cs 61 C L 21 muldiv. 1 Patterson Spring 99 ©UCB

Outline ° Review Datapath, ALU ° Including subtract in a 32 -bit ALU ° Review Binary Multiplication ° Administrivia, “What’s this Stuff Good For” ° Multiplier ° Review Binary Division ° Divider ° Conclusion cs 61 C L 21 muldiv. 2 Patterson Spring 99 ©UCB

Review 1/5: Steps in Executing MIPS Subset 1) Fetch Instruction and Increment PC 2) Read 1 or 2 Registers 3) Mem-ref: Calculate Address Arith-log: Perform Operation Branch: Compare if operands == 4) Load: Read Data from Memory Store: Write Data to Memory Arith-og: Write Result to Register Branch: if operands ==, Change PC 5) Load: Write Data to Register cs 61 C L 21 muldiv. 3 Patterson Spring 99 ©UCB

Review 2/5 : A Datapath for MIPS Address Data In Data Out Address Data Out Data In Data Out (Step 4, 5) PC Instruction Cache Step 1 cs 61 C L 21 muldiv. 4 Registers Step 2 ALU Step 3 Data Cache (Step 4) Patterson Spring 99 ©UCB

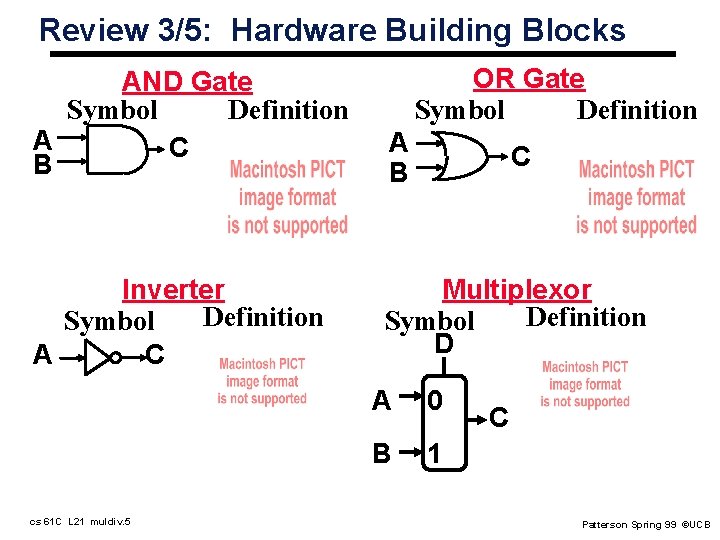

Review 3/5: Hardware Building Blocks OR Gate Symbol Definition AND Gate Symbol Definition A C B A B Inverter Definition Symbol A C Multiplexor Definition Symbol D cs 61 C L 21 muldiv. 5 C A 0 B 1 C Patterson Spring 99 ©UCB

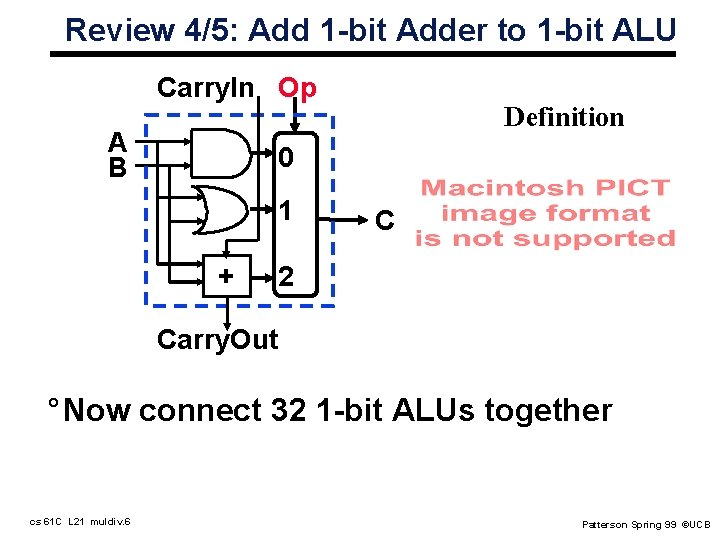

Review 4/5: Add 1 -bit Adder to 1 -bit ALU Carry. In Op A B Definition 0 1 + C 2 Carry. Out ° Now connect 32 1 -bit ALUs together cs 61 C L 21 muldiv. 6 Patterson Spring 99 ©UCB

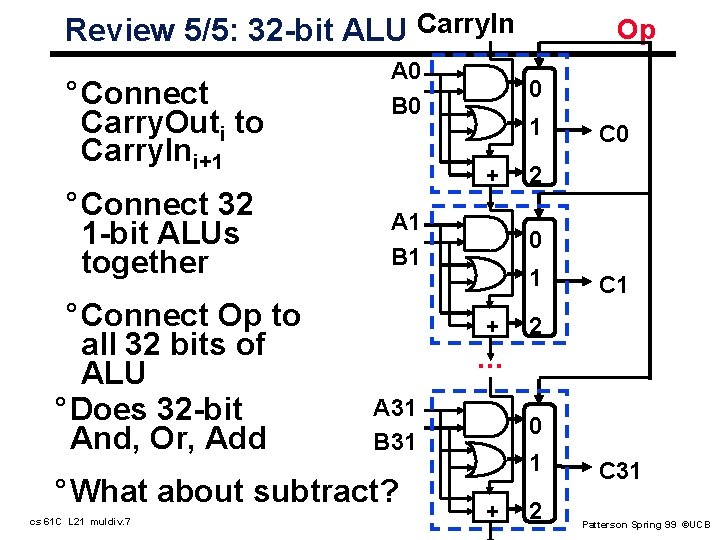

Review 5/5: 32 -bit ALU Carry. In ° Connect Carry. Outi to Carry. Ini+1 ° Connect 32 1 -bit ALUs together ° Connect Op to all 32 bits of ALU ° Does 32 -bit And, Or, Add A 0 B 0 0 1 + A 1 B 1 C 0 2 0 1 + C 1 2 . . . A 31 B 31 ° What about subtract? cs 61 C L 21 muldiv. 7 Op 0 1 + 2 C 31 Patterson Spring 99 ©UCB

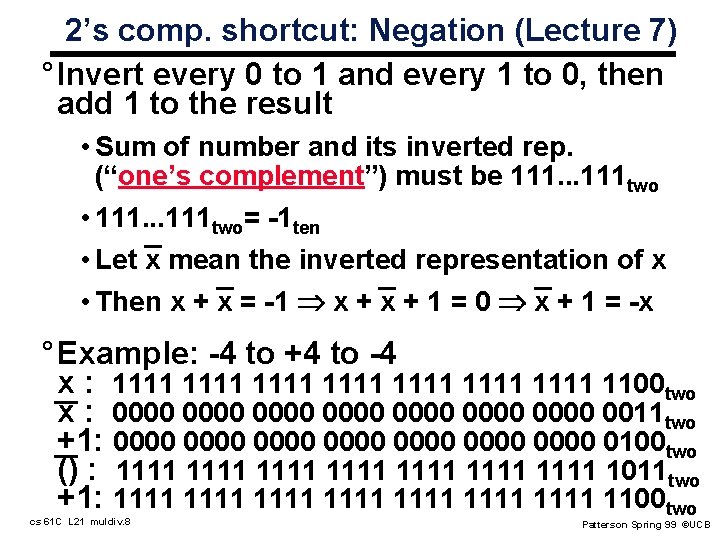

2’s comp. shortcut: Negation (Lecture 7) ° Invert every 0 to 1 and every 1 to 0, then add 1 to the result • Sum of number and its inverted rep. (“one’s complement”) must be 111. . . 111 two • 111. . . 111 two= -1 ten • Let x mean the inverted representation of x • Then x + x = -1 x + 1 = 0 x + 1 = -x ° Example: -4 to +4 to -4 x : 1111 1111 1100 two x : 0000 0000 0011 two +1: 0000 0000 0100 two () : 1111 1111 1011 two +1: 1111 1111 1100 two cs 61 C L 21 muldiv. 8 Patterson Spring 99 ©UCB

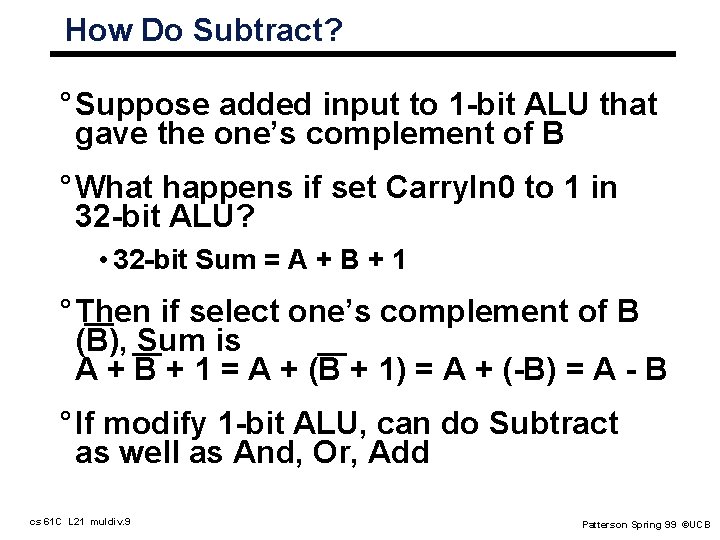

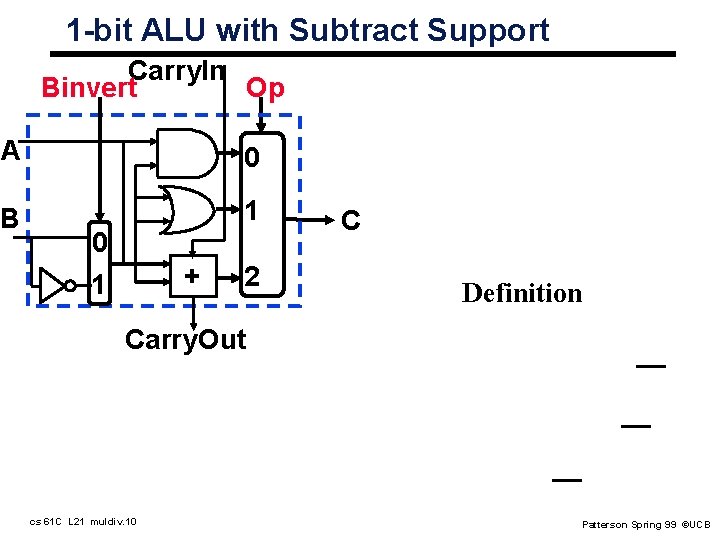

How Do Subtract? ° Suppose added input to 1 -bit ALU that gave the one’s complement of B ° What happens if set Carry. In 0 to 1 in 32 -bit ALU? • 32 -bit Sum = A + B + 1 ° Then if select one’s complement of B (B), Sum is A + B + 1 = A + (B + 1) = A + (-B) = A - B ° If modify 1 -bit ALU, can do Subtract as well as And, Or, Add cs 61 C L 21 muldiv. 9 Patterson Spring 99 ©UCB

1 -bit ALU with Subtract Support Carry. In Binvert Op A 0 B 1 0 + 1 2 C Definition Carry. Out cs 61 C L 21 muldiv. 10 Patterson Spring 99 ©UCB

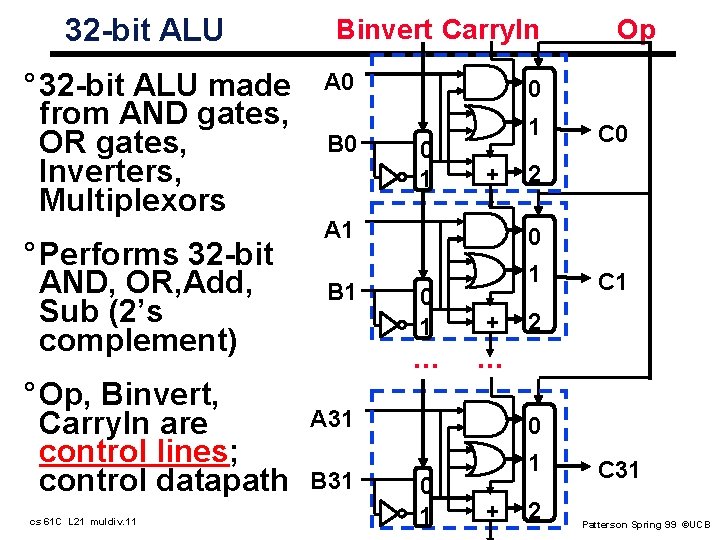

32 -bit ALU ° 32 -bit ALU made from AND gates, OR gates, Inverters, Multiplexors ° Performs 32 -bit AND, OR, Add, Sub (2’s complement) ° Op, Binvert, Carry. In are control lines; control datapath cs 61 C L 21 muldiv. 11 Binvert Carry. In A 0 B 0 0 0 1 1 + A 1 B 1 C 0 2 0 0 1 . . . 1 + C 1 2 . . . A 31 B 31 Op 0 0 1 1 + 2 C 31 Patterson Spring 99 ©UCB

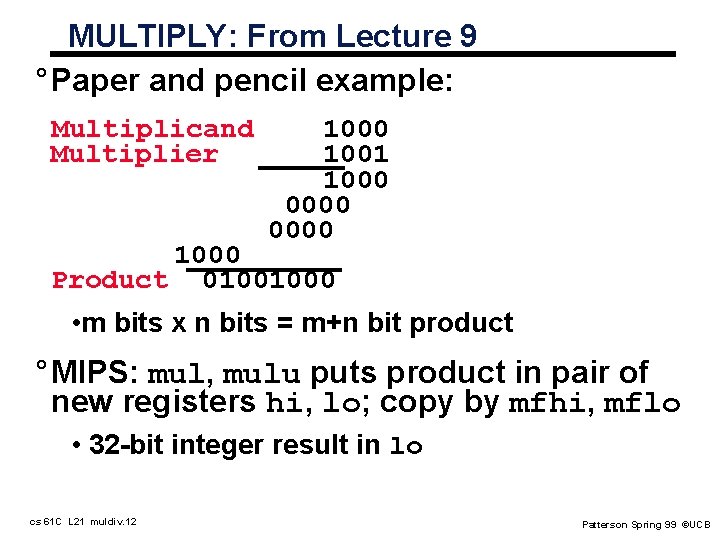

MULTIPLY: From Lecture 9 ° Paper and pencil example: Multiplicand Multiplier 1000 1001 1000 0000 1000 Product 01001000 • m bits x n bits = m+n bit product ° MIPS: mul, mulu puts product in pair of new registers hi, lo; copy by mfhi, mflo • 32 -bit integer result in lo cs 61 C L 21 muldiv. 12 Patterson Spring 99 ©UCB

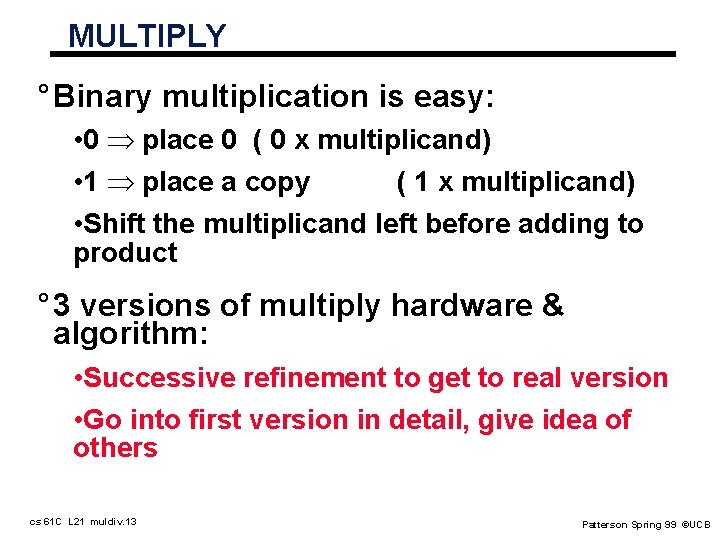

MULTIPLY ° Binary multiplication is easy: • 0 place 0 ( 0 x multiplicand) • 1 place a copy ( 1 x multiplicand) • Shift the multiplicand left before adding to product ° 3 versions of multiply hardware & algorithm: • Successive refinement to get to real version • Go into first version in detail, give idea of others cs 61 C L 21 muldiv. 13 Patterson Spring 99 ©UCB

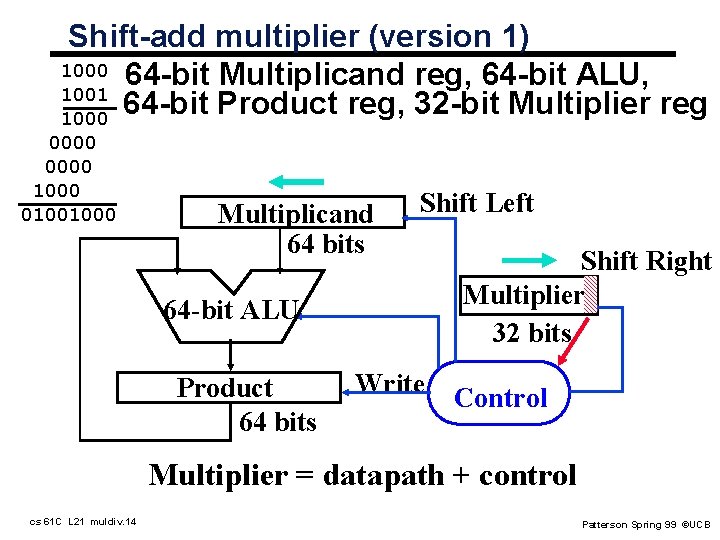

Shift-add multiplier (version 1) 1000 64 -bit Multiplicand reg, 64 -bit ALU, 1001 64 -bit Product reg, 32 -bit Multiplier reg 1000 0000 1000 01001000 Multiplicand 64 bits Shift Left 64 -bit ALU Product 64 bits Write Shift Right Multiplier 32 bits Control Multiplier = datapath + control cs 61 C L 21 muldiv. 14 Patterson Spring 99 ©UCB

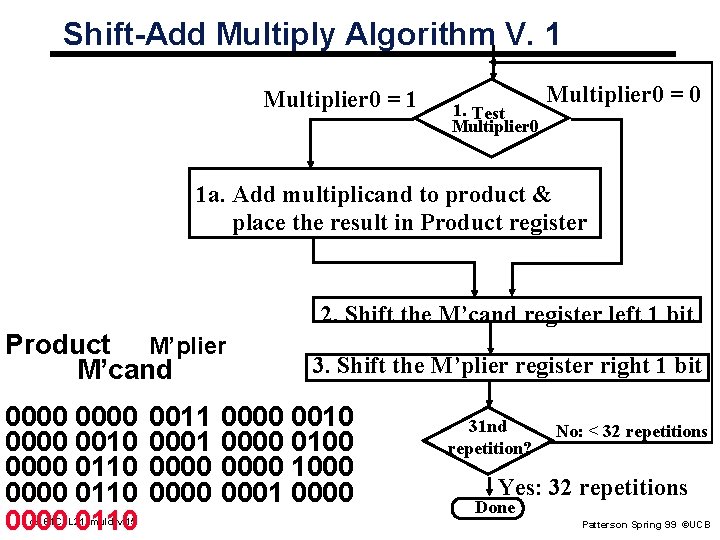

Shift-Add Multiply Algorithm V. 1 Multiplier 0 = 1 1. Test Multiplier 0 = 0 1 a. Add multiplicand to product & place the result in Product register 2. Shift the M’cand register left 1 bit Product M’plier M’cand 0000 0010 0000 0110 cs 61 C L 21 muldiv. 15 0011 0000 3. Shift the M’plier register right 1 bit 0000 0010 0000 0100 0000 1000 0001 0000 31 nd repetition? No: < 32 repetitions Yes: 32 repetitions Done Patterson Spring 99 ©UCB

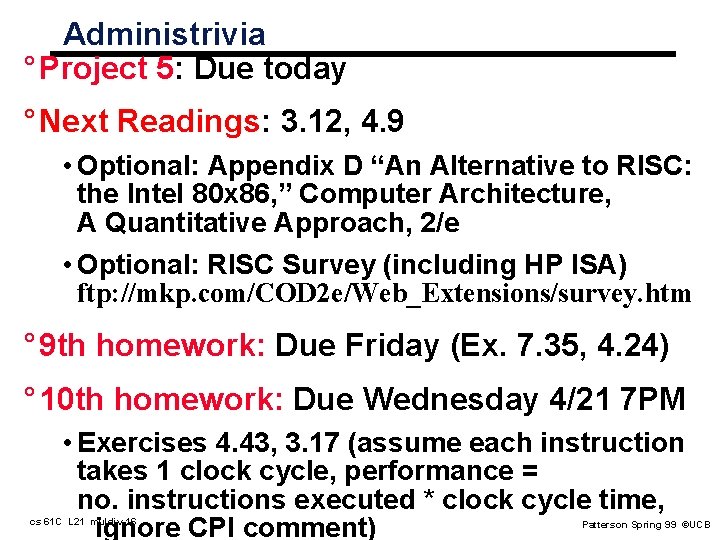

Administrivia ° Project 5: Due today ° Next Readings: 3. 12, 4. 9 • Optional: Appendix D “An Alternative to RISC: the Intel 80 x 86, ” Computer Architecture, A Quantitative Approach, 2/e • Optional: RISC Survey (including HP ISA) ftp: //mkp. com/COD 2 e/Web_Extensions/survey. htm ° 9 th homework: Due Friday (Ex. 7. 35, 4. 24) ° 10 th homework: Due Wednesday 4/21 7 PM • Exercises 4. 43, 3. 17 (assume each instruction takes 1 clock cycle, performance = no. instructions executed * clock cycle time, ignore CPI comment) cs 61 C L 21 muldiv. 16 Patterson Spring 99 ©UCB

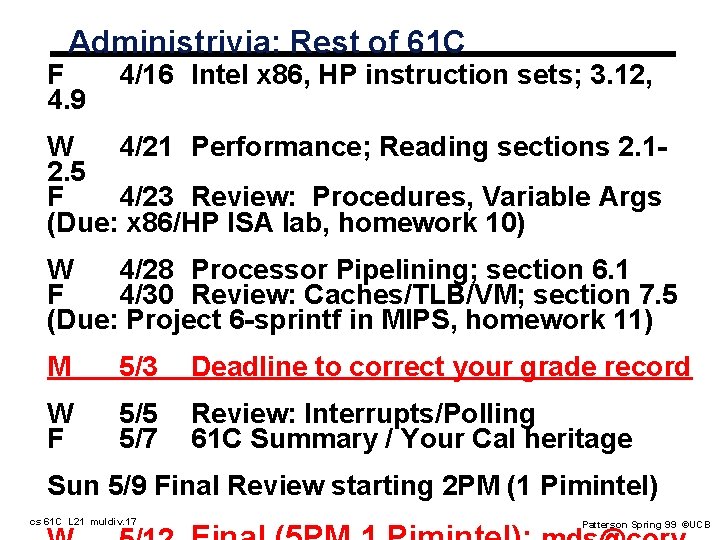

Administrivia: Rest of 61 C F 4. 9 4/16 Intel x 86, HP instruction sets; 3. 12, W 4/21 Performance; Reading sections 2. 12. 5 F 4/23 Review: Procedures, Variable Args (Due: x 86/HP ISA lab, homework 10) W 4/28 Processor Pipelining; section 6. 1 F 4/30 Review: Caches/TLB/VM; section 7. 5 (Due: Project 6 -sprintf in MIPS, homework 11) M 5/3 Deadline to correct your grade record W F 5/5 5/7 Review: Interrupts/Polling 61 C Summary / Your Cal heritage Sun 5/9 Final Review starting 2 PM (1 Pimintel) cs 61 C L 21 muldiv. 17 Patterson Spring 99 ©UCB

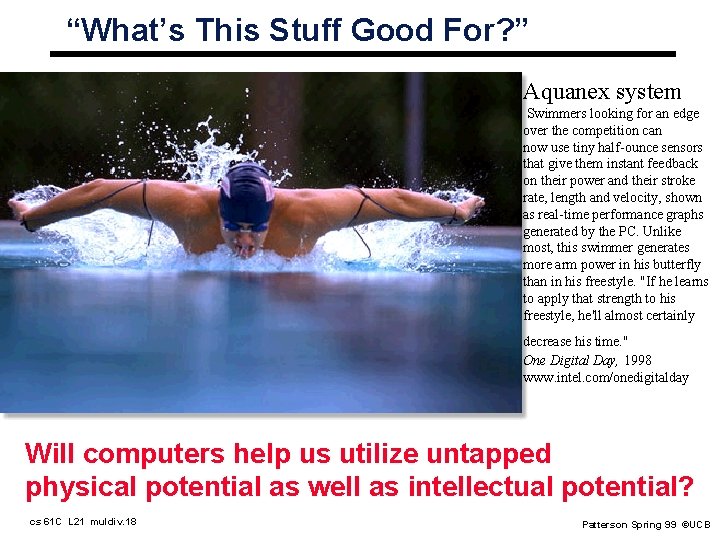

“What’s This Stuff Good For? ” Aquanex system Swimmers looking for an edge over the competition can now use tiny half-ounce sensors that give them instant feedback on their power and their stroke rate, length and velocity, shown as real-time performance graphs generated by the PC. Unlike most, this swimmer generates more arm power in his butterfly than in his freestyle. "If he learns to apply that strength to his freestyle, he'll almost certainly decrease his time. " One Digital Day, 1998 www. intel. com/onedigitalday Will computers help us utilize untapped physical potential as well as intellectual potential? cs 61 C L 21 muldiv. 18 Patterson Spring 99 ©UCB

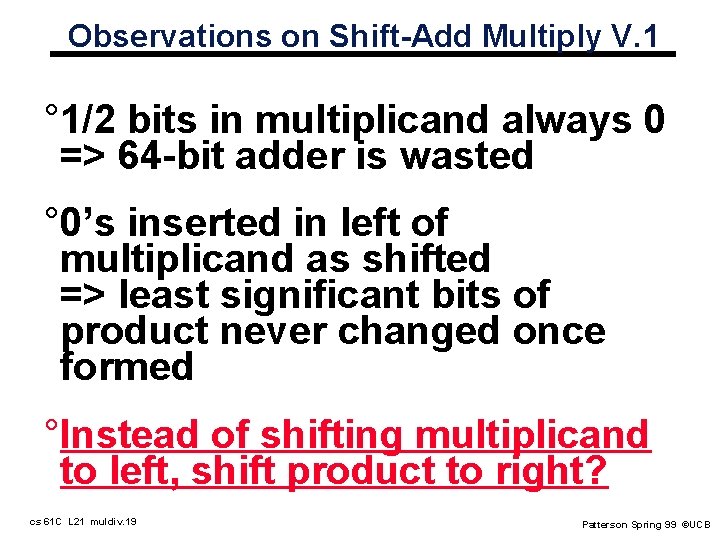

Observations on Shift-Add Multiply V. 1 ° 1/2 bits in multiplicand always 0 => 64 -bit adder is wasted ° 0’s inserted in left of multiplicand as shifted => least significant bits of product never changed once formed °Instead of shifting multiplicand to left, shift product to right? cs 61 C L 21 muldiv. 19 Patterson Spring 99 ©UCB

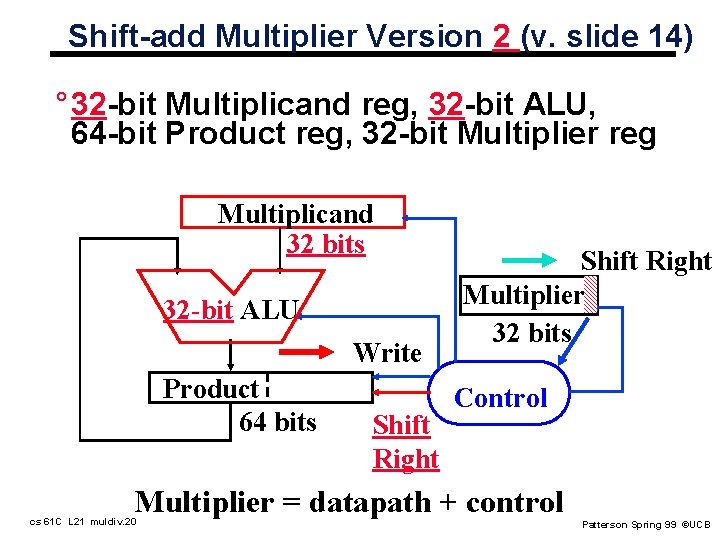

Shift-add Multiplier Version 2 (v. slide 14) ° 32 -bit Multiplicand reg, 32 -bit ALU, 64 -bit Product reg, 32 -bit Multiplier reg Multiplicand 32 bits 32 -bit ALU Write Product 64 bits Shift Right Multiplier 32 bits Control Multiplier = datapath + control cs 61 C L 21 muldiv. 20 Patterson Spring 99 ©UCB

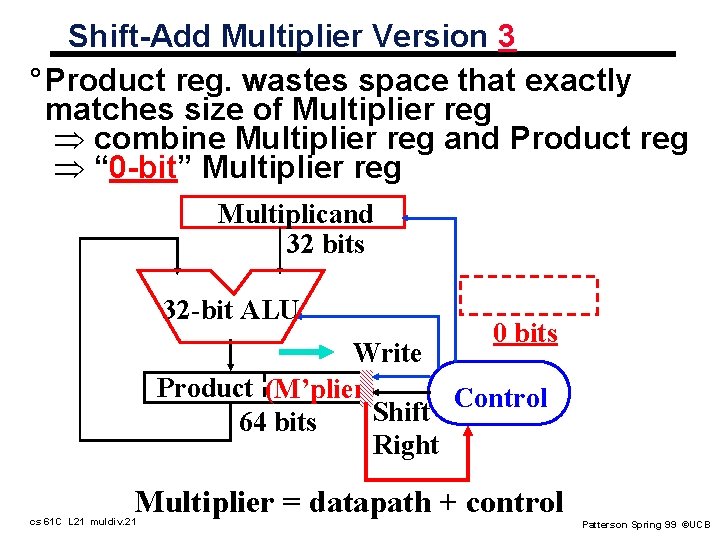

Shift-Add Multiplier Version 3 ° Product reg. wastes space that exactly matches size of Multiplier reg combine Multiplier reg and Product reg “ 0 -bit” Multiplier reg Multiplicand 32 bits 32 -bit ALU 0 bits Write Product (M’plier) Control Shift 64 bits Right Multiplier = datapath + control cs 61 C L 21 muldiv. 21 Patterson Spring 99 ©UCB

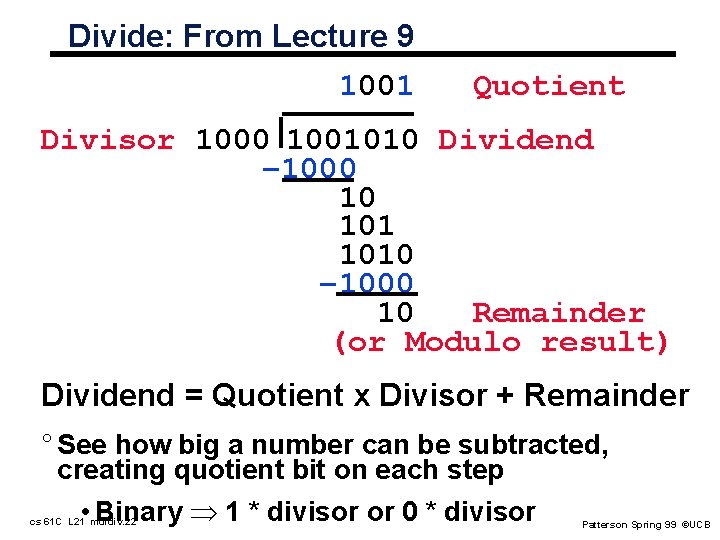

Divide: From Lecture 9 1001 Quotient Divisor 1000 1001010 Dividend – 1000 10 1010 – 1000 10 Remainder (or Modulo result) Dividend = Quotient x Divisor + Remainder ° See how big a number can be subtracted, creating quotient bit on each step • Binary 1 * divisor or 0 * divisor cs 61 C L 21 muldiv. 22 Patterson Spring 99 ©UCB

DIVIDE HARDWARE Version 1 64 -bit Divisor reg, 64 -bit ALU, 64 -bit Remainder reg, 32 -bit Quotient reg Divisor 64 bits Shift Quotient Shift Left 32 bits 64 -bit ALU Remainder 64 bits 1001 1000 1001010 – 1000 10 1010 Right – 1000 10 Write Control ° Put Dividend into Remainder to start, collect Quotient 1 bit at a time cs 61 C L 21 muldiv. 23 Patterson Spring 99 ©UCB

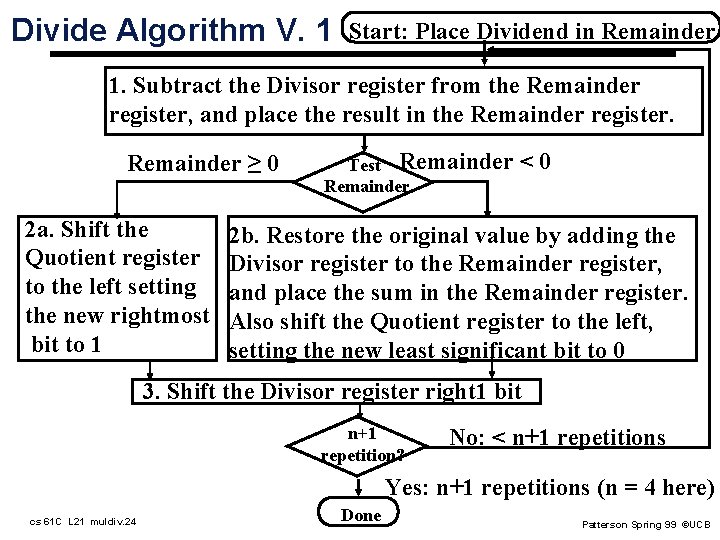

Divide Algorithm V. 1 Start: Place Dividend in Remainder 1. Subtract the Divisor register from the Remainder register, and place the result in the Remainder register. Remainder ≥ 0 2 a. Shift the Quotient register to the left setting the new rightmost bit to 1 Test Remainder <0 2 b. Restore the original value by adding the Divisor register to the Remainder register, and place the sum in the Remainder register. Also shift the Quotient register to the left, setting the new least significant bit to 0 3. Shift the Divisor register right 1 bit n+1 repetition? No: < n+1 repetitions Yes: n+1 repetitions (n = 4 here) cs 61 C L 21 muldiv. 24 Done Patterson Spring 99 ©UCB

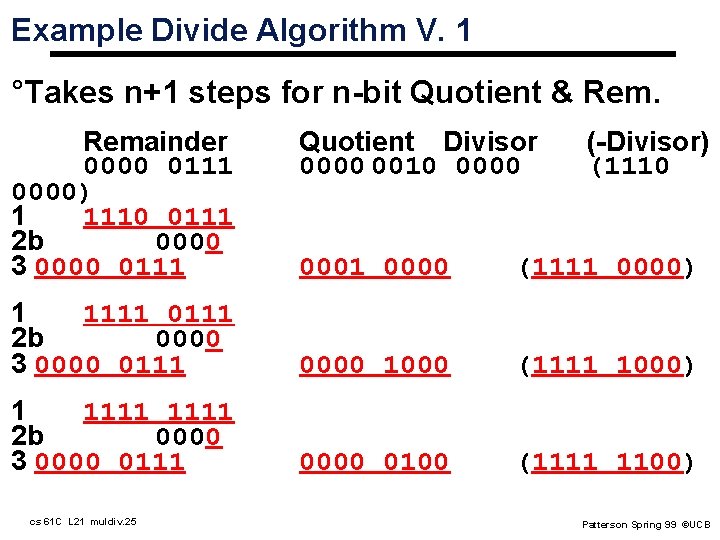

Example Divide Algorithm V. 1 °Takes n+1 steps for n-bit Quotient & Remainder 0000 0111 0000) 1 1110 0111 2 b 0000 3 0000 0111 Quotient Divisor 0000 0010 0000 (-Divisor) (1110 0001 0000 (1111 0000) 1 1111 0111 2 b 0000 3 0000 0111 0000 1000 (1111 1000) 1 1111 2 b 0000 3 0000 0111 0000 0100 (1111 1100) cs 61 C L 21 muldiv. 25 Patterson Spring 99 ©UCB

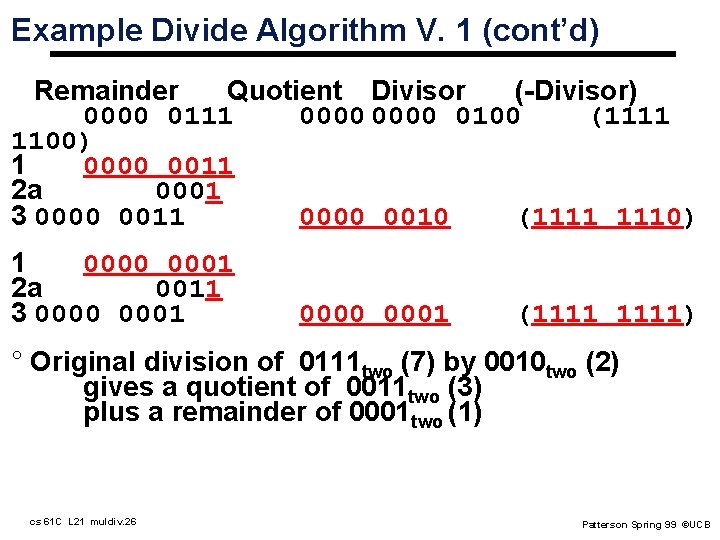

Example Divide Algorithm V. 1 (cont’d) Remainder Quotient Divisor (-Divisor) 0000 0111 0000 0100 (1111 1100) 1 0000 0011 2 a 0001 3 0000 0011 0000 0010 (1111 1110) 1 0000 0001 2 a 0011 3 0000 0001 (1111) ° Original division of 0111 two (7) by 0010 two (2) gives a quotient of 0011 two (3) plus a remainder of 0001 two (1) cs 61 C L 21 muldiv. 26 Patterson Spring 99 ©UCB

Observations on Divide Version 1 ° 1/2 bits in divisor always 0 => 1/2 of 64 -bit adder is wasted => 1/2 of divisor is wasted ° Instead of shifting Divisor to right, shift Remainder to left? cs 61 C L 21 muldiv. 27 Patterson Spring 99 ©UCB

DIVIDE HARDWARE Version 2 (v. slide 28) ° 32 -bit Divisor reg, 32 -bit ALU, 64 -bit Remainder reg, 32 -bit Quotient reg Divisor 32 bits Quotient Shift Left 32 -bit ALU Write Remainder Control 64 bits Shift Left cs 61 C L 21 muldiv. 28 Patterson Spring 99 ©UCB

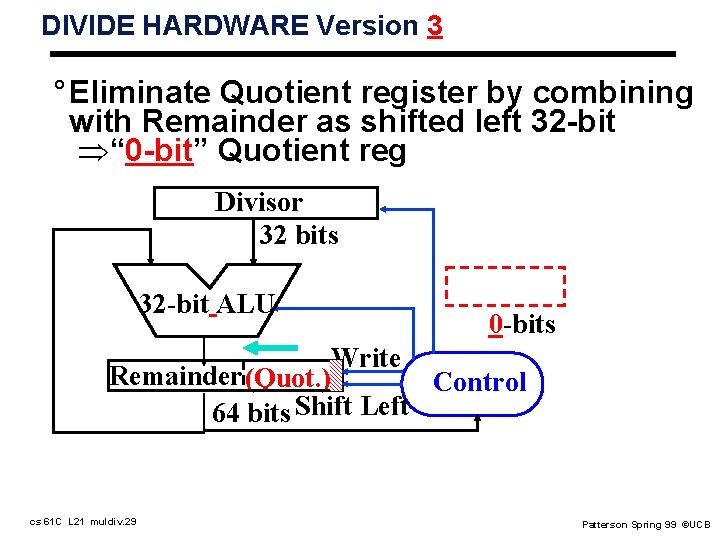

DIVIDE HARDWARE Version 3 ° Eliminate Quotient register by combining with Remainder as shifted left 32 -bit “ 0 -bit” Quotient reg Divisor 32 bits 32 -bit ALU 0 -bits Write Remainder (Quot. ) Control 64 bits Shift Left cs 61 C L 21 muldiv. 29 Patterson Spring 99 ©UCB

Multiply, Divide Algorithms Explain MIPS Multiplicand/Divisor 32 bits 32 -bit ALU Hi Lo Write Product/ Control Remainder Quotient Shift 64 bits °mul puts product in pair of regs hi, lo; • 32 -bit integer result in lo ° MIPS: div, divu puts Remainer into hi, puts Quotient into lo cs 61 C L 21 muldiv. 30 Patterson Spring 99 ©UCB

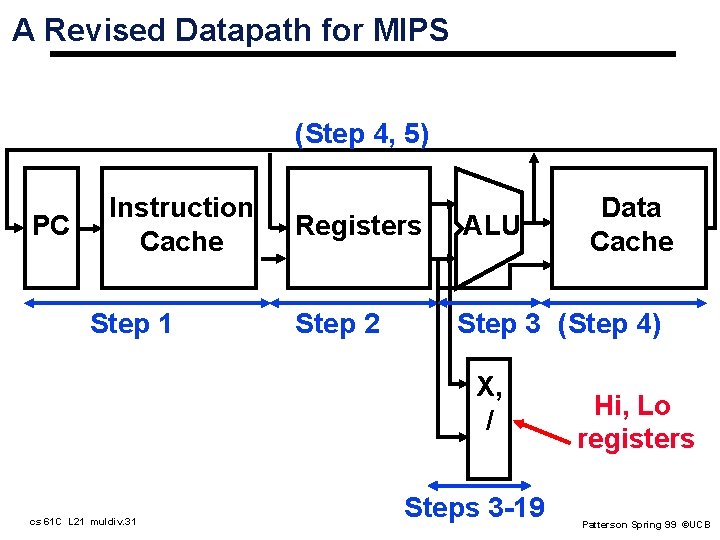

A Revised Datapath for MIPS (Step 4, 5) PC Instruction Cache Step 1 Registers ALU Step 2 Step 3 (Step 4) X, / cs 61 C L 21 muldiv. 31 Data Cache Steps 3 -19 Hi, Lo registers Patterson Spring 99 ©UCB

“And in Conclusion. . ” 1/1 ° Subtract included to ALU by adding one’s complement of B ° Multiple by shift and add ° Divide by shift and subtract, then restore by add if didn’t fit ° Can Multiply, Divide simply by adding 64 -bit shift register to ALU ° MIPS allows multiply, divide in parallel with ALU operations ° Next: Intel and HP Instruction Set Architectures cs 61 C L 21 muldiv. 32 Patterson Spring 99 ©UCB

- Slides: 32