Desain Unit Pemrosesan Mesin von Neumann Konsep untuk

![Siklus Eksekusi Program 1. IR M[PC] // Fetch instruksi 2. PC + d // Siklus Eksekusi Program 1. IR M[PC] // Fetch instruksi 2. PC + d //](https://slidetodoc.com/presentation_image_h/25e5f13041e53c0dac7b3941bfd5e21d/image-18.jpg)

![Menyimpan Data ke Memori Write Instruksi: ST (R 1), R 2 ; M[R 1] Menyimpan Data ke Memori Write Instruksi: ST (R 1), R 2 ; M[R 1]](https://slidetodoc.com/presentation_image_h/25e5f13041e53c0dac7b3941bfd5e21d/image-20.jpg)

![Tahapan Eksekusi Instruksi: Add R 1, (R 3) ; R 1 + M[R 3] Tahapan Eksekusi Instruksi: Add R 1, (R 3) ; R 1 + M[R 3]](https://slidetodoc.com/presentation_image_h/25e5f13041e53c0dac7b3941bfd5e21d/image-24.jpg)

- Slides: 49

Desain Unit Pemrosesan

Mesin von Neumann • Konsep untuk memiliki sebuah program yang tersimpan dalam memori komputer • Arsitektur dasar mesin ini masih menjadi kerangka referensi pada komputer modern

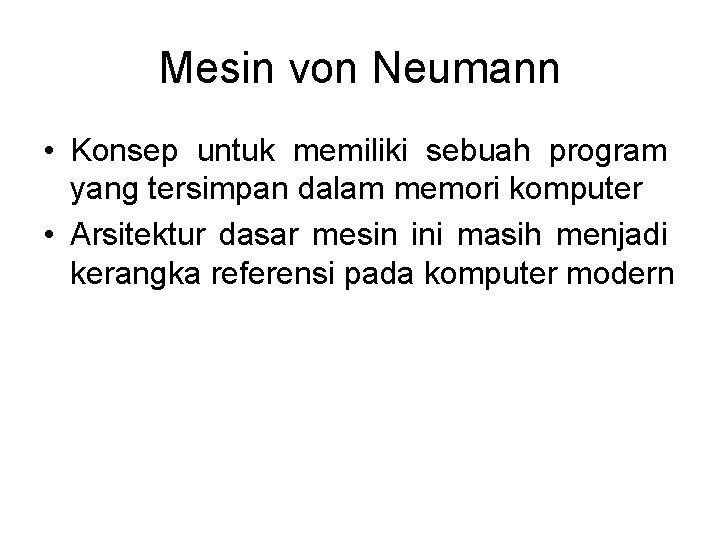

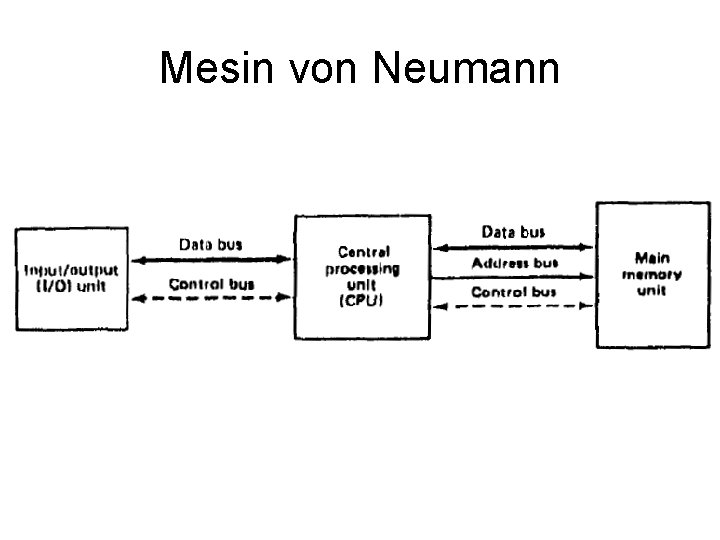

Mesin von Neumann

Mesin von Neumann • Program disimpan dalam unit memori utama, yang berhadapan dengan piranti input/output (I/O) melalui unit pengolahan pusat (CPU atau central processing unit) • CPU membaca dari atau menulis ke memori, pertama dengan mengirimkan alamat word ke unit memori melalui bus adress dan kemudian menerima atau mengirimkan data melalui bus data. • Data dipertukarkan antara CPU dan unit I/O juga menggunakan data bus. • Operasi ini disinkronisasikan oleh dua bus control dengan sinyal kendali yang dikirim oleh CPU dan sinyal acknowledgement serta sinyal interupsi yang diterima oleh CPU.

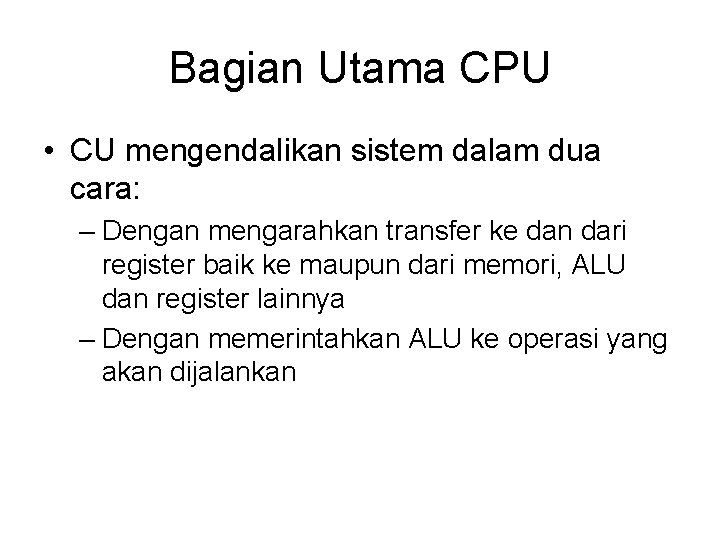

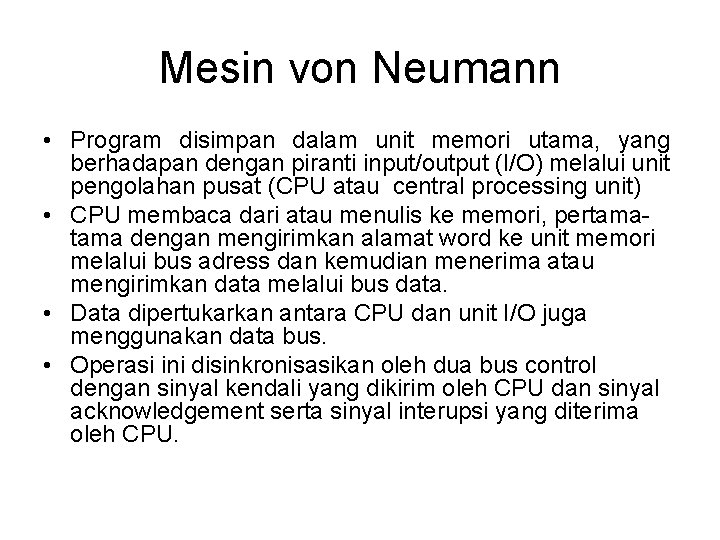

Prosesor: Control & Datapath Computer Processor (active) Control Datapath Memory (passive) (dimana program, data ada ketika dijalankan) Devices Input Output 5

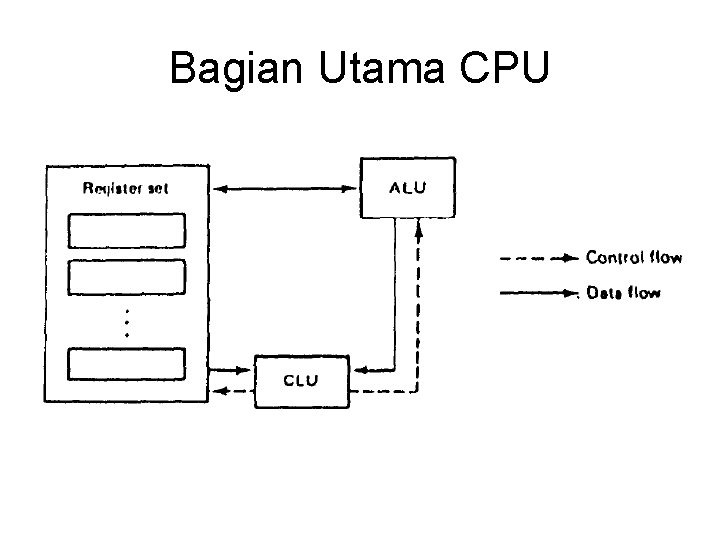

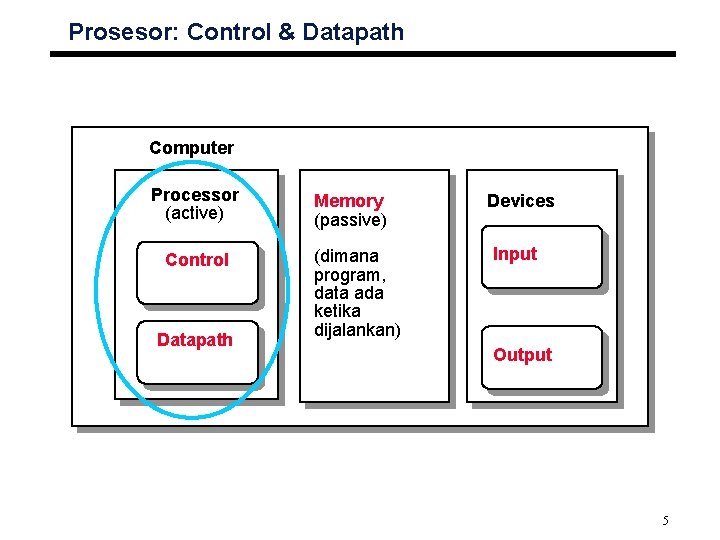

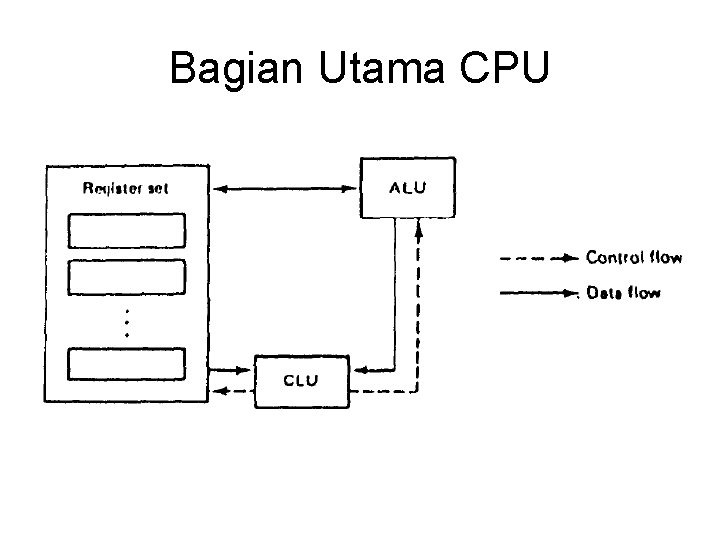

Bagian Utama CPU • Kumpulan register / register set • Unit aritmatika dan logika (ALU / Arithmetic and Logic Unit) • Unit kendali logika (CU / Control Unit)

Bagian Utama CPU • Kumpulan register menyimpan informasi sementara yang diperlukan untuk melaksanakan sebuah instruksi atau kumpulan instruksi / program • ALU menggunakan nilai-nilai yang tersimpan dalam kumpulan register untuk melakukan operasi aritmatika dan logika

Bagian Utama CPU • CU mengendalikan sistem dalam dua cara: – Dengan mengarahkan transfer ke dan dari register baik ke maupun dari memori, ALU dan register lainnya – Dengan memerintahkan ALU ke operasi yang akan dijalankan

Bagian Utama CPU

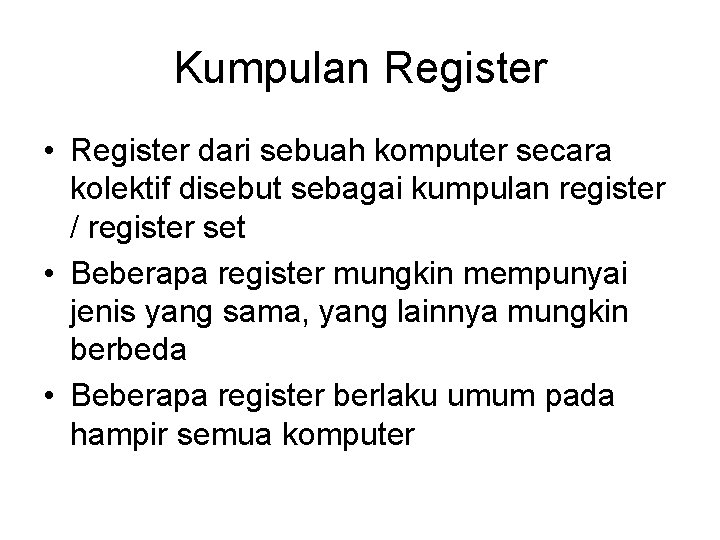

Kumpulan Register • Register dari sebuah komputer secara kolektif disebut sebagai kumpulan register / register set • Beberapa register mungkin mempunyai jenis yang sama, yang lainnya mungkin berbeda • Beberapa register berlaku umum pada hampir semua komputer

Register Program Counter • Menyimpan alamat memori dari instruksi selanjutnya yang akan dijalankan • Pelaksanaan sebuah program biasanya dilakukan berurutan, maka alamat instruksi berikutnya bernilai 1 lebih tinggi daripada alamat dari instruksi saat ini. • PC ← (PC)+1 • Jika suatu jump atau cabang instruksi dijalankan, instruksi yang akan dilaksanakan berikutnya disimpan pada alamat yang ditentukan dalam cabang instruksi. • Dalam hal ini, kita ingin me-load langsung alamat baru ke PC : • PC ← bagian alamat dari instruksi cabang

Register Instruksi • Register khusus untuk menyimpan instruksi • Pertama, instruksi di-fetch dari memori dan disimpan dalam IR kemudian PC ditingkatkan sehingga ia menunjuk ke instruksi berikutnya • IR ← M[PC] • PC ← (PC)+1 • M[PC] menunjukkan isi lokasi memori yang ditunjuk oleh PC. • Sekali instruksi disimpan dalam IR, maka instruksi tersebut dapat di-decode oleh Control Unit (CU) dan operasi mikro dapat diaktifkan untuk pelaksanaannya

Register Umum • Untuk menyimpan nilai-nilai sementara selama pelaksanaan instruksi • Sebuah komputer memiliki sebuah register prosesor untuk pelaksanaan instruksi, disebut Accumulator (ACC)

Register Flag • Mengendalikan aliran pelaksanaan pada CU dan ALU

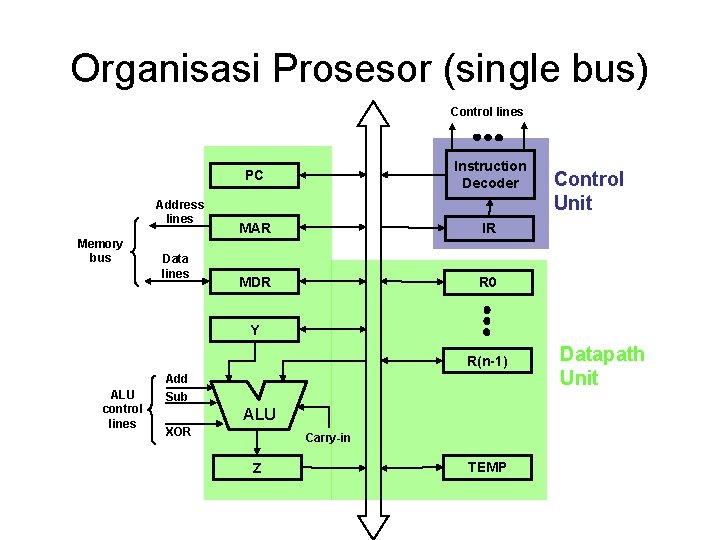

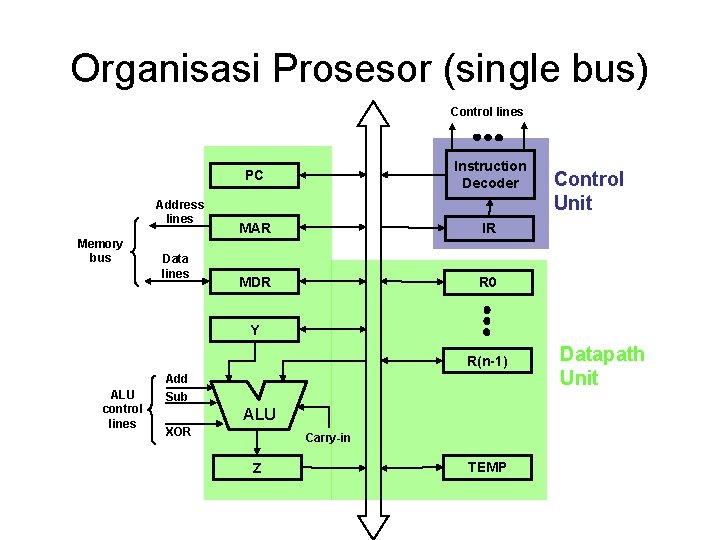

Organisasi Prosesor (single bus) Control lines Address lines Memory bus Data lines PC Instruction Decoder MAR IR MDR R 0 Control Unit Y R(n-1) ALU control lines Add Sub ALU XOR Carry-in Z TEMP Datapath Unit

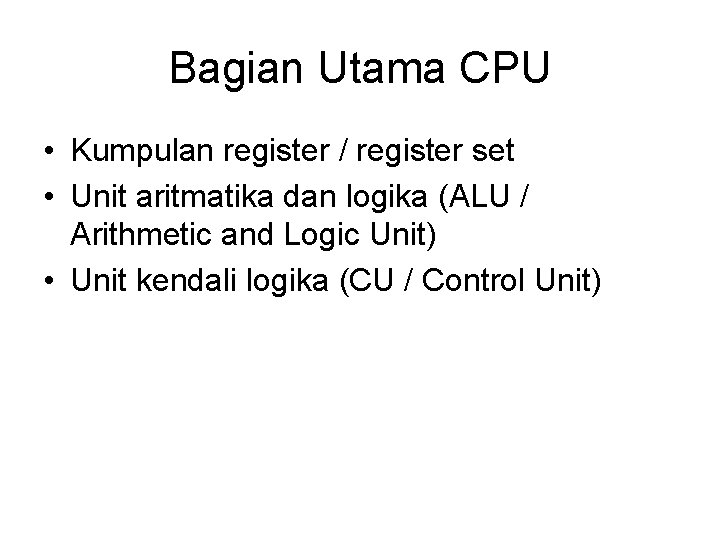

Operasi Dasar Prosesor • Operasi-operasi Dasar: – Mengambil (fetching) Data dari Memori – Menyimpan (storing) Data ke Memori – Pertukaran Data Antar-Register – Operasi Aritmatika & Logika di Datapath

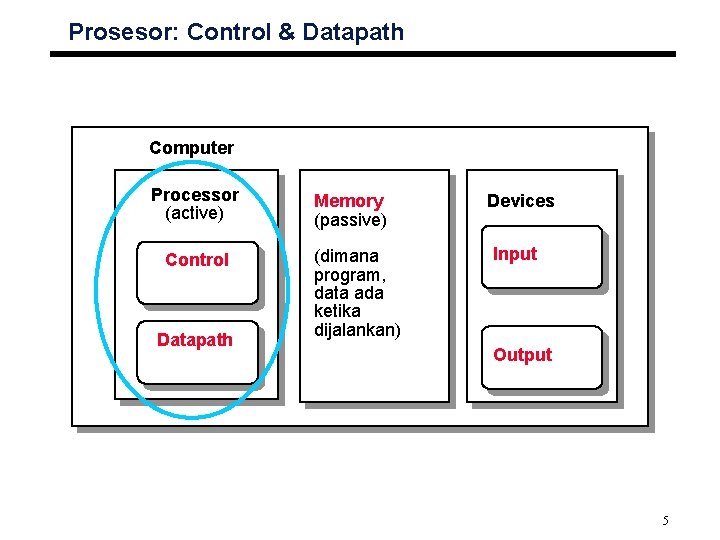

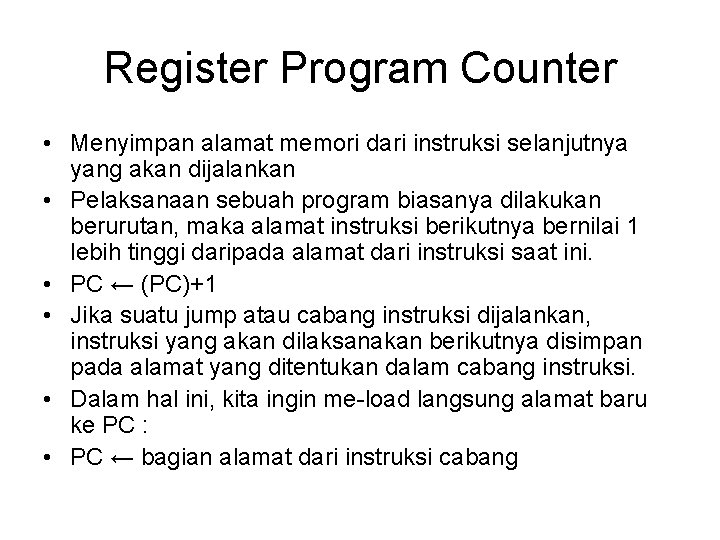

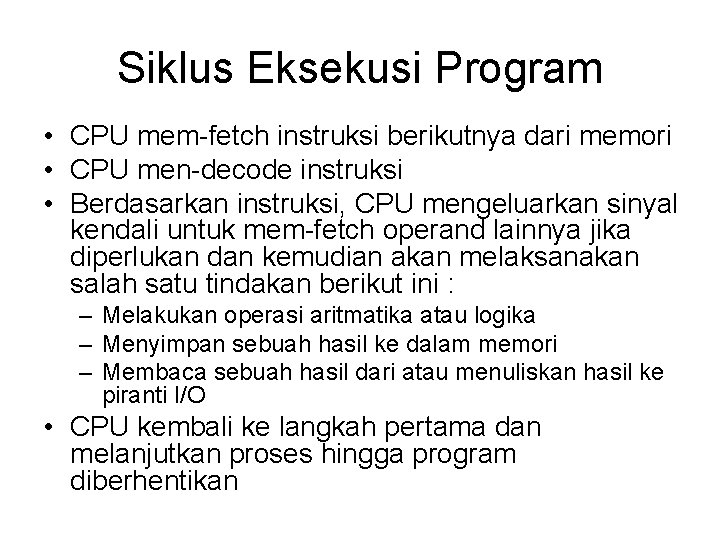

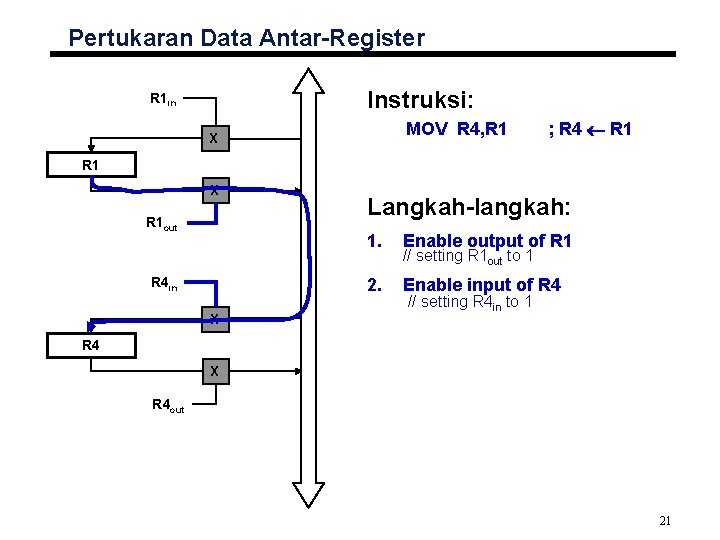

Siklus Eksekusi Program • CPU mem-fetch instruksi berikutnya dari memori • CPU men-decode instruksi • Berdasarkan instruksi, CPU mengeluarkan sinyal kendali untuk mem-fetch operand lainnya jika diperlukan dan kemudian akan melaksanakan salah satu tindakan berikut ini : – Melakukan operasi aritmatika atau logika – Menyimpan sebuah hasil ke dalam memori – Membaca sebuah hasil dari atau menuliskan hasil ke piranti I/O • CPU kembali ke langkah pertama dan melanjutkan proses hingga program diberhentikan

![Siklus Eksekusi Program 1 IR MPC Fetch instruksi 2 PC d Siklus Eksekusi Program 1. IR M[PC] // Fetch instruksi 2. PC + d //](https://slidetodoc.com/presentation_image_h/25e5f13041e53c0dac7b3941bfd5e21d/image-18.jpg)

Siklus Eksekusi Program 1. IR M[PC] // Fetch instruksi 2. PC + d // Tunjuk ke lokasi instruksi berikutnya 3. Eksekusi instruksi

Mengambil Data dari Memori Read Instruksi: LD R 2, (R 1) ; R 2 M[R 1] Address lines Langkah-langkah: 1. MAR R 1 2. Read 3. Tunggu sinyal MFC 4. Data lines PC Instruction Decoder MAR IR MDR R 1 Y // MFC = Memory Function Completed // Pada saat MFC aktif: Add // MDR M[MAR] R 2 MDR MFC R 2 Sub ALU XOR Carry-in Z TEMP 19

![Menyimpan Data ke Memori Write Instruksi ST R 1 R 2 MR 1 Menyimpan Data ke Memori Write Instruksi: ST (R 1), R 2 ; M[R 1]](https://slidetodoc.com/presentation_image_h/25e5f13041e53c0dac7b3941bfd5e21d/image-20.jpg)

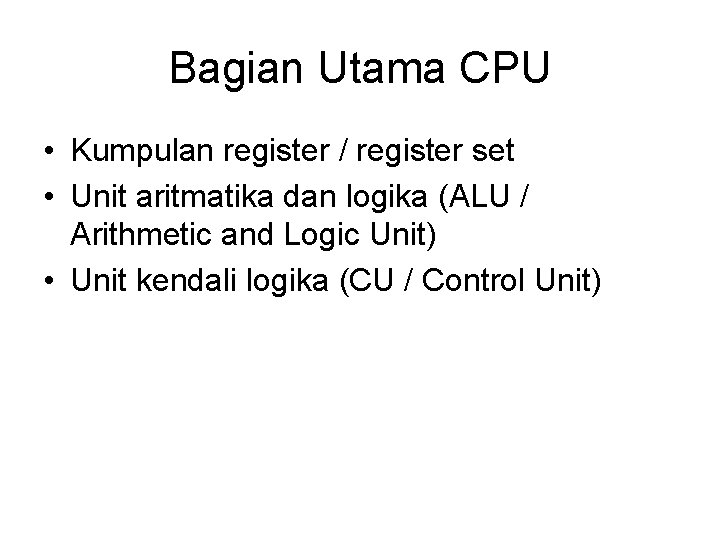

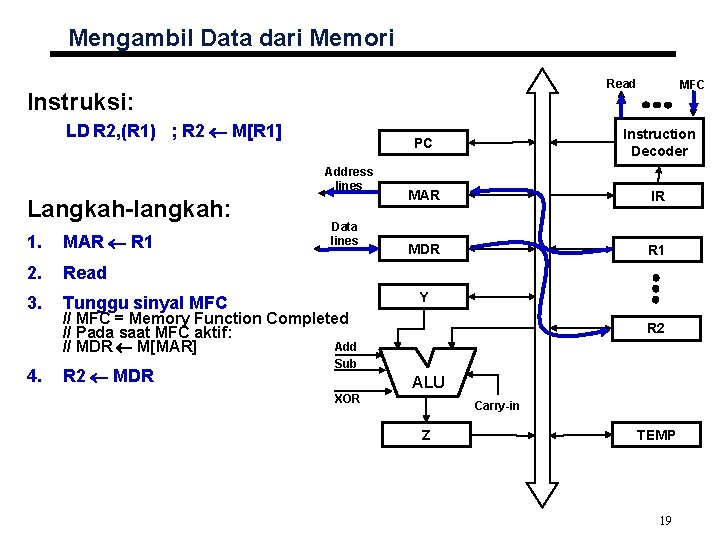

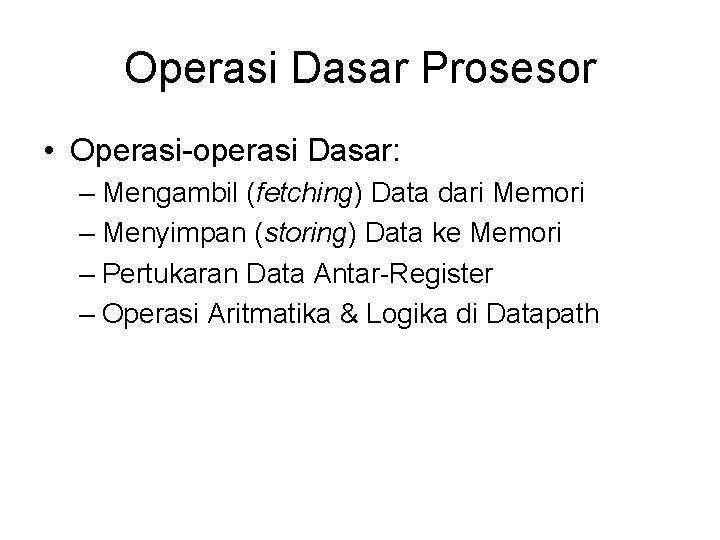

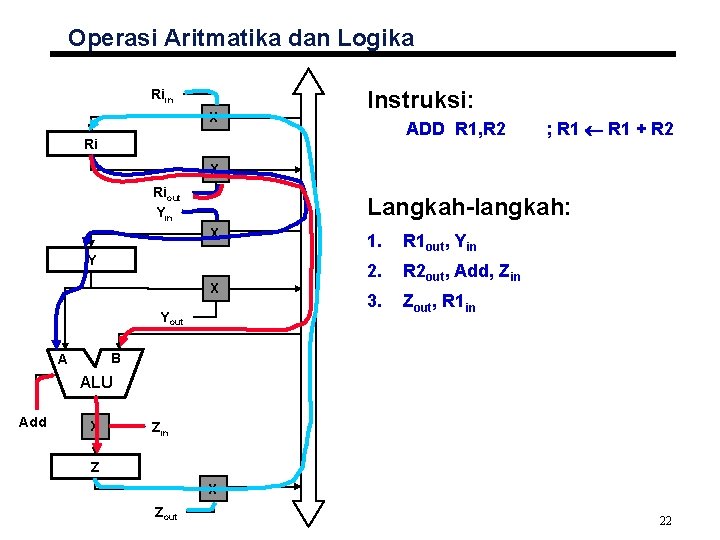

Menyimpan Data ke Memori Write Instruksi: ST (R 1), R 2 ; M[R 1] R 2 Address lines Langkah-langkah: 1. MAR R 1 2. MDR R 2, Write 3. Tunggu sinyal MFC Data lines MFC PC Instruction Decoder MAR IR MDR R 1 Y // MFC = Memory Function Completed // Pada saat MFC aktif: Add // M[MAR] MDR R 2 Sub ALU XOR Carry-in Z TEMP 20

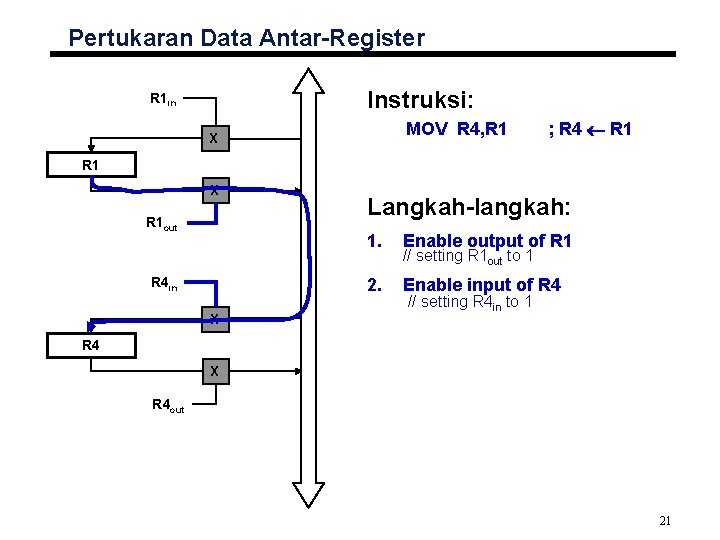

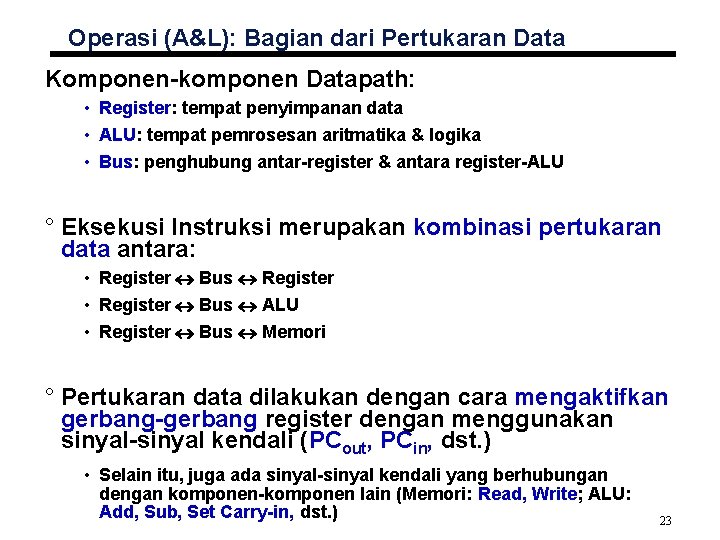

Pertukaran Data Antar-Register Instruksi: R 1 in MOV R 4, R 1 X ; R 4 R 1 X R 1 out R 4 in X Langkah-langkah: 1. Enable output of R 1 2. Enable input of R 4 // setting R 1 out to 1 // setting R 4 in to 1 R 4 X R 4 out 21

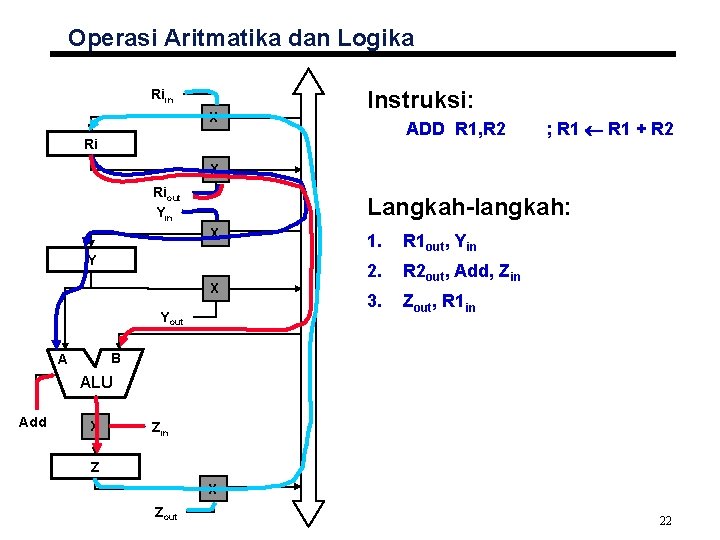

Operasi Aritmatika dan Logika Riin X Instruksi: ADD R 1, R 2 Ri ; R 1 + R 2 X Riout Yin Langkah-langkah: X Yout 1. R 1 out, Yin 2. R 2 out, Add, Zin 3. Zout, R 1 in B A ALU Add X Zin Z X Zout 22

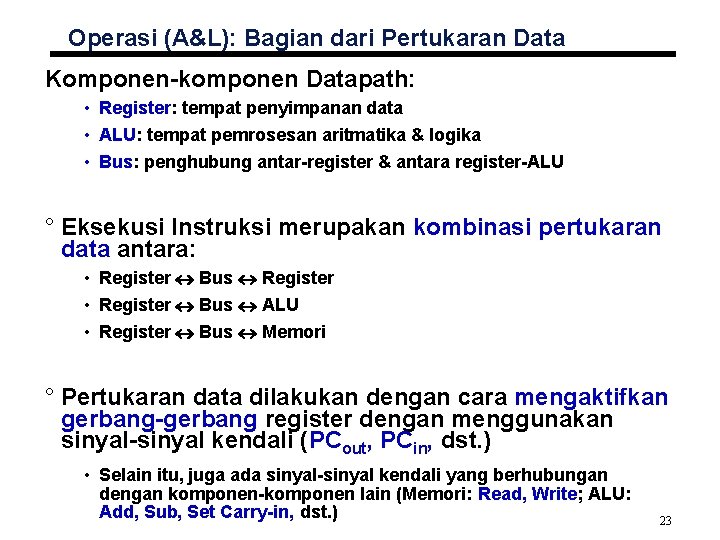

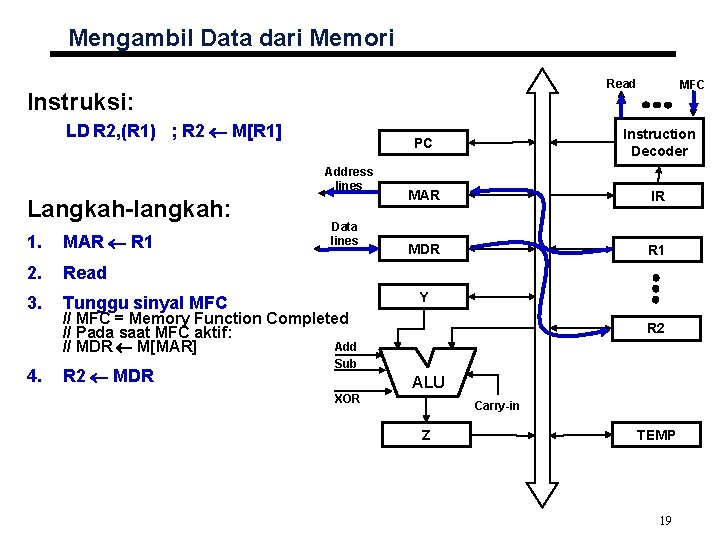

Operasi (A&L): Bagian dari Pertukaran Data Komponen-komponen Datapath: • Register: tempat penyimpanan data • ALU: tempat pemrosesan aritmatika & logika • Bus: penghubung antar-register & antara register-ALU ° Eksekusi Instruksi merupakan kombinasi pertukaran data antara: • Register Bus Register • Register Bus ALU • Register Bus Memori ° Pertukaran data dilakukan dengan cara mengaktifkan gerbang-gerbang register dengan menggunakan sinyal-sinyal kendali (PCout, PCin, dst. ) • Selain itu, juga ada sinyal-sinyal kendali yang berhubungan dengan komponen-komponen lain (Memori: Read, Write; ALU: Add, Sub, Set Carry-in, dst. ) 23

![Tahapan Eksekusi Instruksi Add R 1 R 3 R 1 MR 3 Tahapan Eksekusi Instruksi: Add R 1, (R 3) ; R 1 + M[R 3]](https://slidetodoc.com/presentation_image_h/25e5f13041e53c0dac7b3941bfd5e21d/image-24.jpg)

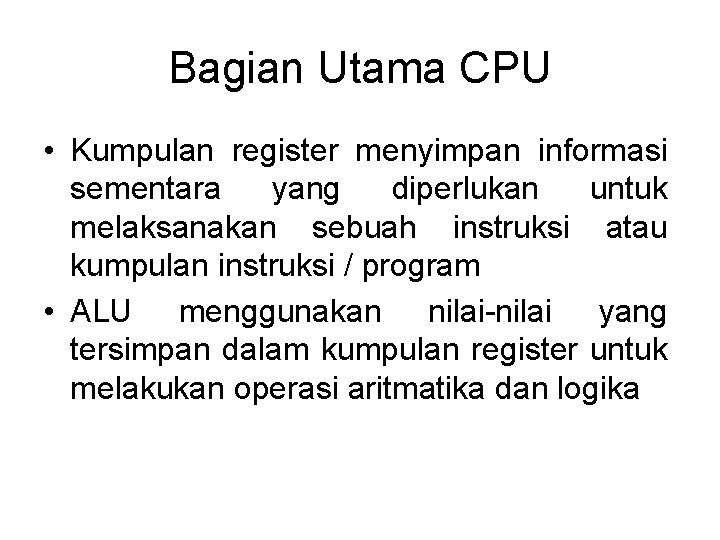

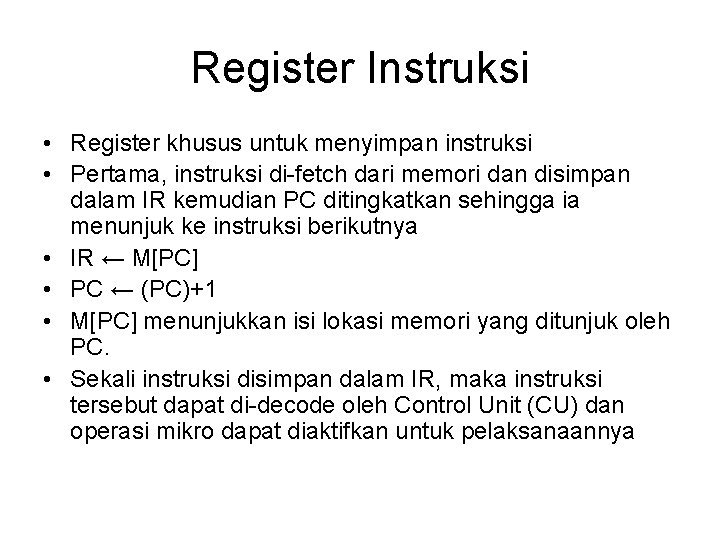

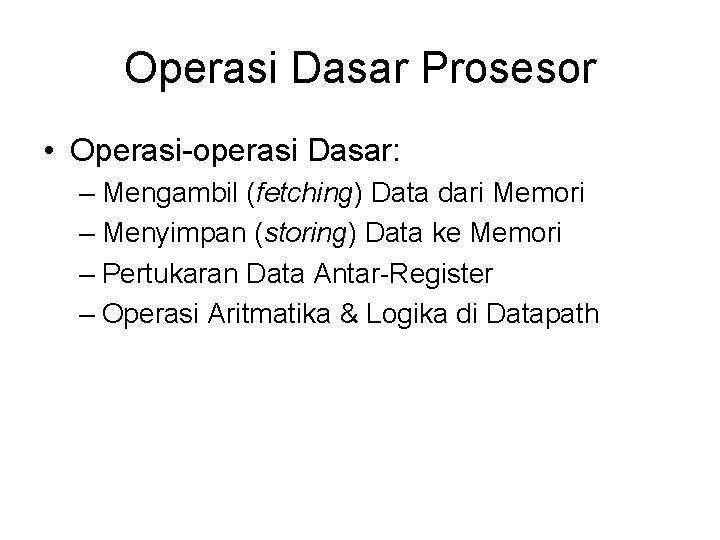

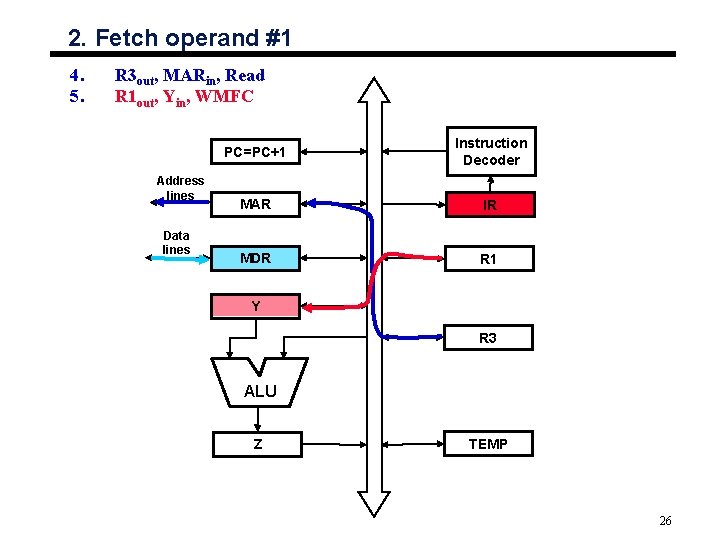

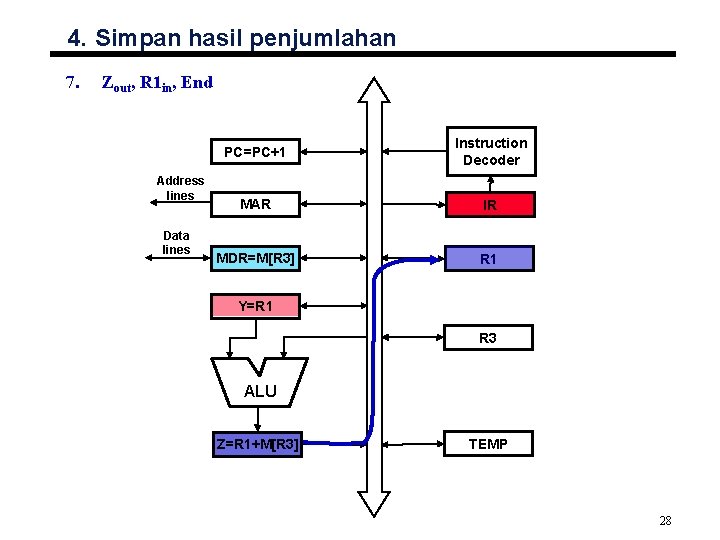

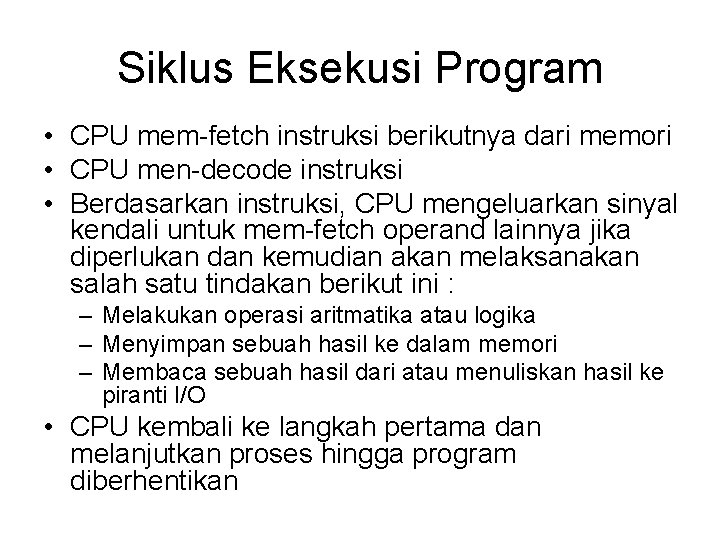

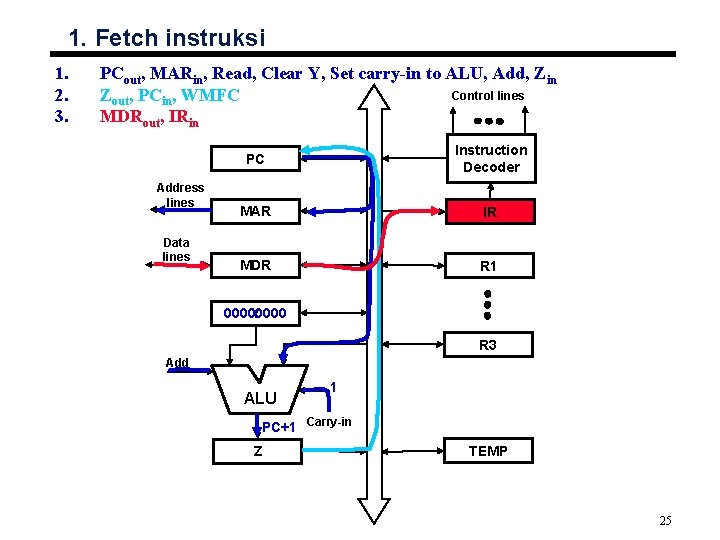

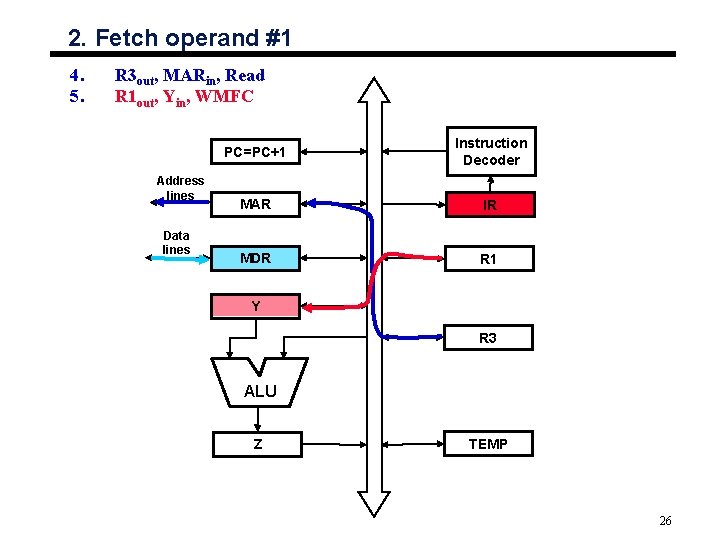

Tahapan Eksekusi Instruksi: Add R 1, (R 3) ; R 1 + M[R 3] Langkah-langkah: 1. Fetch instruksi 1. PCout, MARin, Read, Clear Y, Set carry-in to ALU, Add, Zin 2. Zout, PCin, WMFC 3. MDRout, IRin 2. Fetch operand #1 (isi lokasi memori yg ditunjuk oleh R 3) 4. R 3 out, MARin, Read 5. R 1 out, Yin, WMFC 3. Lakukan operasi penjumlahan 6. MDRout, Add, Zin 4. Simpan hasil penjumlahan di R 1 7. Zout, R 1 in, End 24

1. Fetch instruksi 1. 2. 3. PCout, MARin, Read, Clear Y, Set carry-in to ALU, Add, Zin Control lines Zout, PCin, WMFC MDRout, IRin Address lines Data lines PC Instruction Decoder MAR IR MDR R 1 0000 Y R 3 Add ALU 1 PC+1 Carry-in Z TEMP 25

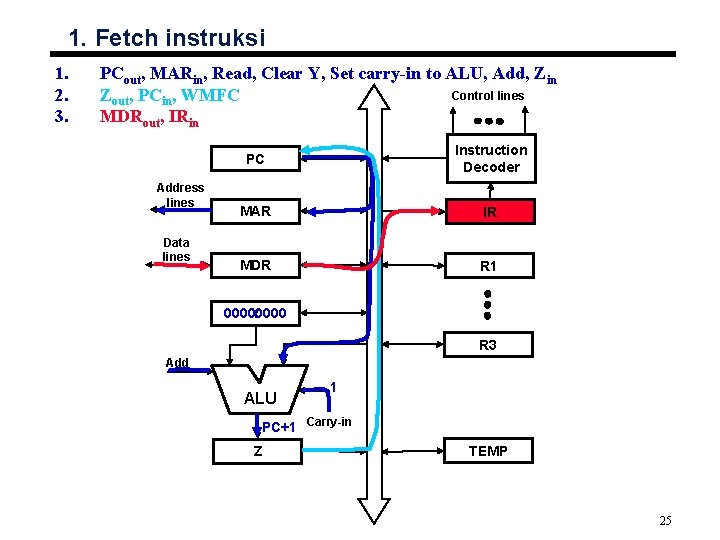

2. Fetch operand #1 4. 5. R 3 out, MARin, Read R 1 out, Yin, WMFC Address lines Data lines PC=PC+1 Instruction Decoder MAR IR MDR R 1 Y R 3 ALU Z TEMP 26

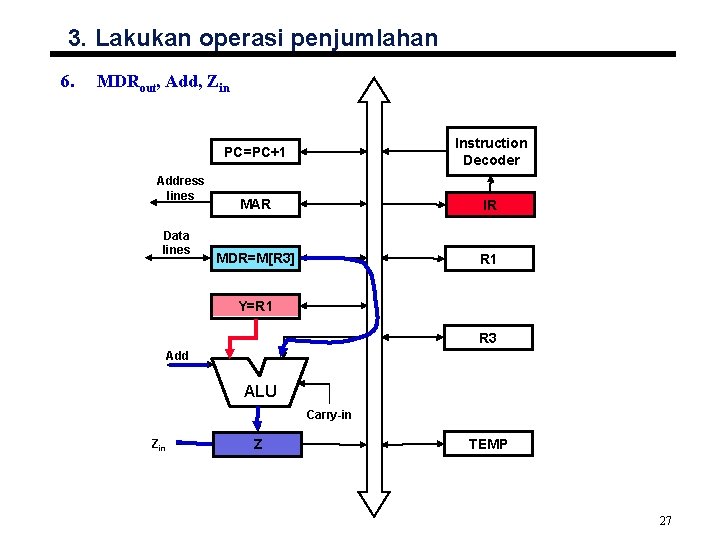

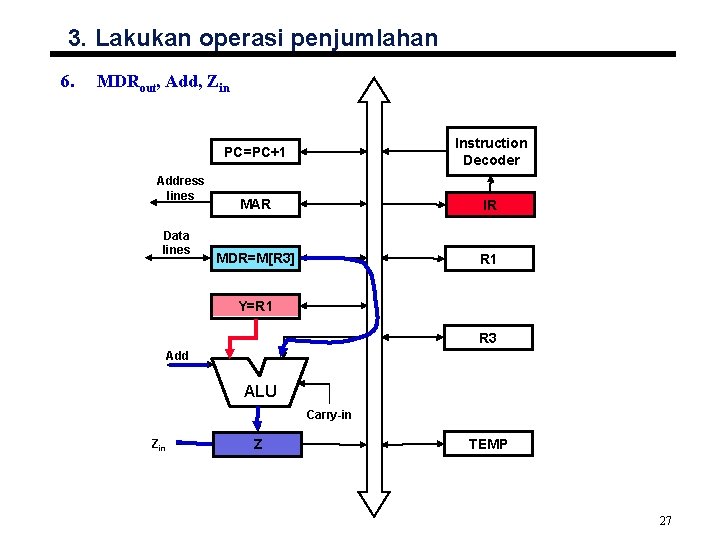

3. Lakukan operasi penjumlahan 6. MDRout, Add, Zin Address lines Data lines PC=PC+1 Instruction Decoder MAR IR MDR=M[R 3] R 1 Y=R 1 R 3 Add ALU Carry-in Z TEMP 27

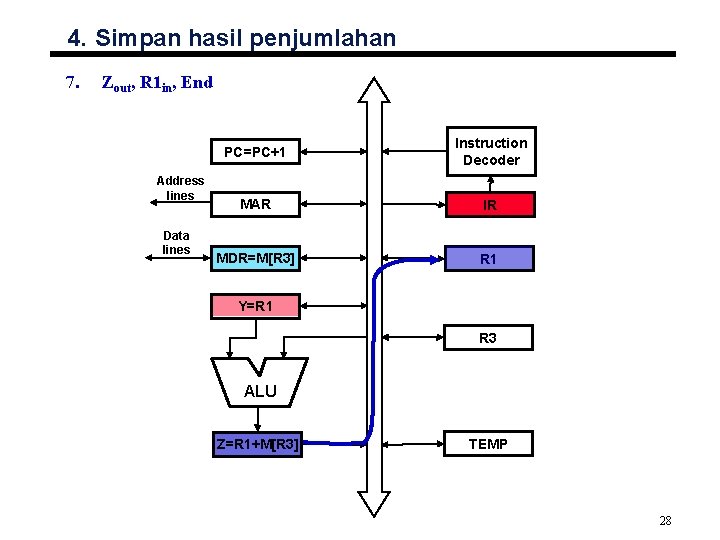

4. Simpan hasil penjumlahan 7. Zout, R 1 in, End Address lines Data lines PC=PC+1 Instruction Decoder MAR IR MDR=M[R 3] R 1 Y=R 1 R 3 ALU Z=R 1+M[R 3] TEMP 28

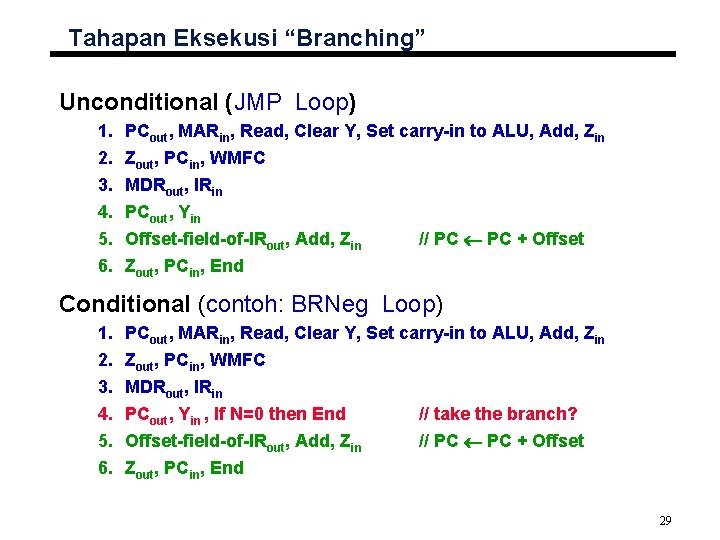

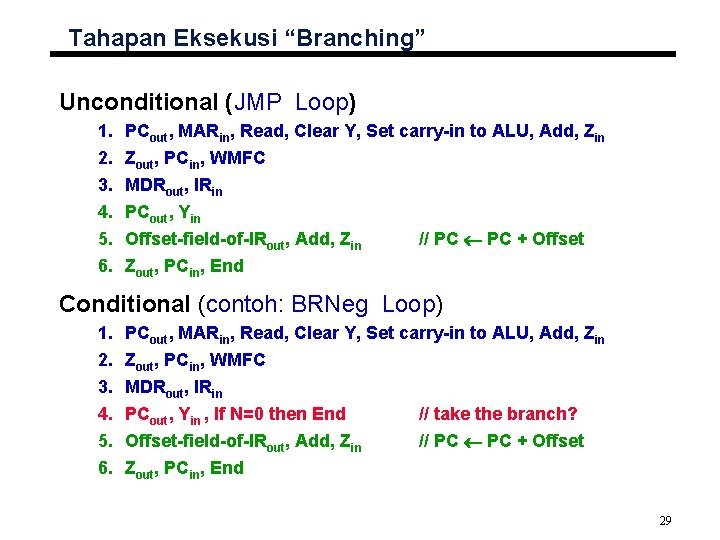

Tahapan Eksekusi “Branching” Unconditional (JMP Loop) 1. 2. 3. 4. 5. 6. PCout, MARin, Read, Clear Y, Set carry-in to ALU, Add, Zin Zout, PCin, WMFC MDRout, IRin PCout, Yin Offset-field-of-IRout, Add, Zin Zout, PCin, End // PC + Offset Conditional (contoh: BRNeg Loop) 1. 2. 3. 4. 5. 6. PCout, MARin, Read, Clear Y, Set carry-in to ALU, Add, Zin Zout, PCin, WMFC MDRout, IRin PCout, Yin , If N=0 then End // take the branch? Offset-field-of-IRout, Add, Zin // PC + Offset Zout, PCin, End 29

LD Rd, X 30

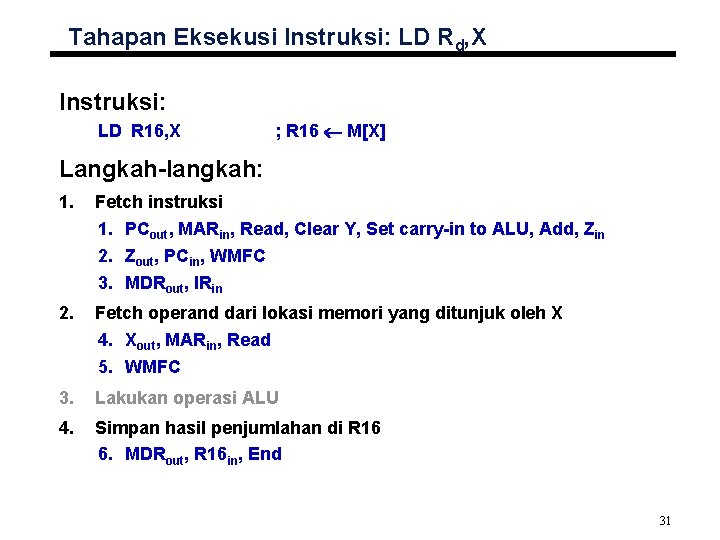

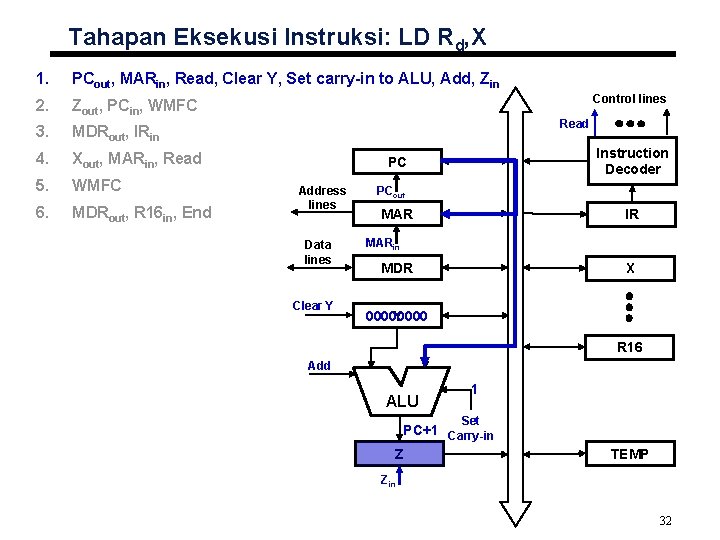

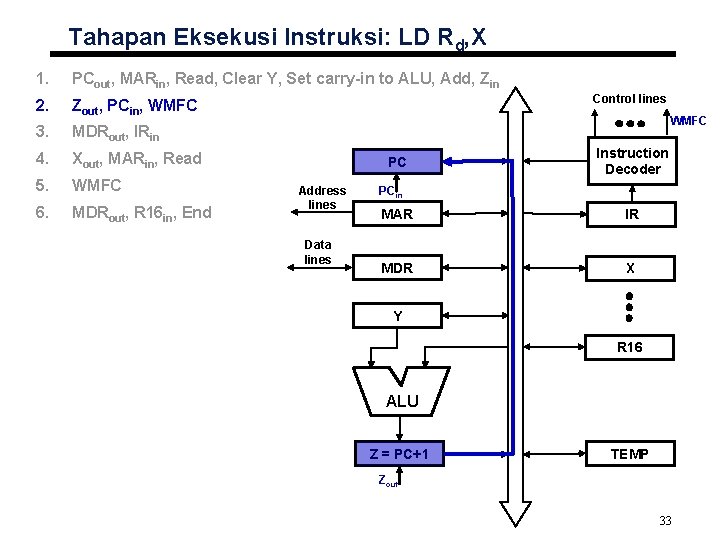

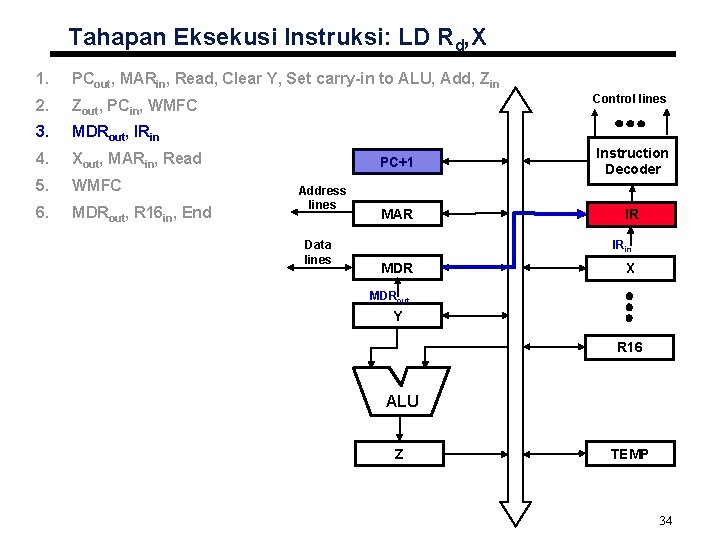

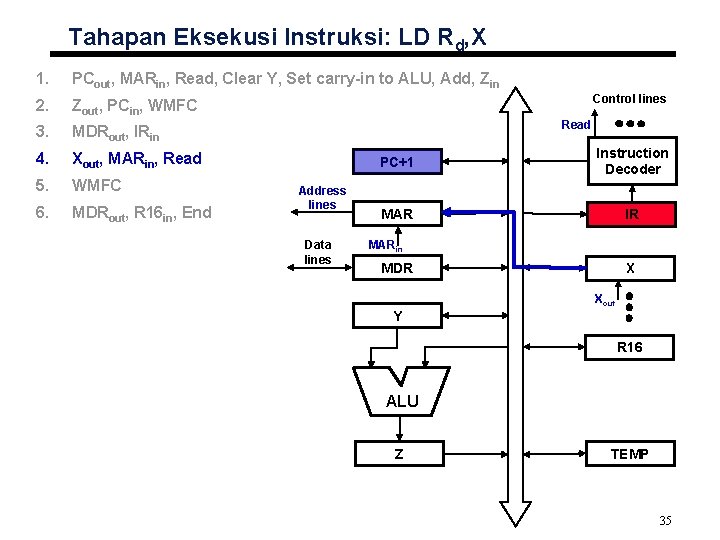

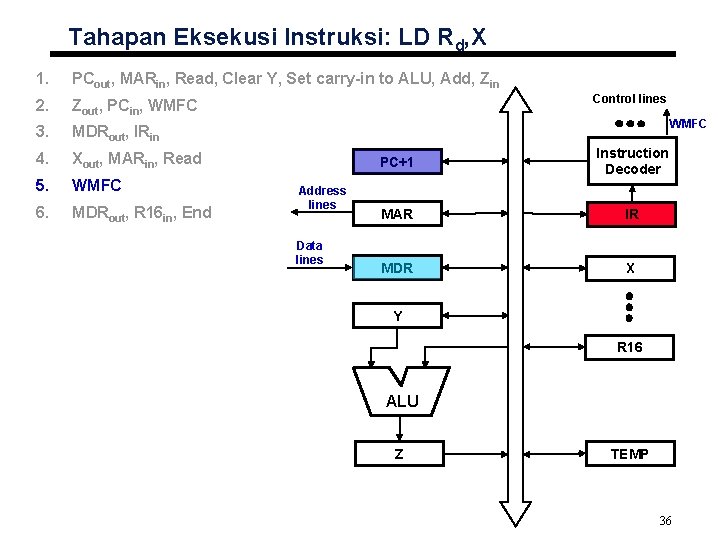

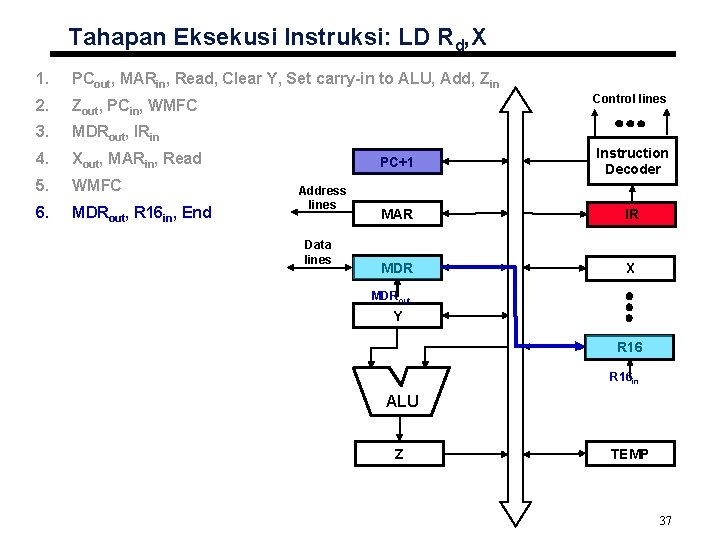

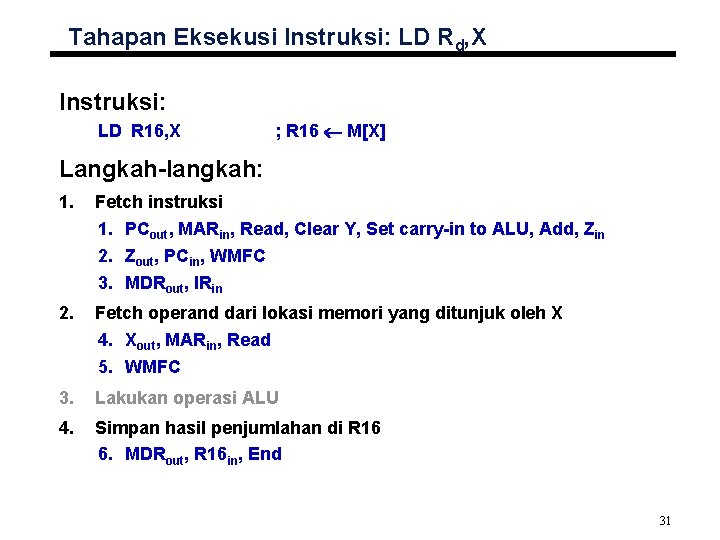

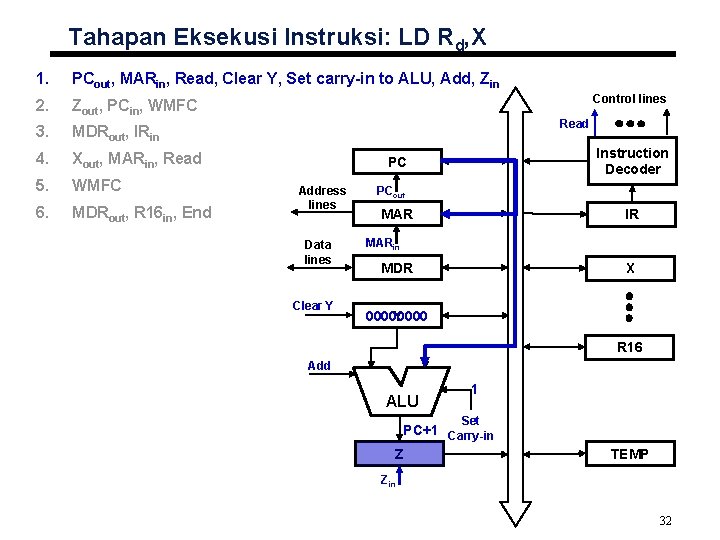

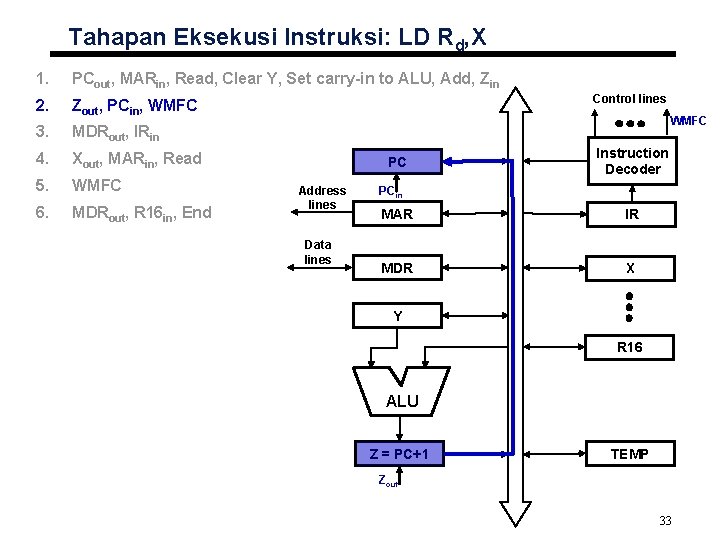

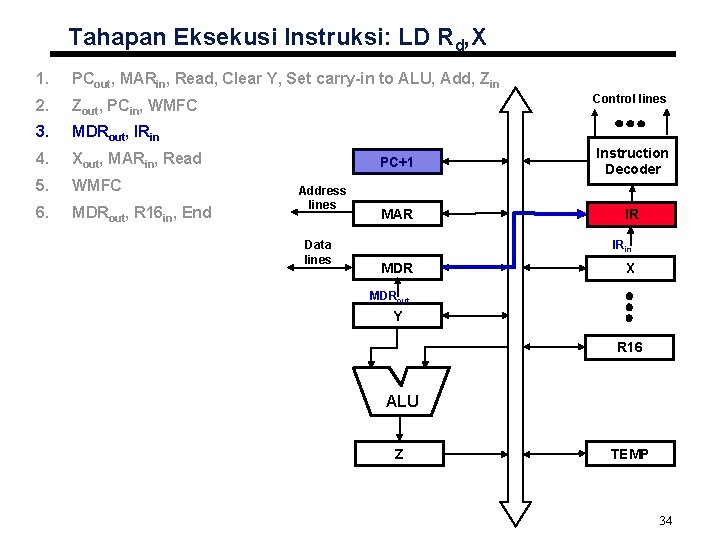

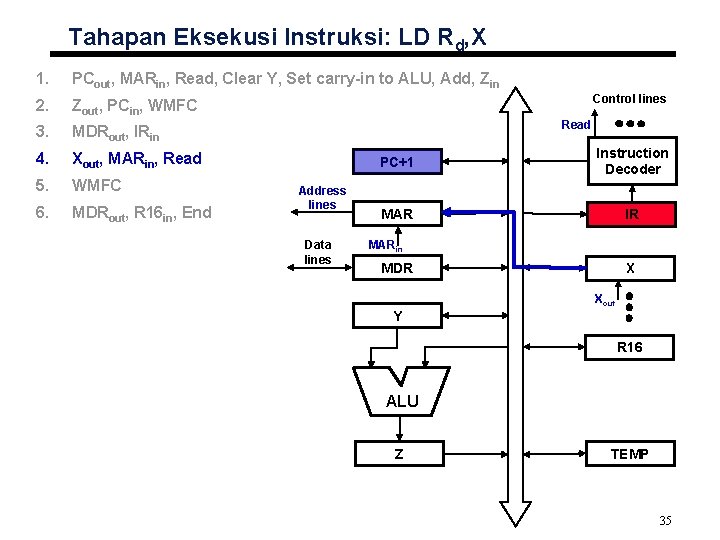

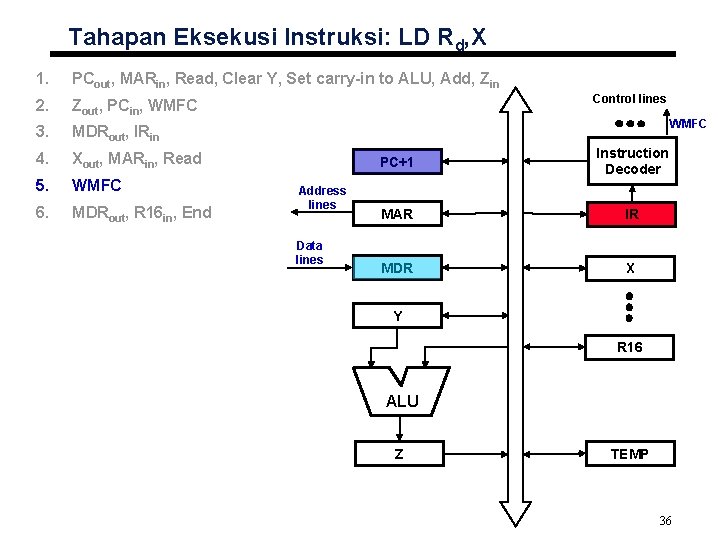

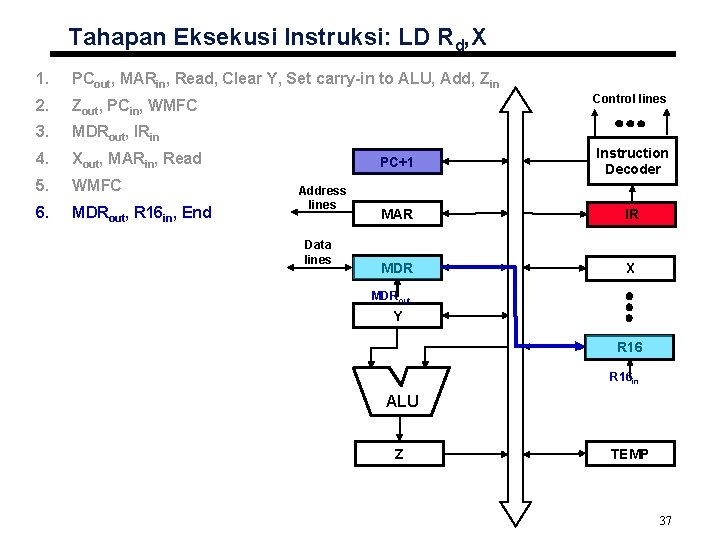

Tahapan Eksekusi Instruksi: LD Rd, X Instruksi: LD R 16, X ; R 16 M[X] Langkah-langkah: 1. Fetch instruksi 1. PCout, MARin, Read, Clear Y, Set carry-in to ALU, Add, Zin 2. Zout, PCin, WMFC 3. MDRout, IRin 2. Fetch operand dari lokasi memori yang ditunjuk oleh X 4. Xout, MARin, Read 5. WMFC 3. Lakukan operasi ALU 4. Simpan hasil penjumlahan di R 16 6. MDRout, R 16 in, End 31

Tahapan Eksekusi Instruksi: LD Rd, X 1. PCout, MARin, Read, Clear Y, Set carry-in to ALU, Add, Zin 2. Zout, PCin, WMFC 3. MDRout, IRin 4. Xout, MARin, Read 5. WMFC 6. MDRout, R 16 in, End Control lines Read Instruction Decoder PC Address lines Data lines Clear Y PCout MAR IR MARin MDR X 0000 Y R 16 Add ALU 1 Set PC+1 Carry-in Z TEMP Zin 32

Tahapan Eksekusi Instruksi: LD Rd, X 1. PCout, MARin, Read, Clear Y, Set carry-in to ALU, Add, Zin 2. Zout, PCin, WMFC 3. MDRout, IRin 4. Xout, MARin, Read 5. WMFC 6. MDRout, R 16 in, End Control lines WMFC PC Address lines Data lines Instruction Decoder PCin MAR IR MDR X Y R 16 ALU Z = PC+1 TEMP Zout 33

Tahapan Eksekusi Instruksi: LD Rd, X 1. PCout, MARin, Read, Clear Y, Set carry-in to ALU, Add, Zin 2. Zout, PCin, WMFC 3. MDRout, IRin 4. Xout, MARin, Read 5. WMFC 6. MDRout, R 16 in, End Control lines Address lines Data lines PC+1 Instruction Decoder MAR IR IRin MDR X MDRout Y R 16 ALU Z TEMP 34

Tahapan Eksekusi Instruksi: LD Rd, X 1. PCout, MARin, Read, Clear Y, Set carry-in to ALU, Add, Zin 2. Zout, PCin, WMFC 3. MDRout, IRin 4. Xout, MARin, Read 5. WMFC 6. MDRout, R 16 in, End Control lines Read Address lines Data lines PC+1 Instruction Decoder MAR IR MARin MDR X Xout Y R 16 ALU Z TEMP 35

Tahapan Eksekusi Instruksi: LD Rd, X 1. PCout, MARin, Read, Clear Y, Set carry-in to ALU, Add, Zin 2. Zout, PCin, WMFC 3. MDRout, IRin 4. Xout, MARin, Read 5. WMFC 6. MDRout, R 16 in, End Control lines WMFC Address lines Data lines PC+1 Instruction Decoder MAR IR MDR X Y R 16 ALU Z TEMP 36

Tahapan Eksekusi Instruksi: LD Rd, X 1. PCout, MARin, Read, Clear Y, Set carry-in to ALU, Add, Zin 2. Zout, PCin, WMFC 3. MDRout, IRin 4. Xout, MARin, Read 5. WMFC 6. MDRout, R 16 in, End Control lines Address lines Data lines PC+1 Instruction Decoder MAR IR MDR X MDRout Y R 16 in ALU Z TEMP 37

ADD Rd, Rs 38

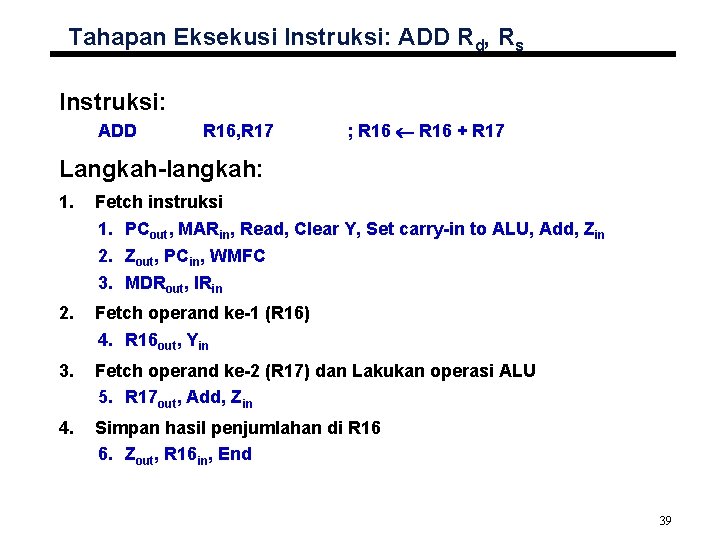

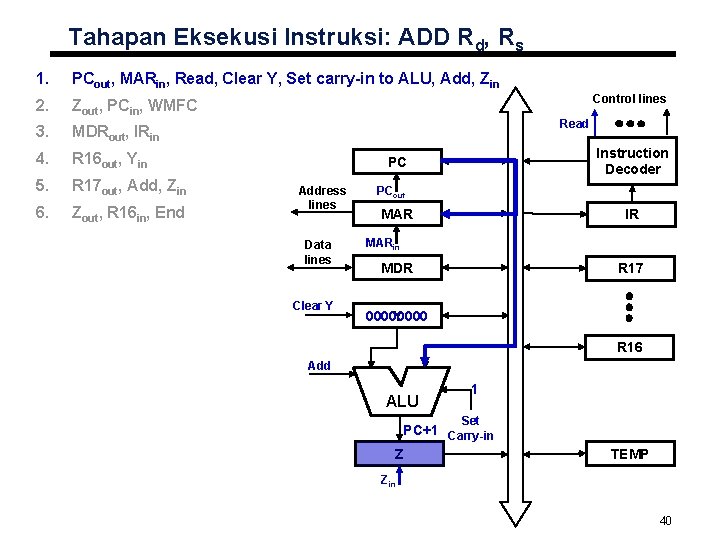

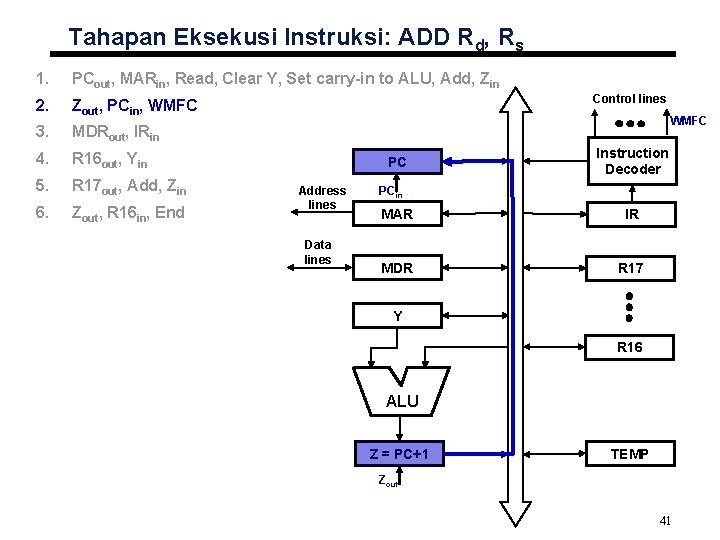

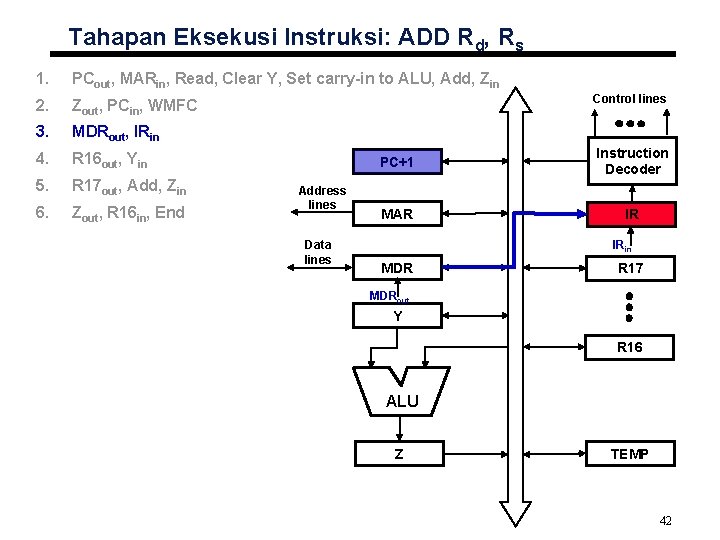

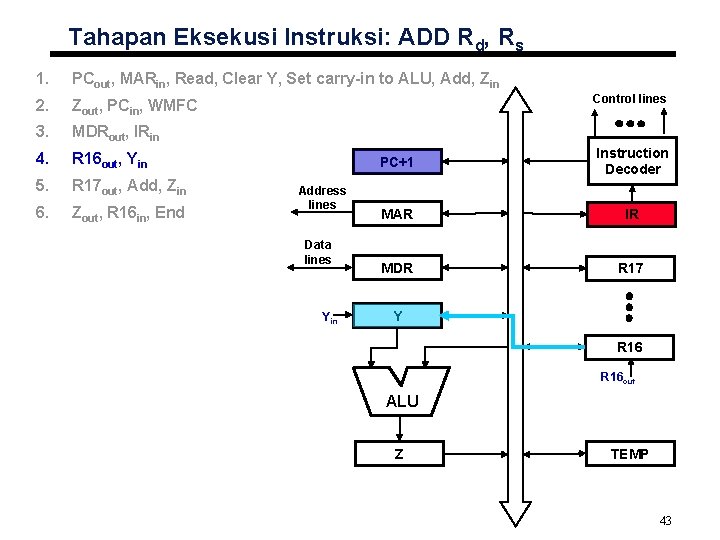

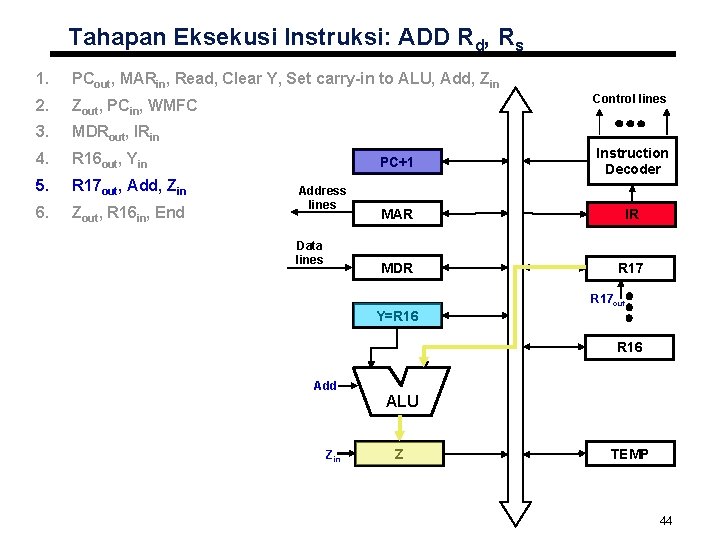

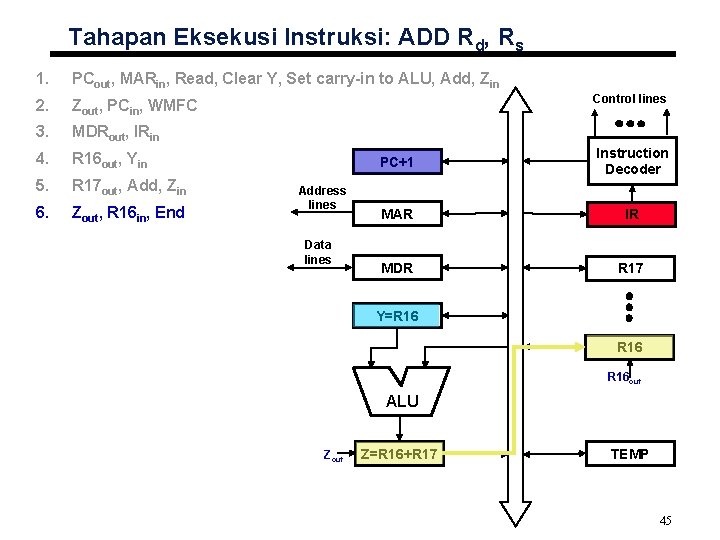

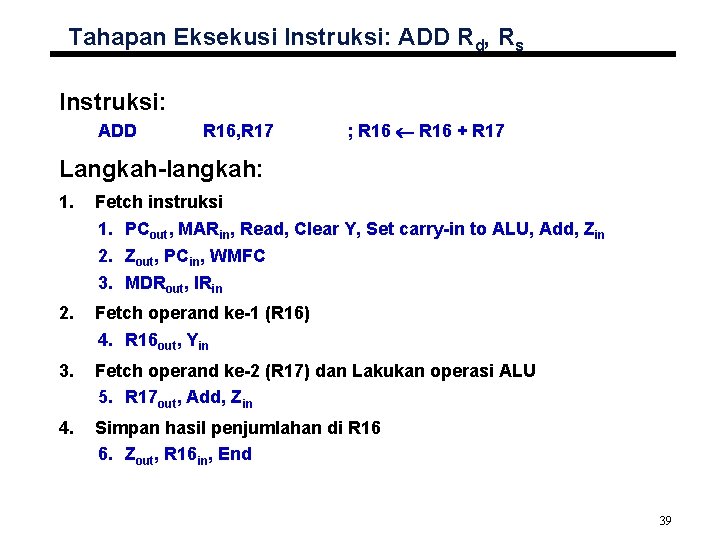

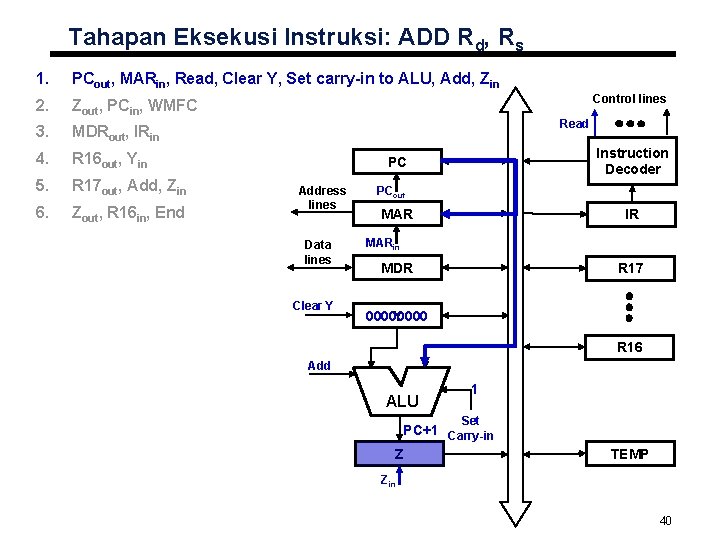

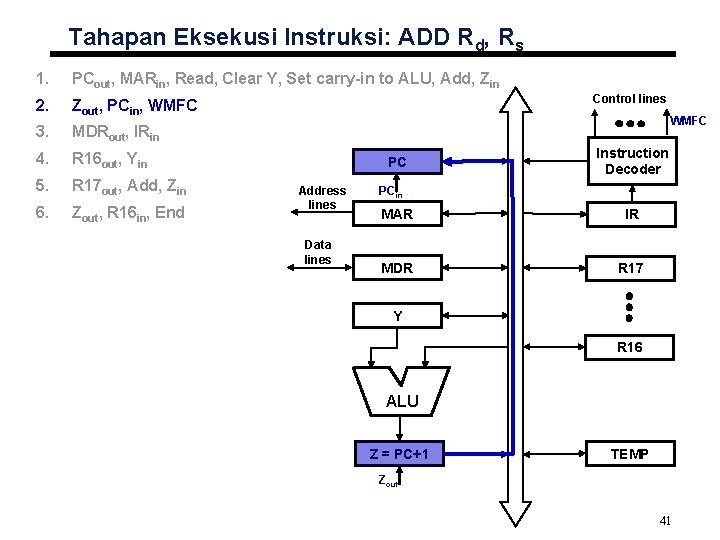

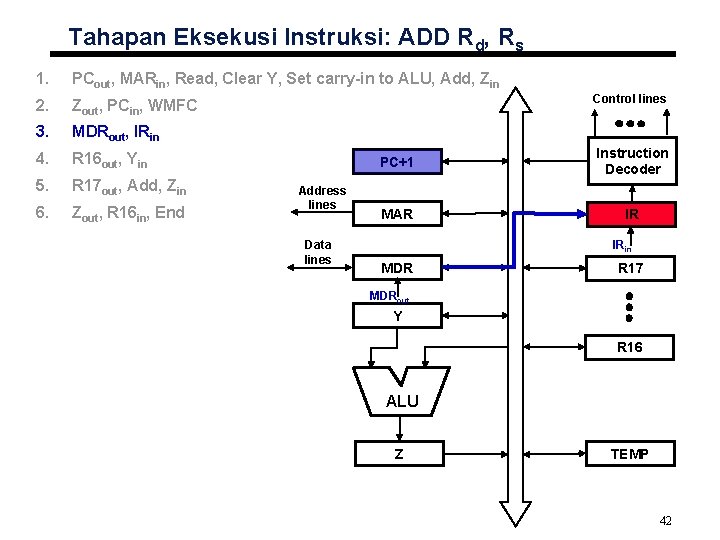

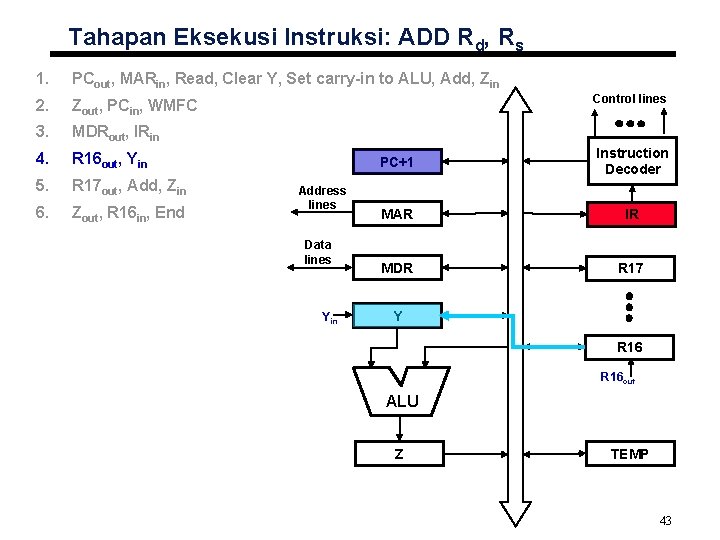

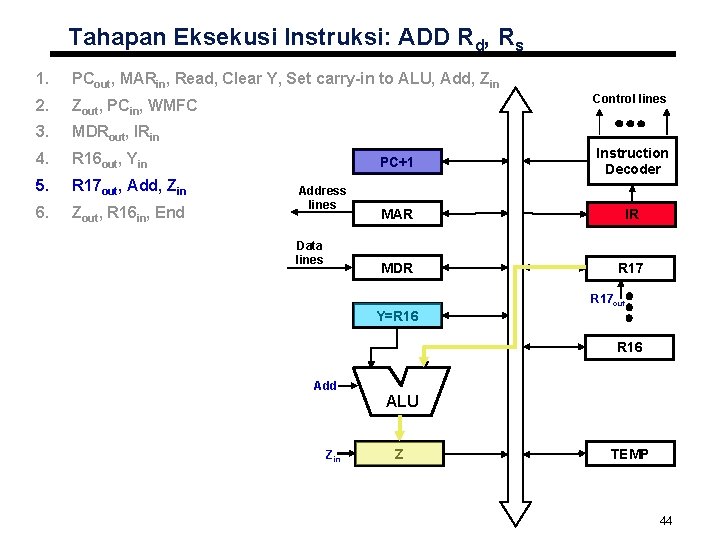

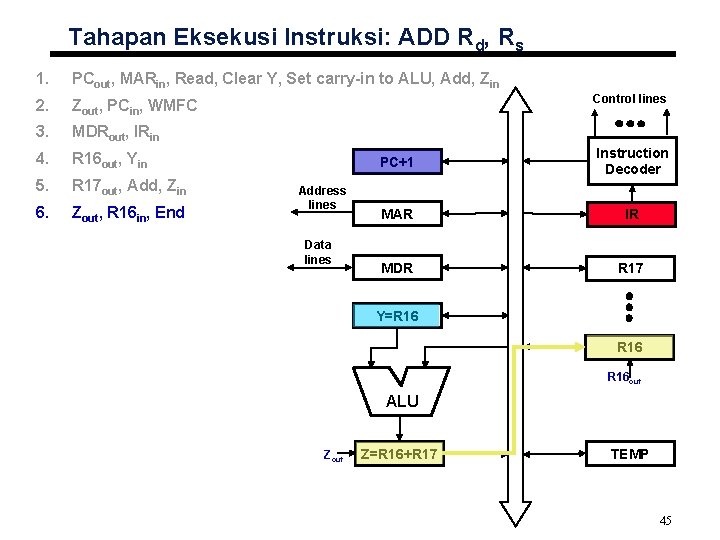

Tahapan Eksekusi Instruksi: ADD Rd, Rs Instruksi: ADD R 16, R 17 ; R 16 + R 17 Langkah-langkah: 1. Fetch instruksi 1. PCout, MARin, Read, Clear Y, Set carry-in to ALU, Add, Zin 2. Zout, PCin, WMFC 3. MDRout, IRin 2. Fetch operand ke-1 (R 16) 4. R 16 out, Yin 3. Fetch operand ke-2 (R 17) dan Lakukan operasi ALU 5. R 17 out, Add, Zin 4. Simpan hasil penjumlahan di R 16 6. Zout, R 16 in, End 39

Tahapan Eksekusi Instruksi: ADD Rd, Rs 1. PCout, MARin, Read, Clear Y, Set carry-in to ALU, Add, Zin 2. Zout, PCin, WMFC 3. MDRout, IRin 4. R 16 out, Yin 5. R 17 out, Add, Zin 6. Zout, R 16 in, End Control lines Read Instruction Decoder PC Address lines Data lines Clear Y PCout MAR IR MARin MDR R 17 0000 Y R 16 Add ALU 1 Set PC+1 Carry-in Z TEMP Zin 40

Tahapan Eksekusi Instruksi: ADD Rd, Rs 1. PCout, MARin, Read, Clear Y, Set carry-in to ALU, Add, Zin 2. Zout, PCin, WMFC 3. MDRout, IRin 4. R 16 out, Yin 5. R 17 out, Add, Zin 6. Zout, R 16 in, End Control lines WMFC PC Address lines Data lines Instruction Decoder PCin MAR IR MDR R 17 Y R 16 ALU Z = PC+1 TEMP Zout 41

Tahapan Eksekusi Instruksi: ADD Rd, Rs 1. PCout, MARin, Read, Clear Y, Set carry-in to ALU, Add, Zin 2. Zout, PCin, WMFC 3. MDRout, IRin 4. R 16 out, Yin 5. R 17 out, Add, Zin 6. Zout, R 16 in, End Control lines Address lines Data lines PC+1 Instruction Decoder MAR IR IRin MDR R 17 MDRout Y R 16 ALU Z TEMP 42

Tahapan Eksekusi Instruksi: ADD Rd, Rs 1. PCout, MARin, Read, Clear Y, Set carry-in to ALU, Add, Zin 2. Zout, PCin, WMFC 3. MDRout, IRin 4. R 16 out, Yin 5. R 17 out, Add, Zin 6. Zout, R 16 in, End Control lines Address lines Data lines Yin PC+1 Instruction Decoder MAR IR MDR R 17 Y R 16 out ALU Z TEMP 43

Tahapan Eksekusi Instruksi: ADD Rd, Rs 1. PCout, MARin, Read, Clear Y, Set carry-in to ALU, Add, Zin 2. Zout, PCin, WMFC 3. MDRout, IRin 4. R 16 out, Yin 5. R 17 out, Add, Zin 6. Zout, R 16 in, End Control lines Address lines Data lines PC+1 Instruction Decoder MAR IR MDR R 17 out Y=R 16 Add Zin ALU Z TEMP 44

Tahapan Eksekusi Instruksi: ADD Rd, Rs 1. PCout, MARin, Read, Clear Y, Set carry-in to ALU, Add, Zin 2. Zout, PCin, WMFC 3. MDRout, IRin 4. R 16 out, Yin 5. R 17 out, Add, Zin 6. Zout, R 16 in, End Control lines Address lines Data lines PC+1 Instruction Decoder MAR IR MDR R 17 Y=R 16 out ALU Zout Z=R 16+R 17 TEMP 45

Peningkatan Kinerja Prosesor 46

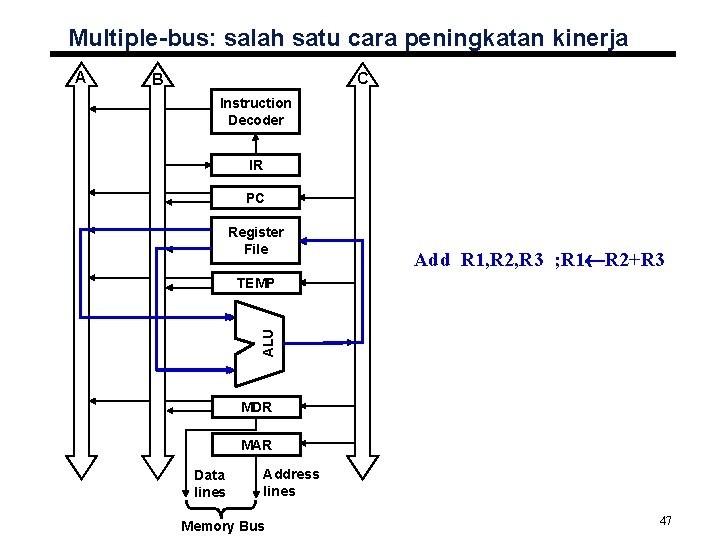

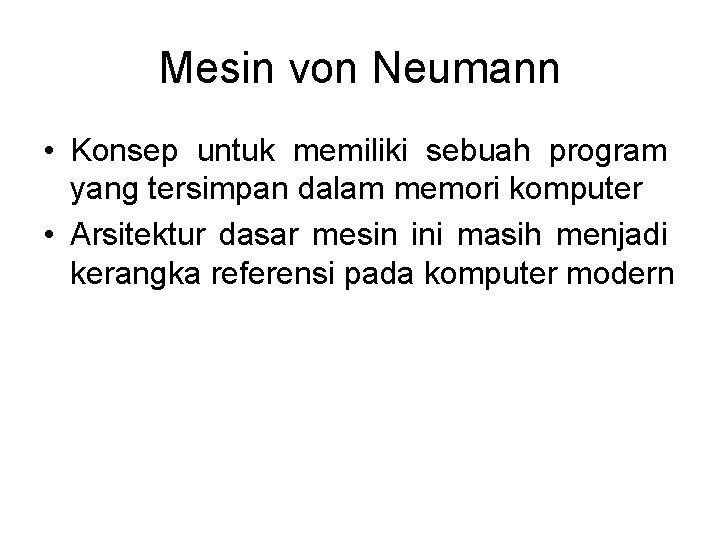

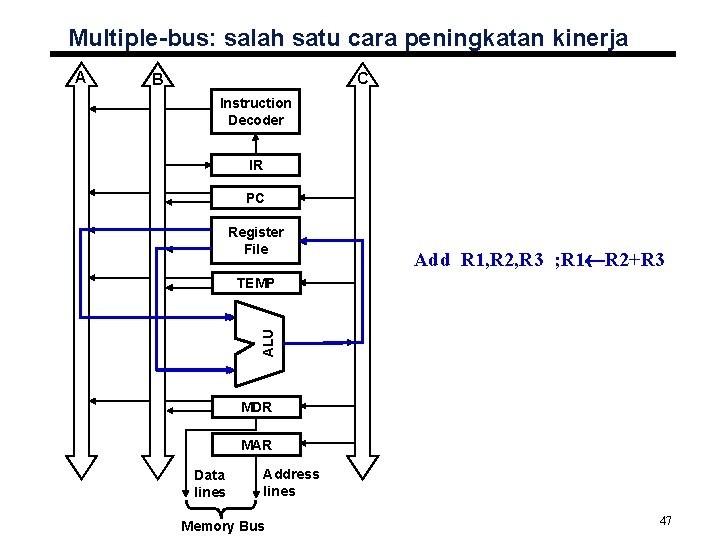

Multiple-bus: salah satu cara peningkatan kinerja C B Instruction Decoder IR PC Register File Add R 1, R 2, R 3 ; R 1 R 2+R 3 TEMP ALU A MDR MAR Data lines Address lines Memory Bus 47

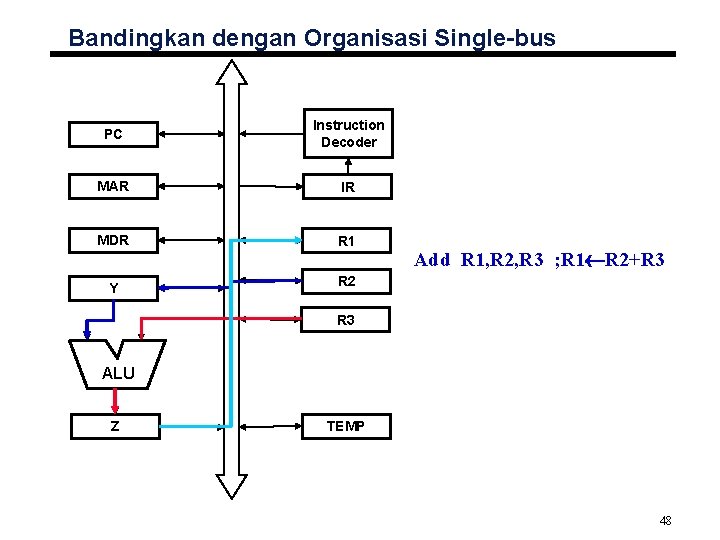

Bandingkan dengan Organisasi Single-bus PC Instruction Decoder MAR IR MDR R 1 Y Add R 1, R 2, R 3 ; R 1 R 2+R 3 R 2 R 3 ALU Z TEMP 48

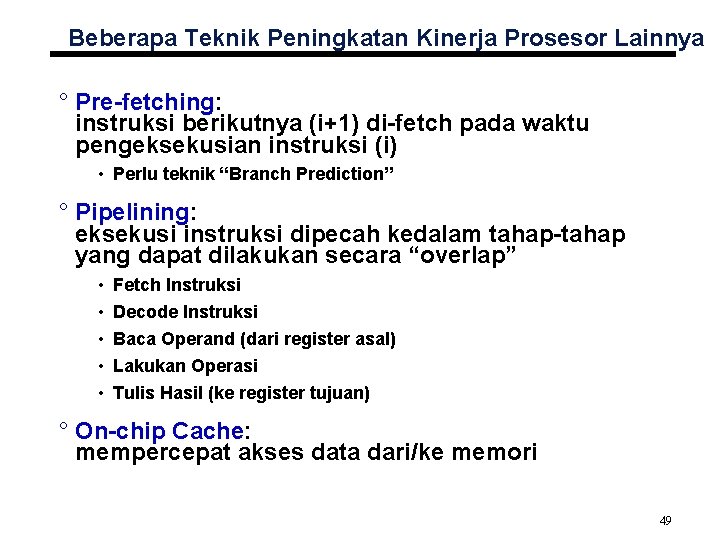

Beberapa Teknik Peningkatan Kinerja Prosesor Lainnya ° Pre-fetching: instruksi berikutnya (i+1) di-fetch pada waktu pengeksekusian instruksi (i) • Perlu teknik “Branch Prediction” ° Pipelining: eksekusi instruksi dipecah kedalam tahap-tahap yang dapat dilakukan secara “overlap” • • • Fetch Instruksi Decode Instruksi Baca Operand (dari register asal) Lakukan Operasi Tulis Hasil (ke register tujuan) ° On-chip Cache: mempercepat akses data dari/ke memori 49