Desain Prosesor Dan Datapath Oleh Devie Rosa Anamisa

- Slides: 14

Desain Prosesor Dan Datapath Oleh : Devie Rosa Anamisa

Pembahasan n n n Level-level Desain Prosesor Mikro Operasi Bahasa Transfer Register Organisasi Datapath Antarmuka memori Utama Register File

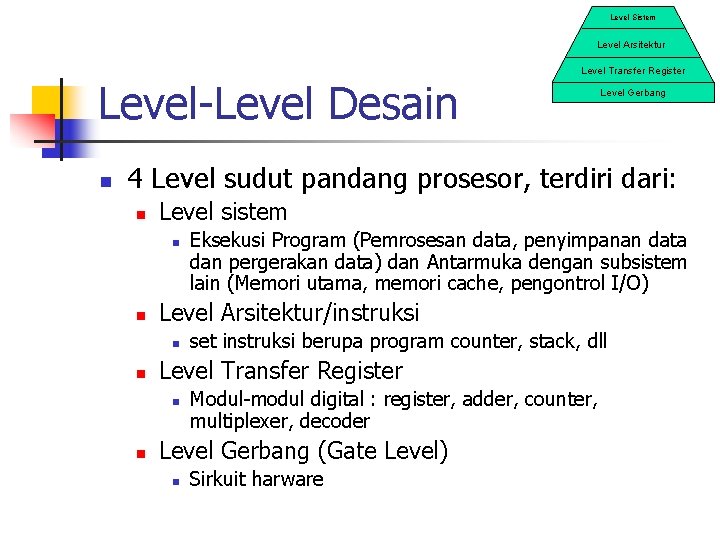

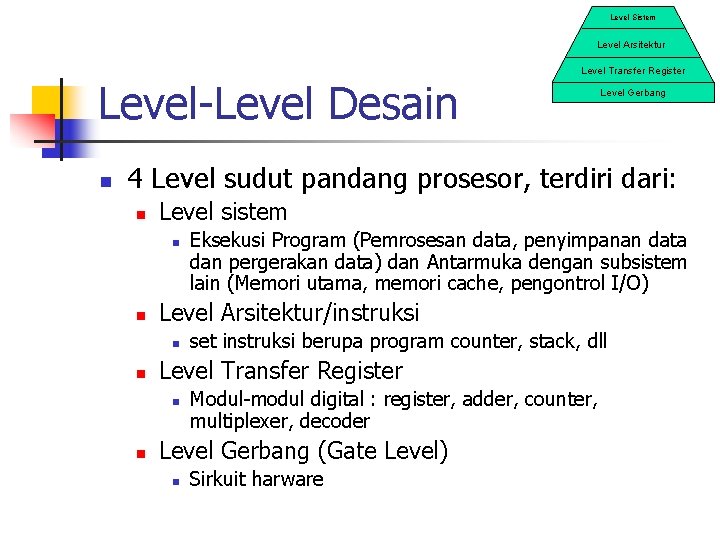

Level Sistem Level Arsitektur Level-Level Desain n Level Transfer Register Level Gerbang 4 Level sudut pandang prosesor, terdiri dari: n Level sistem n n Level Arsitektur/instruksi n n set instruksi berupa program counter, stack, dll Level Transfer Register n n Eksekusi Program (Pemrosesan data, penyimpanan data dan pergerakan data) dan Antarmuka dengan subsistem lain (Memori utama, memori cache, pengontrol I/O) Modul-modul digital : register, adder, counter, multiplexer, decoder Level Gerbang (Gate Level) n Sirkuit harware

Tipe-Tipe Processor n n Uniprocessor Multiprocessor Array Processor Network Processor

Proses Desain Prosesor n n n Mengerti dengan baik setiap instruksi Menetapkan sumber daya hardware yang dihubungkan(register, flag, stack, dll) Menerjemahkan setiap instruksi Menganalisa sirkuit datapath Mengaktifkan titik-titik kontrol

Mikro Operasi n Dikelompokan kedalam 4 tipe: n Mikro operasi transfer register n n Mikro operasi aritmetika n n Melakukan operasi aritmetika pada data dalam register Mikro operasi logika n n Menyalin isi salah satu register ke register lain tanpa mengubah isi sumber Melakukan operasi manipulasi bit pada data dalam register Mikro operasi pergeseran n 0 n Melakukan operasi pergeseran pada data dalam register. Misal : pergeseran logika, seperti bit 0 masuk kedalam posisi bit kosong (terkiri atau terkanan) (a) Operasi geser logika ke kanan

Bahasa Transfer Register n n n RTL (Register Transfer Language) Adalah sebuah notasi yang digunakan untuk menentukan transfer mikro operasi antar register, lebih ke tingkah laku instruksi dan organisasi sebuah komputer. Misal : R 3 : = R 1 menujukkan suatu transfer register sederhana yang melibatkan dua register R 1 dan R 3 dimana isi register R 1 ditransfer (disalin) ke register R 3.

Organisasi Datapath n n Datapath merupakan komponen hardware Diistilahkan sebagai: n n ALU Register sebagai penyimpanan sementara Sirkuit driver untuk mentransmisikan sinyal ke unit eksternal(memori, I/O) Sirkuit receiver untuk menerima sinyal dari unit eksternal

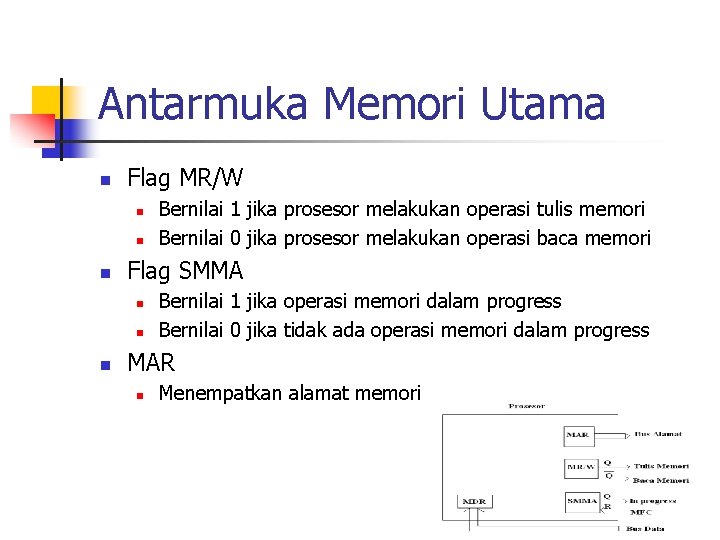

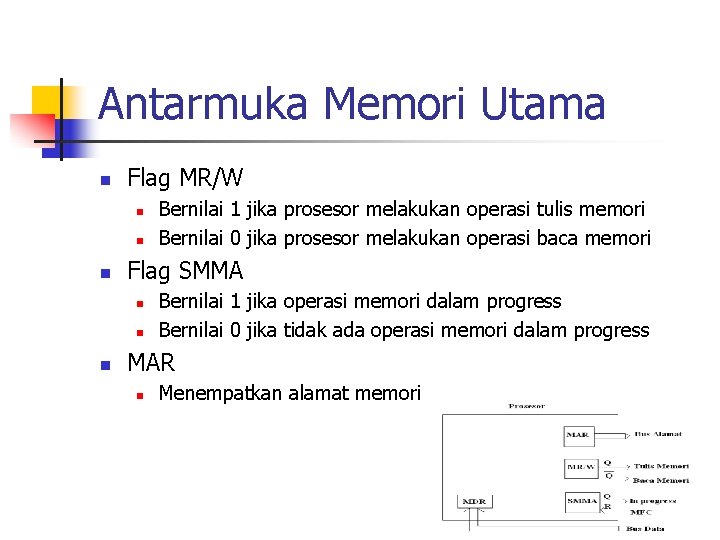

Antarmuka Memori Utama n Flag MR/W n n n Flag SMMA n n n Bernilai 1 jika prosesor melakukan operasi tulis memori Bernilai 0 jika prosesor melakukan operasi baca memori Bernilai 1 jika operasi memori dalam progress Bernilai 0 jika tidak ada operasi memori dalam progress MAR n Menempatkan alamat memori

Operasi Pembacaan Memori oleh Prosesor 1. 2. 3. 4. Menempatkan alamat memori dalam MAR Me-reset flip-flop MR/W menuju ke MEMORI READ Men-set flag SMMA Memeriksa apakah flag SMMA sudah menjadi 0. ketika SMMA menjadi 0 maka prosesor meload data dari memori ke MDR.

Operasi Penulisan Memori oleh Prosesor n n n Menempatkan alamat memori dalam MAR Menempatkan data dalam MDR Menset flip-flop MR/W menuju MEMORI WRITE Menset flag SMMA Memeriksa apakah flag SMMA sudah menjadi 0, ketika SMMA menjadi 0 maka prosesor memulai operasi lain

Register File n n Terdiri dari sekumpulan register prosesor. Terdapat 2 tipe register: n Program addressable register n n n Untuk menyimpan operand dan hasil Untuk register khusus, seperti stack pointer Scartch pad register n n n Untuk register sementara oleh unit kontrol Untuk penyimpanan hasil sementara Sebagai konstanta yang diperlukan selama eksekusi suatu instruksi

Macam-Macam Instruksi n Instruksi HALT n n n Instruksi JUMP n n n Menghentikan siklus instruksi Hal ini digambarkan dengan RUN/HALT: =0 Bercabang ke alamat instruksi Digambarkan dengan PC: =BA, dimana BA adalah alamat cabang yang diberikan oleh instruksi yang ada di register ALU. Instruksi LOAD n n Menyalin isi suatu lokasi memori ke dalam suatu register Digambarkan dengan <RA>: =<MA>, dimana MA adalah alamat memori dan RA adalah alamat register.

Terima Kasih