Cp E 442 Computer Architecture and Engineering Designing

- Slides: 38

Cp. E 442 Computer Architecture and Engineering Designing Single Cycle Control cs 152 control. 1 ©DAP & SIK 1995

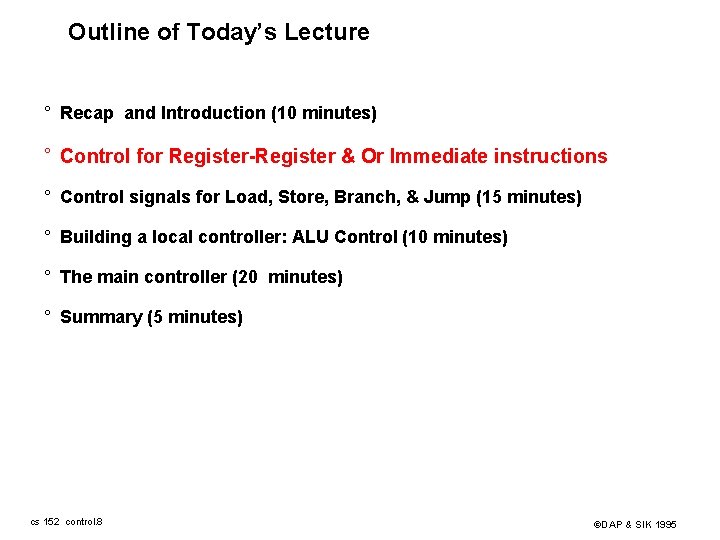

Outline of Today’s Lecture ° Recap and Introduction (10 minutes) ° Control for Register-Register & Or Immediate instructions (10 minutes) ° Control signals for Load, Store, Branch, & Jump (15 minutes) ° Building a local controller: ALU Control (10 minutes) ° The main controller (20 minutes) ° Summary (5 minutes) cs 152 control. 2 ©DAP & SIK 1995

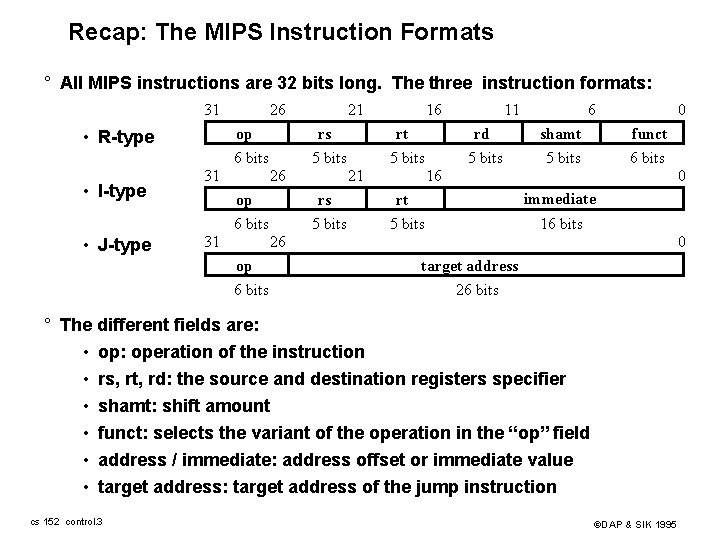

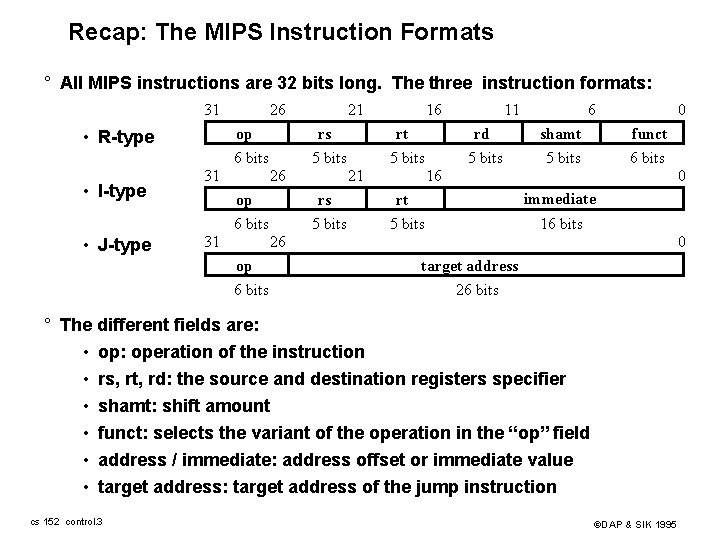

Recap: The MIPS Instruction Formats ° All MIPS instructions are 32 bits long. The three instruction formats: 31 26 op • R-type rs 6 bits • I-type • J-type 31 21 op 6 bits 31 rt 5 bits 26 16 5 bits 21 rs 5 bits 11 6 0 rd shamt funct 5 bits 6 bits 16 rt 5 bits 0 immediate 16 bits 26 op 6 bits 0 target address 26 bits ° The different fields are: • op: operation of the instruction • rs, rt, rd: the source and destination registers specifier • shamt: shift amount • funct: selects the variant of the operation in the “op” field • address / immediate: address offset or immediate value • target address: target address of the jump instruction cs 152 control. 3 ©DAP & SIK 1995

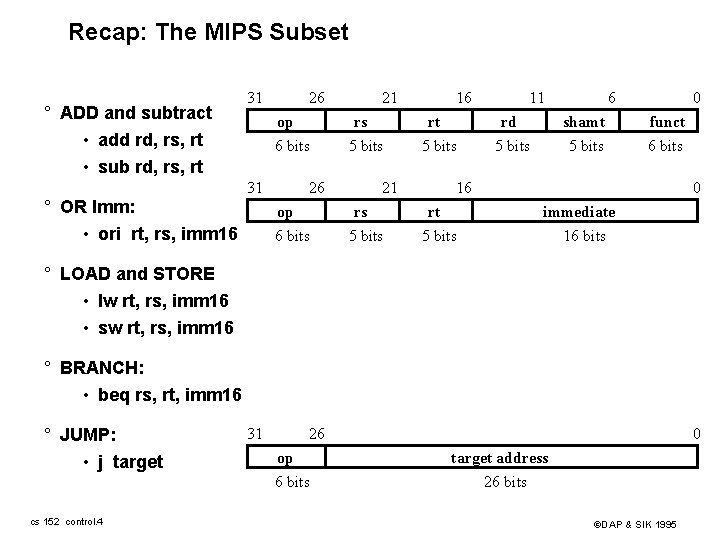

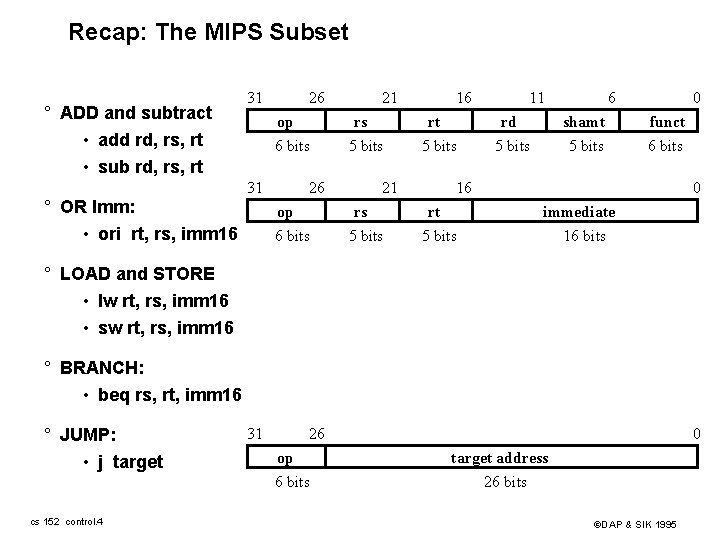

Recap: The MIPS Subset ° ADD and subtract • add rd, rs, rt • sub rd, rs, rt ° OR Imm: • ori rt, rs, imm 16 31 26 op 6 bits 21 rs 5 bits 16 rt 5 bits 11 rd 5 bits 6 shamt 5 bits 0 funct 6 bits 16 rt 5 bits 0 immediate 16 bits ° LOAD and STORE • lw rt, rs, imm 16 • sw rt, rs, imm 16 ° BRANCH: • beq rs, rt, imm 16 ° JUMP: • j target cs 152 control. 4 31 26 op 6 bits 0 target address 26 bits ©DAP & SIK 1995

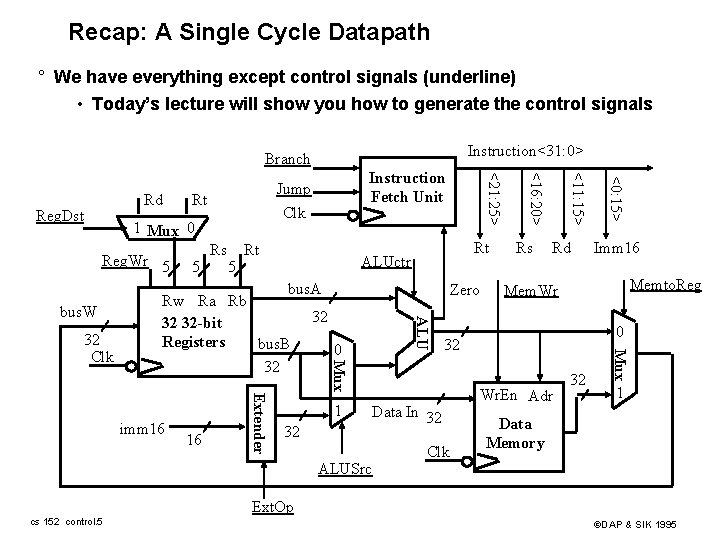

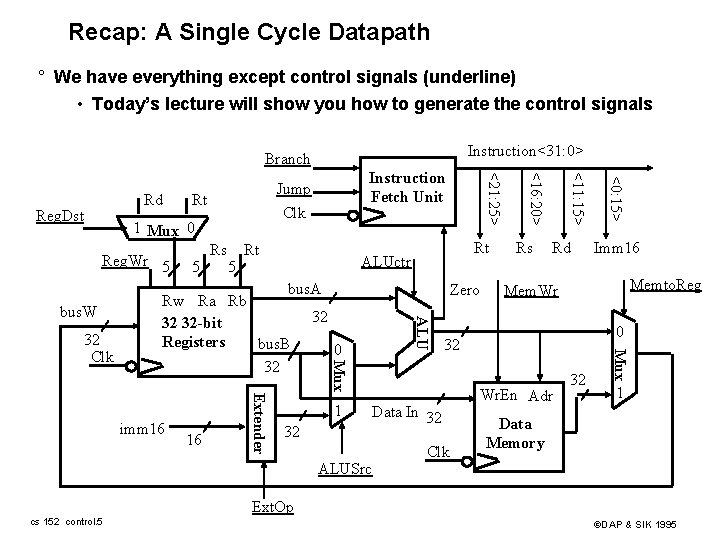

Recap: A Single Cycle Datapath ° We have everything except control signals (underline) • Today’s lecture will show you how to generate the control signals Instruction<31: 0> Branch 5 Rs 5 Rt Rt ALUctr bus. A 0 1 32 cs 152 control. 5 Clk Imm 16 Memto. Reg Mem. Wr 0 32 Data In 32 ALUSrc Rd Wr. En Adr 32 Mux 16 Extender imm 16 32 Mux 32 Clk Rw Ra Rb 32 32 -bit Registers bus. B 32 ALU bus. W Zero Rs <0: 15> Reg. Wr 5 <11: 15> 1 Mux 0 <16: 20> Reg. Dst Rt <21: 25> Rd Instruction Fetch Unit Jump Clk 1 Data Memory Ext. Op ©DAP & SIK 1995

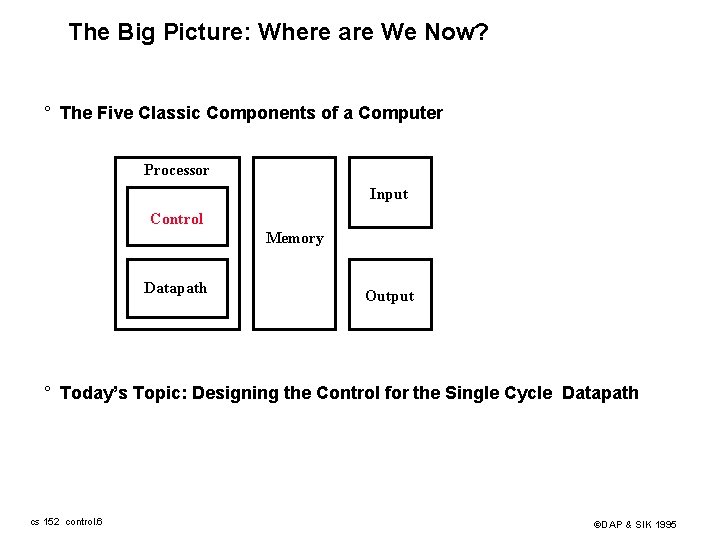

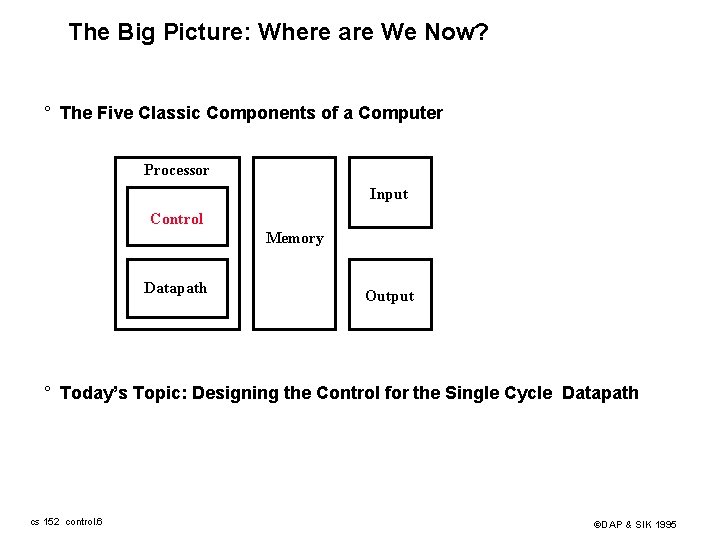

The Big Picture: Where are We Now? ° The Five Classic Components of a Computer Processor Input Control Memory Datapath Output ° Today’s Topic: Designing the Control for the Single Cycle Datapath cs 152 control. 6 ©DAP & SIK 1995

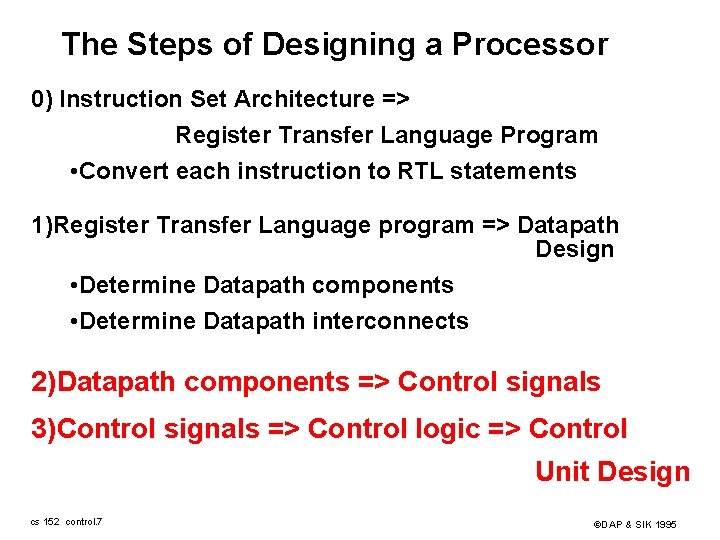

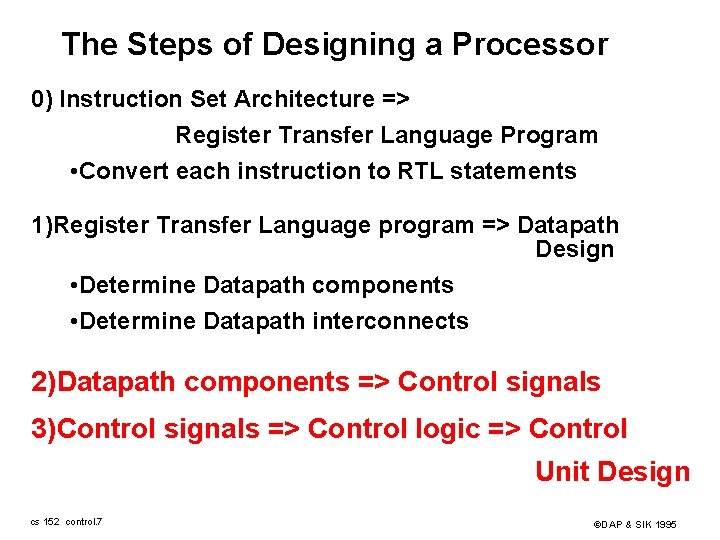

The Steps of Designing a Processor 0) Instruction Set Architecture => Register Transfer Language Program • Convert each instruction to RTL statements 1)Register Transfer Language program => Datapath Design • Determine Datapath components • Determine Datapath interconnects 2)Datapath components => Control signals 3)Control signals => Control logic => Control Unit Design cs 152 control. 7 ©DAP & SIK 1995

Outline of Today’s Lecture ° Recap and Introduction (10 minutes) ° Control for Register-Register & Or Immediate instructions ° Control signals for Load, Store, Branch, & Jump (15 minutes) ° Building a local controller: ALU Control (10 minutes) ° The main controller (20 minutes) ° Summary (5 minutes) cs 152 control. 8 ©DAP & SIK 1995

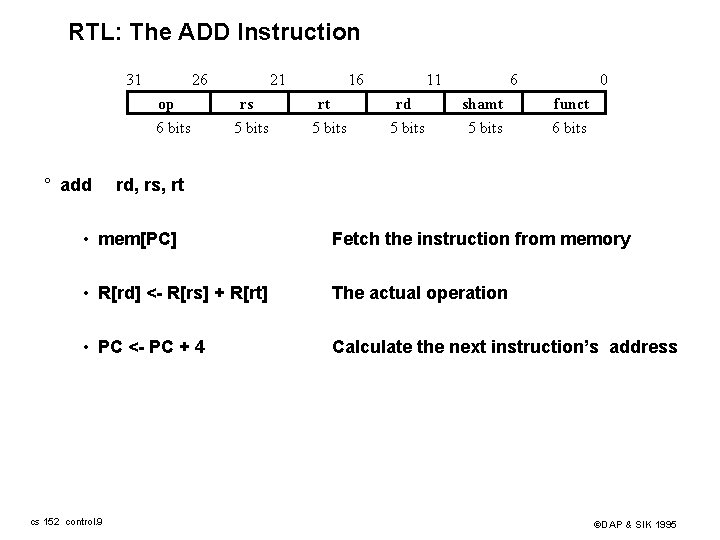

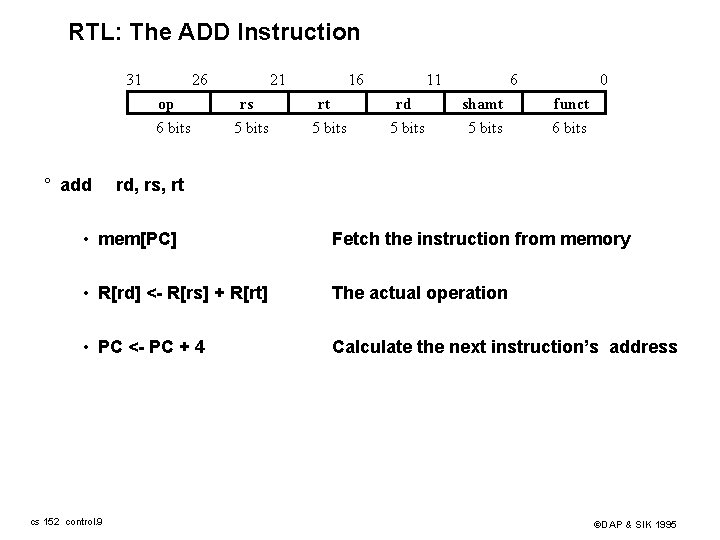

RTL: The ADD Instruction 31 26 op 6 bits ° add 21 rs 5 bits 16 rt 5 bits 11 rd 5 bits 6 shamt 5 bits 0 funct 6 bits rd, rs, rt • mem[PC] Fetch the instruction from memory • R[rd] <- R[rs] + R[rt] The actual operation • PC <- PC + 4 Calculate the next instruction’s address cs 152 control. 9 ©DAP & SIK 1995

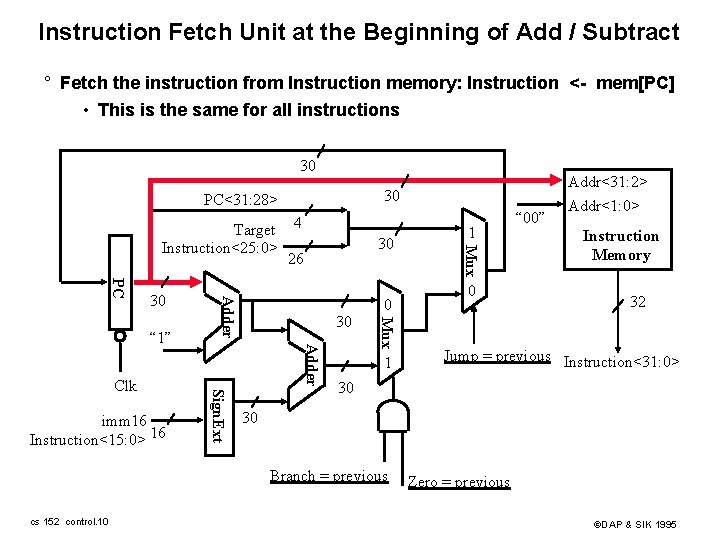

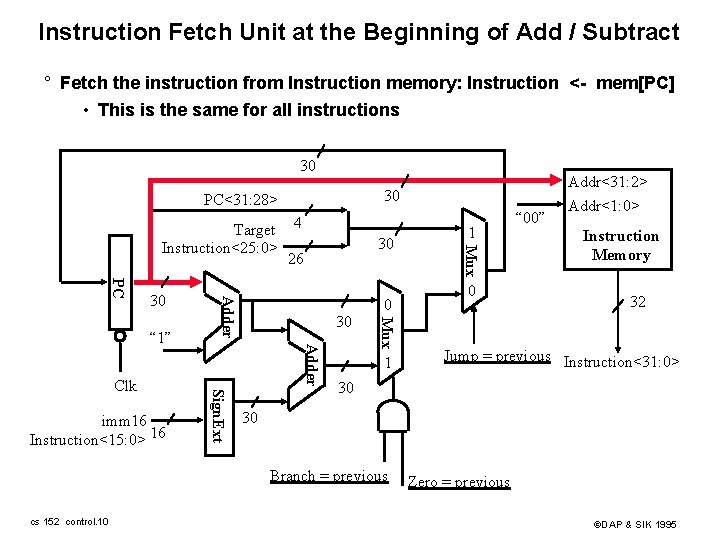

Instruction Fetch Unit at the Beginning of Add / Subtract ° Fetch the instruction from Instruction memory: Instruction <- mem[PC] • This is the same for all instructions 30 30 PC<31: 28> 0 Mux imm 16 Instruction<15: 0> 16 Sign. Ext Clk 30 Adder “ 1” 30 26 Adder PC 30 4 1 0 “ 00” Instruction Memory 32 Jump = previous Instruction<31: 0> 30 30 Branch = previous cs 152 control. 10 1 Mux Target Instruction<25: 0> Addr<31: 2> Addr<1: 0> Zero = previous ©DAP & SIK 1995

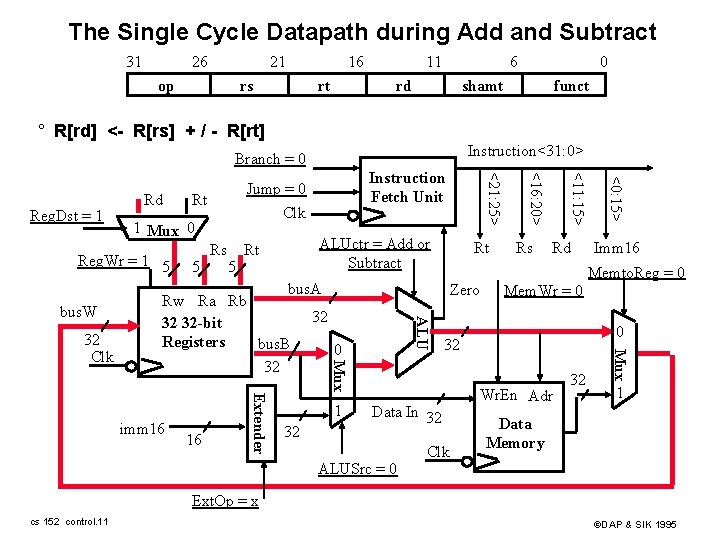

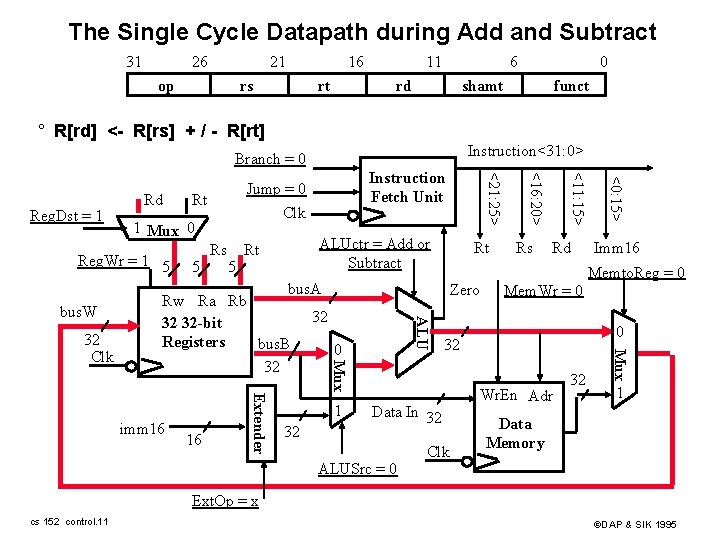

The Single Cycle Datapath during Add and Subtract 31 26 21 op rs 16 rt 11 6 rd 0 shamt funct ° R[rd] <- R[rs] + / - R[rt] Instruction<31: 0> Branch = 0 Zero 32 Clk Imm 16 Memto. Reg = 0 Mem. Wr = 0 0 32 Data In 32 ALUSrc = 0 Rd Wr. En Adr 32 Mux ALU 16 Extender imm 16 1 Rs <0: 15> bus. A Rw Ra Rb 32 32 32 -bit Registers bus. B 0 32 Rt <11: 15> 5 ALUctr = Add or Subtract Rt Mux 32 Clk 5 Rs <16: 20> 1 Mux 0 Reg. Wr = 1 5 bus. W Rt <21: 25> Reg. Dst = 1 Rd Instruction Fetch Unit Jump = 0 Clk 1 Data Memory Ext. Op = x cs 152 control. 11 ©DAP & SIK 1995

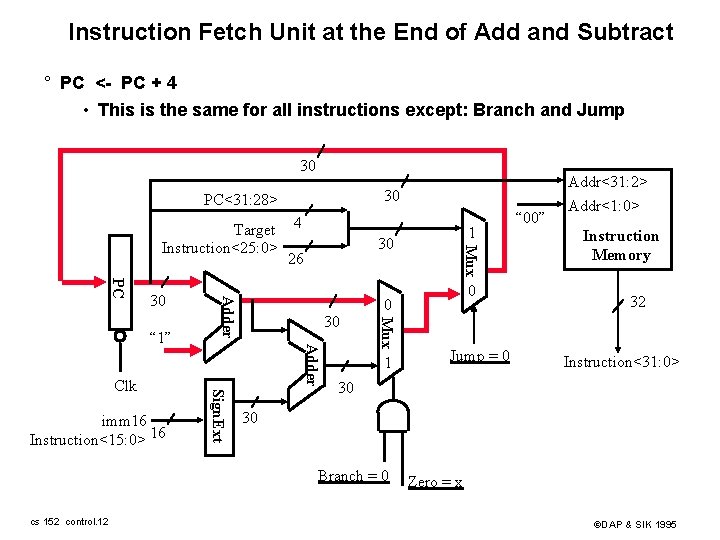

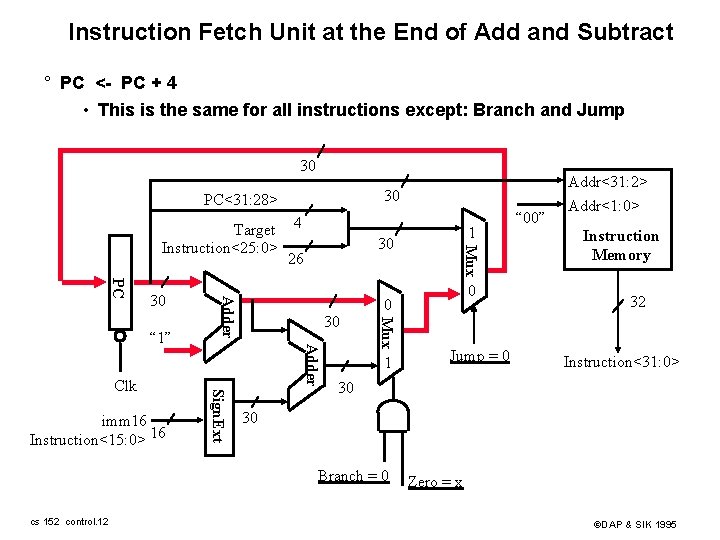

Instruction Fetch Unit at the End of Add and Subtract ° PC <- PC + 4 • This is the same for all instructions except: Branch and Jump 30 30 PC<31: 28> 30 1 0 Jump = 0 “ 00” Instruction Memory 32 Instruction<31: 0> 30 30 Branch = 0 cs 152 control. 12 1 0 Mux imm 16 Instruction<15: 0> 16 Sign. Ext Clk 26 Adder “ 1” 30 Adder PC 30 4 Mux Target Instruction<25: 0> Addr<31: 2> Addr<1: 0> Zero = x ©DAP & SIK 1995

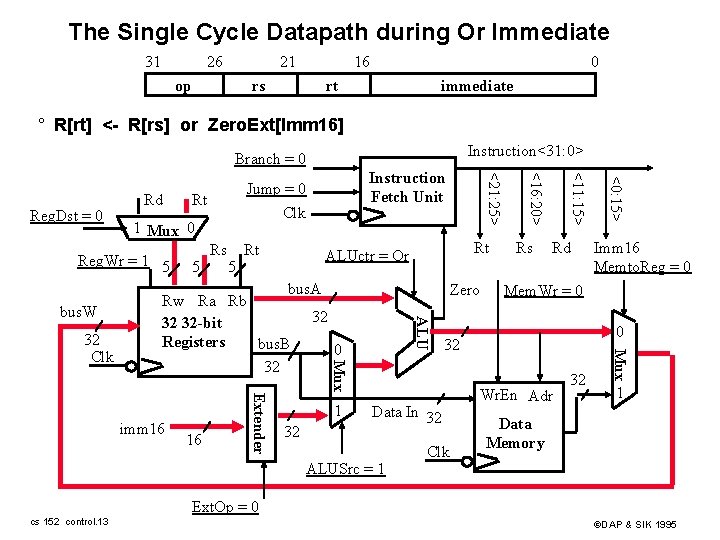

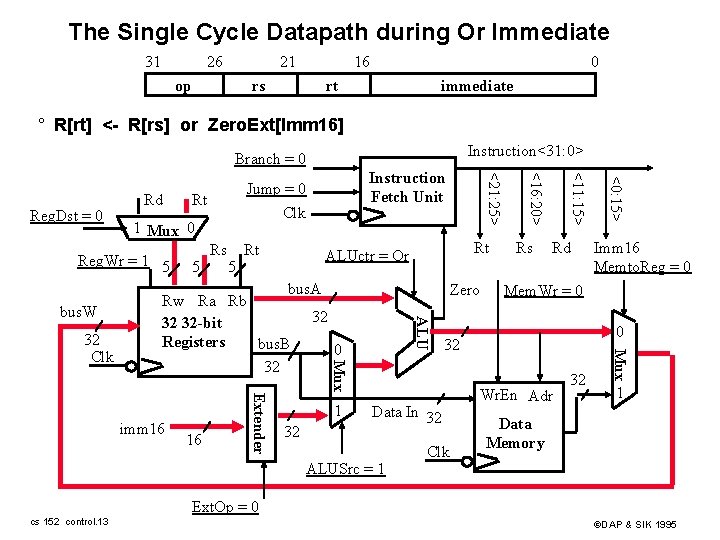

The Single Cycle Datapath during Or Immediate 31 26 21 op 16 rs 0 immediate rt ° R[rt] <- R[rs] or Zero. Ext[Imm 16] Instruction<31: 0> Branch = 0 Zero 32 Clk Imm 16 Memto. Reg = 0 Mem. Wr = 0 0 32 Data In 32 ALUSrc = 1 Rd Wr. En Adr 32 Mux ALU Extender 16 1 Rs <0: 15> bus. A Rw Ra Rb 32 32 32 -bit Registers bus. B 0 32 imm 16 cs 152 control. 13 Rt ALUctr = Or <11: 15> 5 Rt Mux 32 Clk 5 Rs <16: 20> 1 Mux 0 Reg. Wr = 1 5 bus. W Rt <21: 25> Reg. Dst = 0 Rd Instruction Fetch Unit Jump = 0 Clk 1 Data Memory Ext. Op = 0 ©DAP & SIK 1995

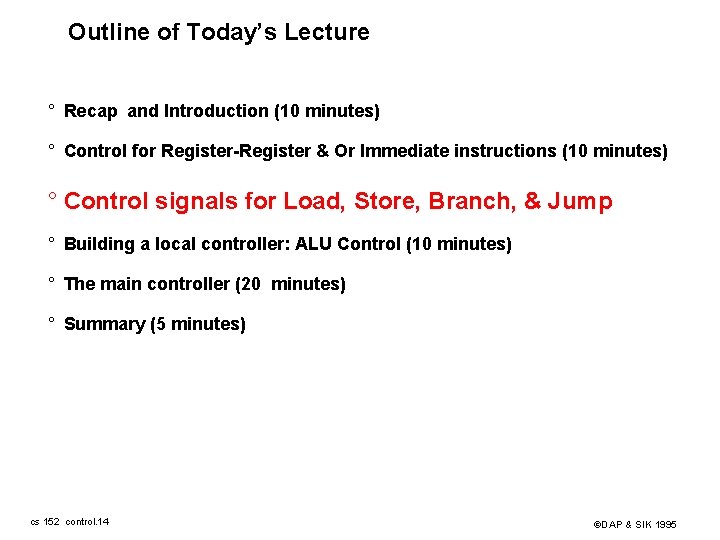

Outline of Today’s Lecture ° Recap and Introduction (10 minutes) ° Control for Register-Register & Or Immediate instructions (10 minutes) ° Control signals for Load, Store, Branch, & Jump ° Building a local controller: ALU Control (10 minutes) ° The main controller (20 minutes) ° Summary (5 minutes) cs 152 control. 14 ©DAP & SIK 1995

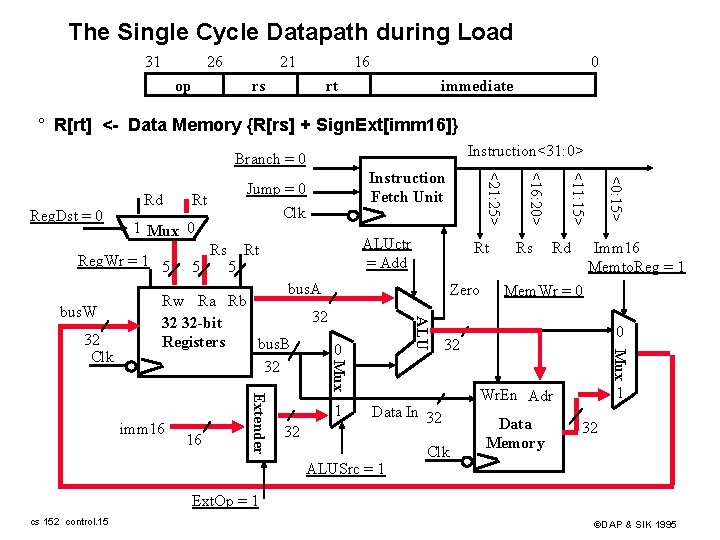

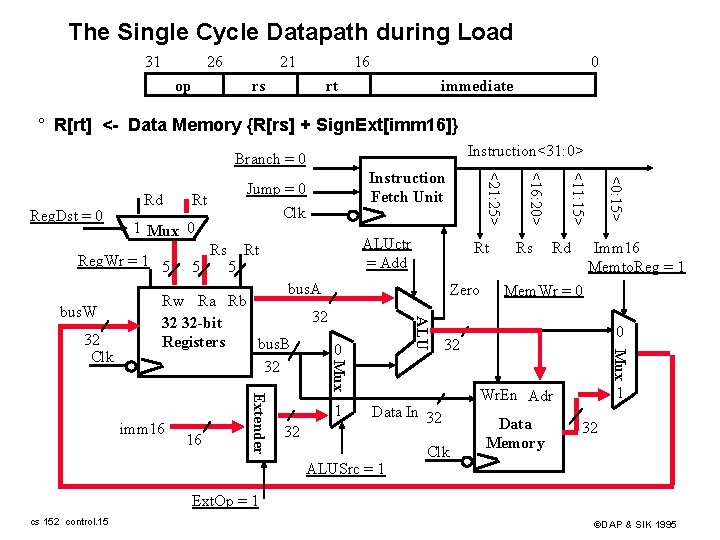

The Single Cycle Datapath during Load 31 26 21 op 16 rs 0 immediate rt ° R[rt] <- Data Memory {R[rs] + Sign. Ext[imm 16]} Instruction<31: 0> Branch = 0 Zero 32 Imm 16 Memto. Reg = 1 Mem. Wr = 0 0 32 Data In 32 ALUSrc = 1 Rd Clk Mux ALU 16 Extender imm 16 1 Rs <0: 15> bus. A Rw Ra Rb 32 32 32 -bit Registers bus. B 0 32 Rt <11: 15> 5 ALUctr = Add Rt Mux 32 Clk 5 Rs <16: 20> 1 Mux 0 Reg. Wr = 1 5 bus. W Rt <21: 25> Reg. Dst = 0 Rd Instruction Fetch Unit Jump = 0 Clk 1 Wr. En Adr Data Memory 32 Ext. Op = 1 cs 152 control. 15 ©DAP & SIK 1995

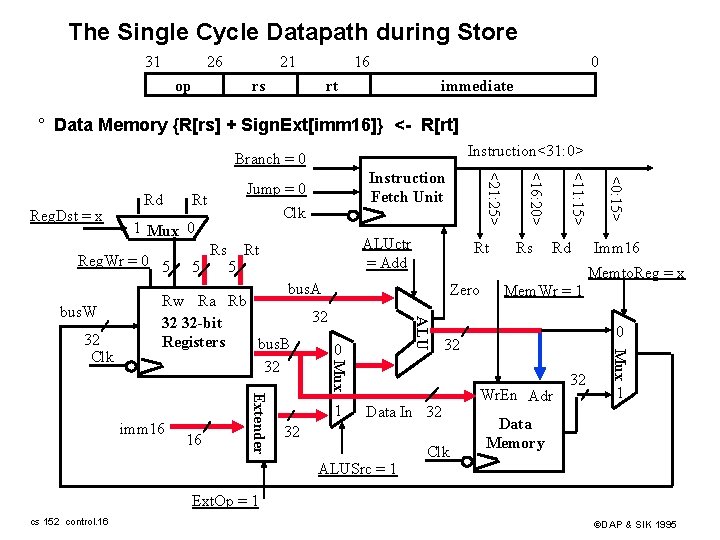

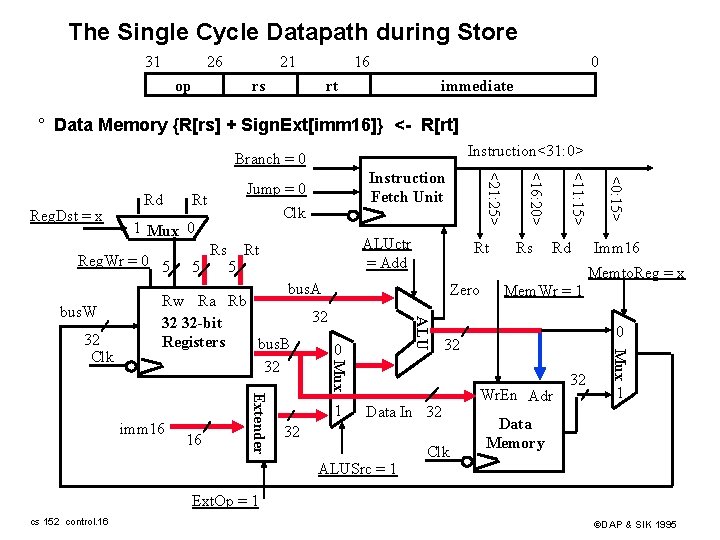

The Single Cycle Datapath during Store 31 26 21 op rs 16 0 immediate rt ° Data Memory {R[rs] + Sign. Ext[imm 16]} <- R[rt] Instruction<31: 0> Branch = 0 Zero 32 Clk Imm 16 Memto. Reg = x Mem. Wr = 1 0 32 Data In 32 ALUSrc = 1 Rd Wr. En Adr 32 Mux ALU 16 Extender imm 16 1 Rs <0: 15> bus. A Rw Ra Rb 32 32 32 -bit Registers bus. B 0 32 Rt <11: 15> 5 ALUctr = Add Rt Mux 32 Clk 5 Rs <16: 20> 1 Mux 0 Reg. Wr = 0 5 bus. W Rt <21: 25> Reg. Dst = x Rd Instruction Fetch Unit Jump = 0 Clk 1 Data Memory Ext. Op = 1 cs 152 control. 16 ©DAP & SIK 1995

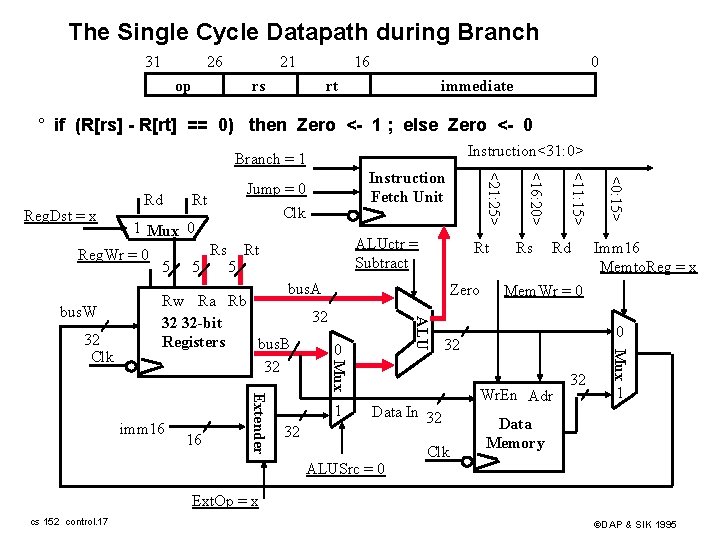

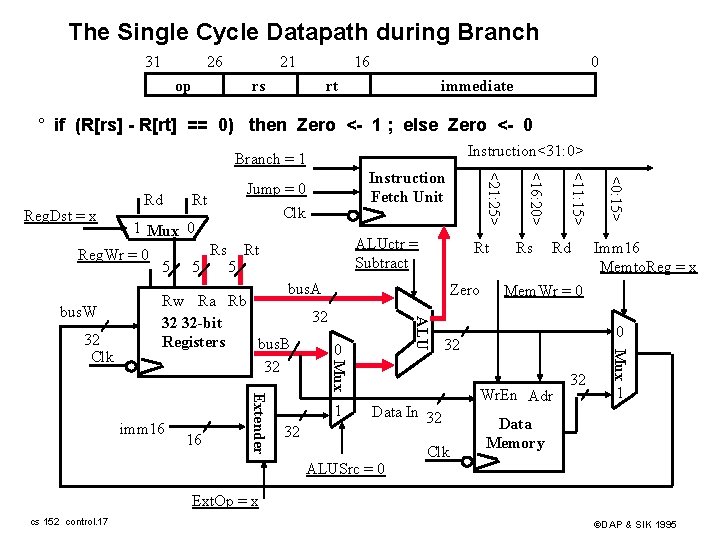

The Single Cycle Datapath during Branch 31 26 21 op 16 rs 0 immediate rt ° if (R[rs] - R[rt] == 0) then Zero <- 1 ; else Zero <- 0 Instruction<31: 0> Branch = 1 Zero ALU 16 Extender imm 16 1 32 Clk Imm 16 Memto. Reg = x Mem. Wr = 0 0 32 Data In 32 ALUSrc = 0 Rd Wr. En Adr 32 Mux bus. A Rw Ra Rb 32 32 32 -bit Registers bus. B 0 32 Rs <0: 15> 5 Rt <11: 15> 5 ALUctr = Subtract Rt Mux 32 Clk 5 Rs <16: 20> 1 Mux 0 Reg. Wr = 0 bus. W Rt <21: 25> Reg. Dst = x Rd Instruction Fetch Unit Jump = 0 Clk 1 Data Memory Ext. Op = x cs 152 control. 17 ©DAP & SIK 1995

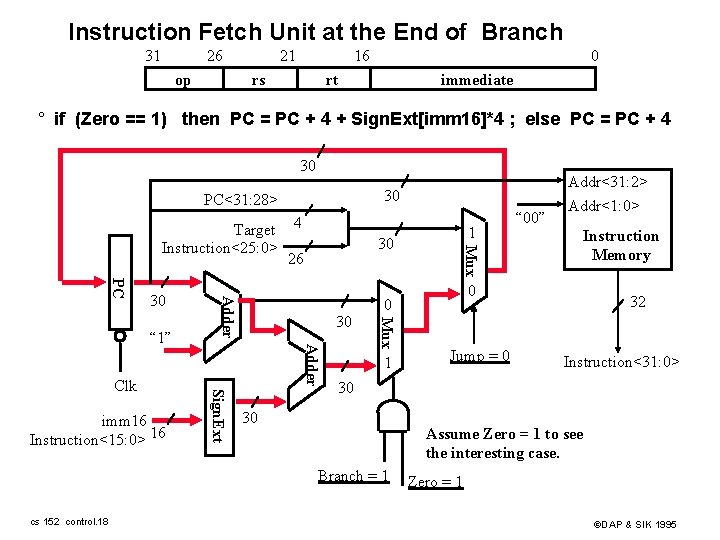

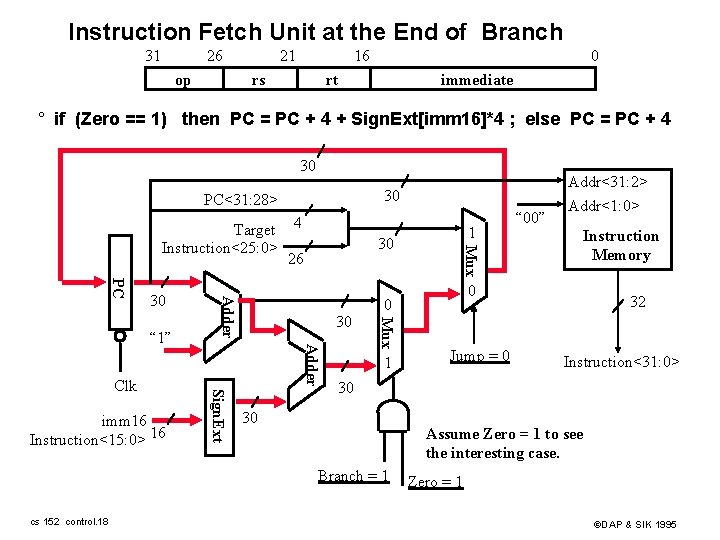

Instruction Fetch Unit at the End of Branch 31 26 op 21 16 rs 0 rt immediate ° if (Zero == 1) then PC = PC + 4 + Sign. Ext[imm 16]*4 ; else PC = PC + 4 30 30 PC<31: 28> 30 1 “ 00” Instruction Memory 0 Jump = 0 32 Instruction<31: 0> 30 30 Assume Zero = 1 to see the interesting case. Branch = 1 cs 152 control. 18 1 0 Mux imm 16 Instruction<15: 0> 16 Sign. Ext Clk 26 Adder “ 1” 30 Adder PC 30 4 Mux Target Instruction<25: 0> Addr<31: 2> Addr<1: 0> Zero = 1 ©DAP & SIK 1995

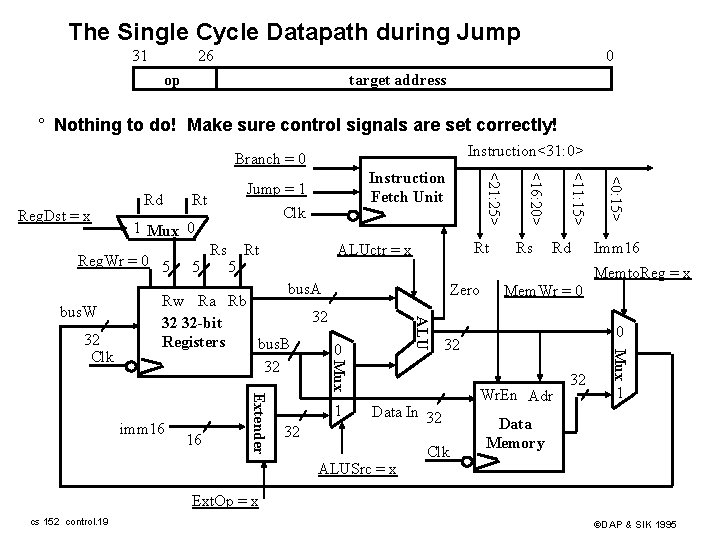

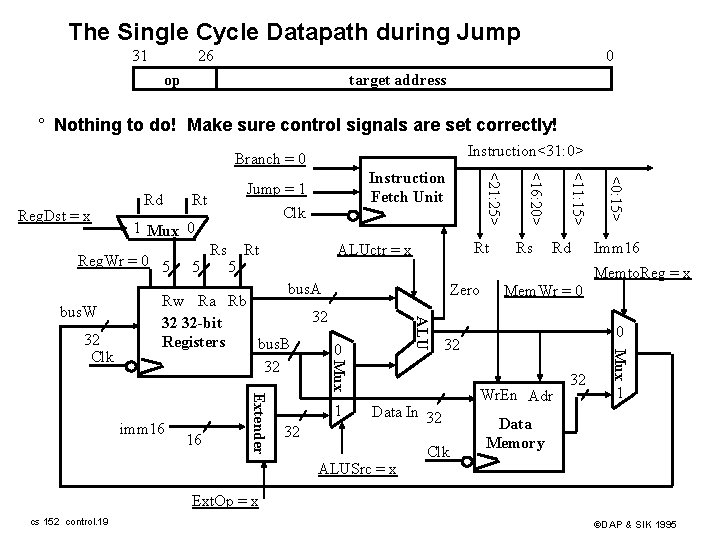

The Single Cycle Datapath during Jump 31 26 0 op target address ° Nothing to do! Make sure control signals are set correctly! Instruction<31: 0> Branch = 0 Zero 32 ALUSrc = x Memto. Reg = x Mem. Wr = 0 0 32 Data In 32 Clk Imm 16 Wr. En Adr 32 Mux ALU 16 Extender imm 16 1 Rd <0: 15> bus. A Rw Ra Rb 32 32 32 -bit Registers bus. B 0 32 Rs <11: 15> 5 Rt ALUctr = x Rt Mux 32 Clk 5 Rs <16: 20> 1 Mux 0 Reg. Wr = 0 5 bus. W Rt <21: 25> Reg. Dst = x Rd Instruction Fetch Unit Jump = 1 Clk 1 Data Memory Ext. Op = x cs 152 control. 19 ©DAP & SIK 1995

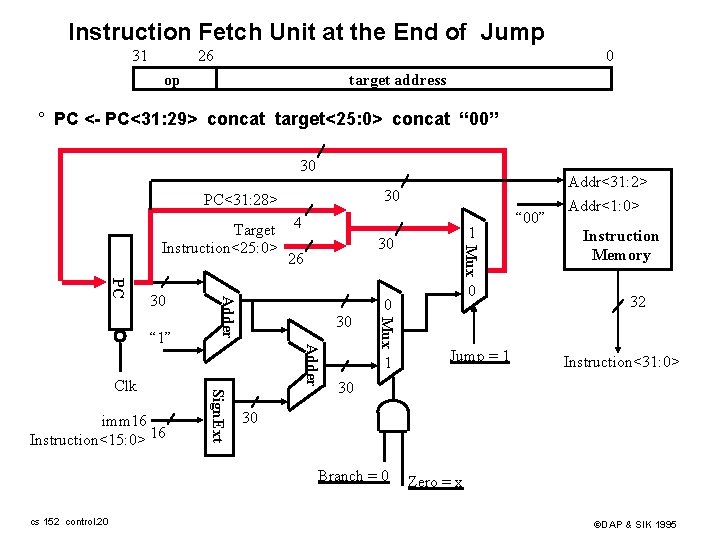

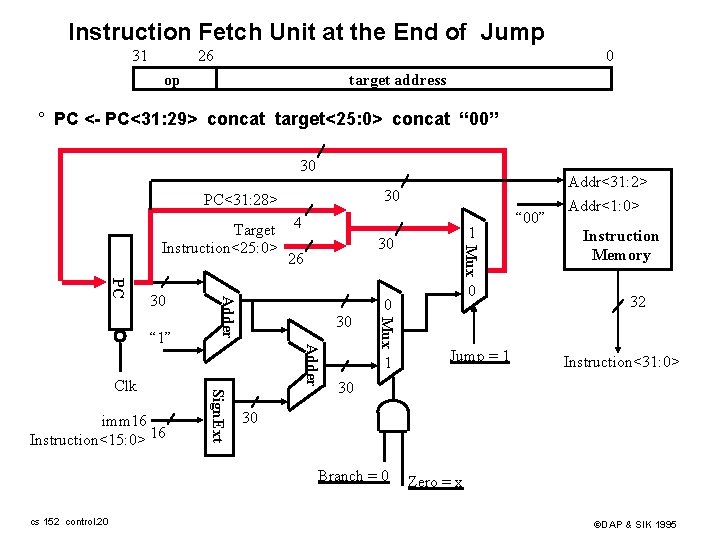

Instruction Fetch Unit at the End of Jump 31 26 0 op target address ° PC <- PC<31: 29> concat target<25: 0> concat “ 00” 30 30 PC<31: 28> 30 1 0 Jump = 1 “ 00” Instruction Memory 32 Instruction<31: 0> 30 30 Branch = 0 cs 152 control. 20 1 0 Mux imm 16 Instruction<15: 0> 16 Sign. Ext Clk 26 Adder “ 1” 30 Adder PC 30 4 Mux Target Instruction<25: 0> Addr<31: 2> Addr<1: 0> Zero = x ©DAP & SIK 1995

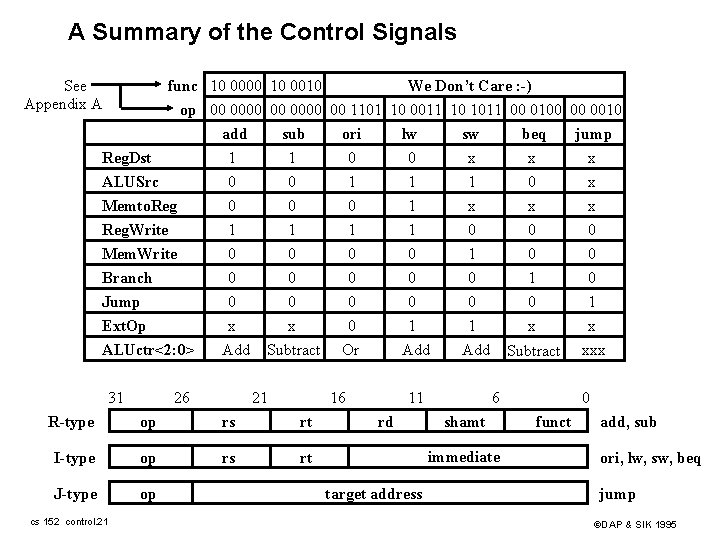

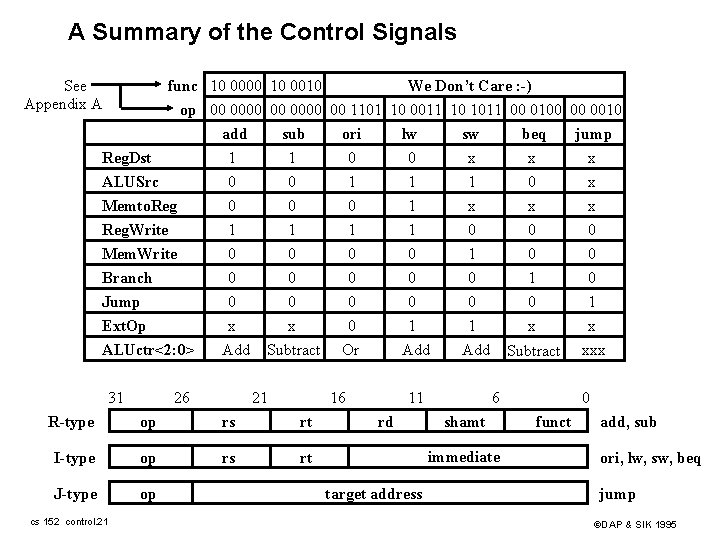

A Summary of the Control Signals See Appendix A func 10 0000 10 0010 We Don’t Care : -) op 00 0000 00 1101 10 0011 10 1011 00 0100 00 0010 add sub ori lw sw beq jump 1 Reg. Dst 1 0 0 x x x ALUSrc 0 0 1 1 1 0 x 0 0 0 1 x x x Memto. Reg. Write 1 1 0 0 0 Mem. Write 0 0 1 0 0 Branch 0 0 0 1 0 Jump 0 0 0 1 Ext. Op x x 0 1 1 x x ALUctr<2: 0> Add Subtract Or Add Subtract xxx 31 26 21 16 R-type op rs rt I-type op rs rt J-type op cs 152 control. 21 11 rd 6 shamt immediate target address 0 funct add, sub ori, lw, sw, beq jump ©DAP & SIK 1995

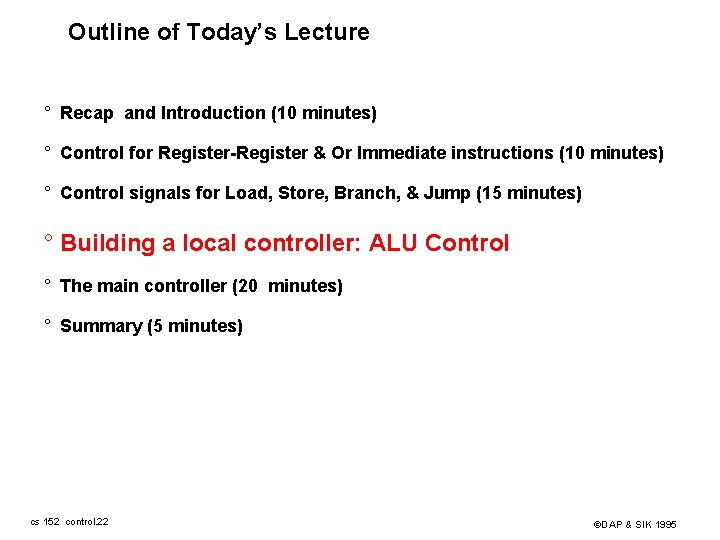

Outline of Today’s Lecture ° Recap and Introduction (10 minutes) ° Control for Register-Register & Or Immediate instructions (10 minutes) ° Control signals for Load, Store, Branch, & Jump (15 minutes) ° Building a local controller: ALU Control ° The main controller (20 minutes) ° Summary (5 minutes) cs 152 control. 22 ©DAP & SIK 1995

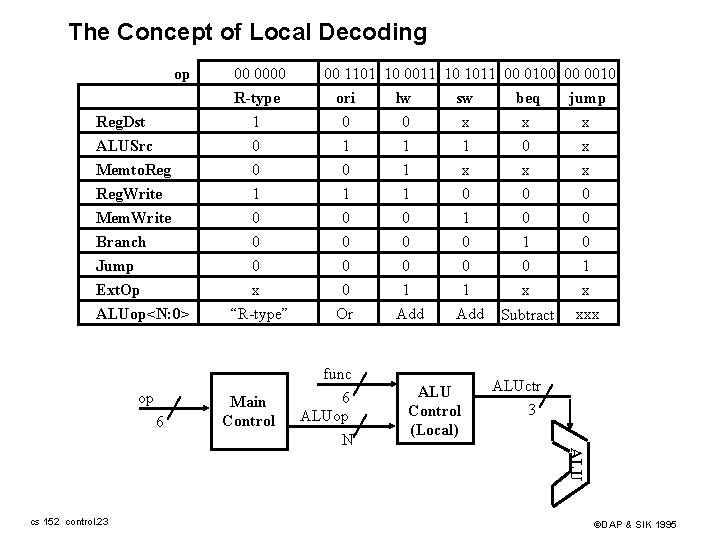

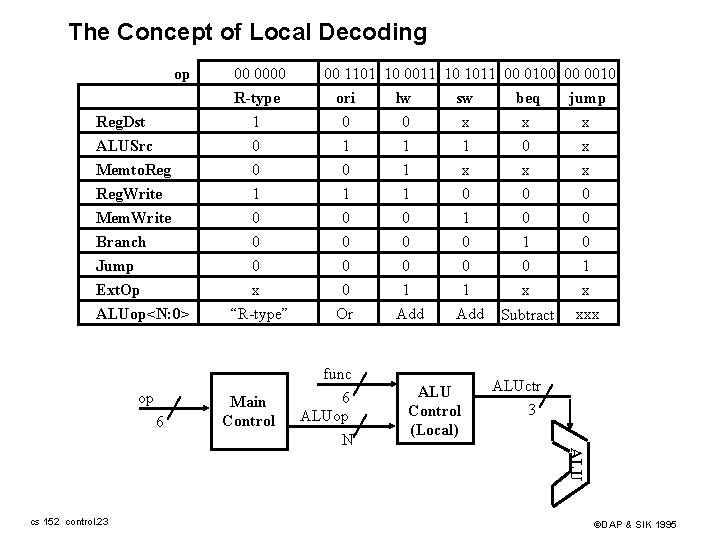

The Concept of Local Decoding op Reg. Dst ALUSrc Memto. Reg. Write Mem. Write Branch 00 0000 R-type 1 0 0 Jump Ext. Op ALUop<N: 0> 0 x “R-type” op 6 0 0 Or func 6 ALUop N 0 1 Add ALU Control (Local) 0 x Subtract 1 x xxx ALUctr 3 ALU cs 152 control. 23 Main Control 00 1101 10 0011 10 1011 00 0100 00 0010 ori lw sw beq jump 0 0 x x x 1 1 1 0 x 0 1 x x x 1 1 0 0 0 0 0 1 0 ©DAP & SIK 1995

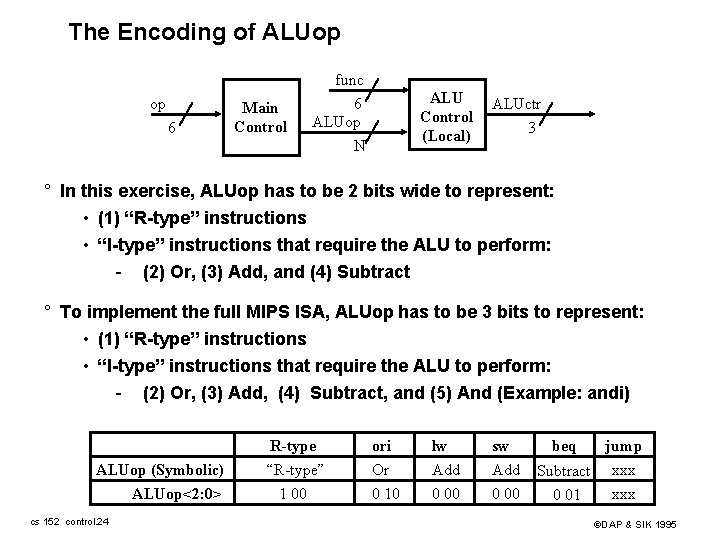

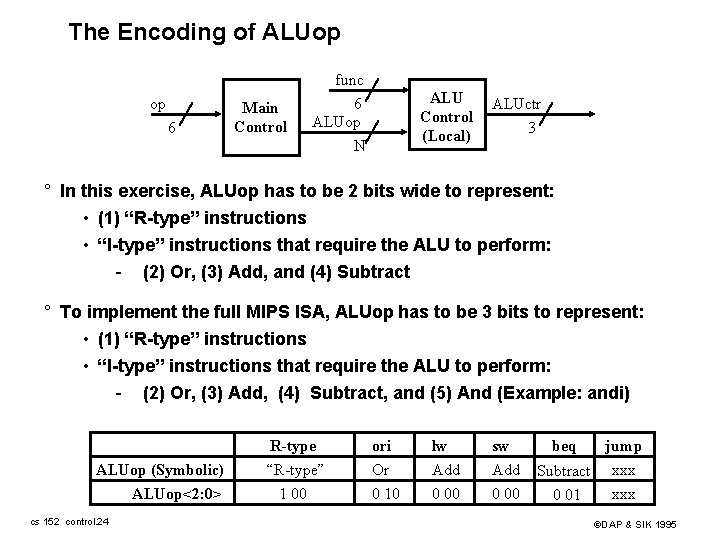

The Encoding of ALUop op 6 Main Control func 6 ALUop N ALU Control (Local) ALUctr 3 ° In this exercise, ALUop has to be 2 bits wide to represent: • (1) “R-type” instructions • “I-type” instructions that require the ALU to perform: - (2) Or, (3) Add, and (4) Subtract ° To implement the full MIPS ISA, ALUop has to be 3 bits to represent: • (1) “R-type” instructions • “I-type” instructions that require the ALU to perform: - (2) Or, (3) Add, (4) Subtract, and (5) And (Example: andi) ALUop (Symbolic) ALUop<2: 0> cs 152 control. 24 R-type “R-type” 1 00 ori Or 0 10 lw Add 0 00 sw Add 0 00 beq jump Subtract xxx 0 01 ©DAP & SIK 1995

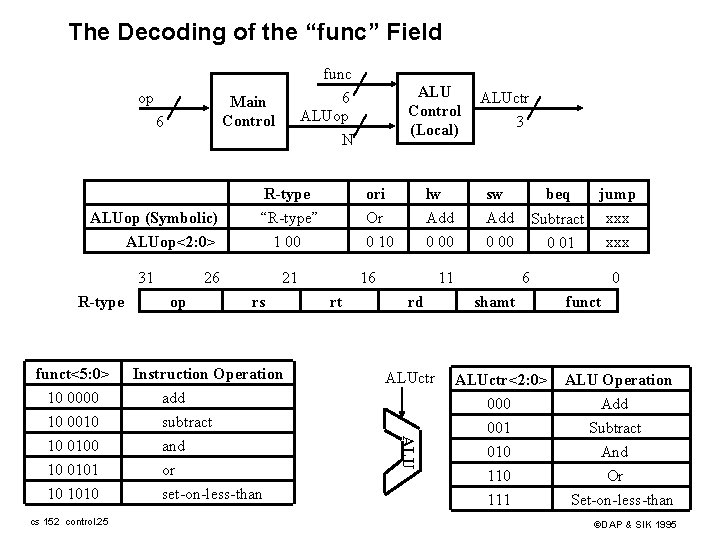

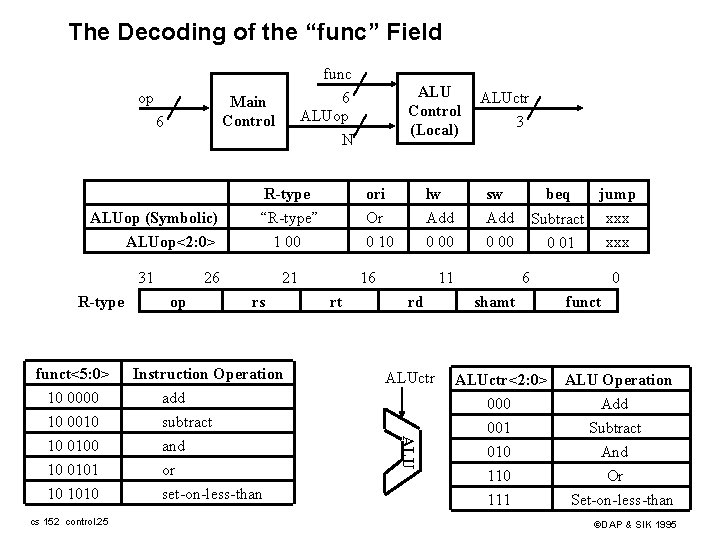

The Decoding of the “func” Field op func 6 ALUop Main Control 6 ALU Control (Local) N ALUop (Symbolic) ALUop<2: 0> 31 R-type funct<5: 0> 10 0000 10 0010 R-type “R-type” 1 00 26 op 21 rs Instruction Operation add subtract and or 10 1010 set-on-less-than lw Add 0 00 16 rt sw Add 0 00 11 rd ALUctr ALU 10 0100 10 0101 cs 152 control. 25 ori Or 0 10 ALUctr 3 beq jump Subtract xxx 0 01 6 shamt 0 funct ALUctr<2: 0> 000 ALU Operation Add 001 010 110 Subtract And Or 111 Set-on-less-than ©DAP & SIK 1995

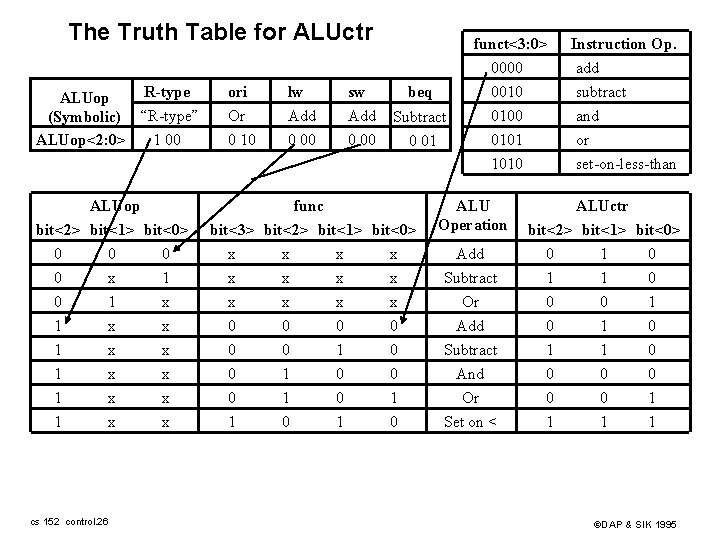

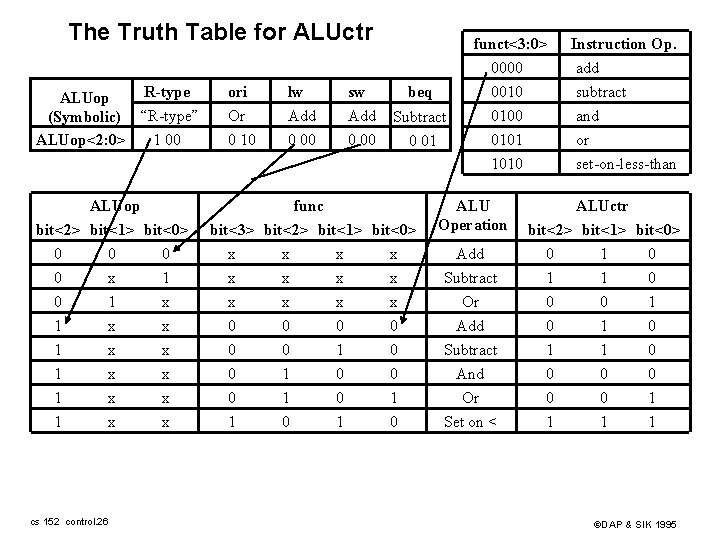

The Truth Table for ALUctr R-type ALUop (Symbolic) “R-type” ALUop<2: 0> 1 00 ALUop bit<2> bit<1> bit<0> 0 0 x 1 0 1 x x 1 x x cs 152 control. 26 ori Or lw Add sw Add beq Subtract 0 10 0 00 0 01 func bit<3> bit<2> bit<1> bit<0> x x x 0 0 0 1 1 0 funct<3: 0> 0000 0010 0101 1010 ALU Operation Add Subtract Or Add Subtract And Or Set on < Instruction Op. add subtract and or set-on-less-than ALUctr bit<2> bit<1> bit<0> 0 1 1 0 0 0 1 1 ©DAP & SIK 1995

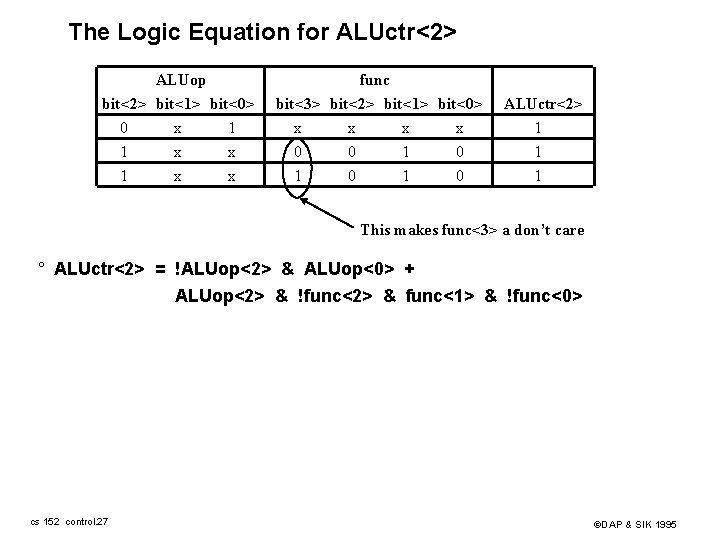

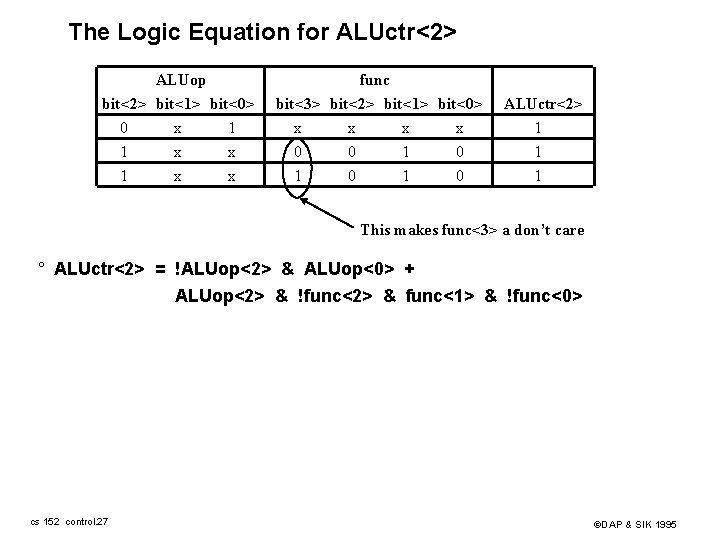

The Logic Equation for ALUctr<2> ALUop bit<2> bit<1> bit<0> 0 x 1 1 x x func bit<3> bit<2> bit<1> bit<0> x x 0 0 1 0 1 0 ALUctr<2> 1 1 1 This makes func<3> a don’t care ° ALUctr<2> = !ALUop<2> & ALUop<0> + ALUop<2> & !func<2> & func<1> & !func<0> cs 152 control. 27 ©DAP & SIK 1995

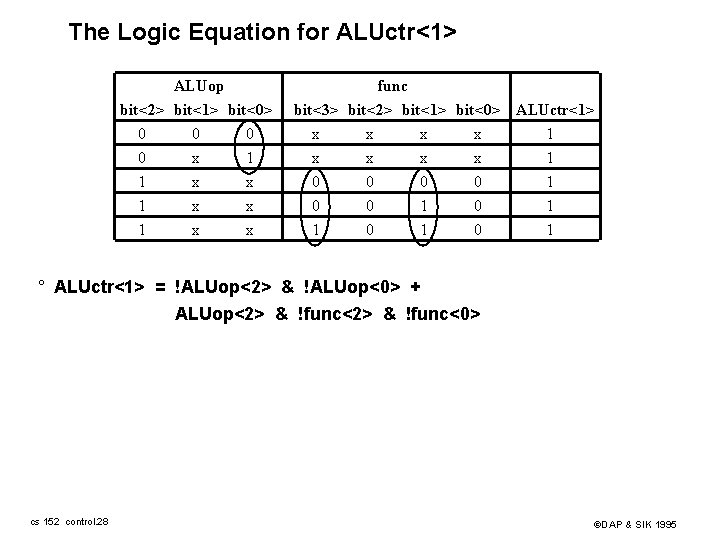

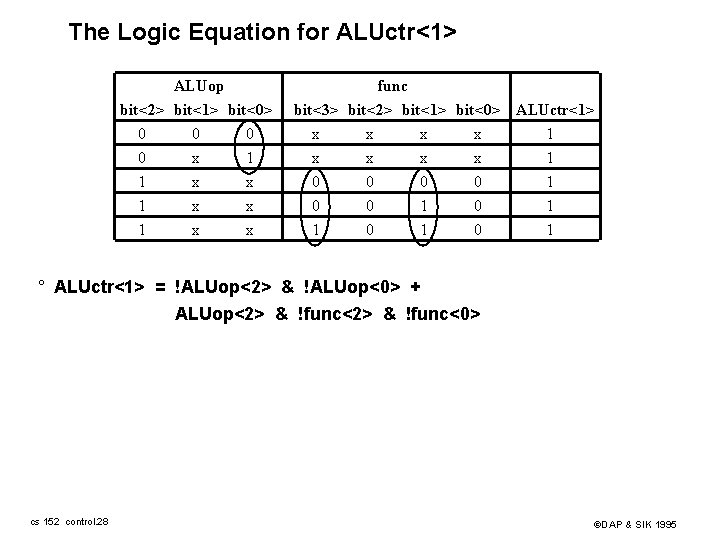

The Logic Equation for ALUctr<1> ALUop bit<2> bit<1> bit<0> 0 0 x 1 1 x x func bit<3> bit<2> bit<1> bit<0> ALUctr<1> x x x x 1 0 0 1 1 0 1 ° ALUctr<1> = !ALUop<2> & !ALUop<0> + ALUop<2> & !func<0> cs 152 control. 28 ©DAP & SIK 1995

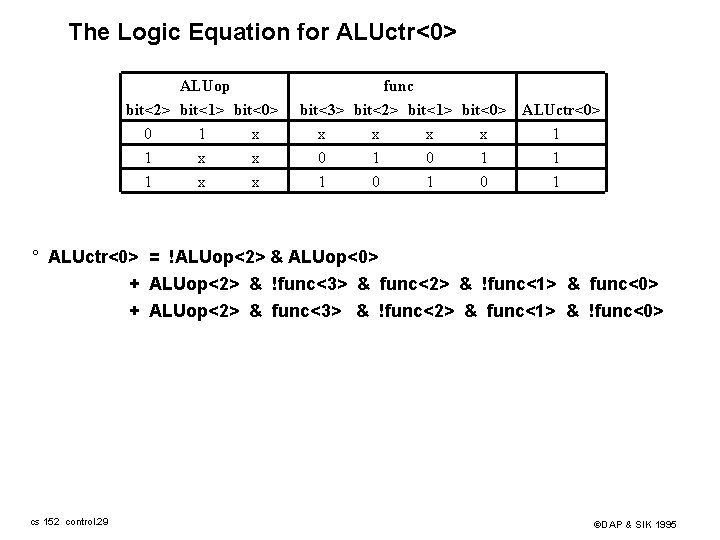

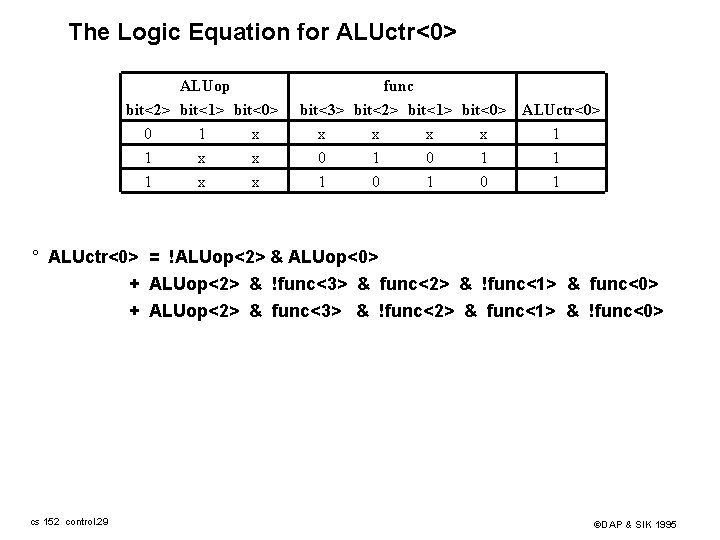

The Logic Equation for ALUctr<0> ALUop bit<2> bit<1> bit<0> 0 1 x x func bit<3> bit<2> bit<1> bit<0> ALUctr<0> x x 1 0 1 1 1 0 1 ° ALUctr<0> = !ALUop<2> & ALUop<0> + ALUop<2> & !func<3> & func<2> & !func<1> & func<0> + ALUop<2> & func<3> & !func<2> & func<1> & !func<0> cs 152 control. 29 ©DAP & SIK 1995

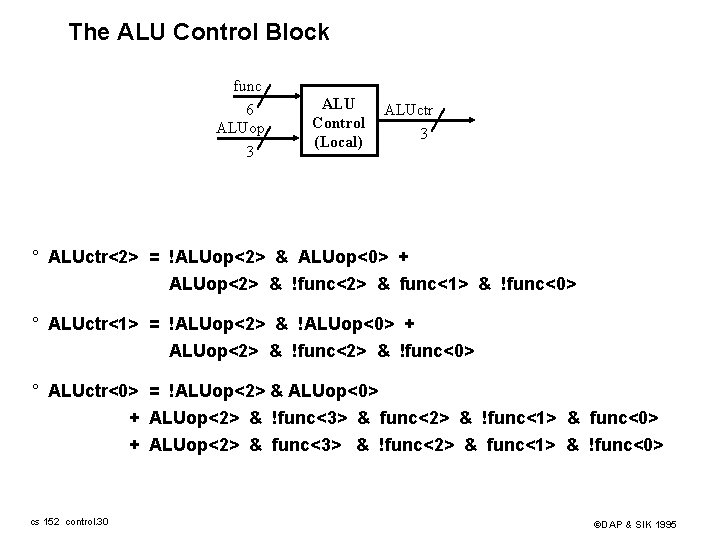

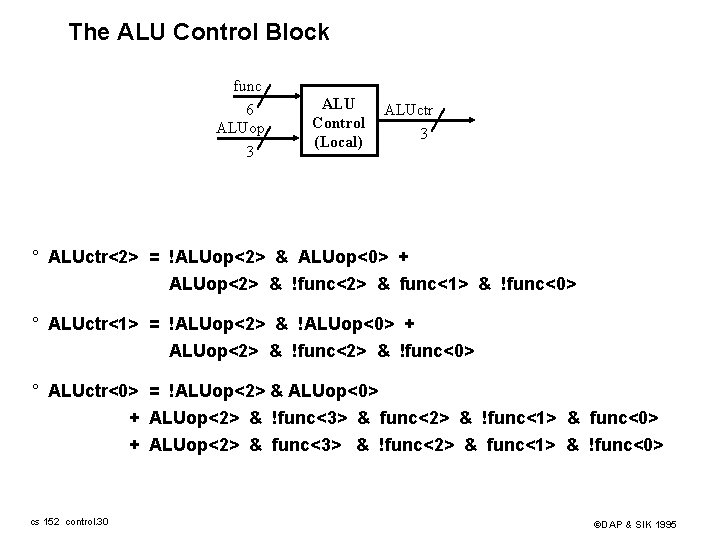

The ALU Control Block func 6 ALUop 3 ALU Control (Local) ALUctr 3 ° ALUctr<2> = !ALUop<2> & ALUop<0> + ALUop<2> & !func<2> & func<1> & !func<0> ° ALUctr<1> = !ALUop<2> & !ALUop<0> + ALUop<2> & !func<0> ° ALUctr<0> = !ALUop<2> & ALUop<0> + ALUop<2> & !func<3> & func<2> & !func<1> & func<0> + ALUop<2> & func<3> & !func<2> & func<1> & !func<0> cs 152 control. 30 ©DAP & SIK 1995

Outline of Today’s Lecture ° Recap and Introduction (10 minutes) ° Control for Register-Register & Or Immediate instructions (10 minutes) ° Control signals for Load, Store, Branch, & Jump (15 minutes) ° Building a local controller: ALU Control (10 minutes) ° The main controller ° Summary (5 minutes) cs 152 control. 31 ©DAP & SIK 1995

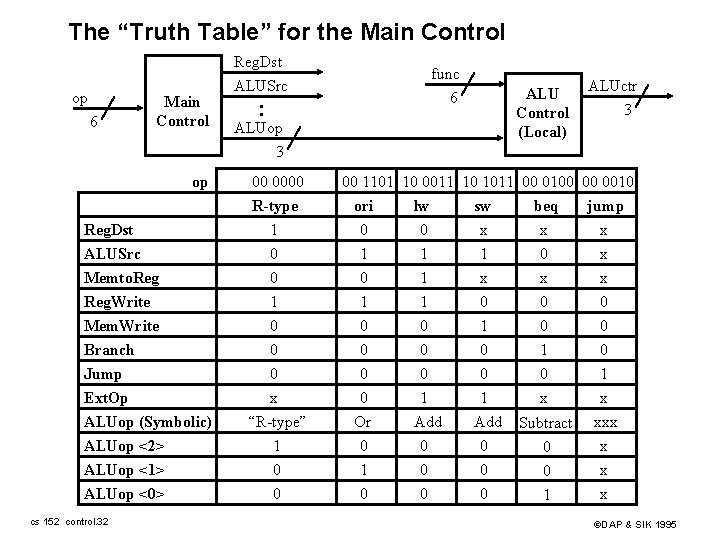

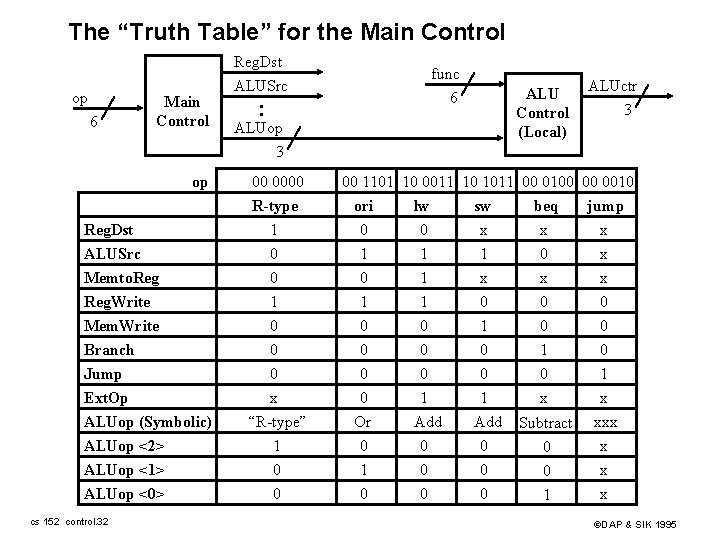

The “Truth Table” for the Main Control op 6 Main Control Reg. Dst ALUSrc : ALUop func 6 ALU Control (Local) ALUctr 3 3 op Reg. Dst ALUSrc Memto. Reg. Write Mem. Write Branch Jump Ext. Op ALUop (Symbolic) ALUop <2> ALUop <1> ALUop <0> cs 152 control. 32 00 0000 R-type 1 0 0 0 x “R-type” 1 0 0 00 1101 10 0011 10 1011 00 0100 00 0010 ori lw sw beq jump 0 0 x x x 1 1 1 0 x 0 1 x x x 1 1 0 0 0 0 0 1 1 x x Or Add Subtract xxx 0 0 0 x 0 1 0 0 x 1 ©DAP & SIK 1995

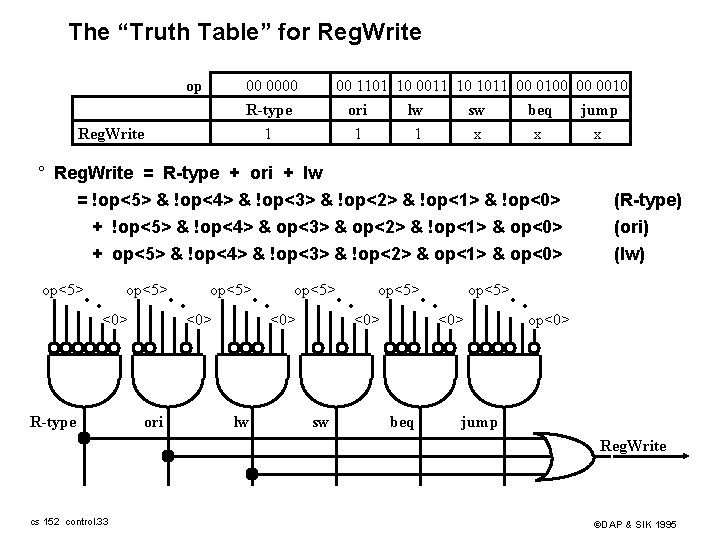

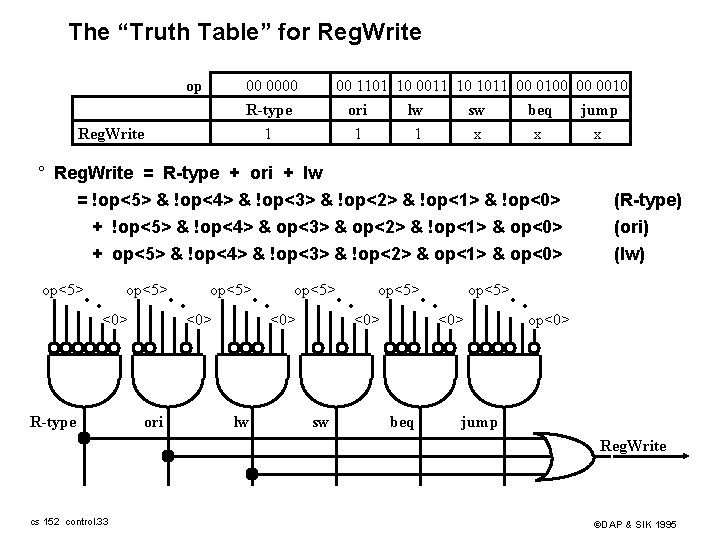

The “Truth Table” for Reg. Write op 00 0000 R-type 1 Reg. Write 00 1101 10 0011 10 1011 00 0100 00 0010 ori lw sw beq jump 1 1 x x x ° Reg. Write = R-type + ori + lw = !op<5> & !op<4> & !op<3> & !op<2> & !op<1> & !op<0> + !op<5> & !op<4> & op<3> & op<2> & !op<1> & op<0> + op<5> & !op<4> & !op<3> & !op<2> & op<1> & op<0> . . op<5> <0> R-type . . op<5> <0> ori . . op<5> <0> lw . . op<5> <0> sw . . op<5> <0> beq (R-type) (ori) (lw) op<0> jump Reg. Write cs 152 control. 33 ©DAP & SIK 1995

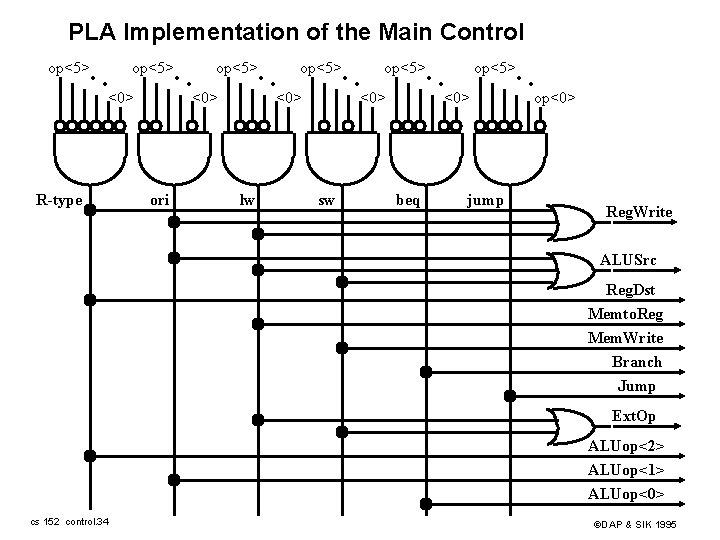

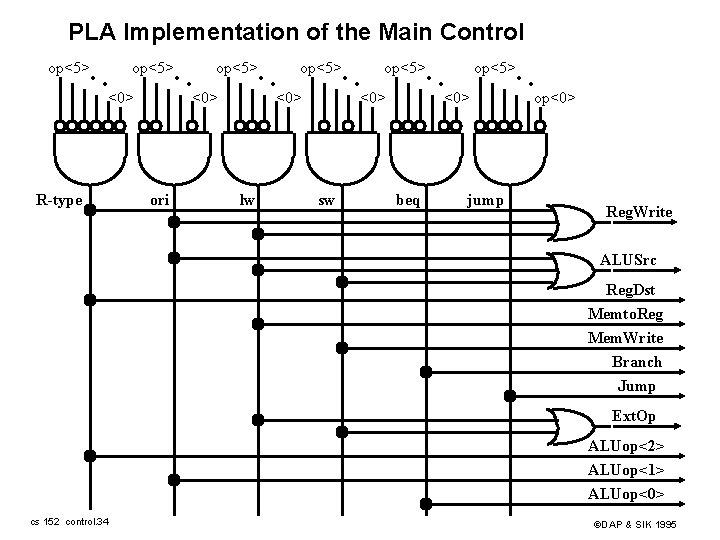

PLA Implementation of the Main Control . . op<5> <0> R-type . . op<5> <0> ori . . op<5> <0> lw . . op<5> <0> sw <0> beq . . op<5> jump op<0> Reg. Write ALUSrc Reg. Dst Memto. Reg Mem. Write Branch Jump Ext. Op ALUop<2> ALUop<1> ALUop<0> cs 152 control. 34 ©DAP & SIK 1995

Outline of Today’s Lecture ° Recap and Introduction (10 minutes) ° Control for Register-Register & Or Immediate instructions (10 minutes) ° Control signals for Load, Store, Branch, & Jump (15 minutes) ° Building a local controller: ALU Control (10 minutes) ° The main controller (20 minutes) ° Summary cs 152 control. 35 ©DAP & SIK 1995

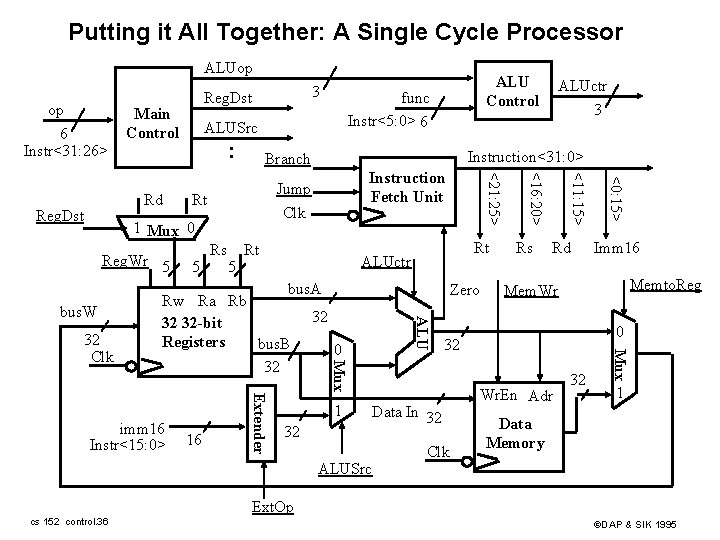

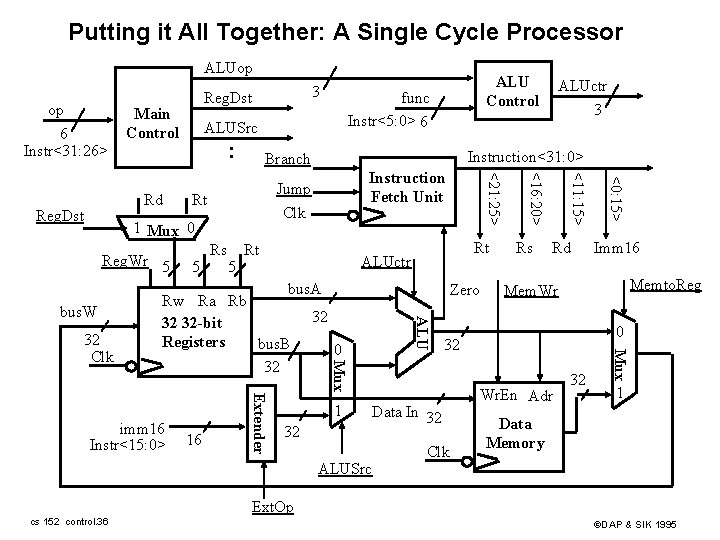

Putting it All Together: A Single Cycle Processor ALUop op 6 Instr<31: 26> Rt ALUctr bus. A 0 1 32 cs 152 control. 36 Clk Imm 16 Memto. Reg Mem. Wr 0 32 Data In 32 ALUSrc Rd Wr. En Adr 32 Mux 16 Extender imm 16 Instr<15: 0> 32 Mux 32 Clk Rw Ra Rb 32 32 -bit Registers bus. B 32 ALU bus. W Zero Rs <0: 15> 5 Rt <11: 15> Rs <16: 20> 5 Instruction Fetch Unit Jump Clk Rt ALUctr 3 Instruction<31: 0> Branch 1 Mux 0 Reg. Wr 5 func Instr<5: 0> 6 ALUSrc : ALU Control <21: 25> Reg. Dst Main Control Rd 3 1 Data Memory Ext. Op ©DAP & SIK 1995

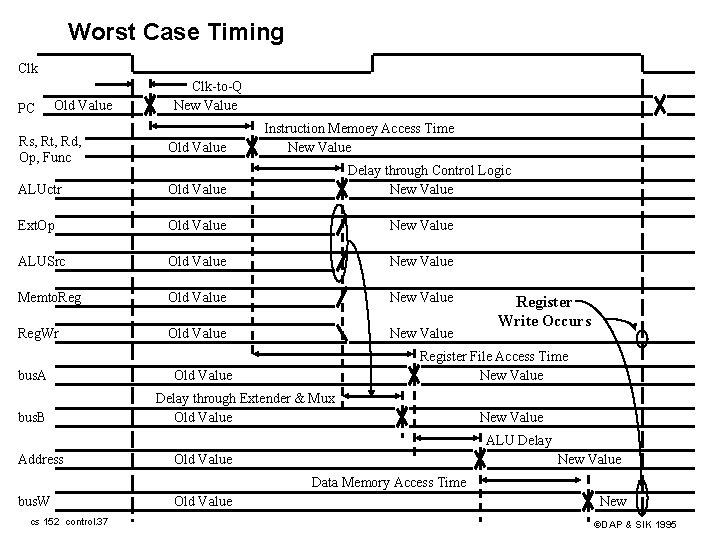

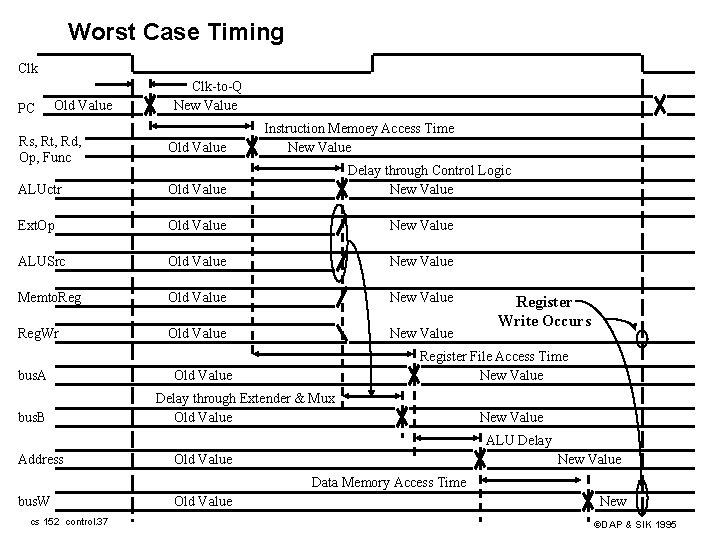

Worst Case Timing Clk PC Old Value Clk-to-Q New Value Instruction Memoey Access Time New Value Rs, Rt, Rd, Op, Func Old Value ALUctr Old Value Ext. Op Old Value New Value ALUSrc Old Value New Value Memto. Reg Old Value New Value Reg. Wr Old Value New Value bus. A bus. B Delay through Control Logic New Value Register Write Occurs Register File Access Time New Value Old Value Delay through Extender & Mux Old Value New Value ALU Delay Address Old Value New Value Data Memory Access Time bus. W cs 152 control. 37 Old Value New ©DAP & SIK 1995

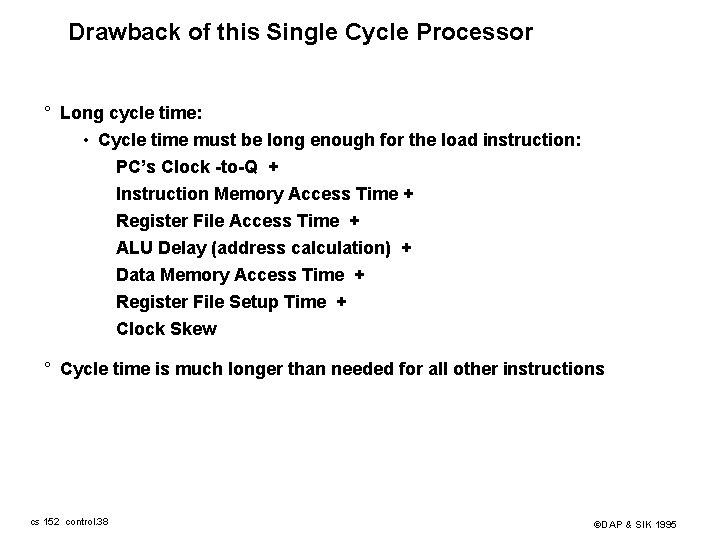

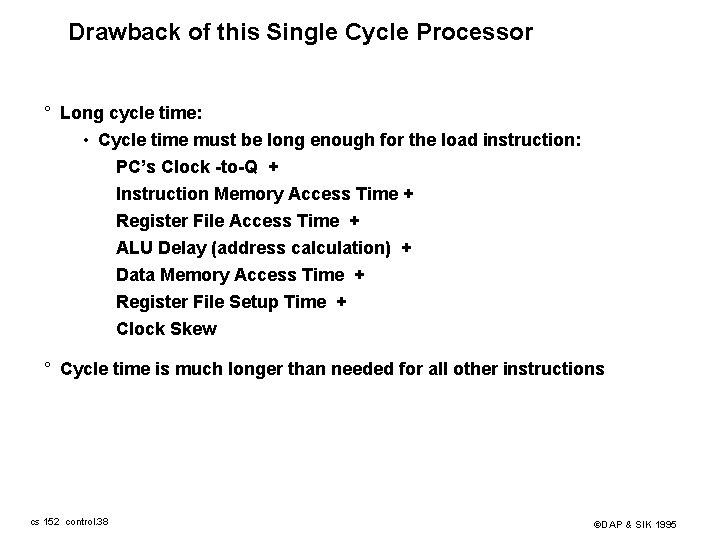

Drawback of this Single Cycle Processor ° Long cycle time: • Cycle time must be long enough for the load instruction: PC’s Clock -to-Q + Instruction Memory Access Time + Register File Access Time + ALU Delay (address calculation) + Data Memory Access Time + Register File Setup Time + Clock Skew ° Cycle time is much longer than needed for all other instructions cs 152 control. 38 ©DAP & SIK 1995