CIS 212 Microcomputer Architecture Day 8 Rhys Eric

- Slides: 29

CIS 212 Microcomputer Architecture Day 8 Rhys Eric Rosholt Office: Office Phone: Web Site: Email Address: Gillet Hall - Room 304 718 -960 -8663 http: //comet. lehman. cuny. edu/rosholt/ rhys. rosholt @ lehman. cuny. edu

Chapter 4 Processor Technology and Architecture

Chapter 4 Processor Technology and Architecture Chapter Outline CPU Operation Instructions and Instruction Sets Instruction Format Clock Rate CPU Registers Word Size Enhancing Processor Performance The Physical CPU Future Trends

Chapter Goals • Describe CPU instruction and execution cycles • Explain how primitive CPS instructions are combined to form complex processing operations • Describe key CPU design features, including instruction format, word size, and clock rate • Describe the function of general-purpose and special-purpose registers • Compare and contrast CISC and RISC CPUs • Describe the principles and limitations of semiconductor-based microprocessors

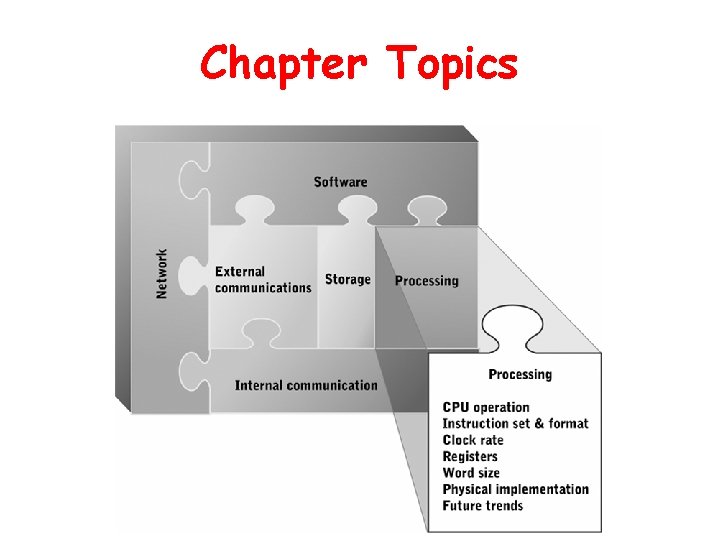

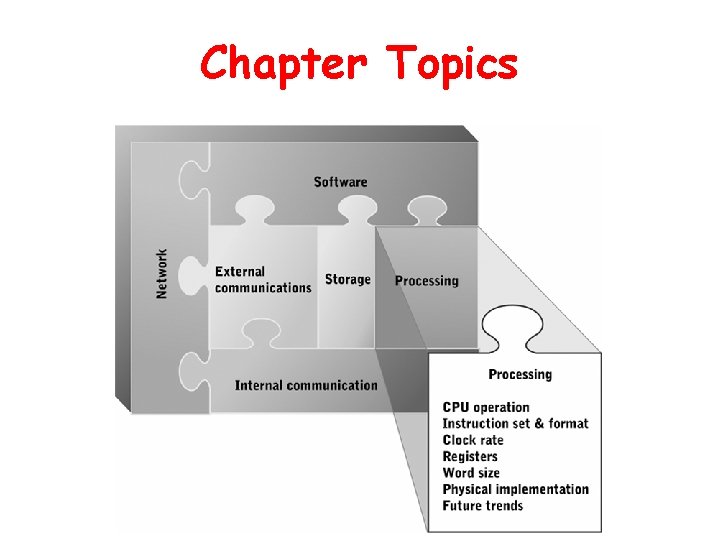

Chapter Topics

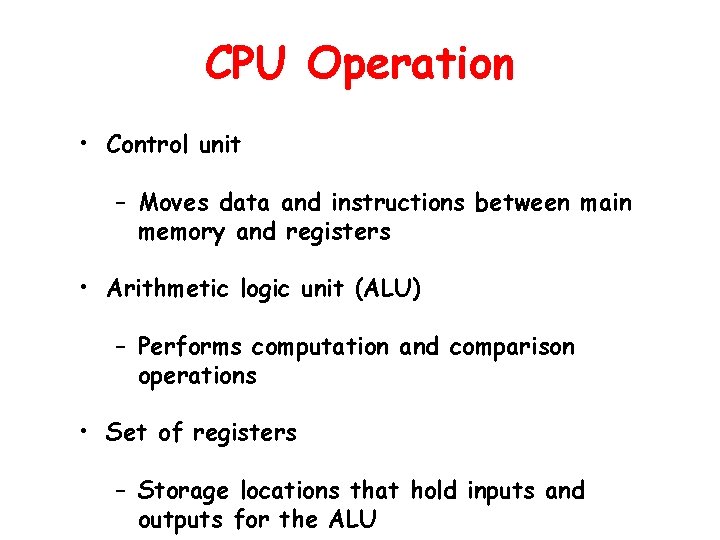

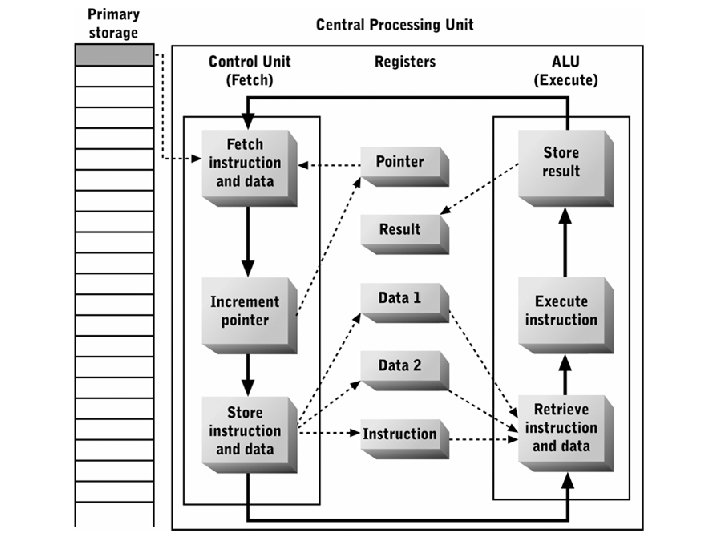

CPU Operation • Control unit – Moves data and instructions between main memory and registers • Arithmetic logic unit (ALU) – Performs computation and comparison operations • Set of registers – Storage locations that hold inputs and outputs for the ALU

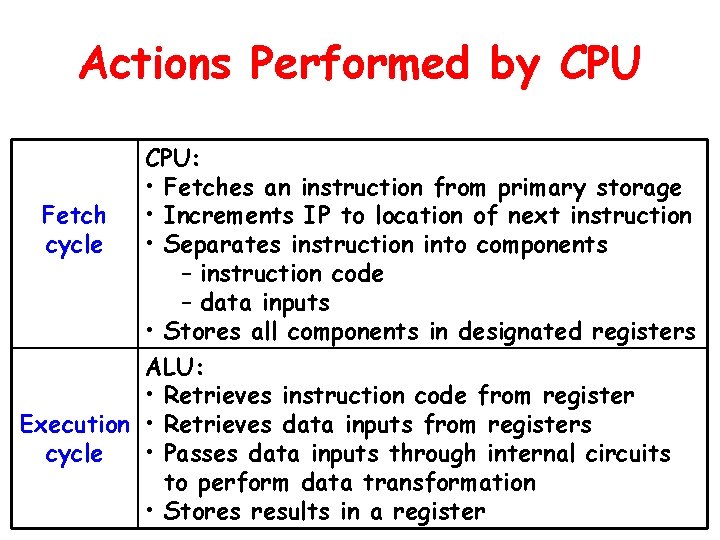

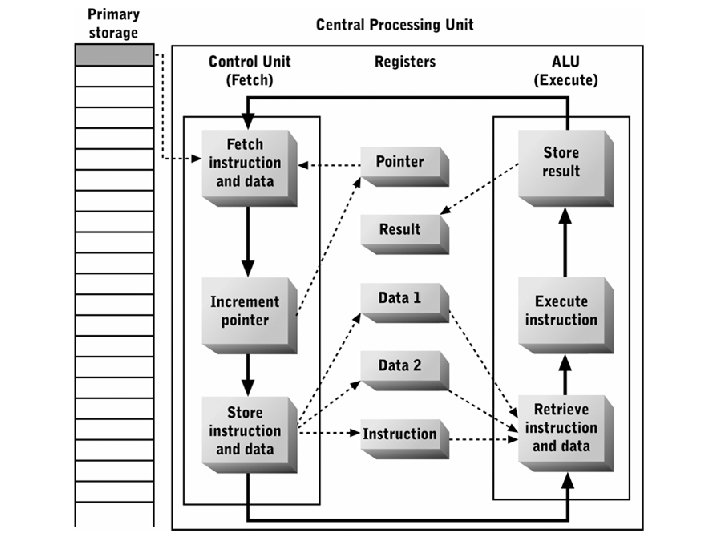

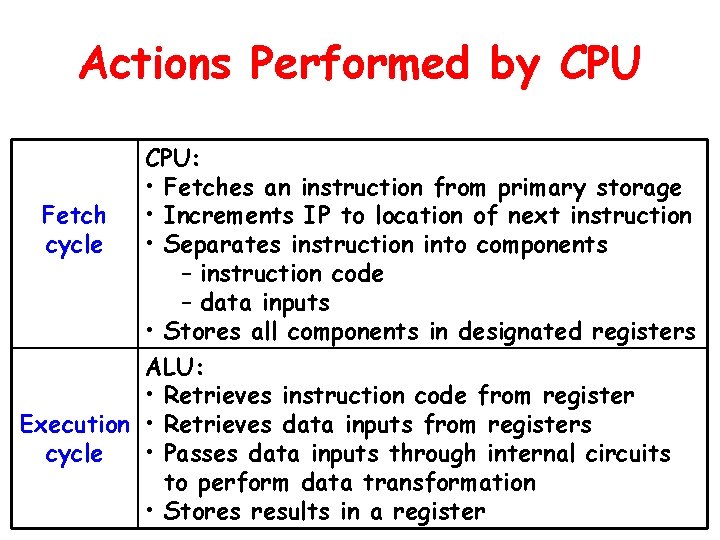

Actions Performed by CPU Fetch cycle CPU: • Fetches an instruction from primary storage • Increments IP to location of next instruction • Separates instruction into components – instruction code – data inputs • Stores all components in designated registers ALU: • Retrieves instruction code from register Execution • Retrieves data inputs from registers cycle • Passes data inputs through internal circuits to perform data transformation • Stores results in a register

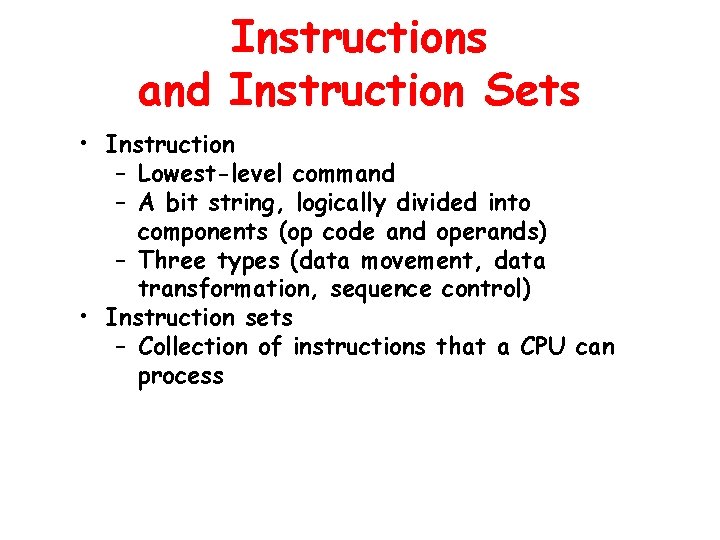

Instructions and Instruction Sets • Instruction – Lowest-level command – A bit string, logically divided into components (op code and operands) – Three types (data movement, data transformation, sequence control) • Instruction sets – Collection of instructions that a CPU can process

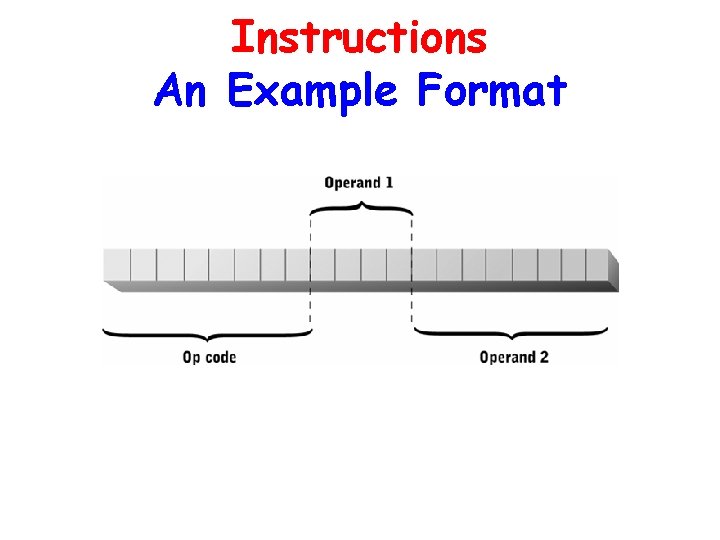

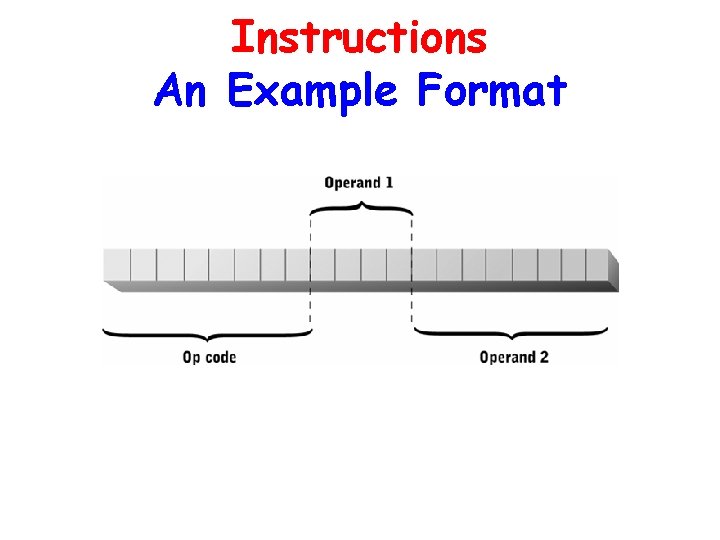

Instructions An Example Format

Data Movement Instructions • Copy data (MOVE) among registers, primary storage, secondary storage, and I/O devices

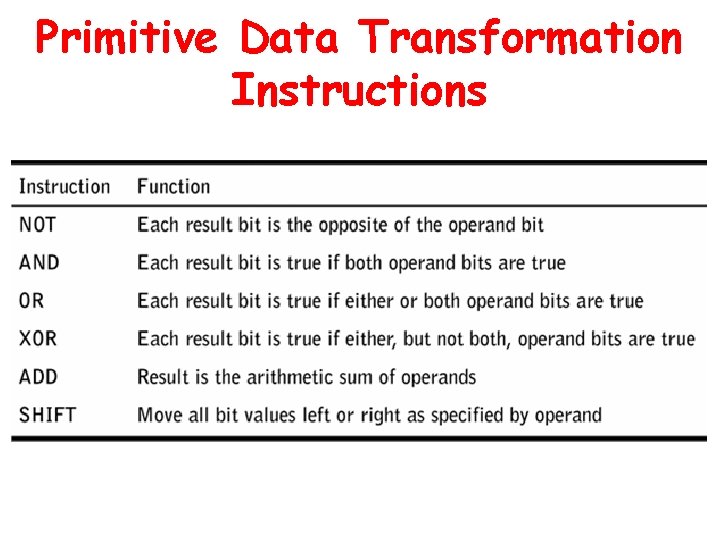

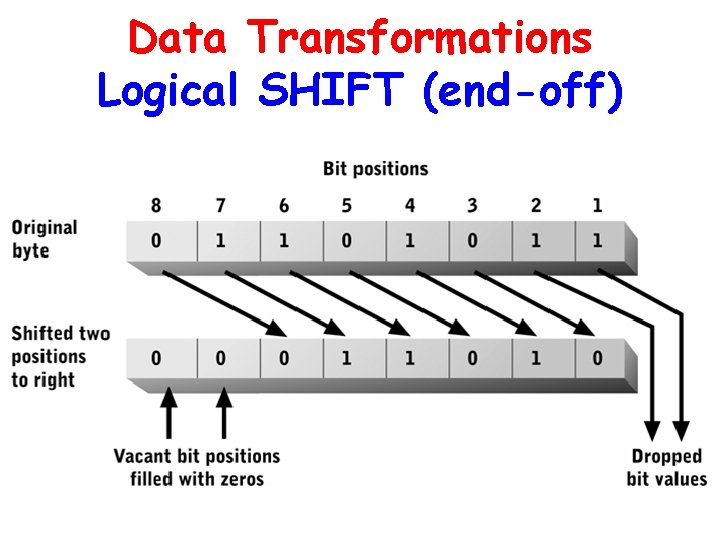

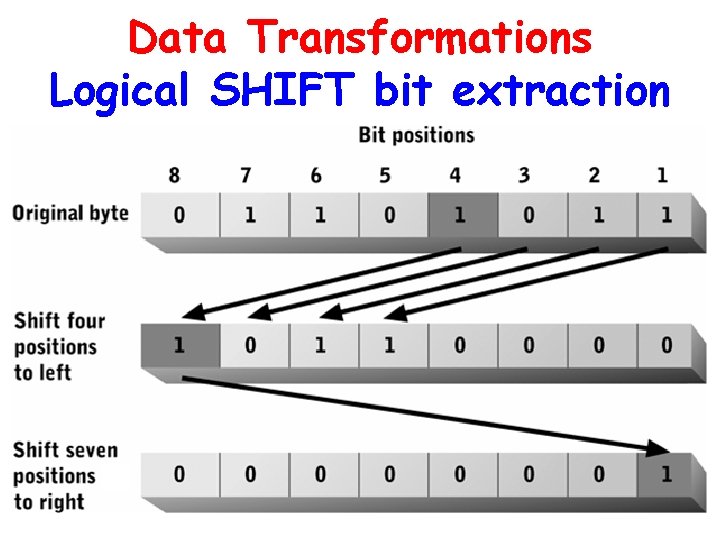

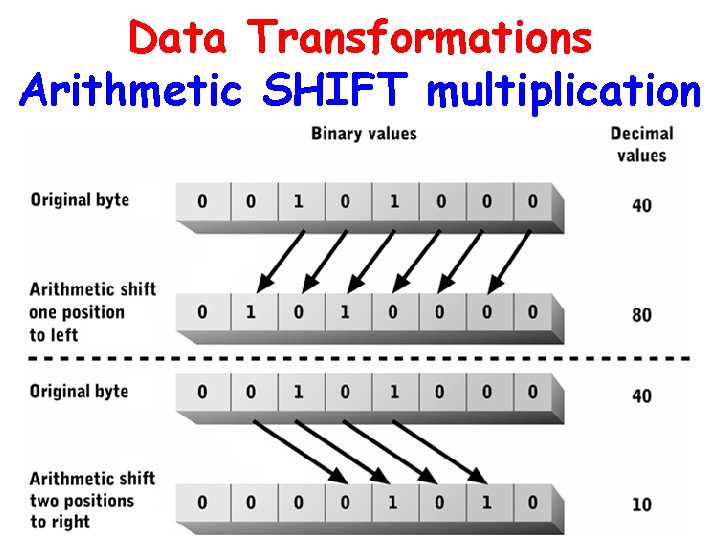

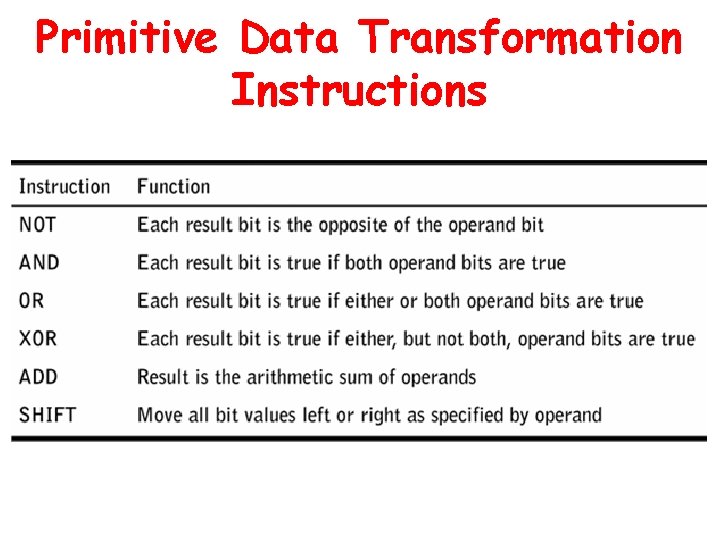

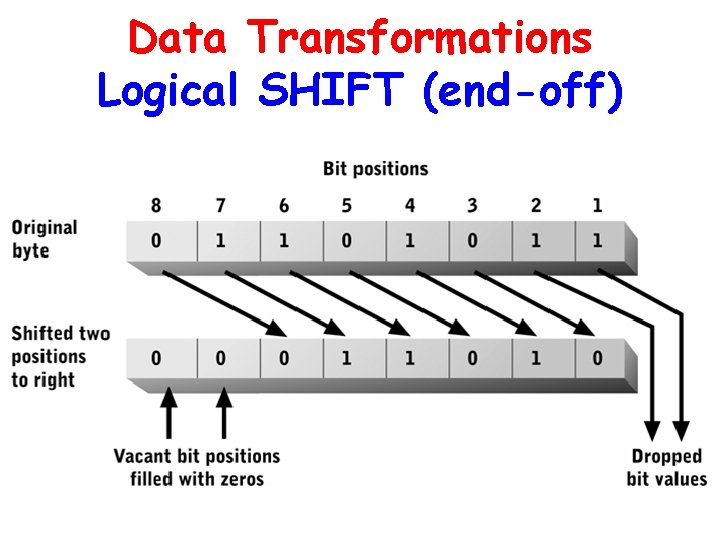

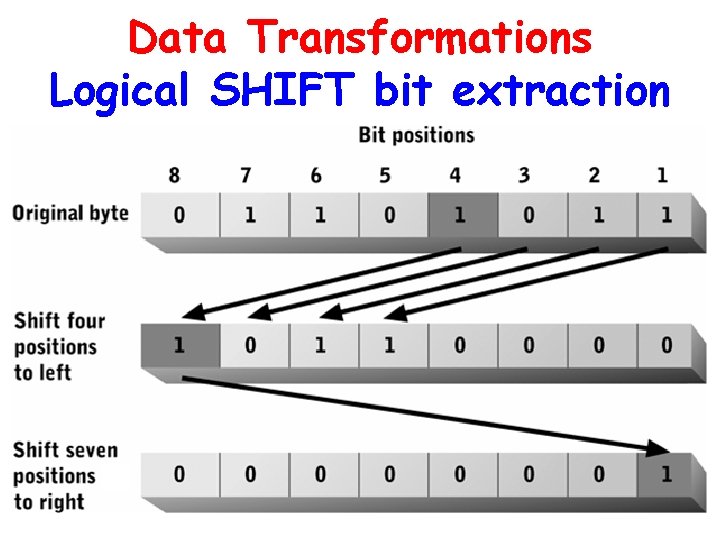

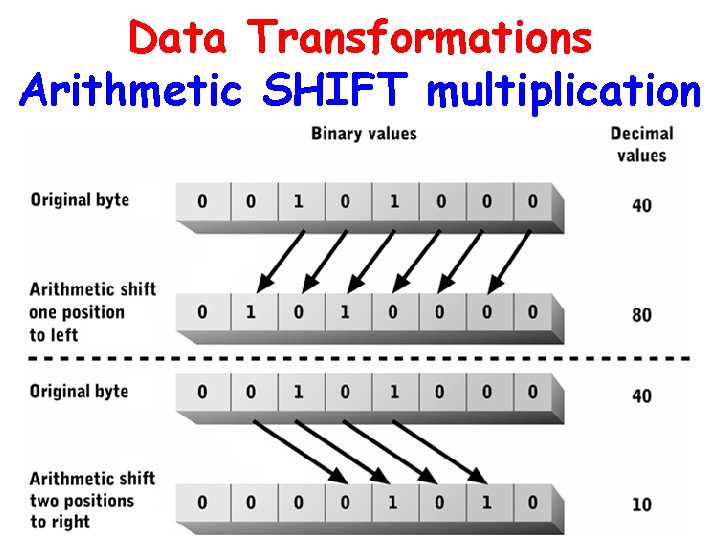

Data Transformations • Implement simple Boolean operations (NOT, AND, OR, and XOR) • Implement addition (ADD) • Implement bit manipulation (SHIFT) – Logical shift – Arithmetic shift

Primitive Data Transformation Instructions

Data Transformations Logical SHIFT (end-off)

Data Transformations Logical SHIFT bit extraction

Data Transformations Arithmetic SHIFT multiplication

Sequence Control Operations • Control the next instruction to be fetched or executed • Operations – Unconditional branch – Conditional branch – Halt

Complex Processing Operations • Implemented by appropriate sequences of primitive instructions • Represent combinations of primitive processing operations • Represent a tradeoff between CPU complexity and – Programming simplicity – Program execution speed

Instruction Set Extensions • Additional instructions required when new data types are added • Some include instructions that combine data transformation with data movement

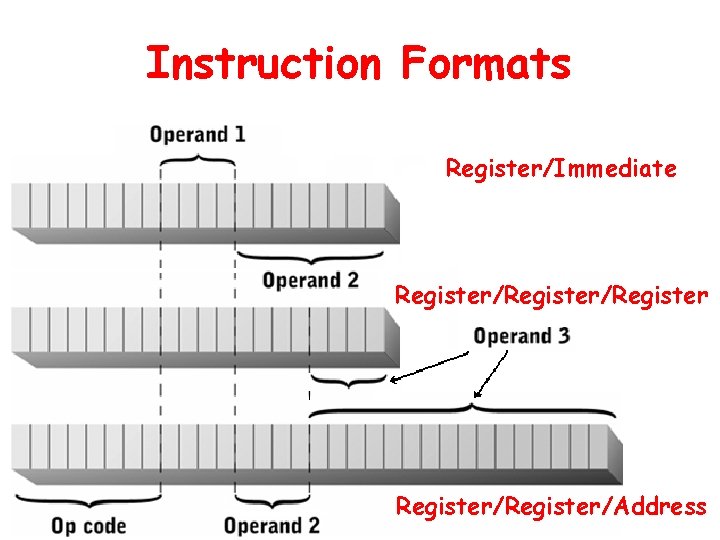

Instruction Format • Template describing op code position and length, and position, type, and length of each operand • Vary among CPUs (op code size, meaning of specific op code values, data types used as operands, length and coding format of each type of operand) • Most CPUs support multiple instructional formats

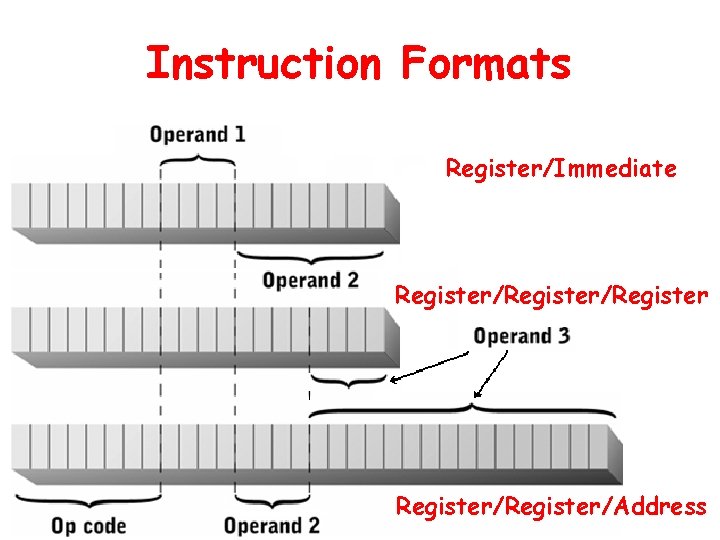

Instruction Formats Register/Immediate Register/Register/Address

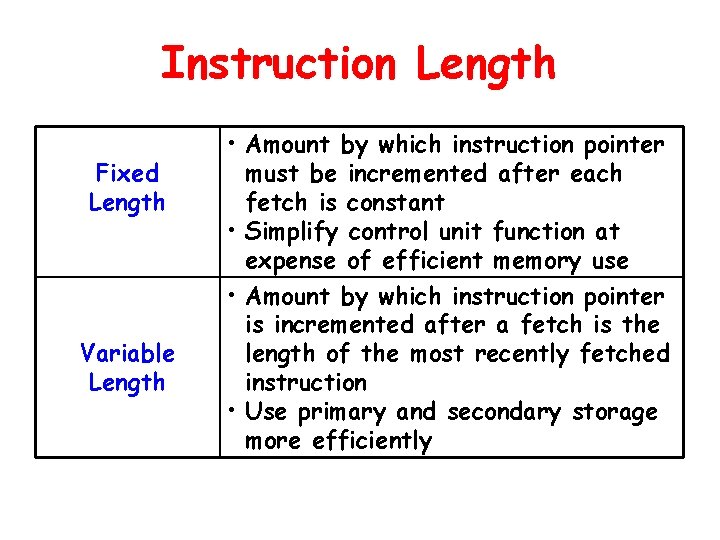

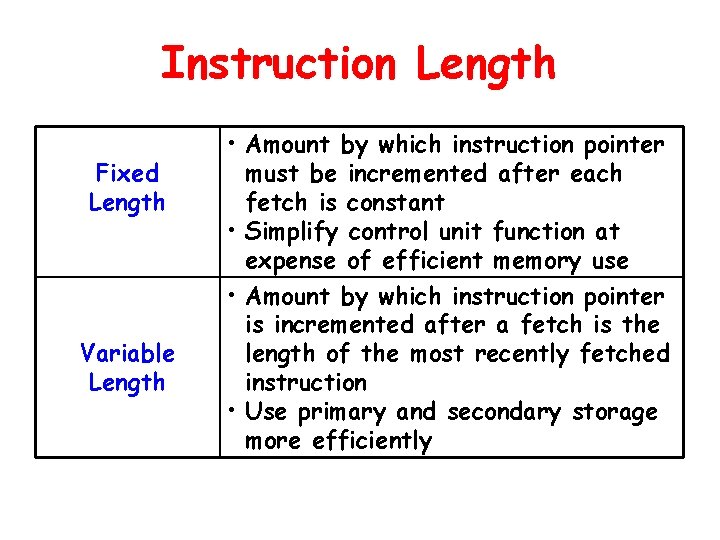

Instruction Length Fixed Length Variable Length • Amount by which instruction pointer must be incremented after each fetch is constant • Simplify control unit function at expense of efficient memory use • Amount by which instruction pointer is incremented after a fetch is the length of the most recently fetched instruction • Use primary and secondary storage more efficiently

Reduced Instruction Set Computing (RISC) • Uses fixed length instructions, short instruction length, large number of generalpurpose registers • Generally avoids complex instructions, especially those that combine data movement and data transformation • Simpler but less efficient than CISC (Complex Instruction Set Computing)

Clock Rate • Number of instructions and execution cycles potentially available in a fixed time interval • Typically measured in thousands of MHz (1000 MHz = 1 GHz) • Rate of actual or average instruction execution is measured in MIPS or MFLOPS • CPU cycle time – inverse of clock rate • Wait state

CPU Registers • Primary roles – Hold data for currently executing program that is needed quickly or frequently (general-purpose registers) – Store information about currently executing program and about status of CPU (special-purpose registers)

General-Purpose Registers • Hold intermediate results and frequently needed data items • Used only by currently executing program • Implemented within the CPU; contents can be read or written quickly • Increasing their number usually decreases program execution time to a point

Special-Purpose Registers • Track processor and program status • Types – Instruction register – Instruction pointer – Program status word (PSW) • Stores results of comparison operation • Controls conditional branch execution • Indicates actual or potential error conditions

Word Size • Number of bits a CPU can process simultaneously • Increasing it usually increases CPU efficiency, up to a point • Other computer components should match or exceed it for optimal performance • Implications for system bus design and physical implementation of memory

Next Class Thursday March 1, 2012 Rhys Eric Rosholt Office: Office Phone: Web Site: Email Address: Gillet Hall - Room 304 718 -960 -8663 http: //comet. lehman. cuny. edu/rosholt/ rhys. rosholt @ lehman. cuny. edu