Chapter 7 Memory Management Operating System Concepts 8

- Slides: 48

Chapter 7: Memory Management Operating System Concepts – 8 th Edition Silberschatz, Galvin and Gagne © 2009

Chapter 7: Memory Management n Background n Swapping n Contiguous Memory Allocation n Paging n Segmentation Operating System Concepts – 8 th Edition 8. 2 Silberschatz, Galvin and Gagne © 2009

Objectives n To provide a detailed description of various ways of organizing memory hardware n To discuss various memory-management techniques, including paging and segmentation Operating System Concepts – 8 th Edition 8. 3 Silberschatz, Galvin and Gagne © 2009

Background n Program must be brought (from disk) into memory and placed within a process for it to be run n Main memory and registers are only storage CPU can access directly n Register access in one CPU clock (or less) n Main memory can take many cycles n Cache sits between main memory and CPU registers n Protection of memory required to ensure correct operation Operating System Concepts – 8 th Edition 8. 4 Silberschatz, Galvin and Gagne © 2009

Memory management n Memory management is the functionality of an operating system which handles or manages primary memory. n Memory management keeps track of each and every memory location either it is allocated to some process or it is free. n It checks how much memory is to be allocated to processes. n It decides which process will get memory at what time. n It tracks whenever some memory gets freed or unallocated and correspondingly it updates the status. Operating System Concepts – 8 th Edition 8. 5 Silberschatz, Galvin and Gagne © 2009

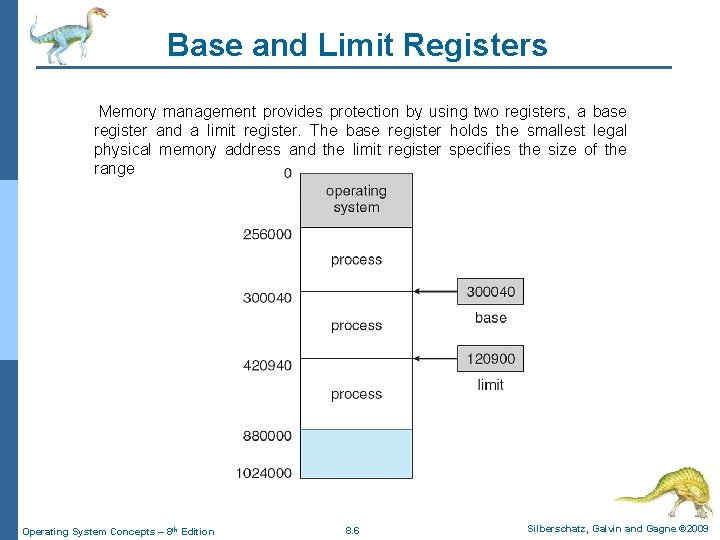

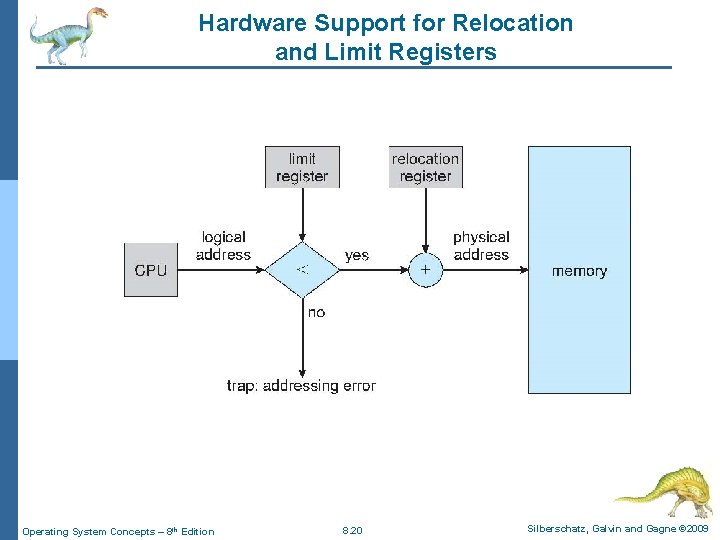

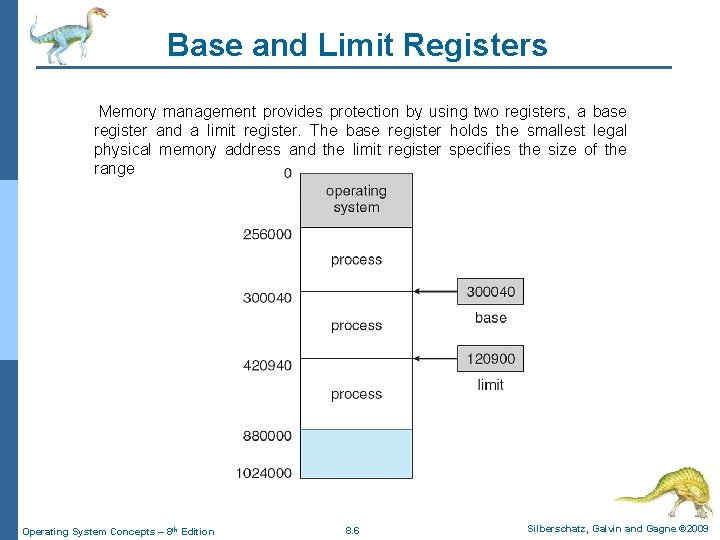

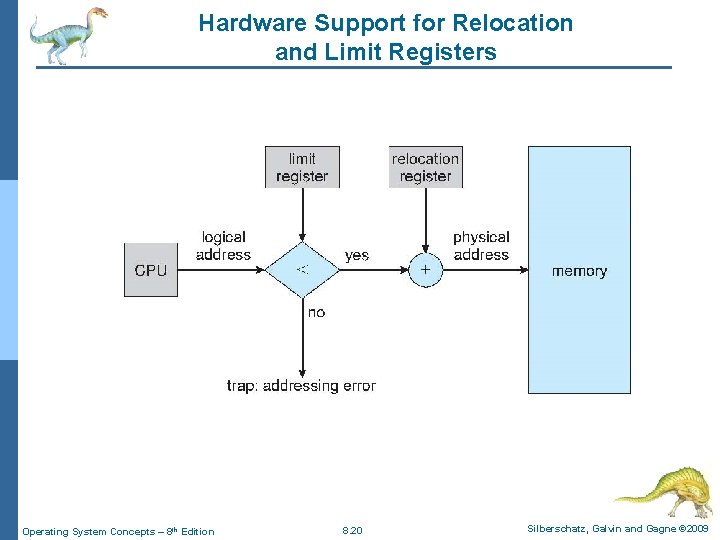

Base and Limit Registers Memory management provides protection by using two registers, a base register and a limit register. The base register holds the smallest legal physical memory address and the limit register specifies the size of the range Operating System Concepts – 8 th Edition 8. 6 Silberschatz, Galvin and Gagne © 2009

Binding of Instructions and Data to Memory Computer memory has two types of addresses. These are logical addresses and physical addresses. Address binding allocates a physical memory location to a logical pointer by associating a physical address to a logical address. The logical address is also known as a virtual address. Address binding is part of memory management and is performed by the operating system on behalf of applications requiring access to memory Address binding relates to how the code of a program is stored in memory. Operating System Concepts – 8 th Edition 8. 7 Silberschatz, Galvin and Gagne © 2009

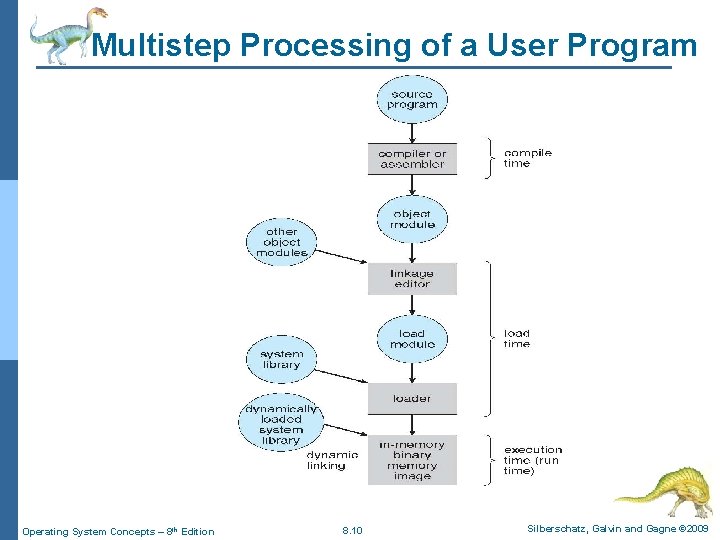

Binding of Instructions and Data to Memory User programs typically refer to memory addresses with symbolic names such as "i", "count", and "average Temperature". These symbolic names must be mapped or bound to physical memory addresses, which typically occurs in several stages: n Compile Time - If it is known at compile time where a program will reside in physical memory, then absolute code can be generated by the compiler, containing actual physical addresses. However if the load address changes at some later time, then the program will have to be recompiled. DOS. COM programs use compile time binding. Operating System Concepts – 8 th Edition 8. 8 Silberschatz, Galvin and Gagne © 2009

Binding of Instructions and Data to Memory n Load Time - If the location at which a program will be loaded is not known at compile time, then compiler must generate re-locatable code, which references addresses relative to the start of the program. If that starting address changes, then the program must be reloaded but not recompiled. n Execution Time - If a program can be moved around in memory during the course of its execution, then binding must be delayed until execution time. This requires special hardware, and is the method implemented by most modern OSes. Operating System Concepts – 8 th Edition 8. 9 Silberschatz, Galvin and Gagne © 2009

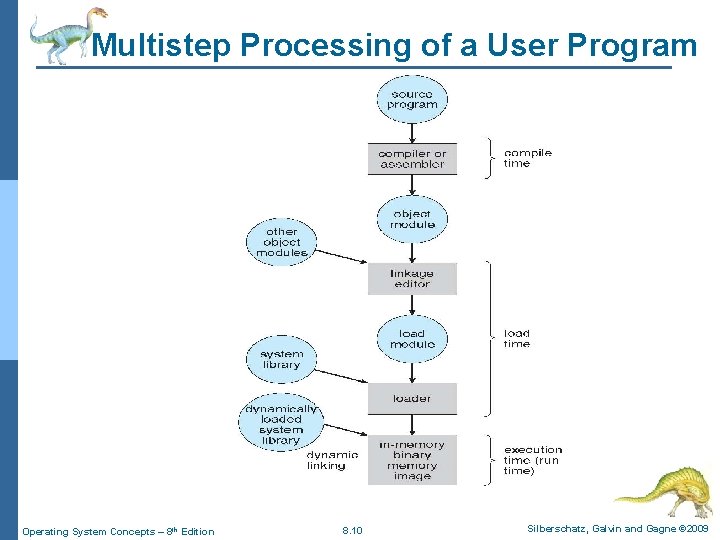

Multistep Processing of a User Program Operating System Concepts – 8 th Edition 8. 10 Silberschatz, Galvin and Gagne © 2009

Logical vs. Physical Address Space n n The concept of a logical address space that is bound to a separate physical address space is central to proper memory management l Logical address – generated by the CPU; also referred to as virtual address l Physical address – address seen by the memory unit Logical and physical addresses are the same in compile-time and loadtime address-binding schemes; logical (virtual) and physical addresses differ in execution-time address-binding scheme Operating System Concepts – 8 th Edition 8. 11 Silberschatz, Galvin and Gagne © 2009

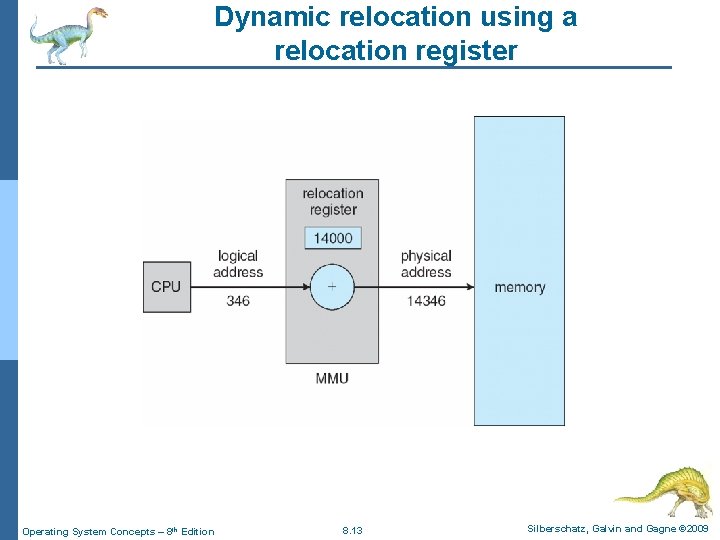

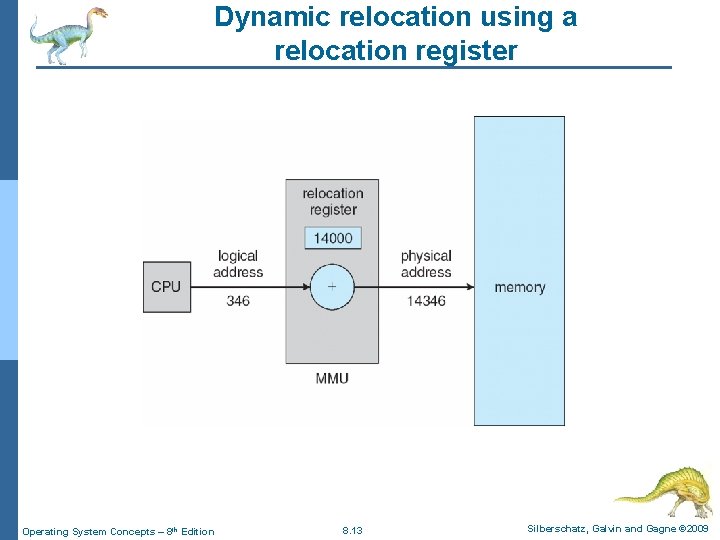

Memory-Management Unit (MMU) n The run time mapping of logical to physical addresses is handled by the memory-management unit, MMU. n Hardware device that maps virtual to physical address n In MMU scheme, the value in the relocation register is added to every address generated by a user process (CPU) at the time it is sent to memory n The user program deals with logical addresses; it never sees the real physical addresses Operating System Concepts – 8 th Edition 8. 12 Silberschatz, Galvin and Gagne © 2009

Dynamic relocation using a relocation register Operating System Concepts – 8 th Edition 8. 13 Silberschatz, Galvin and Gagne © 2009

Dynamic Loading In dynamic loading, a routine of a program is not loaded until it is called by the program. All routines are kept on disk in a re-locatable load format. The main program is loaded into memory and is executed. Other routines methods or modules are loaded on request. Dynamic loading makes better memory space utilization and unused routines are never loaded. The advantage is that unused routines need never be loaded, reducing total memory usage and generating faster program startup times. The downside is the added complexity and overhead of checking to see if a routine is loaded every time it is called and then loading it up if it is not already loaded. Operating System Concepts – 8 th Edition 8. 14 Silberschatz, Galvin and Gagne © 2009

Dynamic Linking n Linking is the process of collecting and combining various modules of code and data into a executable file that can be loaded into memory and executed. Operating system can link system level libraries to a program. When it combines the libraries at load time, the linking is called static linking and when this linking is done at the time of execution, it is called as dynamic linking. n In static linking, libraries linked at compile time, so program code size becomes bigger whereas in dynamic linking libraries linked at execution time so program code size remains smaller. Operating System Concepts – 8 th Edition 8. 15 Silberschatz, Galvin and Gagne © 2009

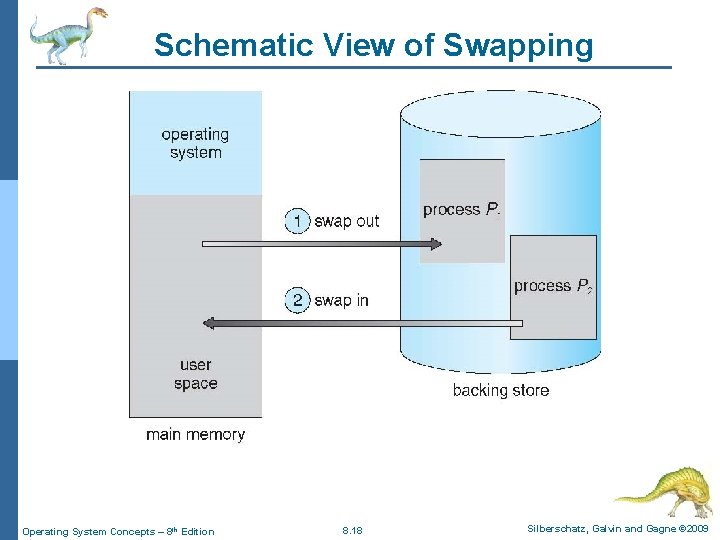

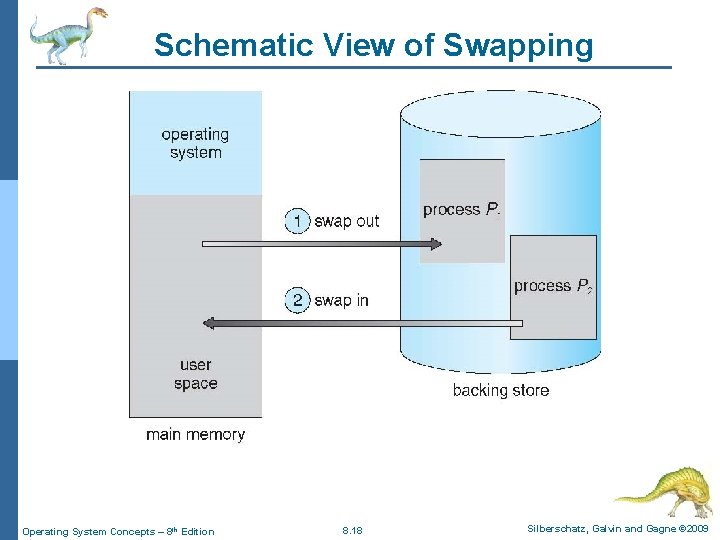

Swapping n A process must be loaded into memory in order to execute. n If there is not enough memory available to keep all running processes in memory at the same time, then some processes who are not currently using the CPU may have their memory swapped out to a fast local disk called the backing store. n Backing store – fast disk large enough to accommodate copies of all memory images for all users; must provide direct access to these memory images n Roll out, roll in – swapping variant used for priority-based scheduling algorithms; lower-priority process is swapped out so higher-priority process can be loaded and executed Operating System Concepts – 8 th Edition 8. 16 Silberschatz, Galvin and Gagne © 2009

Swapping n To reduce swapping transfer overhead, it is desired to transfer as little information as possible, which requires that the system know how much memory a process is using, as opposed to how much it might use n It is important to swap processes out of memory only when they are idle, or more to the point, only when there are no pending I/O operations (Otherwise the pending I/O operation could write into the wrong process's memory space. ) n Most modern OSes no longer use swapping, because it is too slow and there are faster alternatives available. Operating System Concepts – 8 th Edition 8. 17 Silberschatz, Galvin and Gagne © 2009

Schematic View of Swapping Operating System Concepts – 8 th Edition 8. 18 Silberschatz, Galvin and Gagne © 2009

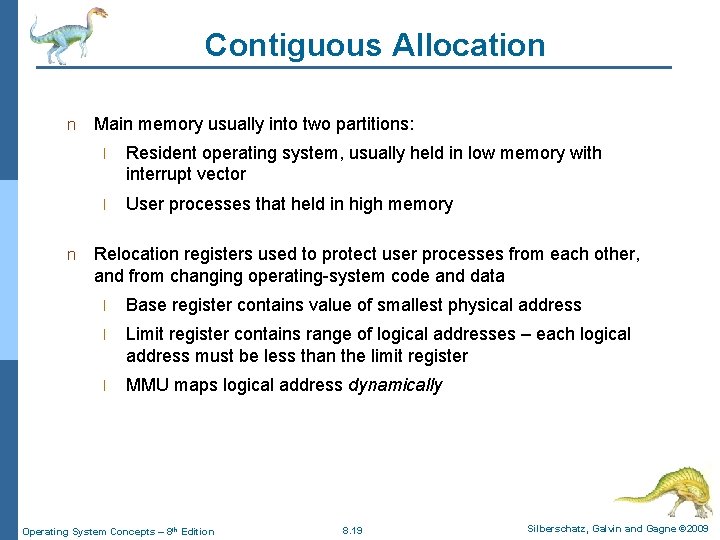

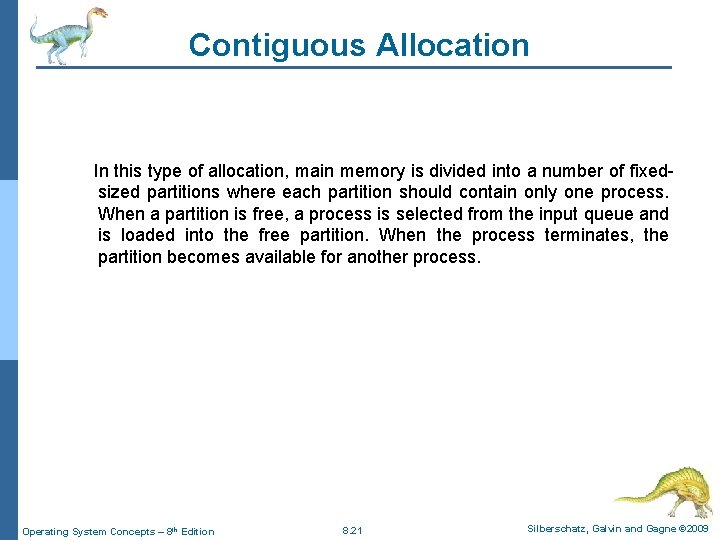

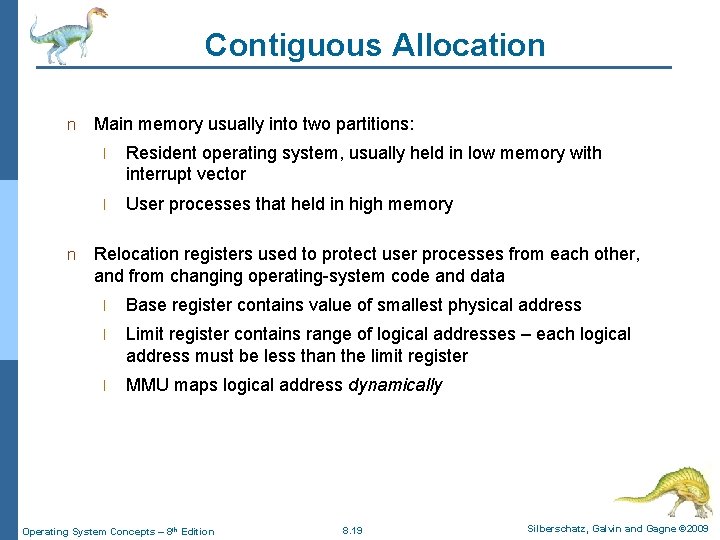

Contiguous Allocation n n Main memory usually into two partitions: l Resident operating system, usually held in low memory with interrupt vector l User processes that held in high memory Relocation registers used to protect user processes from each other, and from changing operating-system code and data l Base register contains value of smallest physical address l Limit register contains range of logical addresses – each logical address must be less than the limit register l MMU maps logical address dynamically Operating System Concepts – 8 th Edition 8. 19 Silberschatz, Galvin and Gagne © 2009

Hardware Support for Relocation and Limit Registers Operating System Concepts – 8 th Edition 8. 20 Silberschatz, Galvin and Gagne © 2009

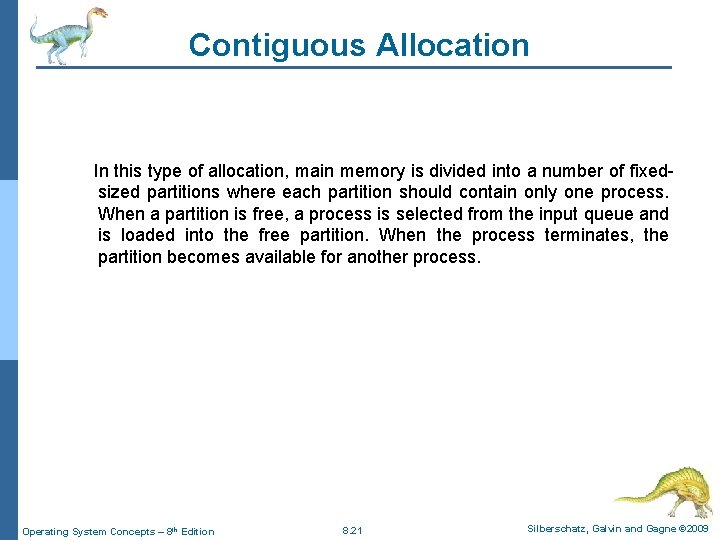

Contiguous Allocation In this type of allocation, main memory is divided into a number of fixedsized partitions where each partition should contain only one process. When a partition is free, a process is selected from the input queue and is loaded into the free partition. When the process terminates, the partition becomes available for another process. Operating System Concepts – 8 th Edition 8. 21 Silberschatz, Galvin and Gagne © 2009

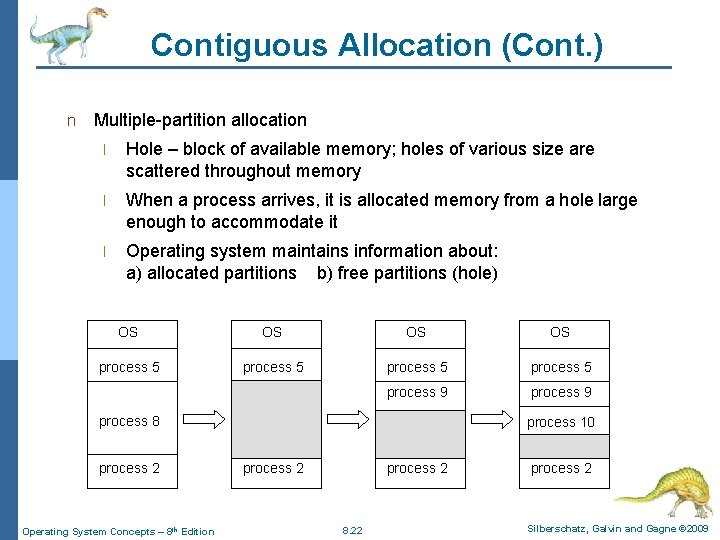

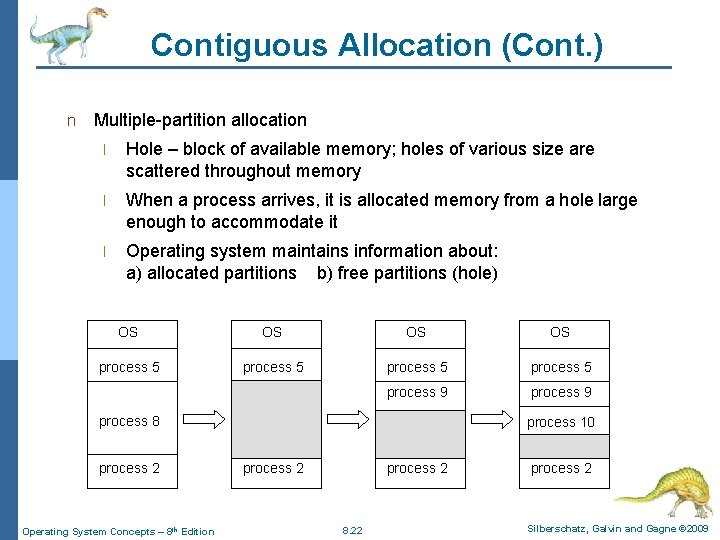

Contiguous Allocation (Cont. ) n Multiple-partition allocation l Hole – block of available memory; holes of various size are scattered throughout memory l When a process arrives, it is allocated memory from a hole large enough to accommodate it l Operating system maintains information about: a) allocated partitions b) free partitions (hole) OS OS process 5 process 9 process 8 process 2 Operating System Concepts – 8 th Edition process 10 process 2 8. 22 process 2 Silberschatz, Galvin and Gagne © 2009

Dynamic Storage-Allocation Problem First fit - Search the list of holes until one is found that is big enough to satisfy the request, and assign a portion of that hole to that process. Whatever fraction of the hole not needed by the request is left on the free list as a smaller hole. Subsequent requests may start looking either from the beginning of the list or from the point at which this search ended. Best fit - Allocate the smallest hole that is big enough to satisfy the request. This saves large holes for other process requests that may need them later, but the resulting unused portions of holes may be too small to be of any use, and will therefore be wasted. Keeping the free list sorted can speed up the process of finding the right hole. Operating System Concepts – 8 th Edition 8. 23 Silberschatz, Galvin and Gagne © 2009

Dynamic Storage-Allocation Problem Worst fit - Allocate the largest hole available, thereby increasing the likelihood that the remaining portion will be usable for satisfying future requests. Simulations show that either first or best fit are better than worst fit in terms of both time and storage utilization. First and best fits are about equal in terms of storage utilization, but first fit is faster Operating System Concepts – 8 th Edition 8. 24 Silberschatz, Galvin and Gagne © 2009

Fragmentation In computer fragmentation is a phenomenon in which storage space is used inefficiently, reducing capacity or performance and often both. External Fragmentation – total memory space exists to satisfy a request, but it is not contiguous Internal Fragmentation – allocated memory may be slightly larger than requested memory; this size difference is memory internal to a partition, but not being used Reduce external fragmentation by compaction l Shuffle memory contents to place all free memory together in one large block Operating System Concepts – 8 th Edition 8. 25 Silberschatz, Galvin and Gagne © 2009

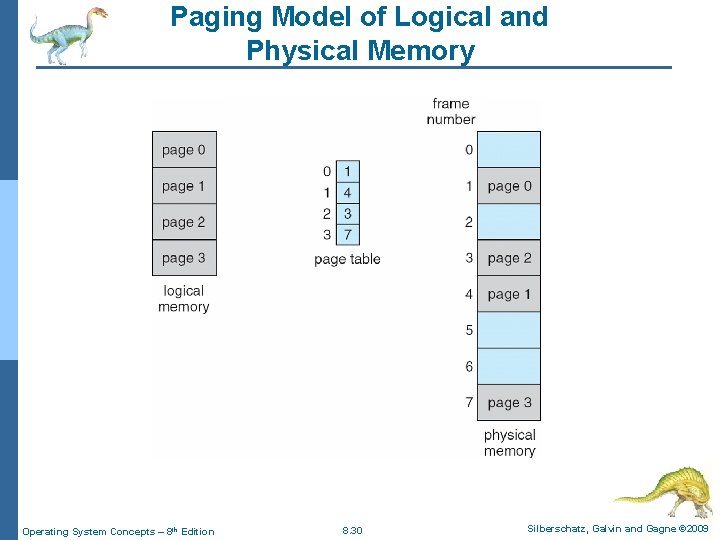

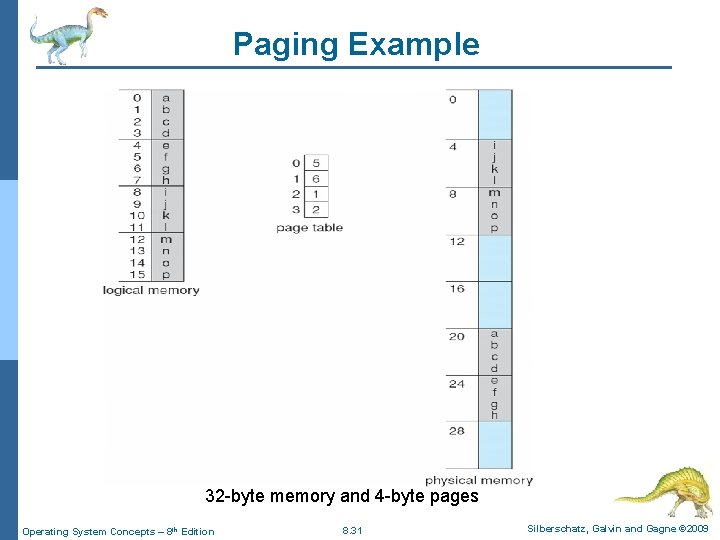

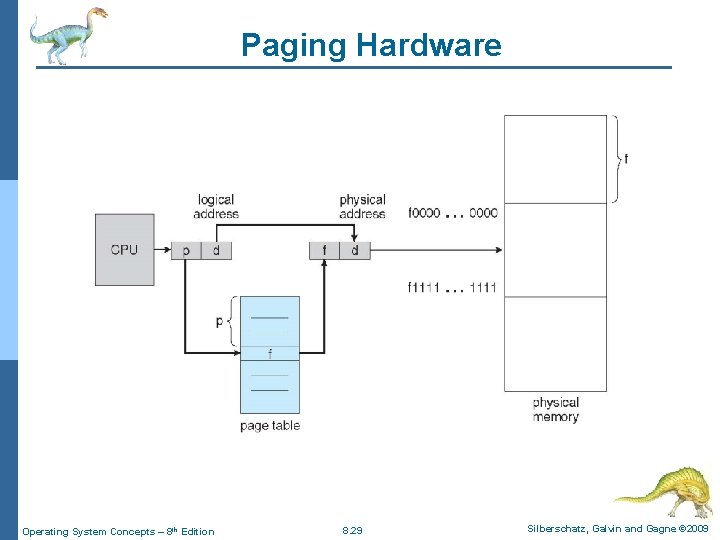

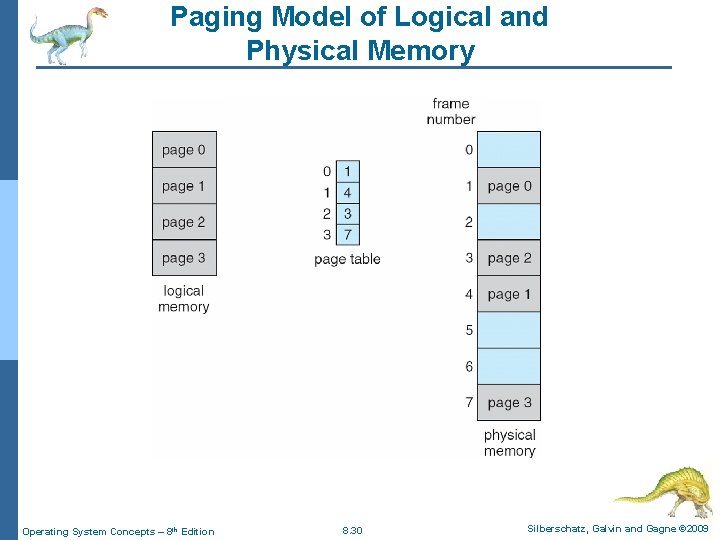

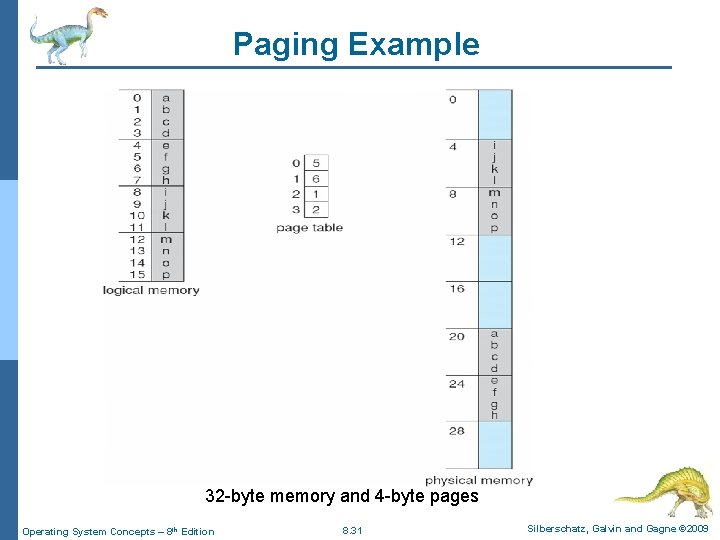

Paging n Paging is a memory management scheme that allows processes physical memory to be discontinuous, and which eliminates problems with fragmentation by allocating memory in equal sized blocks known as pages. n The basic idea behind paging is to divide physical memory into a number of equal sized blocks called frames, and to divide a programs logical memory space into blocks of the same size called pages. n Any page ( from any process ) can be placed into any available frame. n The page table is used to look up what frame a particular page is stored in at the moment Operating System Concepts – 8 th Edition 8. 26 Silberschatz, Galvin and Gagne © 2009

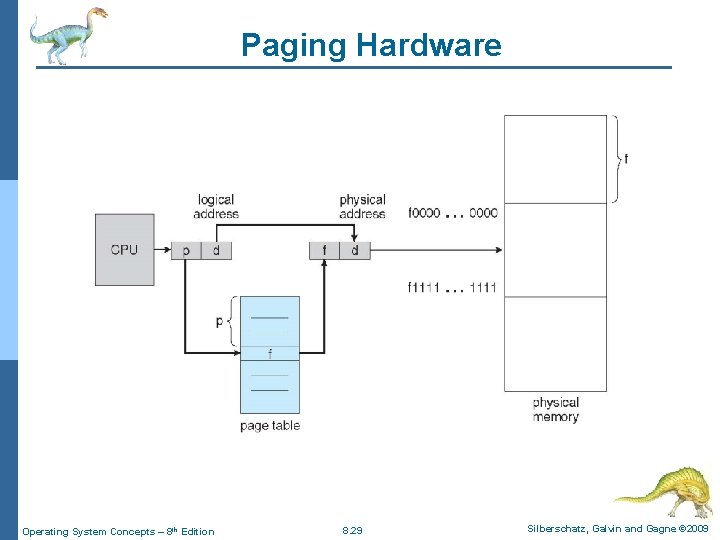

Address Translation Scheme n A logical address consists of two parts: A page number in which the address resides, and an offset from the beginning of that page. n The page table maps the page number to a frame number, to yield a physical address which also has two parts: The frame number and the offset within that frame. n Page numbers, frame numbers, and frame sizes are determined by the architecture, but are typically powers of two, allowing addresses to be split at a certain number of bits. Operating System Concepts – 8 th Edition 8. 27 Silberschatz, Galvin and Gagne © 2009

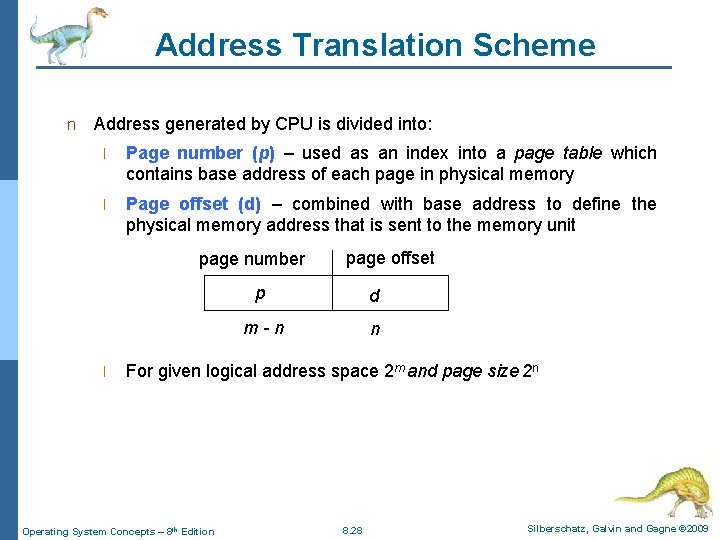

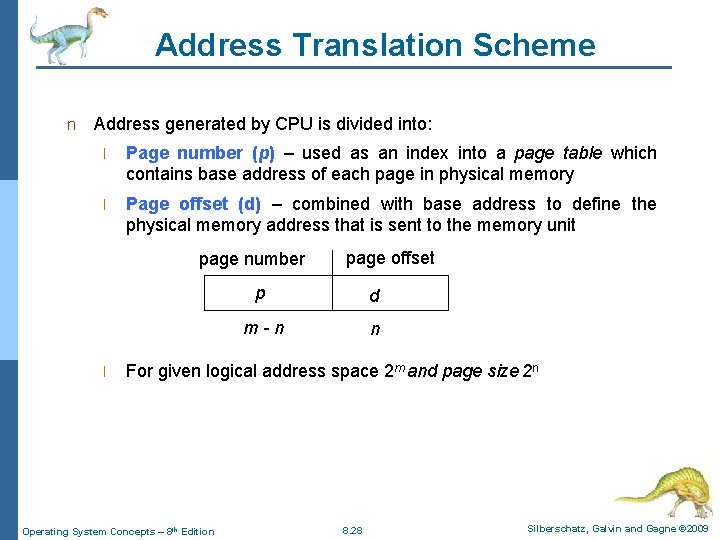

Address Translation Scheme n Address generated by CPU is divided into: l Page number (p) – used as an index into a page table which contains base address of each page in physical memory l Page offset (d) – combined with base address to define the physical memory address that is sent to the memory unit page number l page offset p d m-n n For given logical address space 2 m and page size 2 n Operating System Concepts – 8 th Edition 8. 28 Silberschatz, Galvin and Gagne © 2009

Paging Hardware Operating System Concepts – 8 th Edition 8. 29 Silberschatz, Galvin and Gagne © 2009

Paging Model of Logical and Physical Memory Operating System Concepts – 8 th Edition 8. 30 Silberschatz, Galvin and Gagne © 2009

Paging Example 32 -byte memory and 4 -byte pages Operating System Concepts – 8 th Edition 8. 31 Silberschatz, Galvin and Gagne © 2009

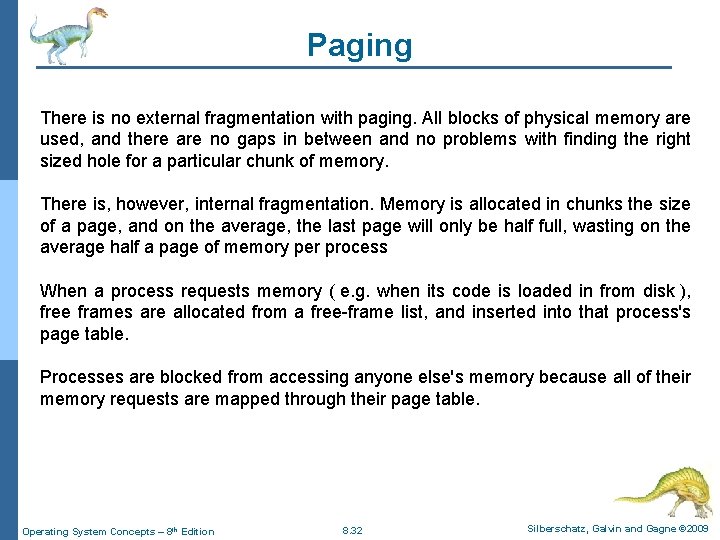

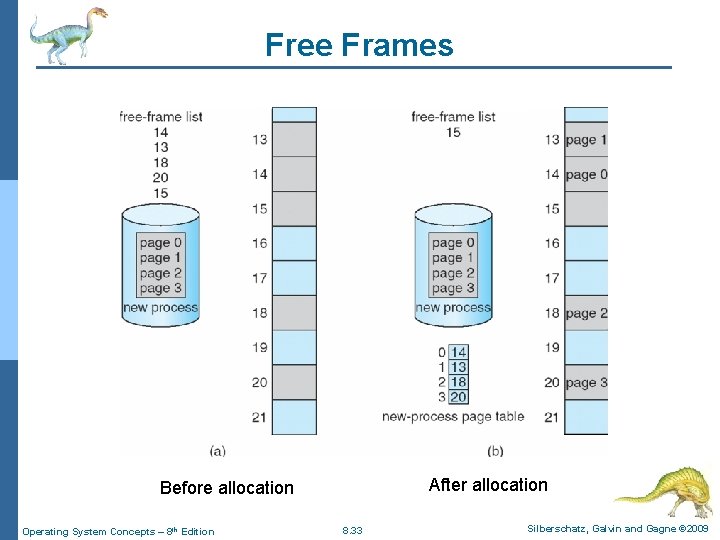

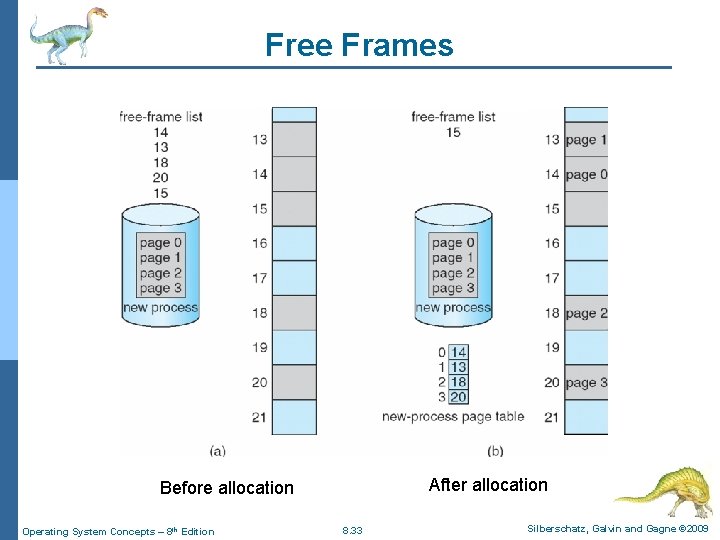

Paging There is no external fragmentation with paging. All blocks of physical memory are used, and there are no gaps in between and no problems with finding the right sized hole for a particular chunk of memory. There is, however, internal fragmentation. Memory is allocated in chunks the size of a page, and on the average, the last page will only be half full, wasting on the average half a page of memory per process When a process requests memory ( e. g. when its code is loaded in from disk ), free frames are allocated from a free-frame list, and inserted into that process's page table. Processes are blocked from accessing anyone else's memory because all of their memory requests are mapped through their page table. Operating System Concepts – 8 th Edition 8. 32 Silberschatz, Galvin and Gagne © 2009

Free Frames After allocation Before allocation Operating System Concepts – 8 th Edition 8. 33 Silberschatz, Galvin and Gagne © 2009

Hardware Support Page lookups must be done for every memory reference, and whenever a process gets swapped in or out of the CPU, its page table must be swapped in and out too, along with the instruction registers, etc. It is therefore appropriate to provide hardware support for this operation, in order to make it as fast as possible and to make process switches as fast as possible also Operating System Concepts – 8 th Edition 8. 34 Silberschatz, Galvin and Gagne © 2009

Hardware Support Special purpose registers • Page table is stored in a set of dedicated, high-speed registers • Instructions to load/modify PT registers are privileged • Acceptable solution if page table is small Example: DEC PDP-11 16 -bit address space 8 K page size page table contains 8 entries Operating System Concepts – 8 th Edition 8. 35 Silberschatz, Galvin and Gagne © 2009

Hardware Support Memory + PTBR: • Needed for large page tables • PT stored in main memory • Base address of PT is stored in page table base register(PTBR) Context switch involves changing 1 register only Two physical memory accesses are needed per user memory access ⇒ memory access is slowed by factor of 2 Operating System Concepts – 8 th Edition 8. 36 Silberschatz, Galvin and Gagne © 2009

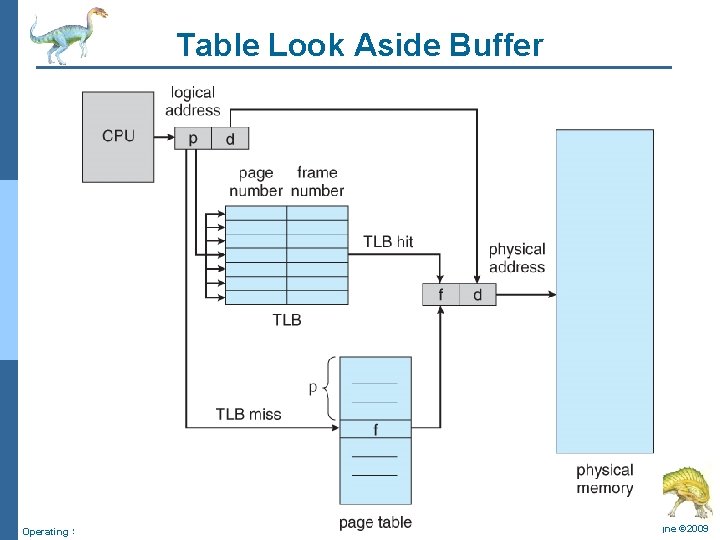

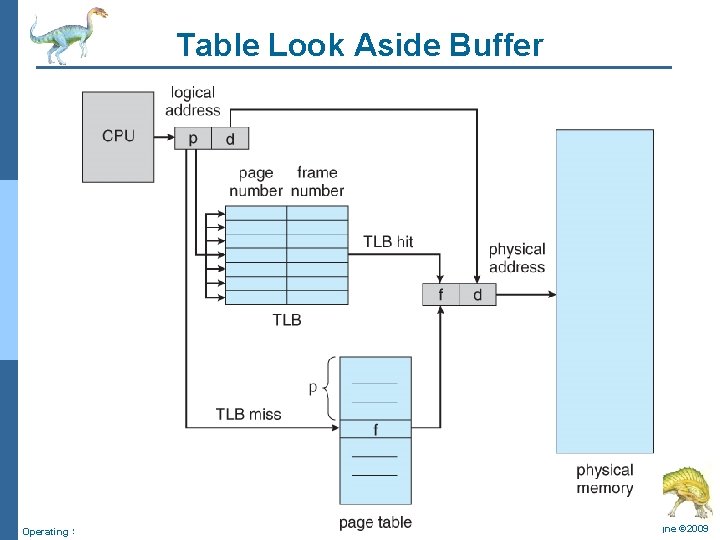

Hardware Support Associative registers/Translation look-aside buffer (TLB) TLB ≡ small, fast-lookup hardware cache, built using high-speed memory (expensive) each register holds key +value input value is compared simultaneously with all keys on match, corresponding value is returned TLB holds subset of page table entries TLB hit ⇒ additional overhead may be 10% or less TLB miss ⇒ new h page#, frame# i added to TLB has to be flushed on context-switch Operating System Concepts – 8 th Edition 8. 37 Silberschatz, Galvin and Gagne © 2009

Table Look Aside Buffer Operating System Concepts – 8 th Edition 8. 38 Silberschatz, Galvin and Gagne © 2009

Table Look Aside Buffer Hit ratio: percentage of times that a page# is found in TLB depends on size of TLB Effective memory access time: average time for a memory access (including TLB lookup) Example: TLB lookup: 20 ns Memory access: 100 ns Hit ratio: 80% Effective access time = 0. 8 × 120 + 0. 2 × 220 = 140 ns Operating System Concepts – 8 th Edition 8. 39 Silberschatz, Galvin and Gagne © 2009

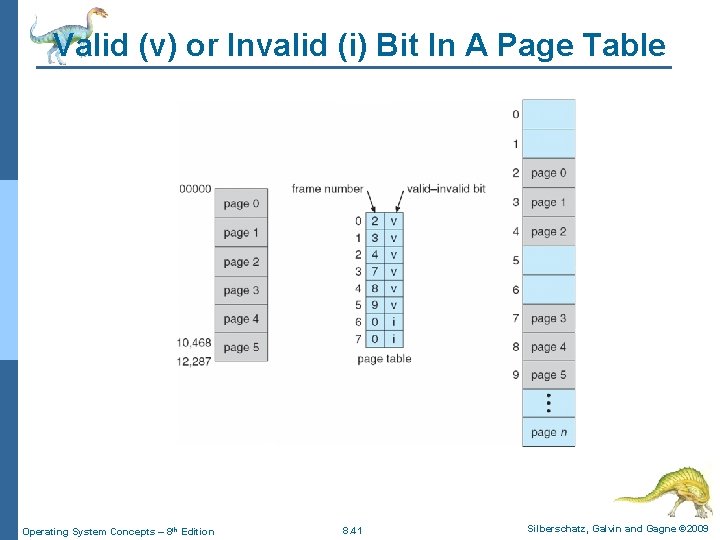

Memory Protection • Protection bit(s) associated with each frame (via page table entry) • protection bit specifies read-only / read-write access • protection bit checked in parallel with address computation • protection violation (writing to read-only page) causes hardware trap to OS • Valid/invalid bit indicates whether page is in the process’ logical address space set by OS for each page may be used to implement process size restrictions Operating System Concepts – 8 th Edition 8. 40 Silberschatz, Galvin and Gagne © 2009

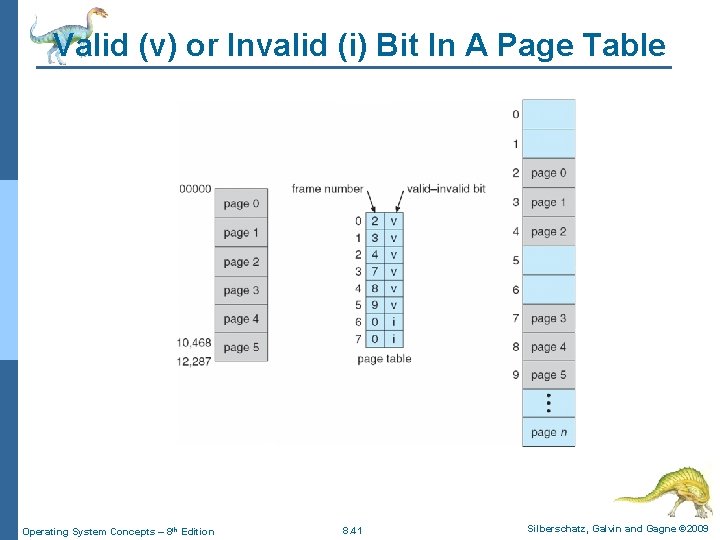

Valid (v) or Invalid (i) Bit In A Page Table Operating System Concepts – 8 th Edition 8. 41 Silberschatz, Galvin and Gagne © 2009

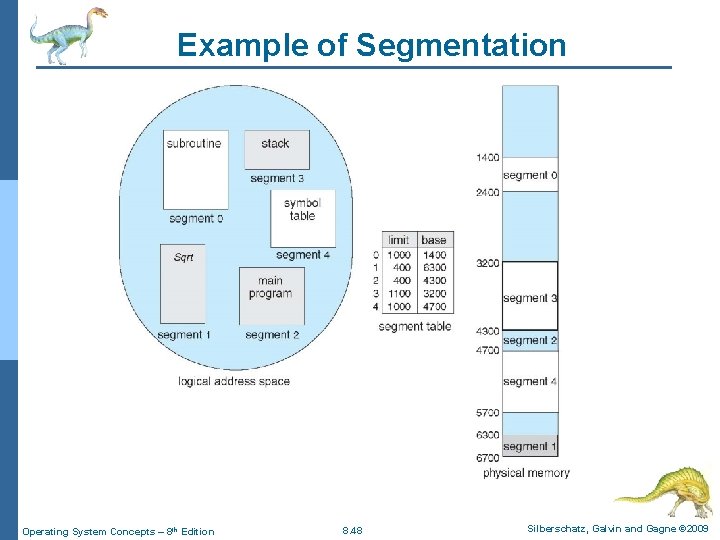

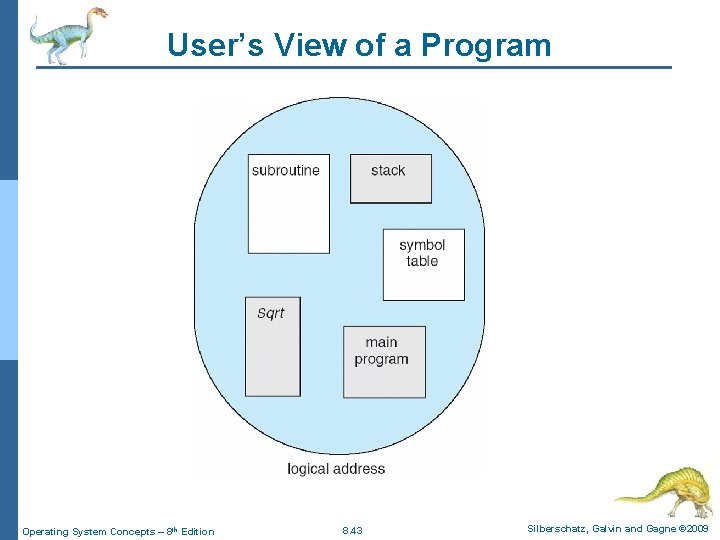

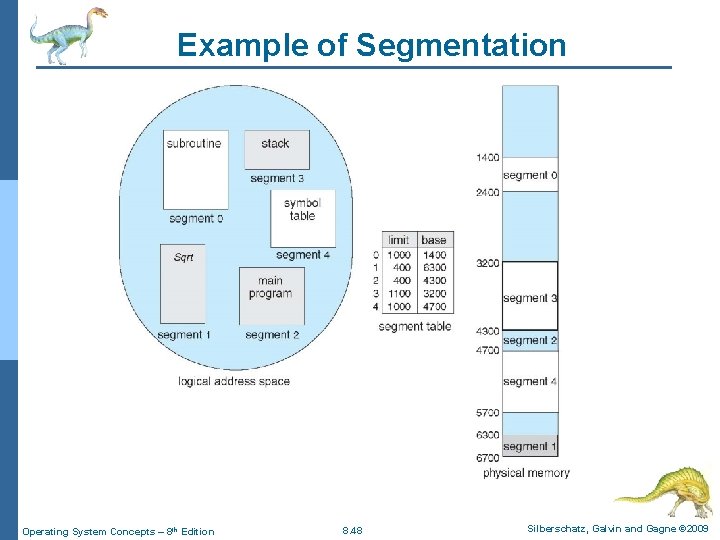

Segmentation n Most users ( programmers ) do not think of their programs as existing in one continuous linear address space. Rather they tend to think of their memory in multiple segments, each dedicated to a particular use, such as code, data, the stack, the heap, etc. n Memory segmentation supports this view by providing addresses with a segment number ( mapped to a segment base address ) and an offset from the beginning of that segment. n For example, a C compiler might generate 5 segments for the user code, library code, global ( static ) variables, the stack, and the heap Operating System Concepts – 8 th Edition 8. 42 Silberschatz, Galvin and Gagne © 2009

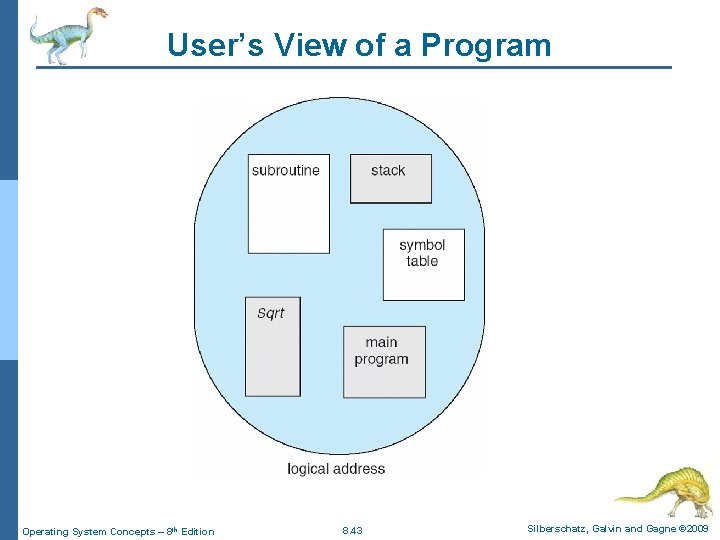

User’s View of a Program Operating System Concepts – 8 th Edition 8. 43 Silberschatz, Galvin and Gagne © 2009

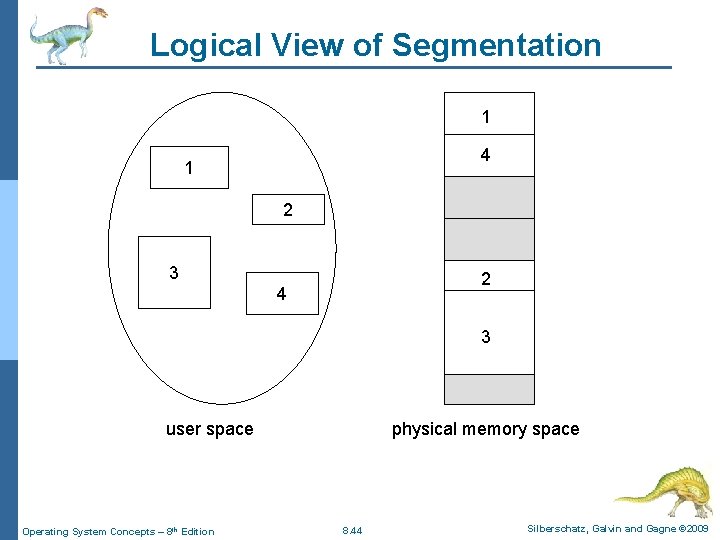

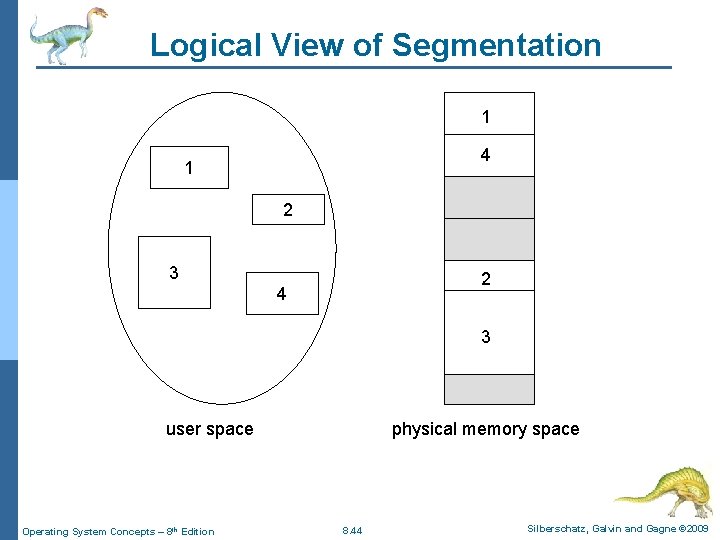

Logical View of Segmentation 1 4 1 2 3 2 4 3 user space Operating System Concepts – 8 th Edition physical memory space 8. 44 Silberschatz, Galvin and Gagne © 2009

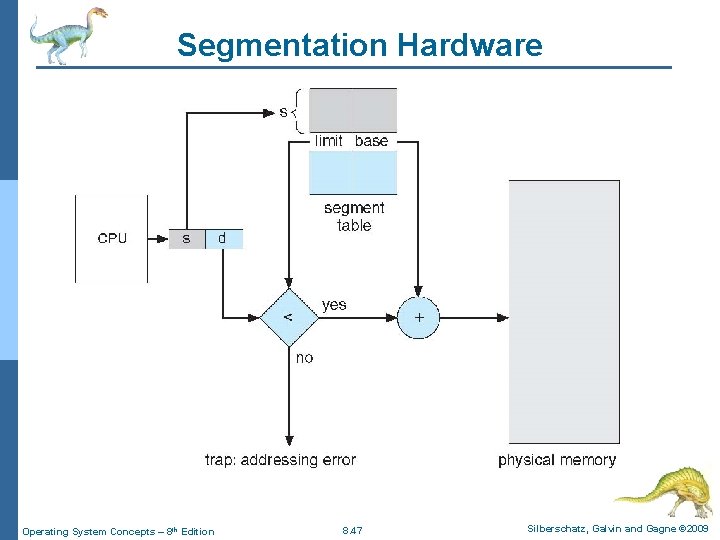

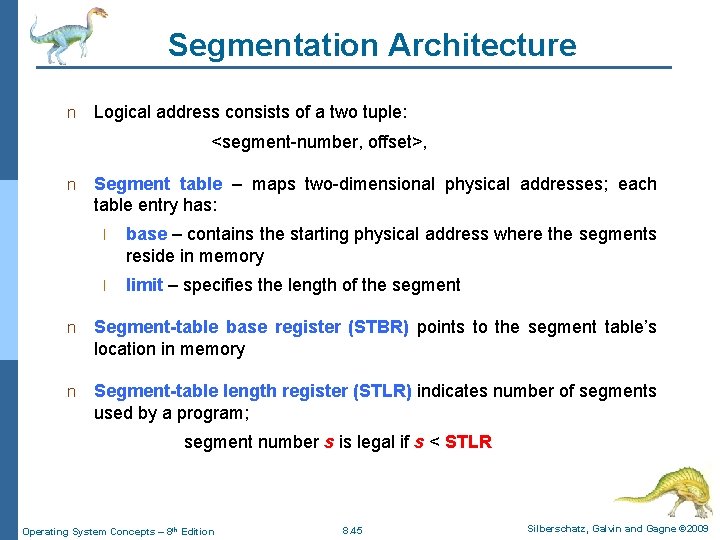

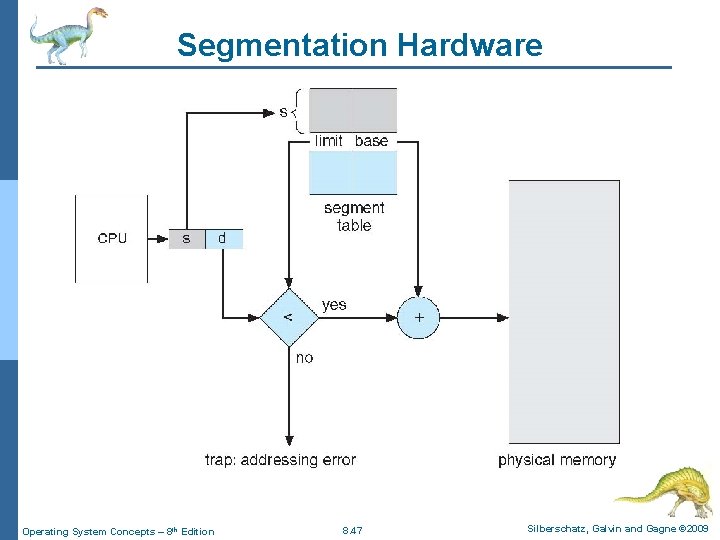

Segmentation Architecture n Logical address consists of a two tuple: <segment-number, offset>, n Segment table – maps two-dimensional physical addresses; each table entry has: l base – contains the starting physical address where the segments reside in memory l limit – specifies the length of the segment n Segment-table base register (STBR) points to the segment table’s location in memory n Segment-table length register (STLR) indicates number of segments used by a program; segment number s is legal if s < STLR Operating System Concepts – 8 th Edition 8. 45 Silberschatz, Galvin and Gagne © 2009

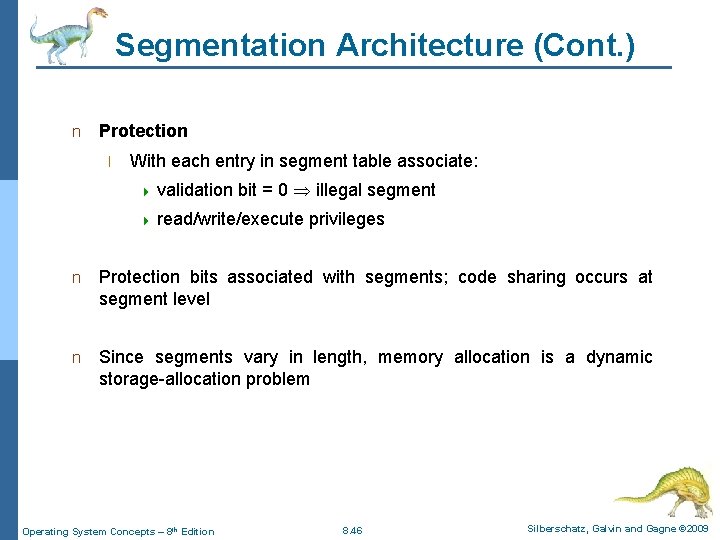

Segmentation Architecture (Cont. ) n Protection l With each entry in segment table associate: 4 validation bit = 0 illegal segment 4 read/write/execute privileges n Protection bits associated with segments; code sharing occurs at segment level n Since segments vary in length, memory allocation is a dynamic storage-allocation problem Operating System Concepts – 8 th Edition 8. 46 Silberschatz, Galvin and Gagne © 2009

Segmentation Hardware Operating System Concepts – 8 th Edition 8. 47 Silberschatz, Galvin and Gagne © 2009

Example of Segmentation Operating System Concepts – 8 th Edition 8. 48 Silberschatz, Galvin and Gagne © 2009