Operating System Main Memory Operating System Concepts 8

- Slides: 47

Operating System Main Memory Operating System Concepts – 8 th Edition, Silberschatz, Galvin and Gagne © 2009

Background n Program must be brought (from disk) into memory and placed within a process for it to be run n Main memory and registers are only storage CPU can access directly n Register access in one CPU clock (or less) n Main memory can take many cycles n Cache sits between main memory and CPU registers n Protection of memory required to ensure correct operation Operating System Concepts – 8 th Edition 8. 2 Silberschatz, Galvin and Gagne © 2009

The Problem n There is a finite amount of RAM on any machine. n There is a bus with finite speed, non-zero latency. n There is a CPU with a given clock speed. n There is a disk with a given speed. n How do we manage memory effectively? l Mainly, that means preventing CPU idle time, maintaining good response time, etc. l While maintaining isolation and security. Operating System Concepts – 8 th Edition 8. 3 Silberschatz, Galvin and Gagne © 2009

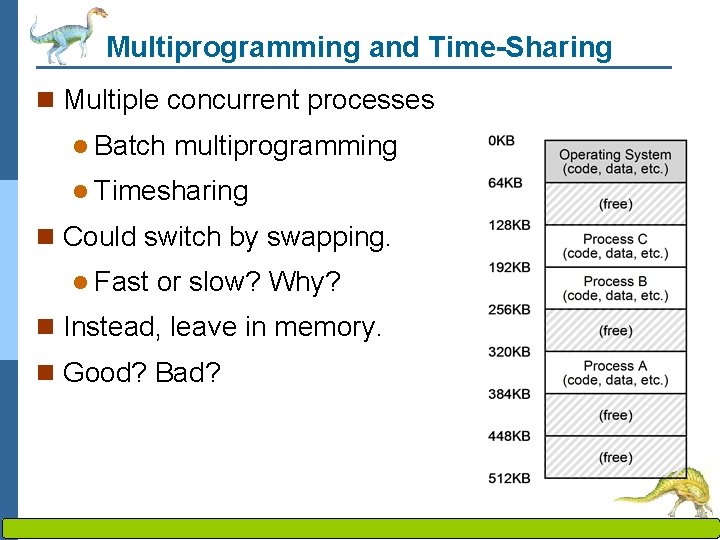

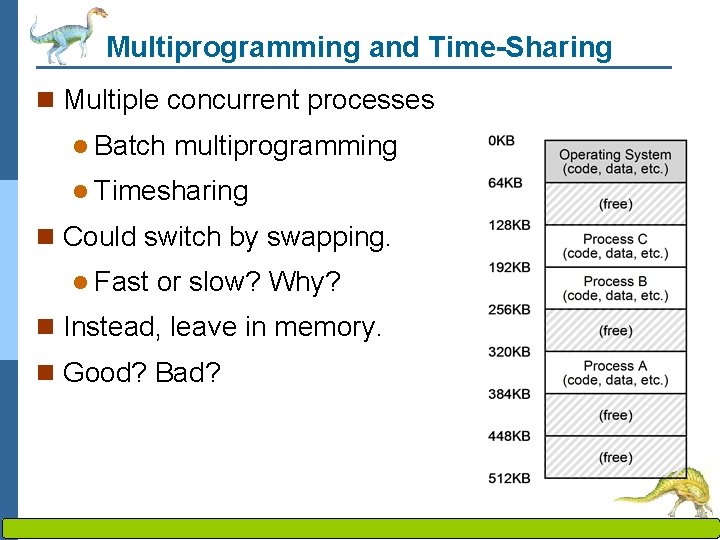

Multiprogramming and Time-Sharing n Multiple concurrent processes l Batch multiprogramming l Timesharing n Could switch by swapping. l Fast or slow? Why? n Instead, leave in memory. n Good? Bad? Operating System Concepts – 8 th Edition 8. 4 Silberschatz, Galvin and Gagne © 2009

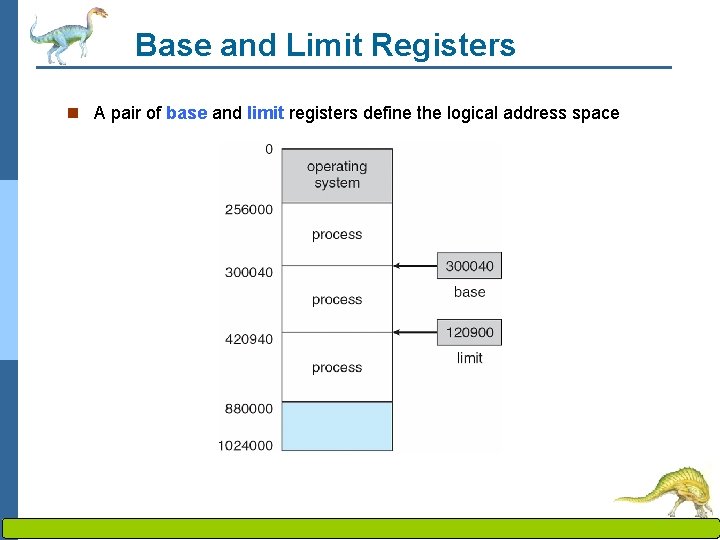

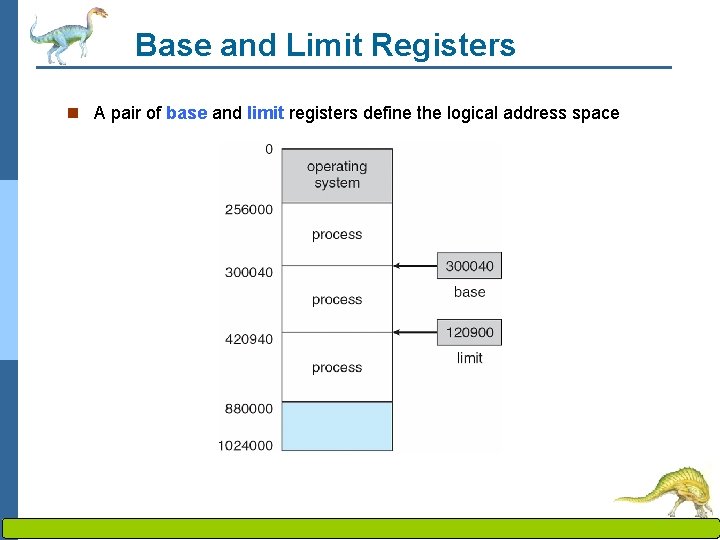

Base and Limit Registers n A pair of base and limit registers define the logical address space Operating System Concepts – 8 th Edition 8. 5 Silberschatz, Galvin and Gagne © 2009

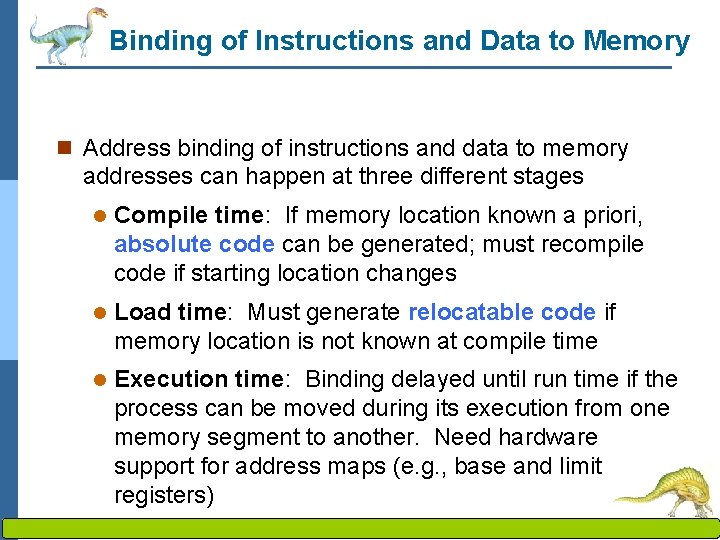

Binding of Instructions and Data to Memory n Address binding of instructions and data to memory addresses can happen at three different stages l Compile time: If memory location known a priori, absolute code can be generated; must recompile code if starting location changes l Load time: Must generate relocatable code if memory location is not known at compile time l Execution time: Binding delayed until run time if the process can be moved during its execution from one memory segment to another. Need hardware support for address maps (e. g. , base and limit registers) Operating System Concepts – 8 th Edition 8. 6 Silberschatz, Galvin and Gagne © 2009

Logical vs. Physical Address Space n The concept of a logical address space that is bound to a separate physical address space is central to proper memory management l Logical address – generated by the CPU; also referred to as virtual address l Physical address – address seen by the memory unit n Logical and physical addresses are the same in compile- time and load-time address-binding schemes; logical (virtual) and physical addresses differ in execution-time address-binding scheme Operating System Concepts – 8 th Edition 8. 7 Silberschatz, Galvin and Gagne © 2009

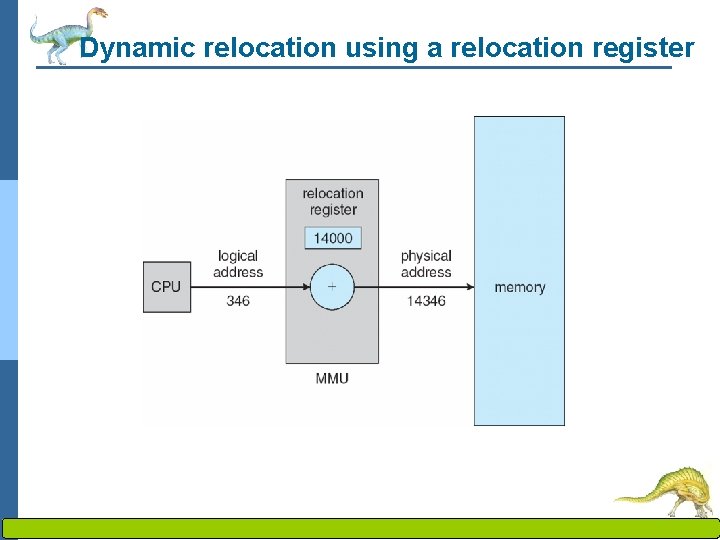

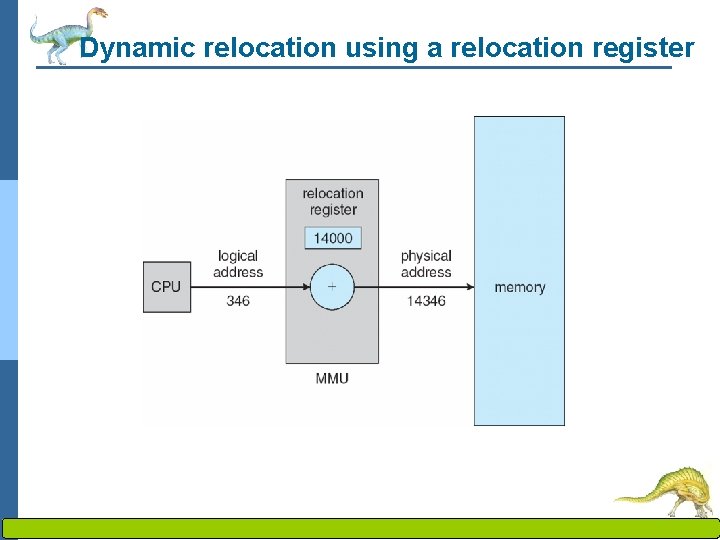

Memory-Management Unit (MMU) n Hardware device that maps virtual to physical address n In MMU scheme, the value in the relocation register is added to every address generated by a user process at the time it is sent to memory n The user program deals with logical addresses; it never sees the real physical addresses Operating System Concepts – 8 th Edition 8. 8 Silberschatz, Galvin and Gagne © 2009

Dynamic relocation using a relocation register Operating System Concepts – 8 th Edition 8. 9 Silberschatz, Galvin and Gagne © 2009

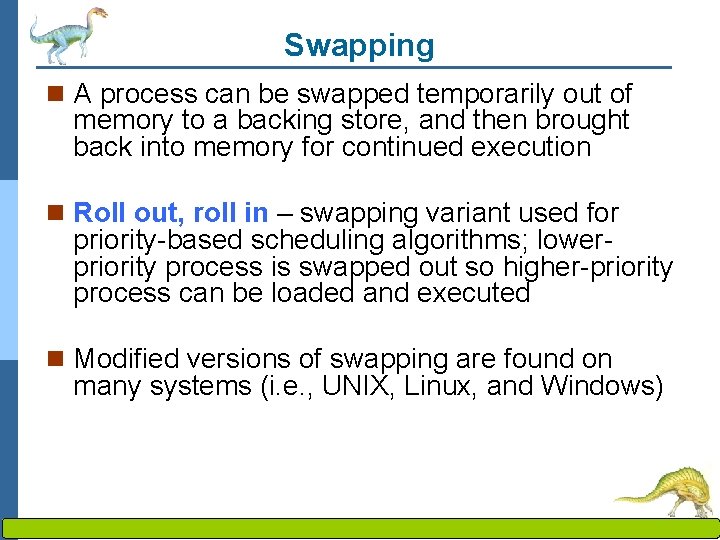

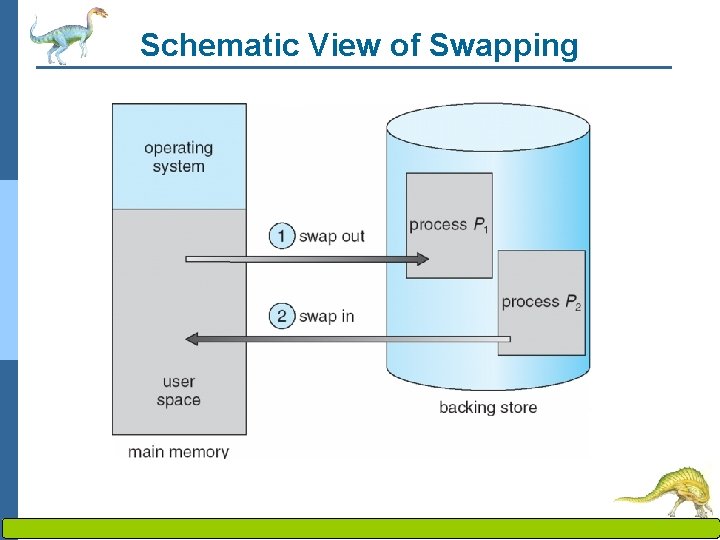

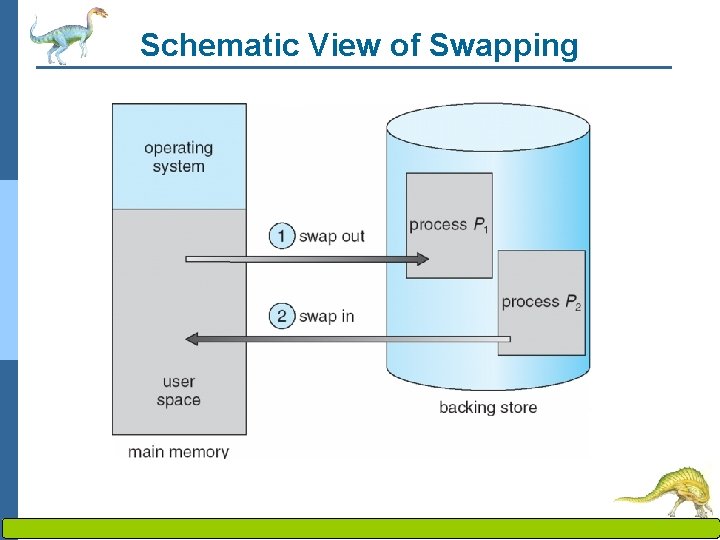

Swapping n A process can be swapped temporarily out of memory to a backing store, and then brought back into memory for continued execution n Roll out, roll in – swapping variant used for priority-based scheduling algorithms; lowerpriority process is swapped out so higher-priority process can be loaded and executed n Modified versions of swapping are found on many systems (i. e. , UNIX, Linux, and Windows) Operating System Concepts – 8 th Edition 8. 10 Silberschatz, Galvin and Gagne © 2009

Schematic View of Swapping Operating System Concepts – 8 th Edition 8. 11 Silberschatz, Galvin and Gagne © 2009

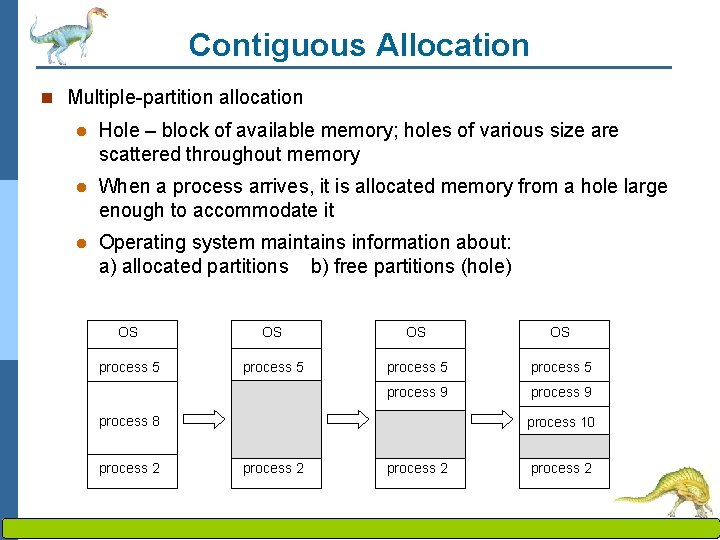

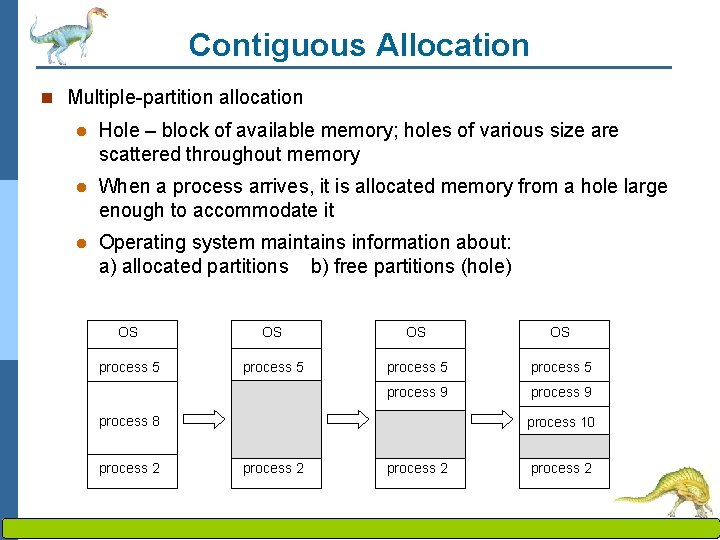

Contiguous Allocation n Multiple-partition allocation l Hole – block of available memory; holes of various size are scattered throughout memory l When a process arrives, it is allocated memory from a hole large enough to accommodate it l Operating system maintains information about: a) allocated partitions b) free partitions (hole) OS OS process 5 process 9 process 8 process 2 Operating System Concepts – 8 th Edition process 10 process 2 8. 12 process 2 Silberschatz, Galvin and Gagne © 2009

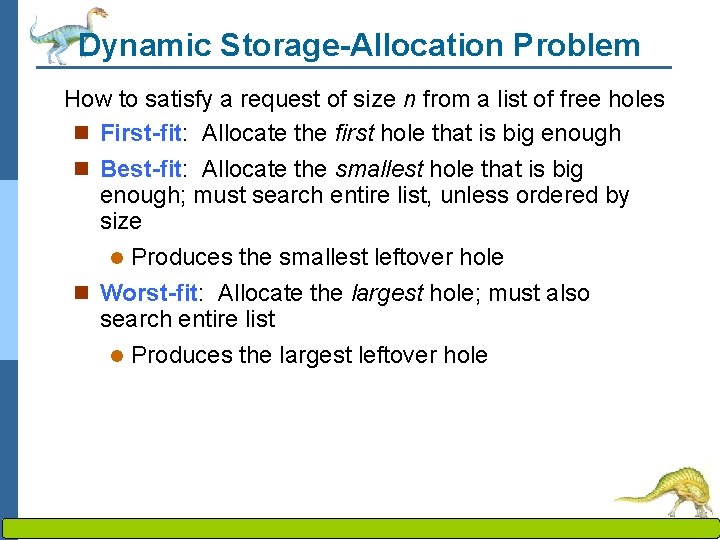

Dynamic Storage-Allocation Problem How to satisfy a request of size n from a list of free holes n First-fit: Allocate the first hole that is big enough n Best-fit: Allocate the smallest hole that is big enough; must search entire list, unless ordered by size l Produces the smallest leftover hole n Worst-fit: Allocate the largest hole; must also search entire list l Produces the largest leftover hole Operating System Concepts – 8 th Edition 8. 13 Silberschatz, Galvin and Gagne © 2009

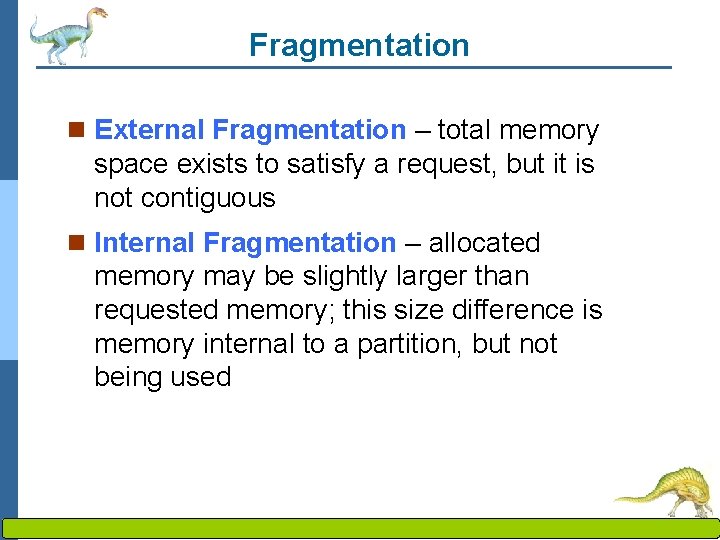

Fragmentation n External Fragmentation – total memory space exists to satisfy a request, but it is not contiguous n Internal Fragmentation – allocated memory may be slightly larger than requested memory; this size difference is memory internal to a partition, but not being used Operating System Concepts – 8 th Edition 8. 14 Silberschatz, Galvin and Gagne © 2009

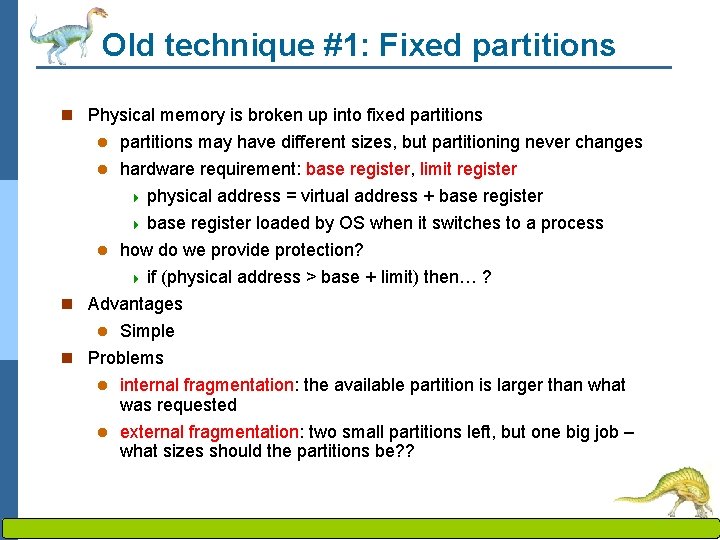

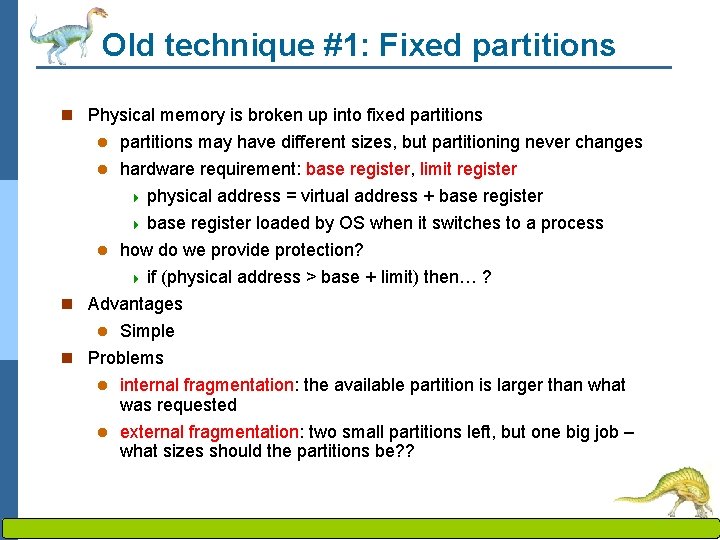

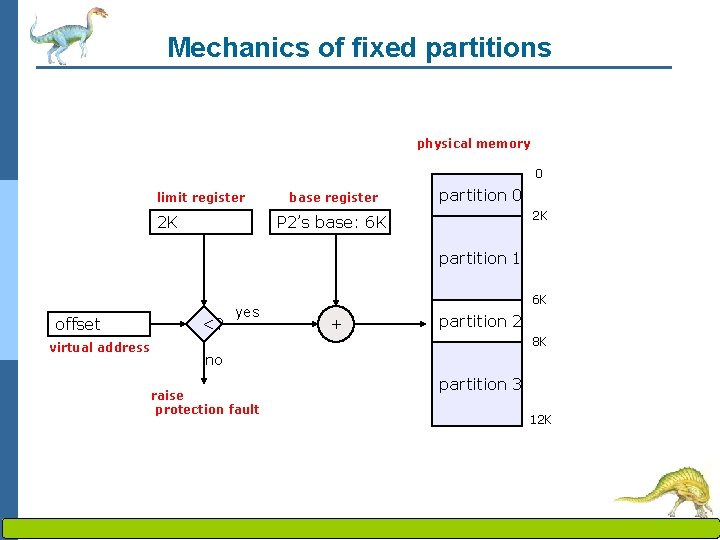

Old technique #1: Fixed partitions n Physical memory is broken up into fixed partitions may have different sizes, but partitioning never changes l hardware requirement: base register, limit register 4 physical address = virtual address + base register 4 base register loaded by OS when it switches to a process l how do we provide protection? 4 if (physical address > base + limit) then… ? n Advantages l Simple l n Problems internal fragmentation: the available partition is larger than what was requested l external fragmentation: two small partitions left, but one big job – what sizes should the partitions be? ? l Operating System Concepts – 8 th Edition 8. 15 Silberschatz, Galvin and Gagne © 2009

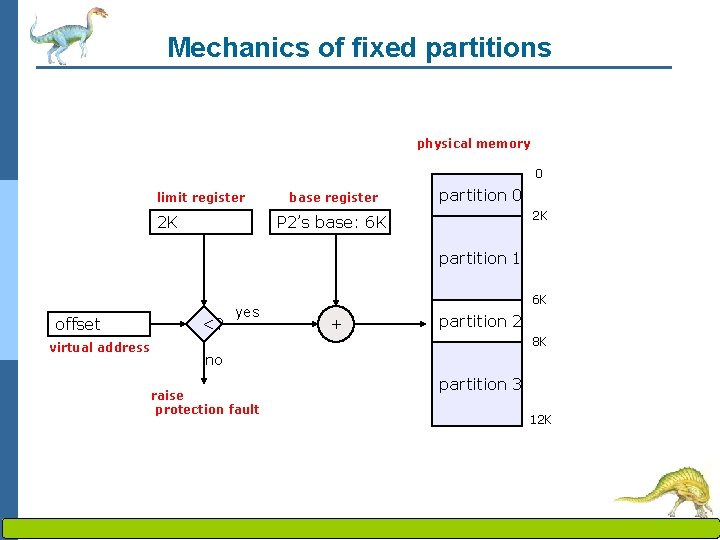

Mechanics of fixed partitions physical memory 0 limit register 2 K base register partition 0 2 K P 2’s base: 6 K partition 1 offset virtual address <? yes 6 K + partition 2 8 K no partition 3 raise protection fault Operating System Concepts – 8 th Edition 12 K 8. 16 Silberschatz, Galvin and Gagne © 2009

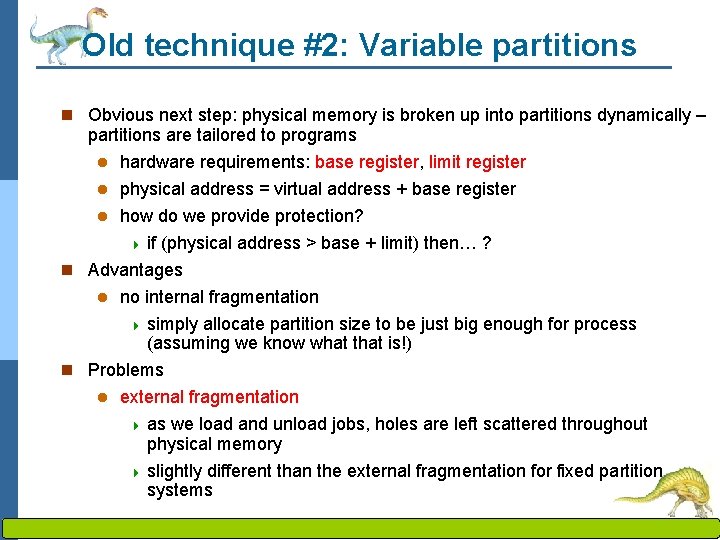

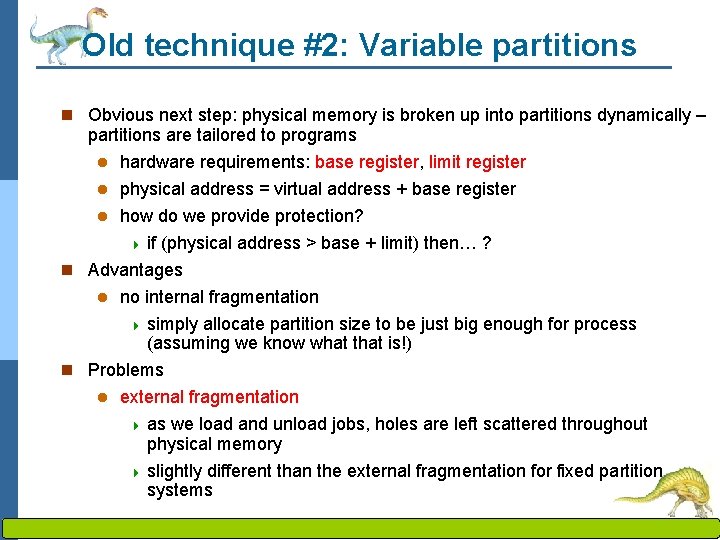

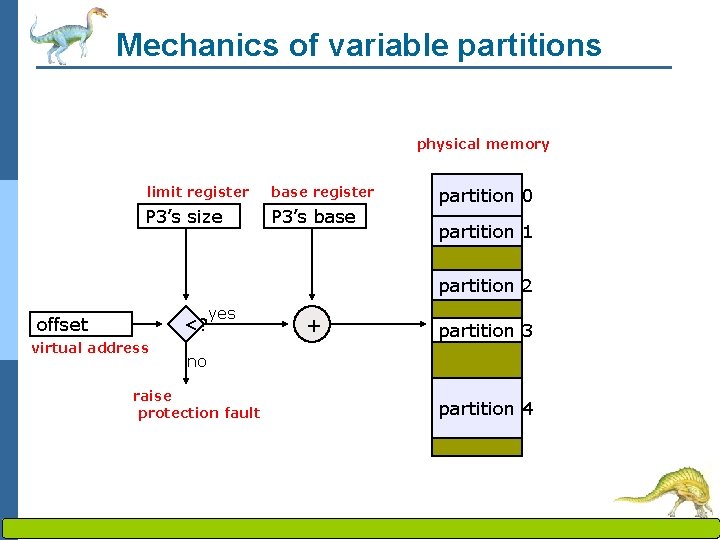

Old technique #2: Variable partitions n Obvious next step: physical memory is broken up into partitions dynamically – partitions are tailored to programs l hardware requirements: base register, limit register l physical address = virtual address + base register l how do we provide protection? 4 if (physical address > base + limit) then… ? n Advantages l no internal fragmentation 4 simply allocate partition size to be just big enough for process (assuming we know what that is!) n Problems l external fragmentation 4 as we load and unload jobs, holes are left scattered throughout physical memory 4 slightly different than the external fragmentation for fixed partition systems Operating System Concepts – 8 th Edition 8. 17 Silberschatz, Galvin and Gagne © 2009

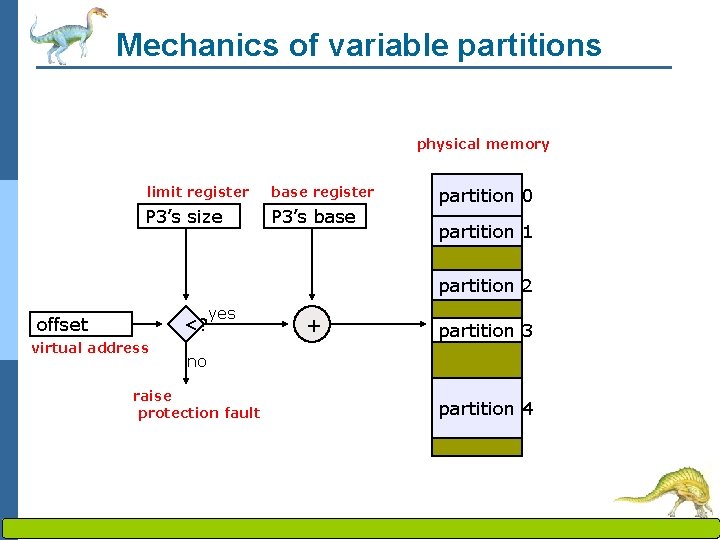

Mechanics of variable partitions physical memory limit register base register P 3’s size P 3’s base partition 0 partition 1 partition 2 yes offset <? virtual address + partition 3 no raise protection fault Operating System Concepts – 8 th Edition partition 4 8. 18 Silberschatz, Galvin and Gagne © 2009

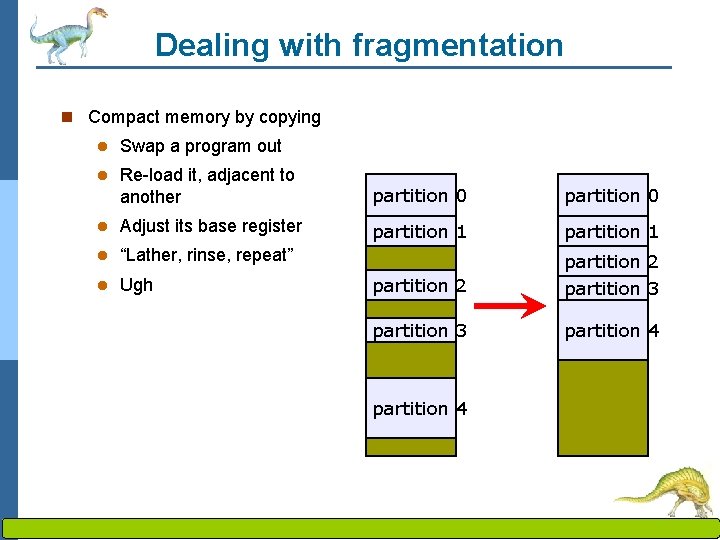

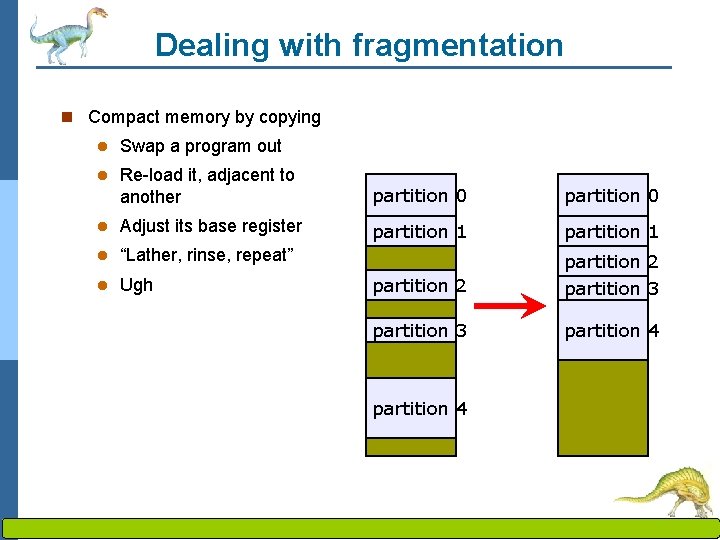

Dealing with fragmentation n Compact memory by copying l Swap a program out l Re-load it, adjacent to another partition 0 l Adjust its base register partition 1 l “Lather, rinse, repeat” l Ugh partition 2 partition 3 partition 4 Operating System Concepts – 8 th Edition 8. 19 Silberschatz, Galvin and Gagne © 2009

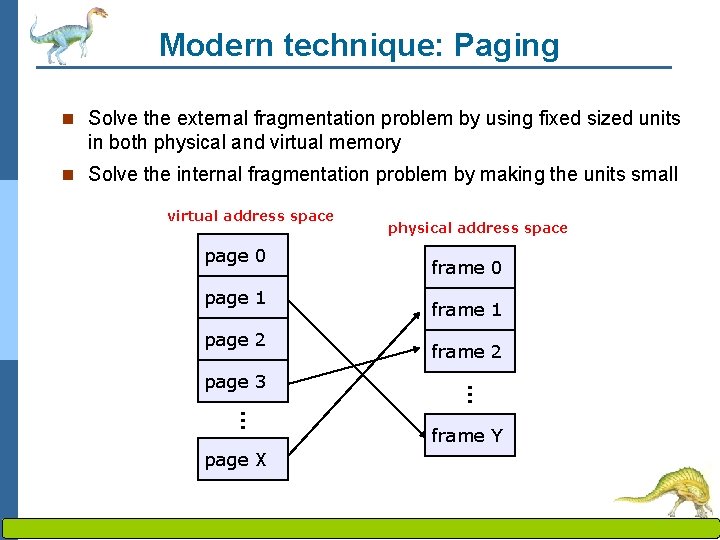

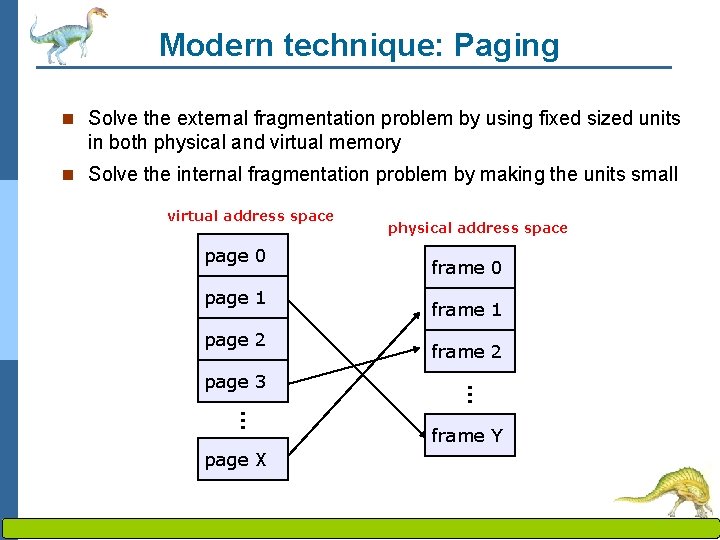

Modern technique: Paging n Solve the external fragmentation problem by using fixed sized units in both physical and virtual memory n Solve the internal fragmentation problem by making the units small virtual address space physical address space page 0 frame 0 page 1 frame 1 page 2 frame 2 … … page 3 frame Y page X Operating System Concepts – 8 th Edition 8. 20 Silberschatz, Galvin and Gagne © 2009

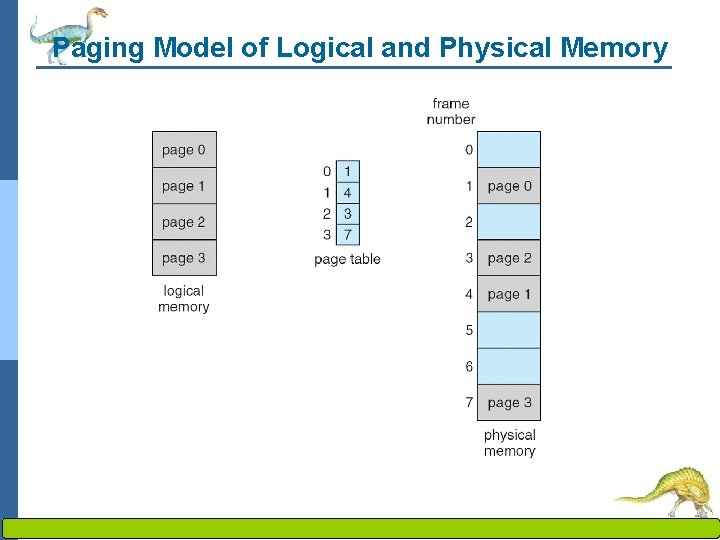

Paging n Logical address space of a process can be noncontiguous; process is allocated physical memory whenever the latter is available n Divide physical memory into fixed-sized blocks called frames (size is power of 2, between 512 bytes and 8, 192 bytes) n Divide logical memory into blocks of same size called pages n Set up a page table to translate logical to physical addresses n Internal fragmentation Operating System Concepts – 8 th Edition 8. 21 Silberschatz, Galvin and Gagne © 2009

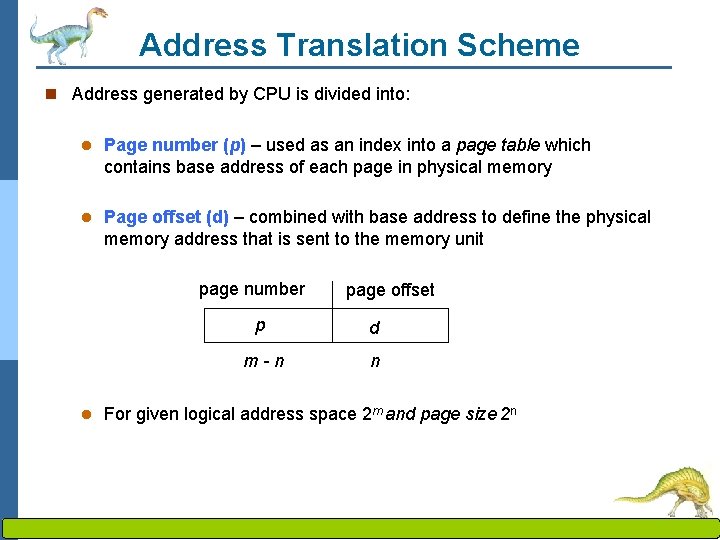

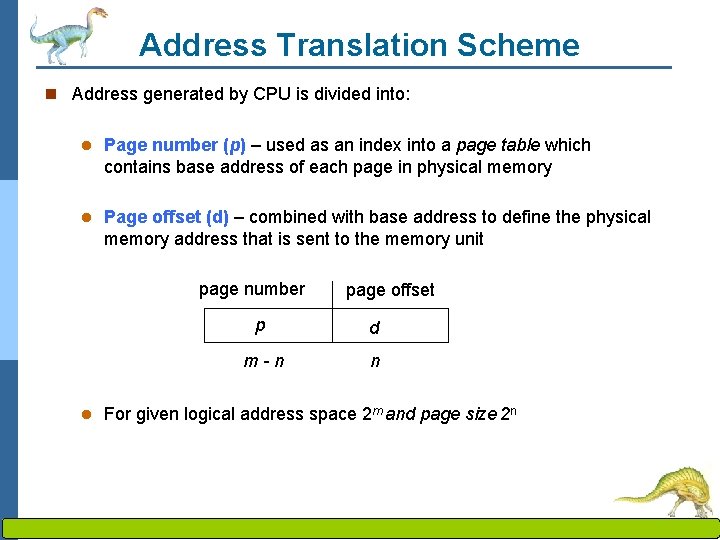

Address Translation Scheme n Address generated by CPU is divided into: l Page number (p) – used as an index into a page table which contains base address of each page in physical memory l Page offset (d) – combined with base address to define the physical memory address that is sent to the memory unit page number l page offset p d m-n n For given logical address space 2 m and page size 2 n Operating System Concepts – 8 th Edition 8. 22 Silberschatz, Galvin and Gagne © 2009

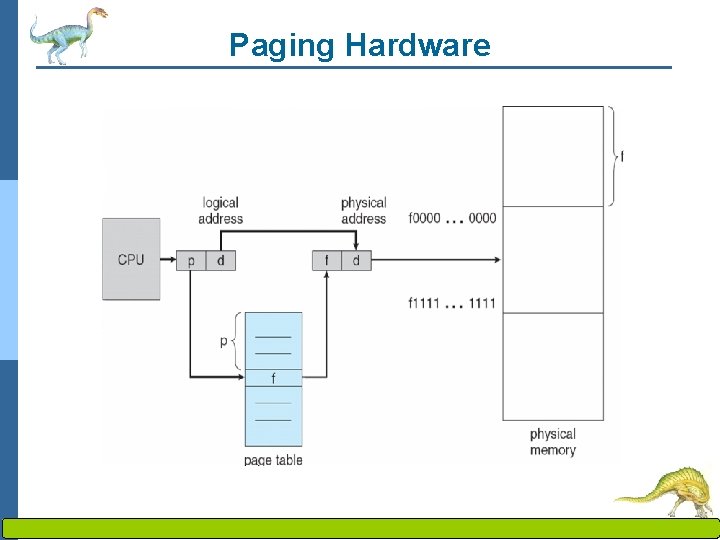

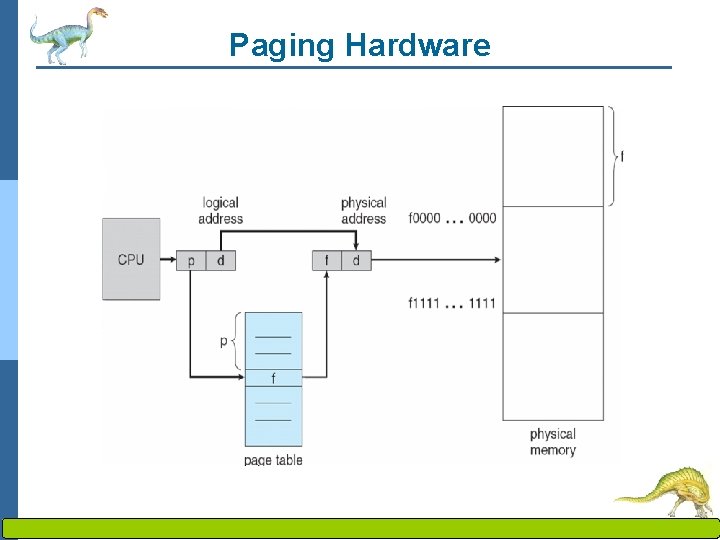

Paging Hardware Operating System Concepts – 8 th Edition 8. 23 Silberschatz, Galvin and Gagne © 2009

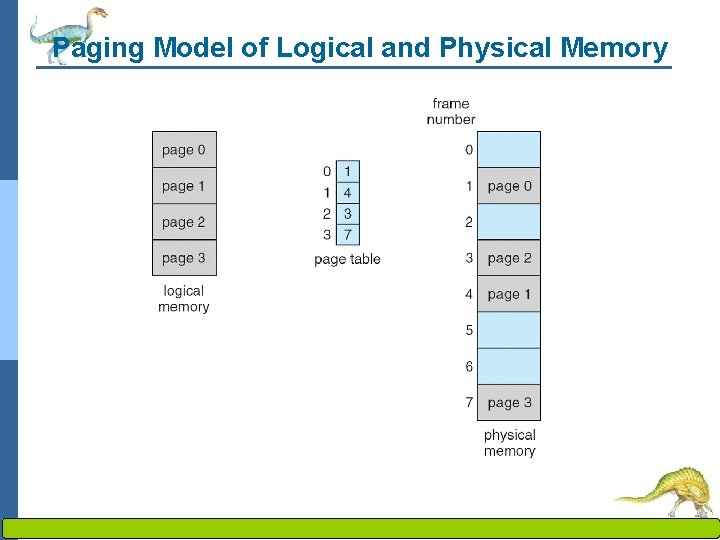

Paging Model of Logical and Physical Memory Operating System Concepts – 8 th Edition 8. 24 Silberschatz, Galvin and Gagne © 2009

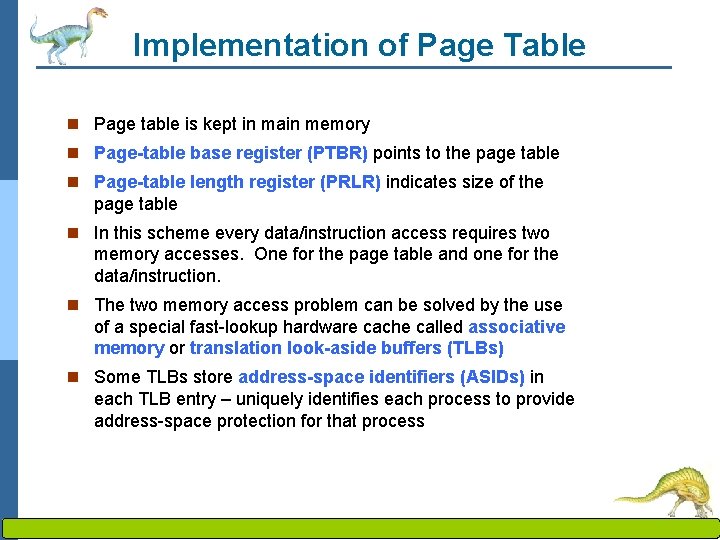

Implementation of Page Table n Page table is kept in main memory n Page-table base register (PTBR) points to the page table n Page-table length register (PRLR) indicates size of the page table n In this scheme every data/instruction access requires two memory accesses. One for the page table and one for the data/instruction. n The two memory access problem can be solved by the use of a special fast-lookup hardware cache called associative memory or translation look-aside buffers (TLBs) n Some TLBs store address-space identifiers (ASIDs) in each TLB entry – uniquely identifies each process to provide address-space protection for that process Operating System Concepts – 8 th Edition 8. 25 Silberschatz, Galvin and Gagne © 2009

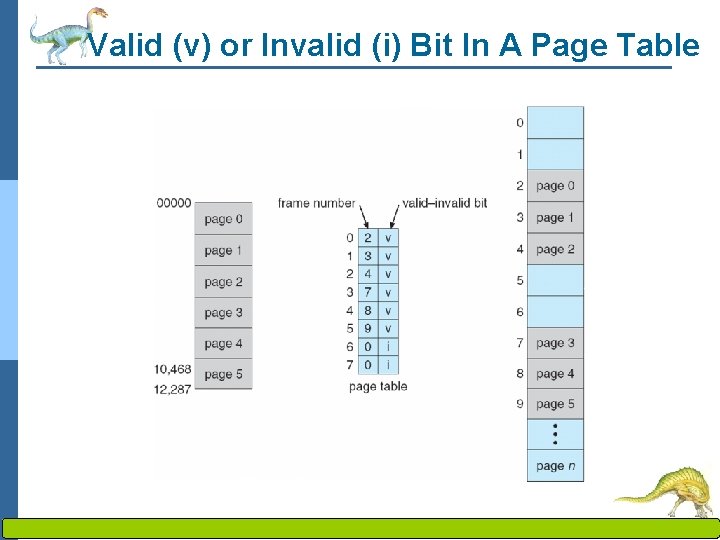

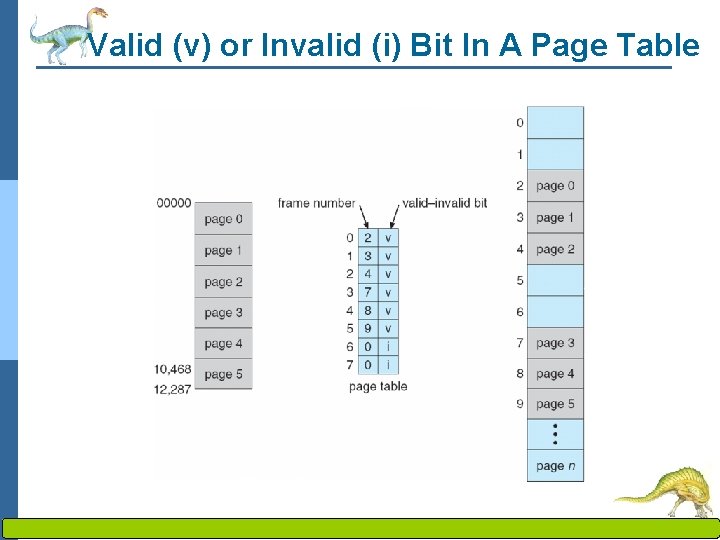

Memory Protection n Memory protection implemented by associating protection bit with each frame n Valid-invalid bit attached to each entry in the page table: l “valid” indicates that the associated page is in the process’ logical address space, and is thus a legal page l “invalid” indicates that the page is not in the process’ logical address space Operating System Concepts – 8 th Edition 8. 26 Silberschatz, Galvin and Gagne © 2009

Valid (v) or Invalid (i) Bit In A Page Table Operating System Concepts – 8 th Edition 8. 27 Silberschatz, Galvin and Gagne © 2009

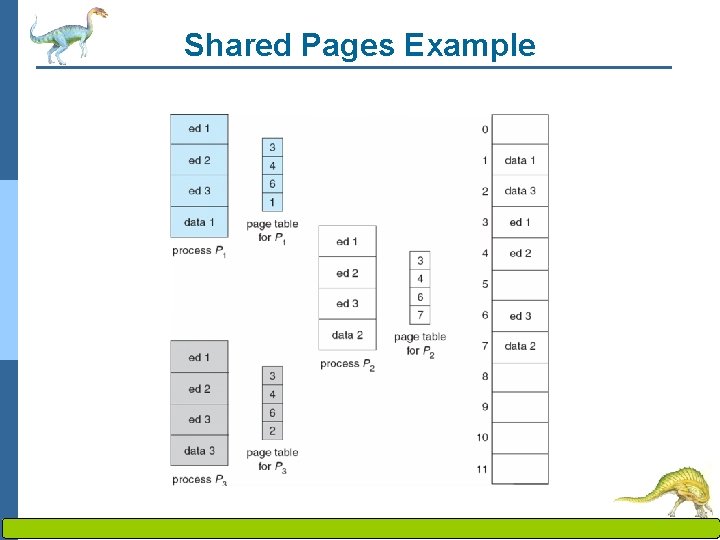

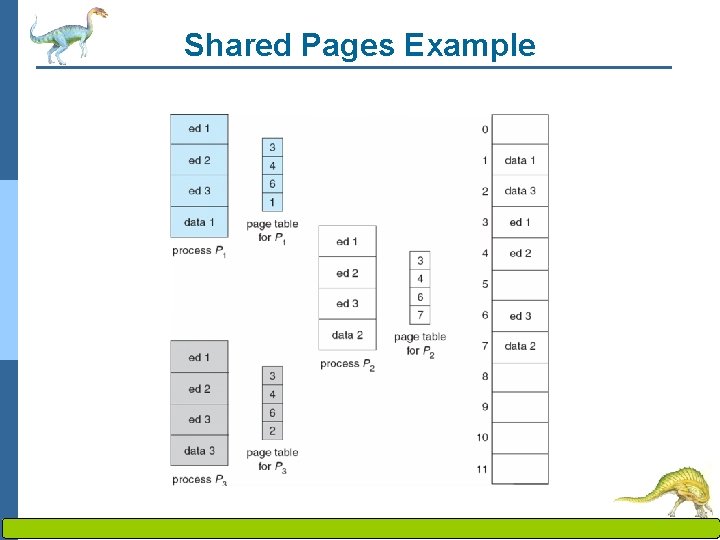

Shared Pages n Shared code l One copy of read-only (reentrant) code shared among processes (i. e. , text editors, compilers, window systems). l Shared code must appear in same location in the logical address space of all processes n Private code and data l Each process keeps a separate copy of the code and data l The pages for the private code and data can appear anywhere in the logical address space Operating System Concepts – 8 th Edition 8. 28 Silberschatz, Galvin and Gagne © 2009

Shared Pages Example Operating System Concepts – 8 th Edition 8. 29 Silberschatz, Galvin and Gagne © 2009

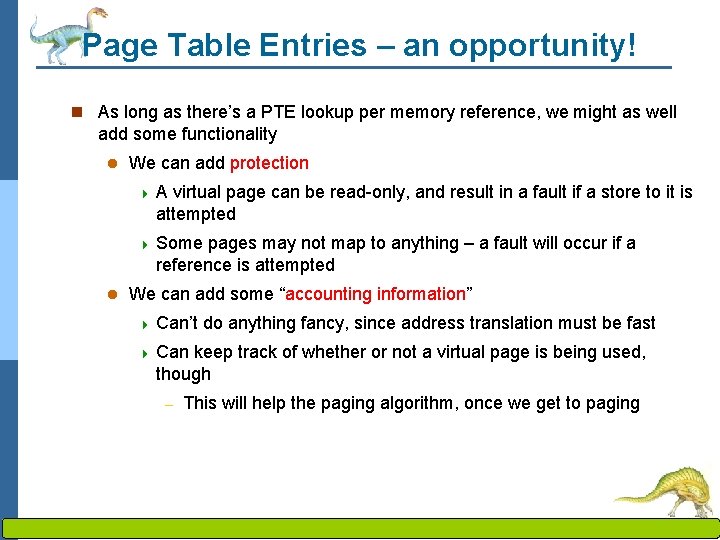

Page Table Entries – an opportunity! n As long as there’s a PTE lookup per memory reference, we might as well add some functionality l We can add protection 4 A virtual page can be read-only, and result in a fault if a store to it is attempted 4 Some pages may not map to anything – a fault will occur if a reference is attempted l We can add some “accounting information” 4 Can’t do anything fancy, since address translation must be fast 4 Can keep track of whether or not a virtual page is being used, though – This will help the paging algorithm, once we get to paging Operating System Concepts – 8 th Edition 8. 30 Silberschatz, Galvin and Gagne © 2009

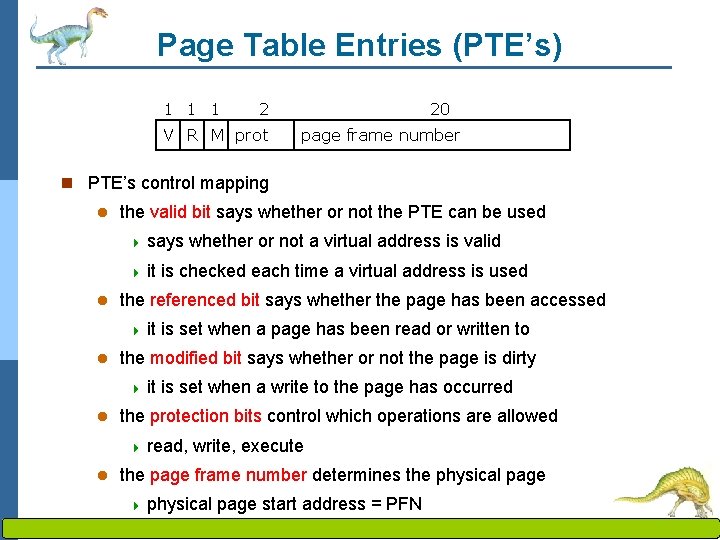

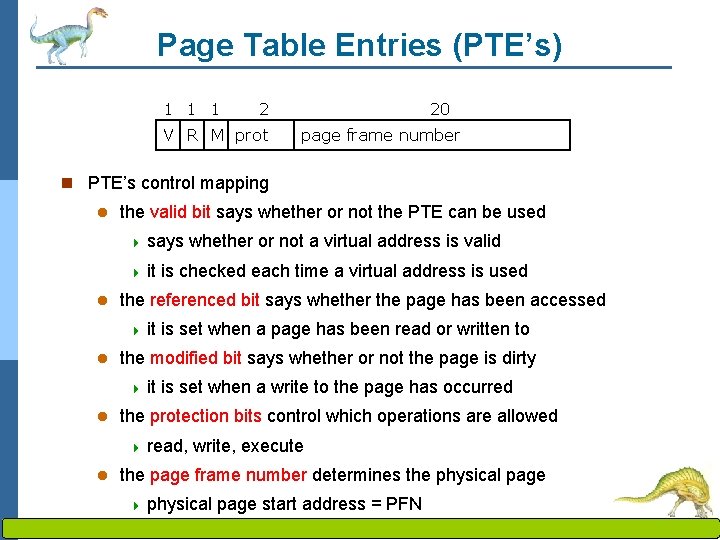

Page Table Entries (PTE’s) 1 1 1 2 V R M prot 20 page frame number n PTE’s control mapping l the valid bit says whether or not the PTE can be used 4 says 4 it l is set when a page has been read or written to the modified bit says whether or not the page is dirty 4 it l is checked each time a virtual address is used the referenced bit says whether the page has been accessed 4 it l is set when a write to the page has occurred the protection bits control which operations are allowed 4 read, l whether or not a virtual address is valid write, execute the page frame number determines the physical page 4 physical Operating System Concepts – 8 th Edition page start address = PFN 8. 31 Silberschatz, Galvin and Gagne © 2009

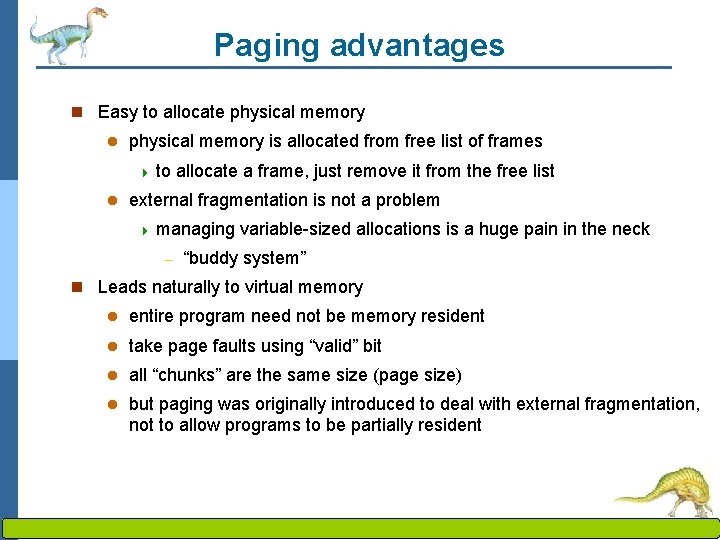

Paging advantages n Easy to allocate physical memory l physical memory is allocated from free list of frames 4 to l allocate a frame, just remove it from the free list external fragmentation is not a problem 4 managing – variable-sized allocations is a huge pain in the neck “buddy system” n Leads naturally to virtual memory l entire program need not be memory resident l take page faults using “valid” bit l all “chunks” are the same size (page size) l but paging was originally introduced to deal with external fragmentation, not to allow programs to be partially resident Operating System Concepts – 8 th Edition 8. 32 Silberschatz, Galvin and Gagne © 2009

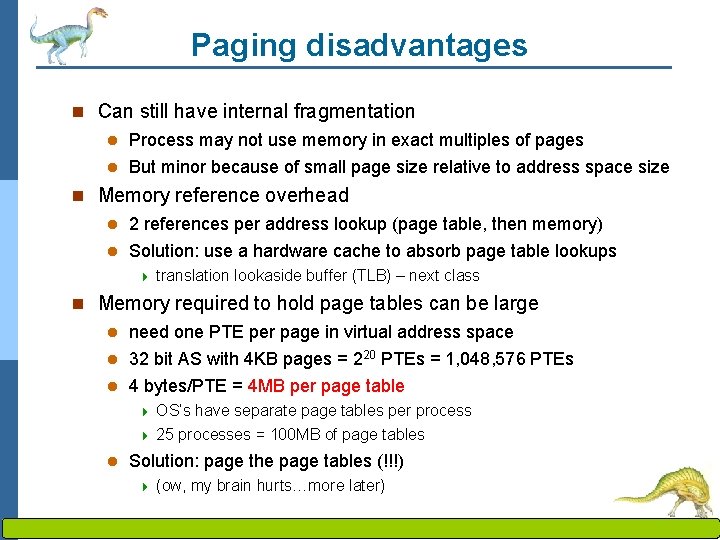

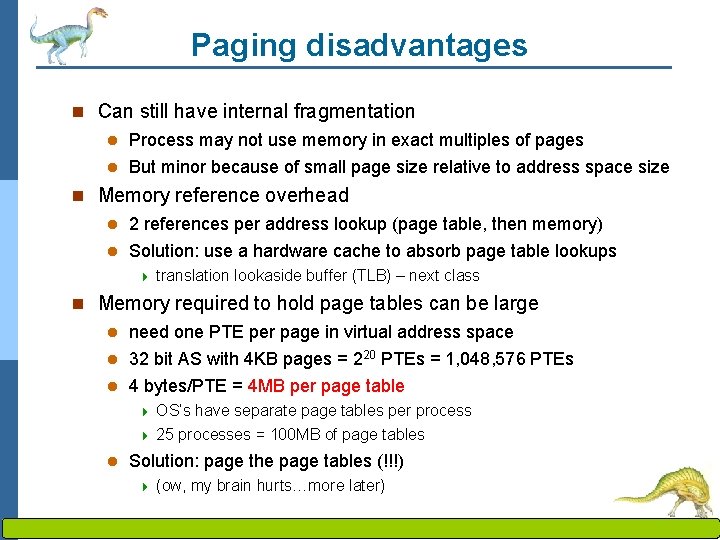

Paging disadvantages n Can still have internal fragmentation l Process may not use memory in exact multiples of pages l But minor because of small page size relative to address space size n Memory reference overhead l 2 references per address lookup (page table, then memory) l Solution: use a hardware cache to absorb page table lookups 4 translation lookaside buffer (TLB) – next class n Memory required to hold page tables can be large l need one PTE per page in virtual address space l 32 bit AS with 4 KB pages = 220 PTEs = 1, 048, 576 PTEs l 4 bytes/PTE = 4 MB per page table 4 4 l OS’s have separate page tables per process 25 processes = 100 MB of page tables Solution: page the page tables (!!!) 4 (ow, my brain hurts…more later) Operating System Concepts – 8 th Edition 8. 33 Silberschatz, Galvin and Gagne © 2009

Segmentation n Memory-management scheme that supports user view of memory n A program is a collection of segments l A segment is a logical unit such as: main program procedure function method object local variables, global variables common block stack symbol table arrays Operating System Concepts – 8 th Edition 8. 34 Silberschatz, Galvin and Gagne © 2009

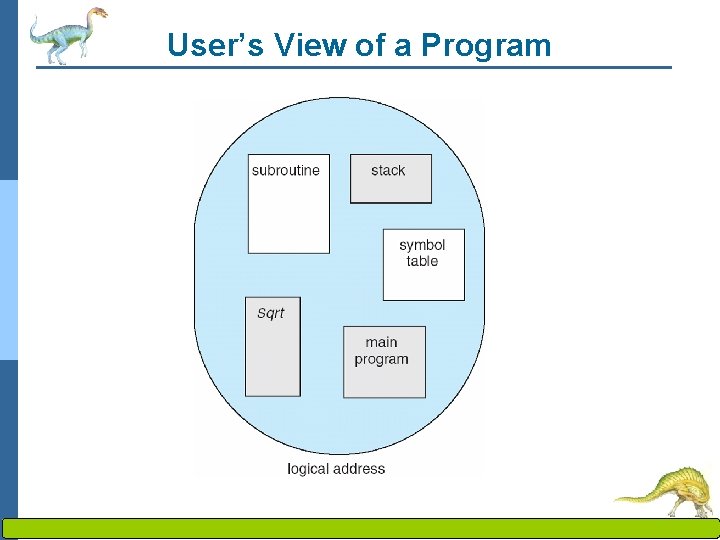

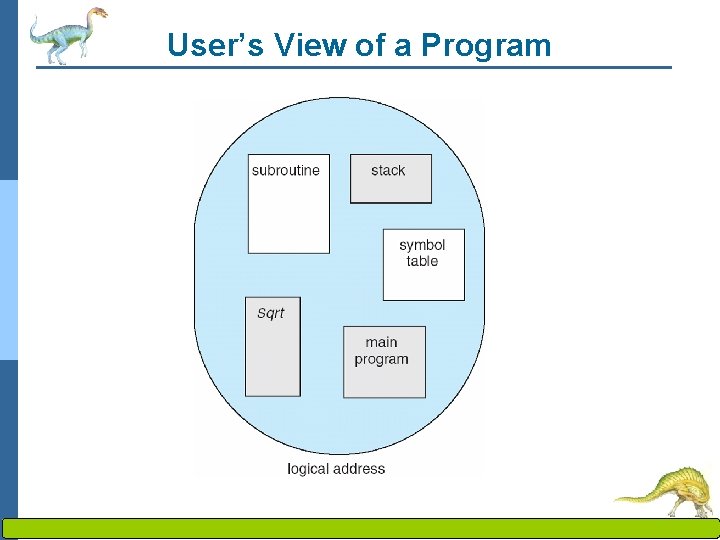

User’s View of a Program Operating System Concepts – 8 th Edition 8. 35 Silberschatz, Galvin and Gagne © 2009

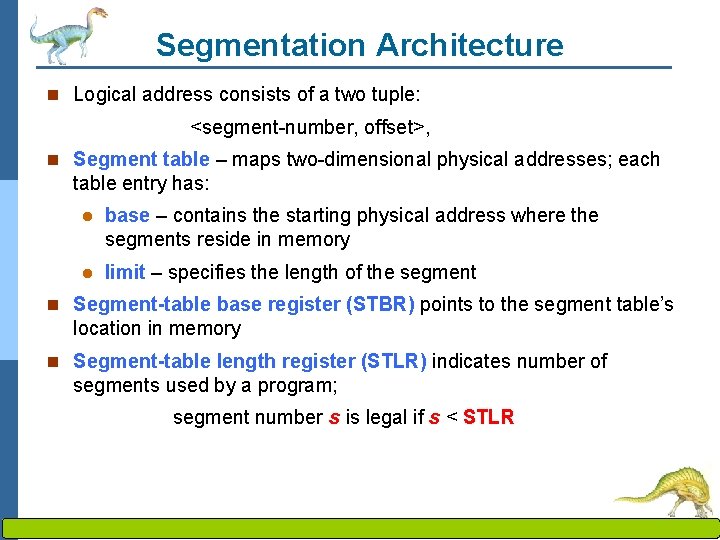

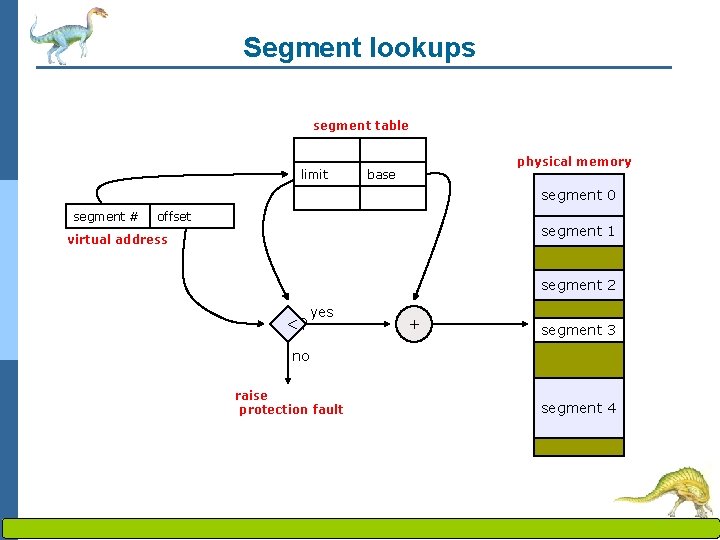

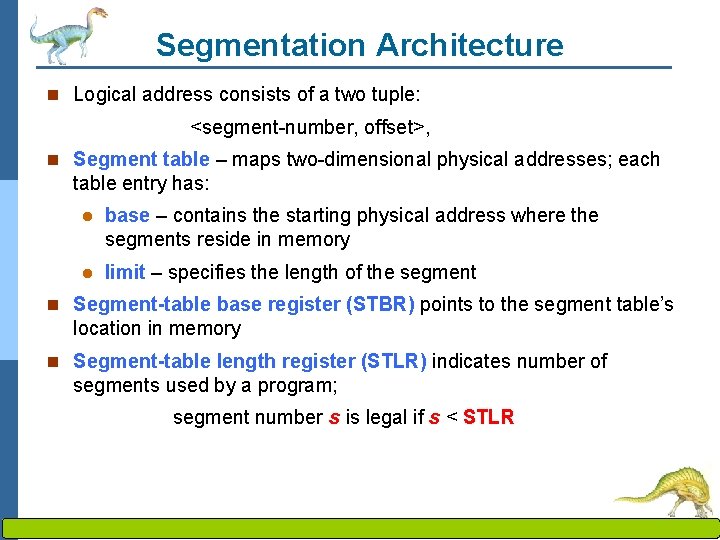

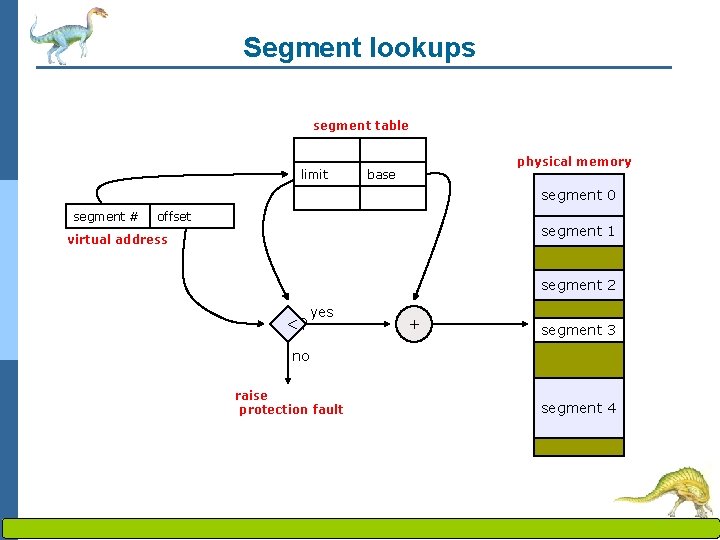

Segmentation Architecture n Logical address consists of a two tuple: <segment-number, offset>, n Segment table – maps two-dimensional physical addresses; each table entry has: l base – contains the starting physical address where the segments reside in memory l limit – specifies the length of the segment n Segment-table base register (STBR) points to the segment table’s location in memory n Segment-table length register (STLR) indicates number of segments used by a program; segment number s is legal if s < STLR Operating System Concepts – 8 th Edition 8. 36 Silberschatz, Galvin and Gagne © 2009

Segment lookups segment table limit physical memory base segment 0 segment # offset segment 1 virtual address segment 2 <? yes + segment 3 no raise protection fault Operating System Concepts – 8 th Edition 8. 37 segment 4 Silberschatz, Galvin and Gagne © 2009

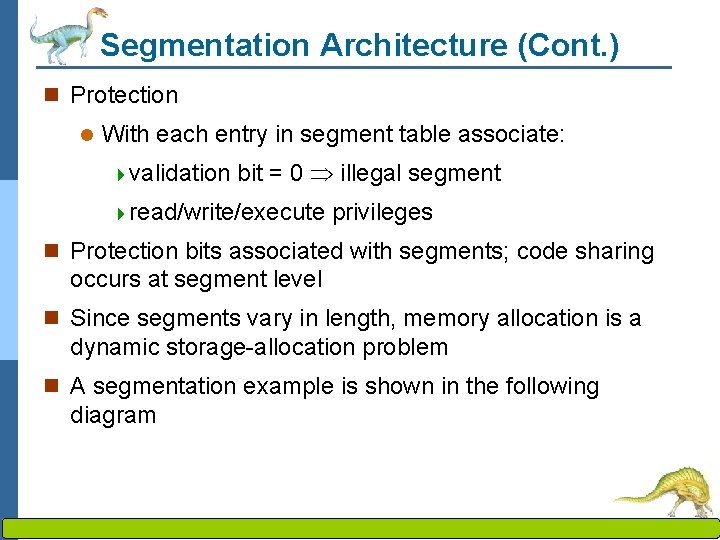

Segmentation Architecture (Cont. ) n Protection l With each entry in segment table associate: 4 validation bit = 0 illegal segment 4 read/write/execute privileges n Protection bits associated with segments; code sharing occurs at segment level n Since segments vary in length, memory allocation is a dynamic storage-allocation problem n A segmentation example is shown in the following diagram Operating System Concepts – 8 th Edition 8. 38 Silberschatz, Galvin and Gagne © 2009

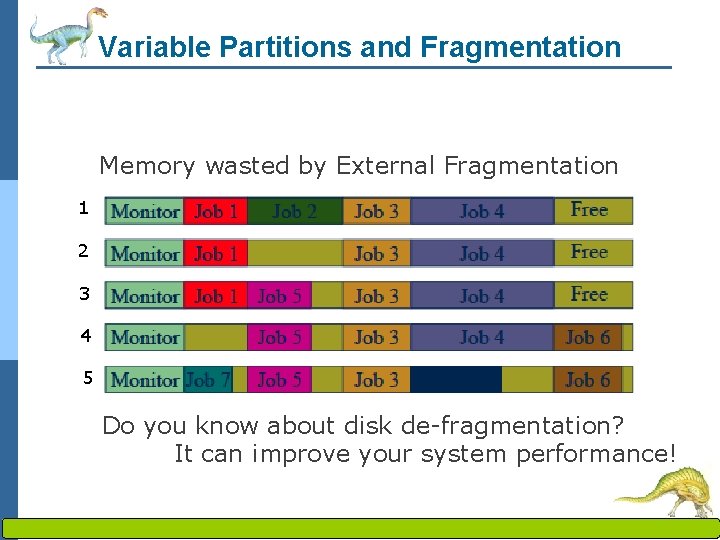

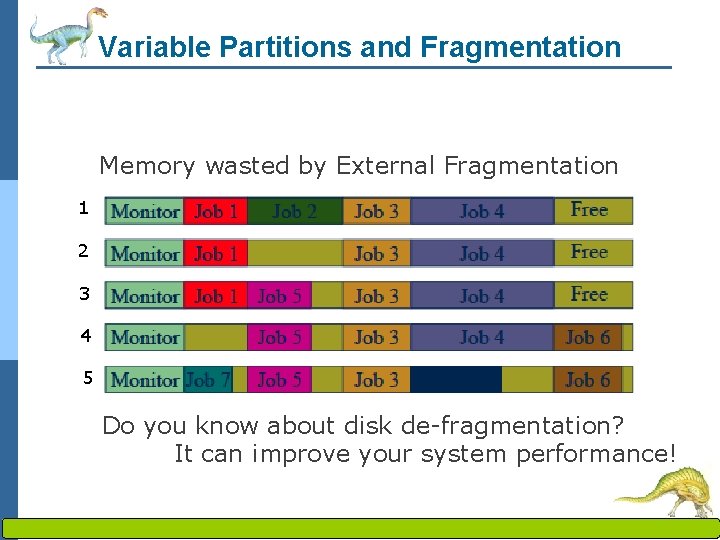

Variable Partitions and Fragmentation Memory wasted by External Fragmentation 1 2 3 4 5 Do you know about disk de-fragmentation? It can improve your system performance! Operating System Concepts – 8 th Edition 8. 39 Silberschatz, Galvin and Gagne © 2009

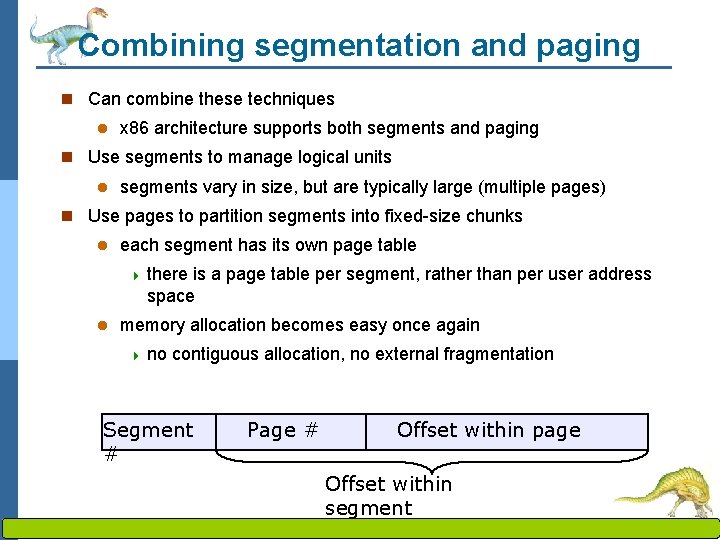

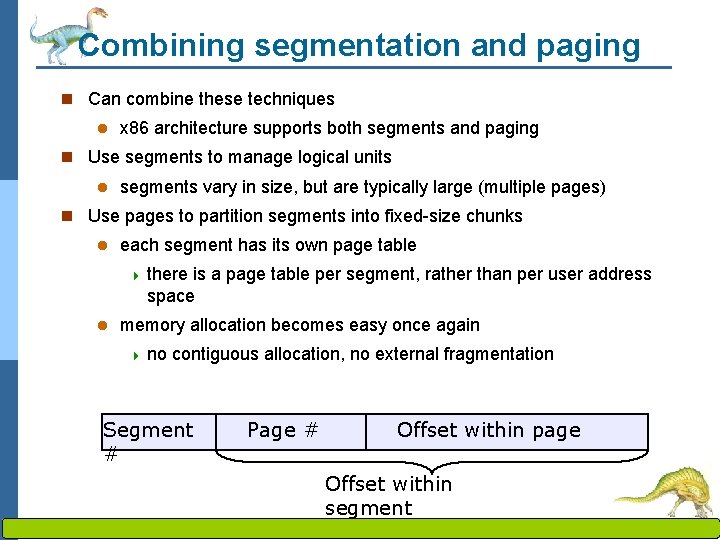

Combining segmentation and paging n Can combine these techniques l x 86 architecture supports both segments and paging n Use segments to manage logical units l segments vary in size, but are typically large (multiple pages) n Use pages to partition segments into fixed-size chunks l each segment has its own page table 4 there is a page table per segment, rather than per user address space l memory allocation becomes easy once again 4 no contiguous allocation, no external fragmentation Segment # Page # Offset within page Offset within segment Operating System Concepts – 8 th Edition 8. 40 Silberschatz, Galvin and Gagne © 2009

n Linux: l 1 kernel code segment, 1 kernel data segment l 1 user code segment, 1 user data segment l all of these segments are paged n Note: this is a very limited/boring use of segments! Operating System Concepts – 8 th Edition 8. 41 Silberschatz, Galvin and Gagne © 2009

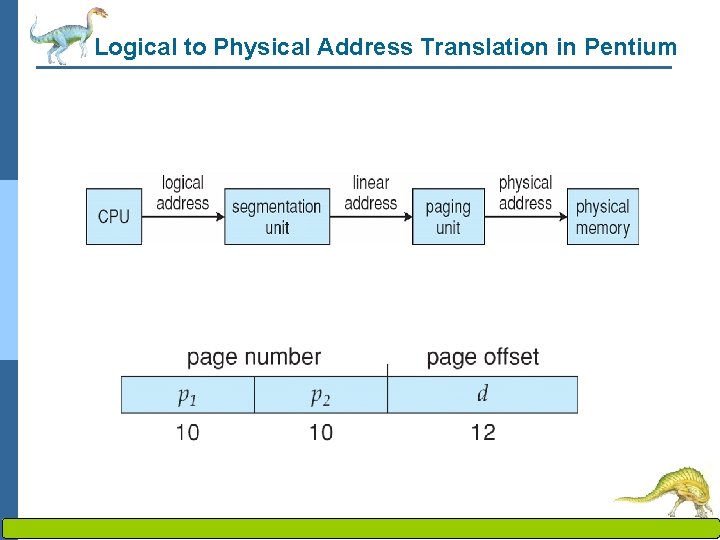

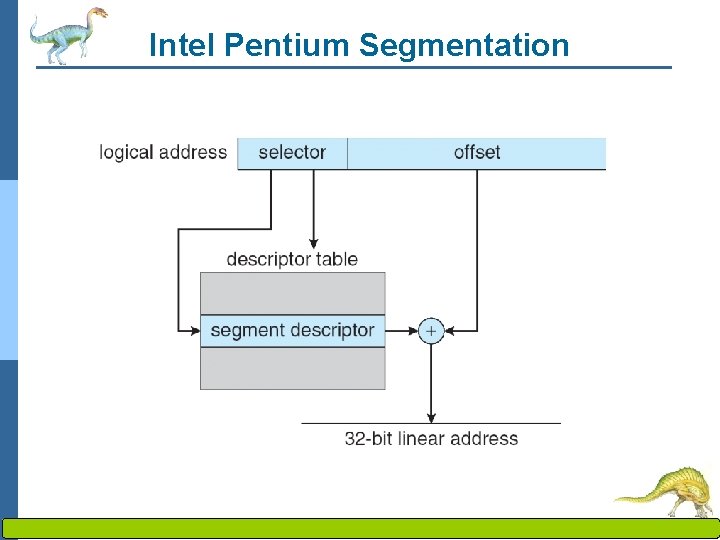

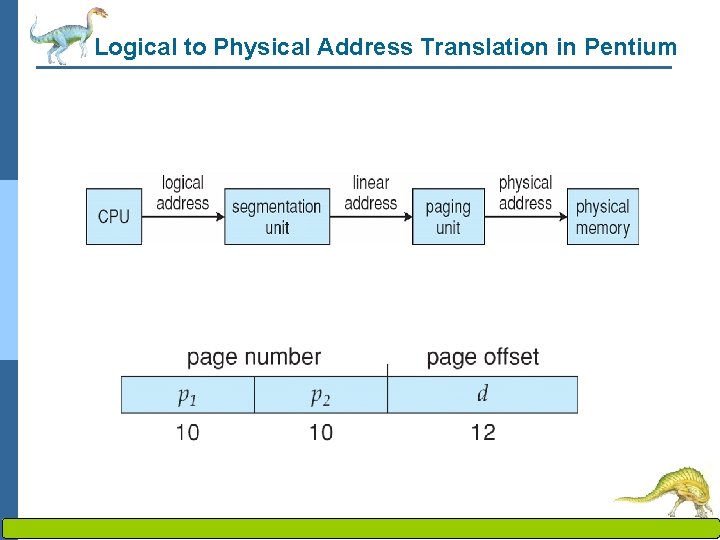

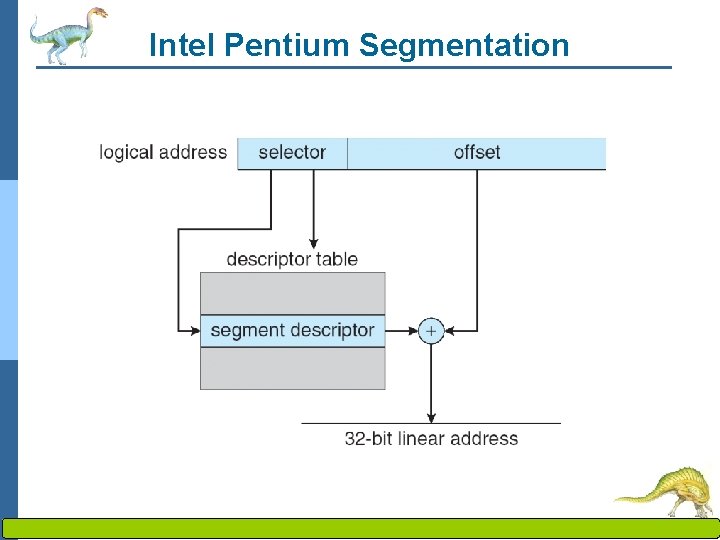

Example: The Intel Pentium n Supports both segmentation and segmentation with paging n CPU generates logical address l Given to segmentation unit 4 Which l Linear produces linear addresses address given to paging unit 4 Which generates physical address in main memory 4 Paging Operating System Concepts – 8 th Edition units form equivalent of MMU 8. 42 Silberschatz, Galvin and Gagne © 2009

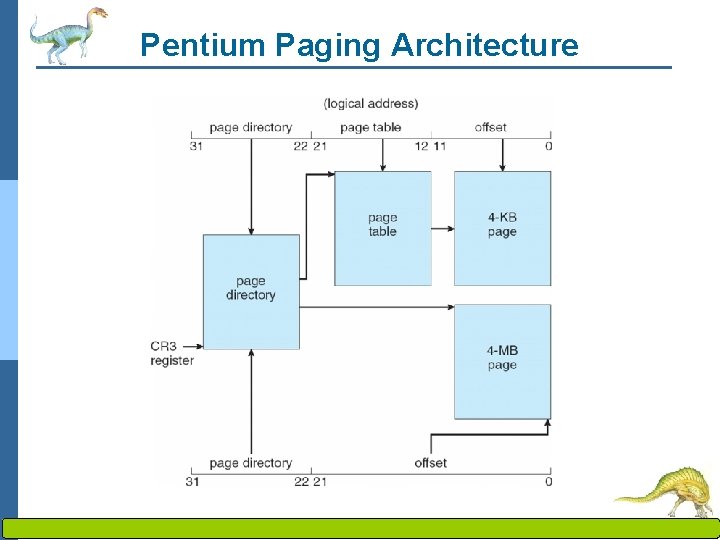

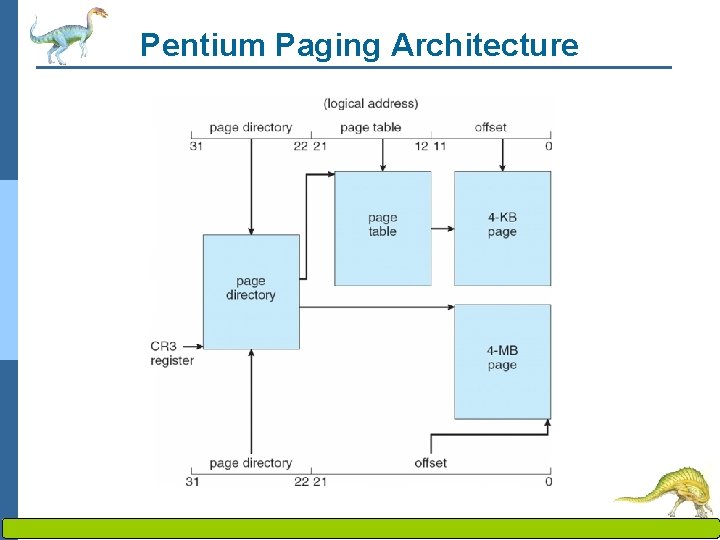

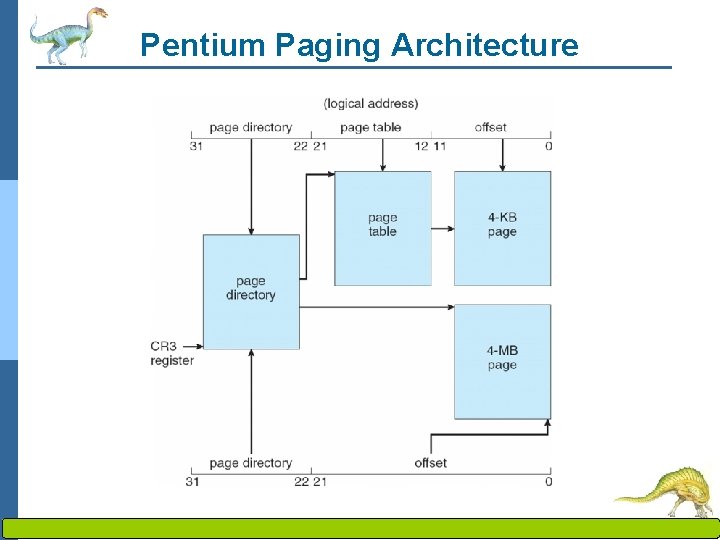

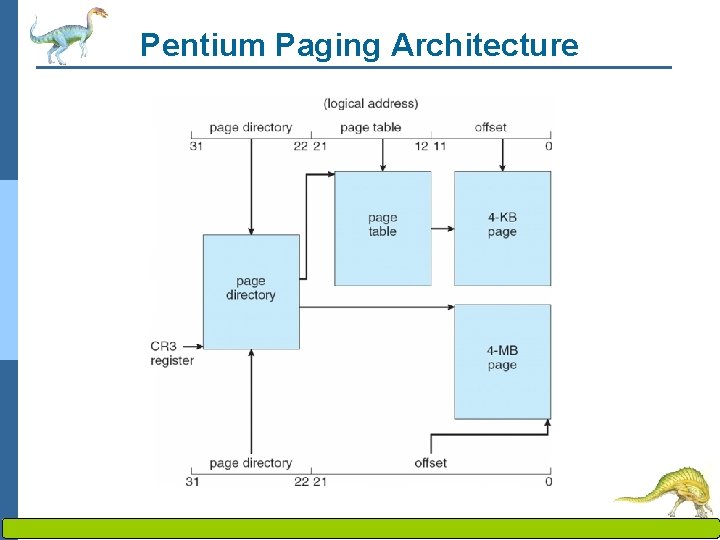

Pentium Paging Architecture Operating System Concepts – 8 th Edition 8. 43 Silberschatz, Galvin and Gagne © 2009

Logical to Physical Address Translation in Pentium Operating System Concepts – 8 th Edition 8. 44 Silberschatz, Galvin and Gagne © 2009

Intel Pentium Segmentation Operating System Concepts – 8 th Edition 8. 45 Silberschatz, Galvin and Gagne © 2009

Pentium Paging Architecture Operating System Concepts – 8 th Edition 8. 46 Silberschatz, Galvin and Gagne © 2009

Locality n Locality is a fundamental property of computer systems. n Spatial locality: l Near by memory addresses are often accessed together. n Temporal locality: l Memory that is accessed now is likely to be accessed again in the near future. Operating System Concepts – 8 th Edition 8. 47 Silberschatz, Galvin and Gagne © 2009