Chapter 5 Register Transfer Languages Images courtesy of

- Slides: 51

Chapter 5 Register Transfer Languages Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

Chapter Outline • • • Micro-operations RTL specifications Realizing RTL specifications VHDL Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

Micro-operations • Specify data transfer • Do not specify conditions under which transfers occur • Do not specify hardware implementation Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

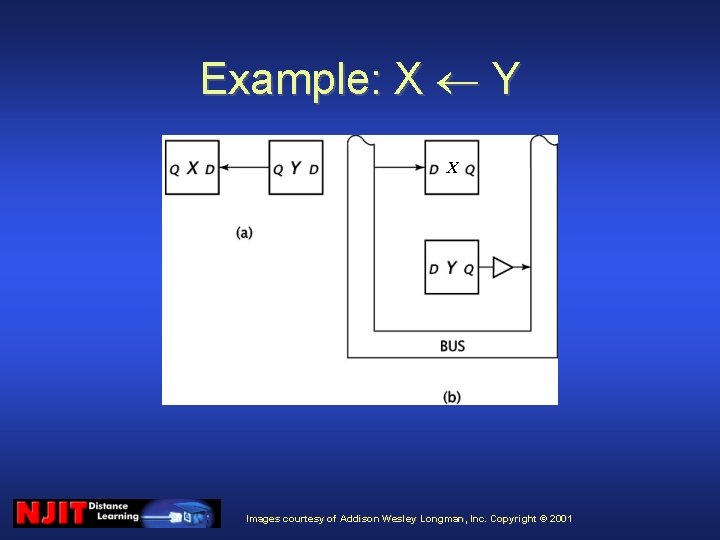

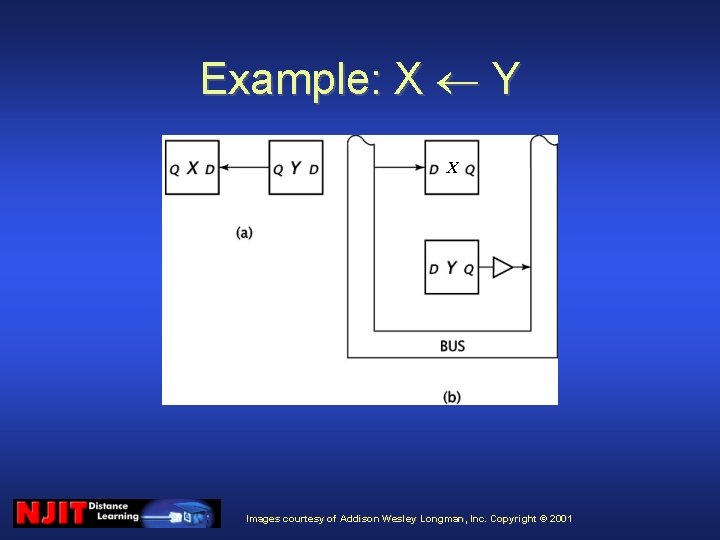

Example: X Y X Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

Register Transfer Language • Specify micro-operations and when they occur • Format: conditions: micro-operations Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

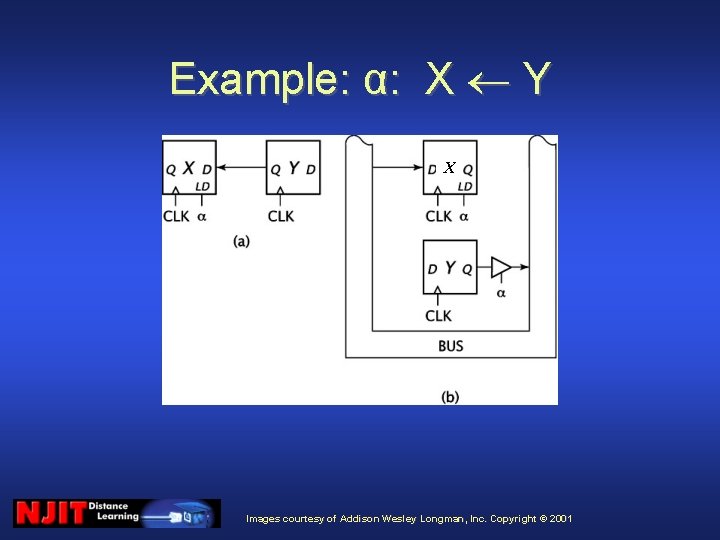

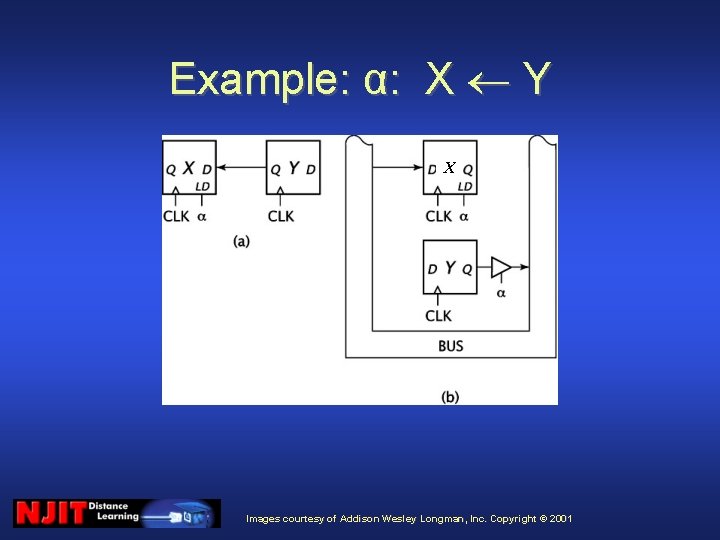

Example: α: X Y X Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

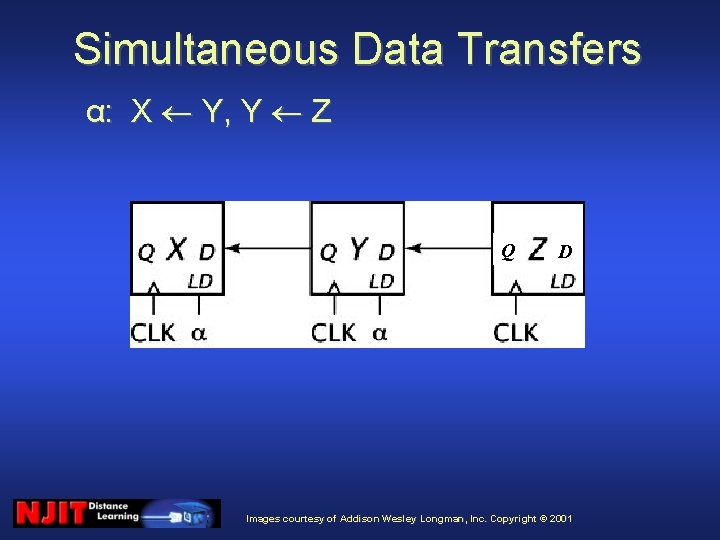

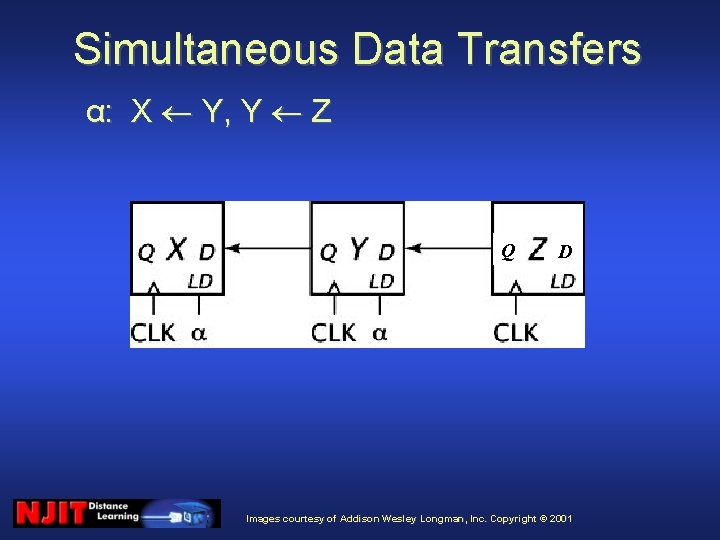

Simultaneous Data Transfers α: X Y, Y Z Q D Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

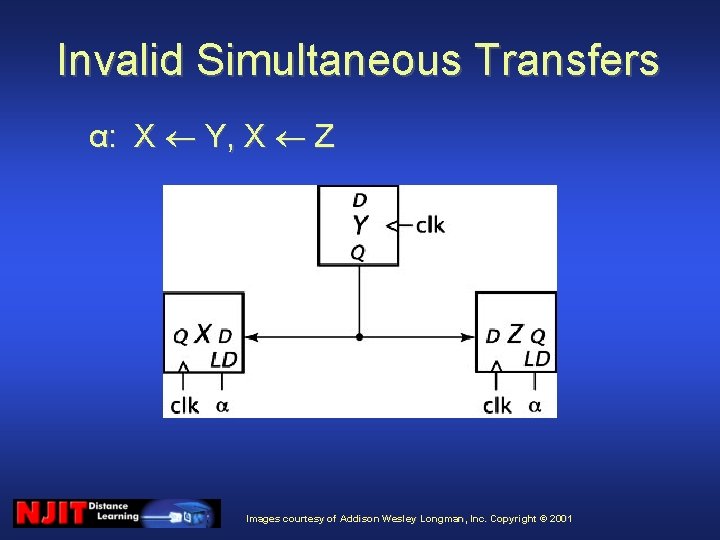

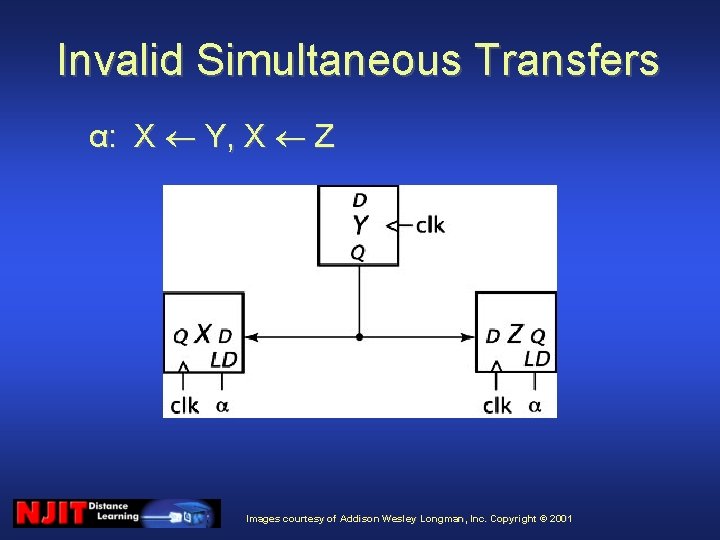

Invalid Simultaneous Transfers α: X Y, X Z Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

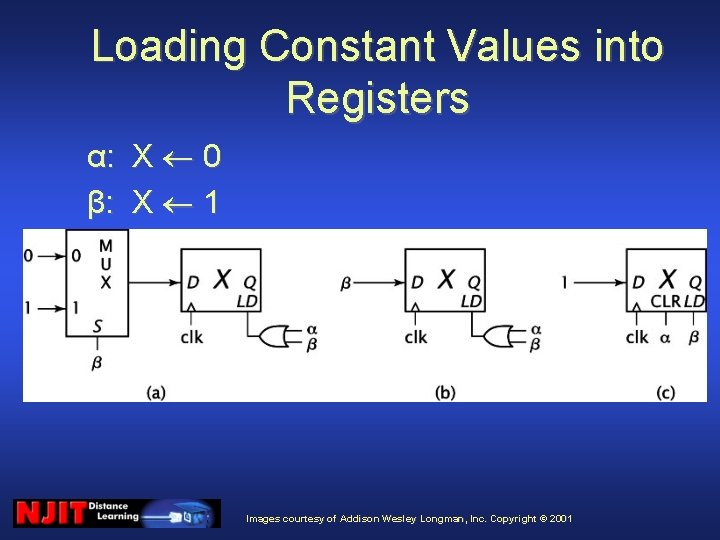

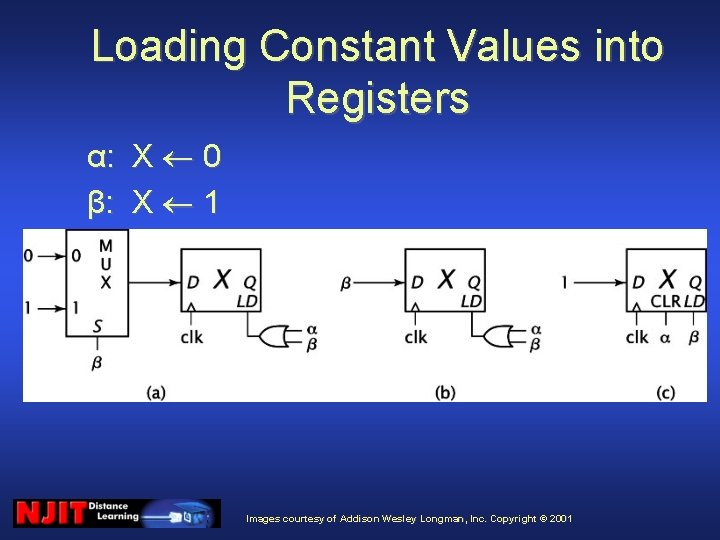

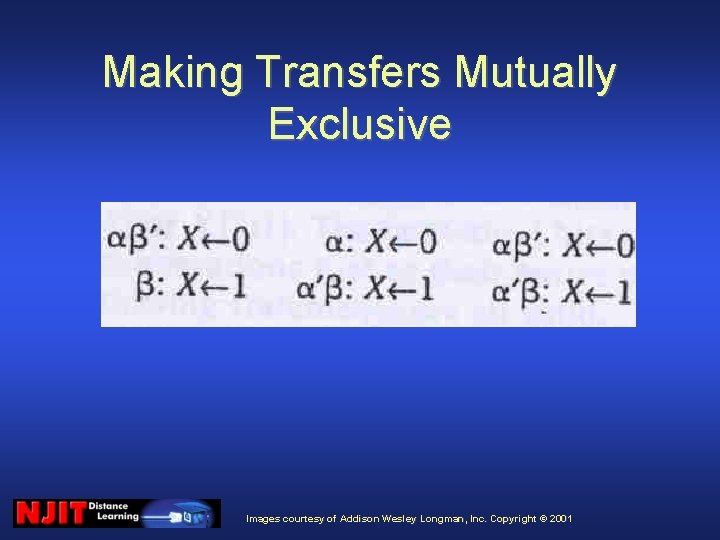

Loading Constant Values into Registers α: X 0 β: X 1 Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

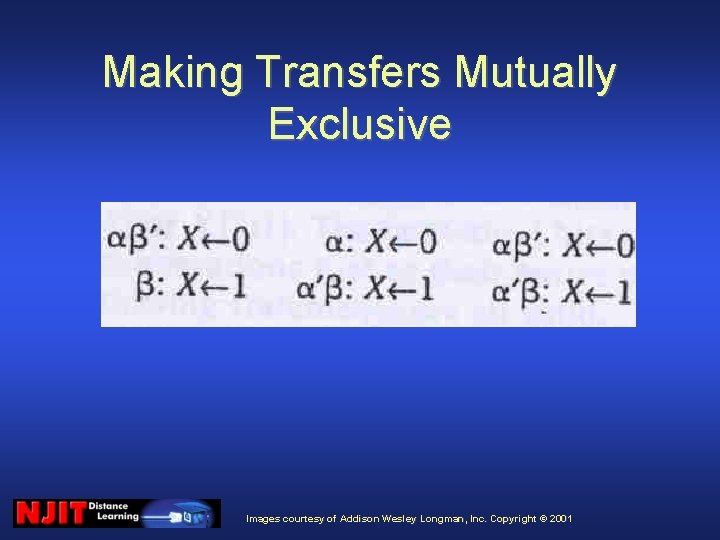

Making Transfers Mutually Exclusive Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

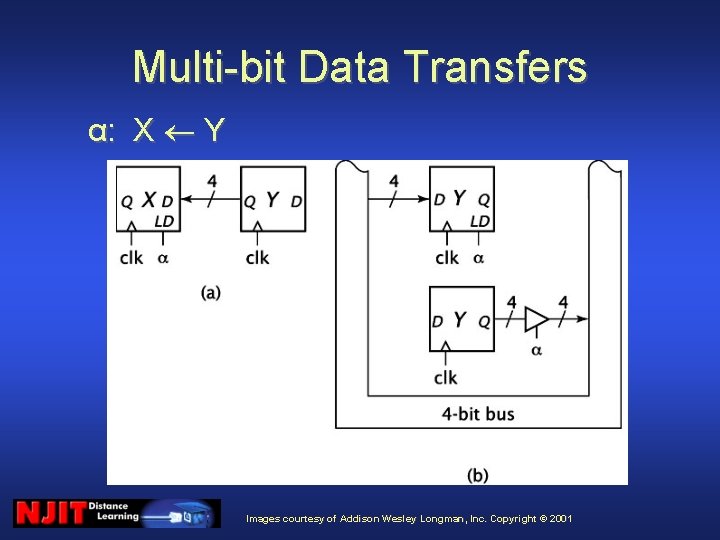

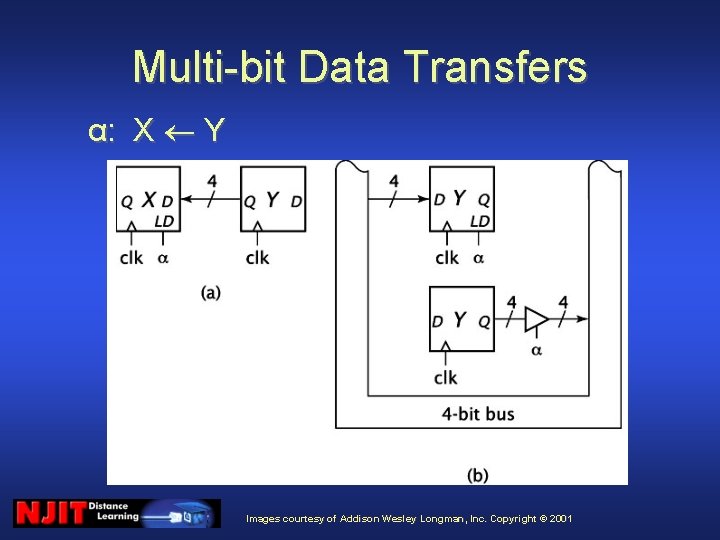

Multi-bit Data Transfers α: X Y Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

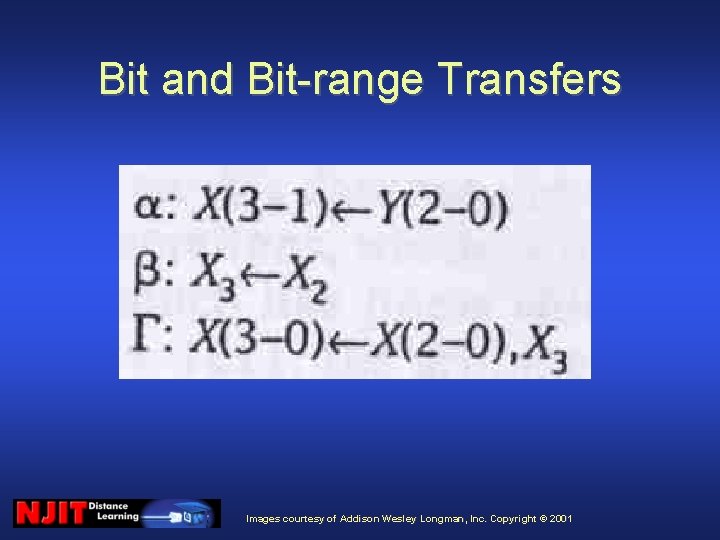

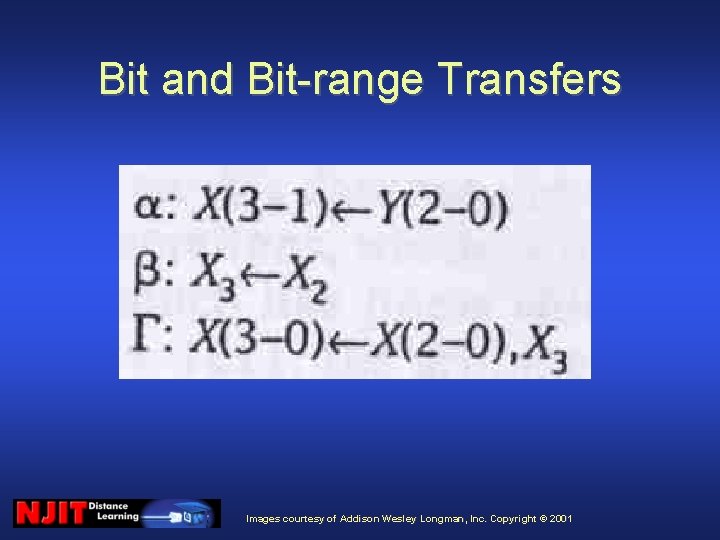

Bit and Bit-range Transfers Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

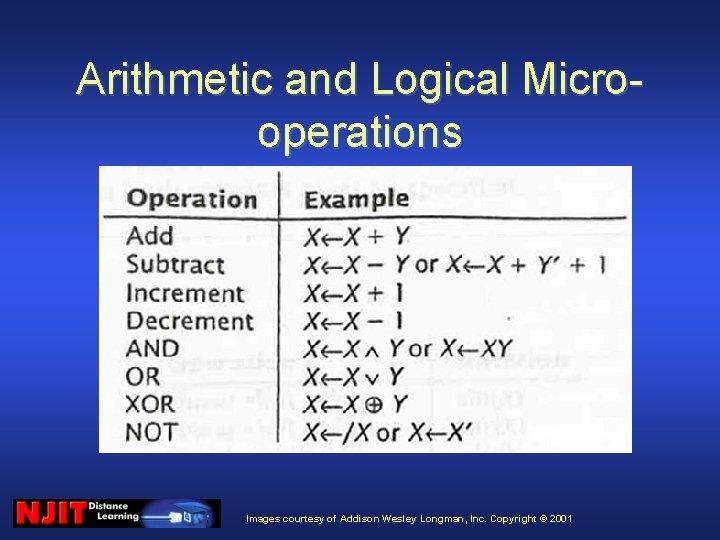

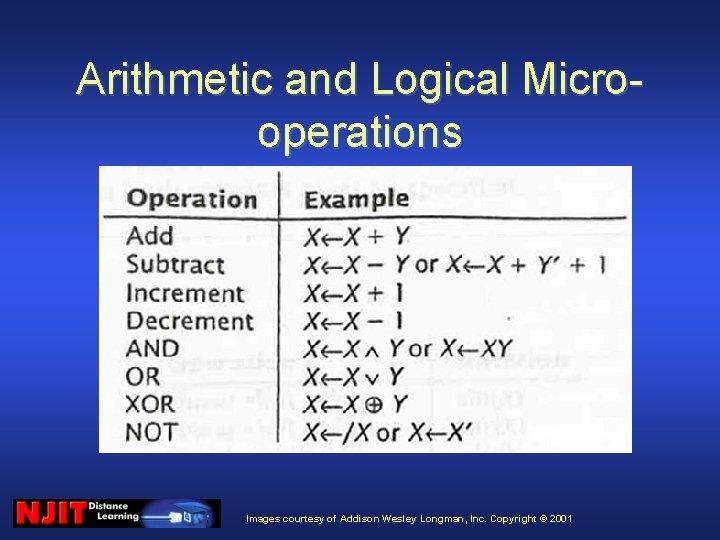

Arithmetic and Logical Microoperations Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

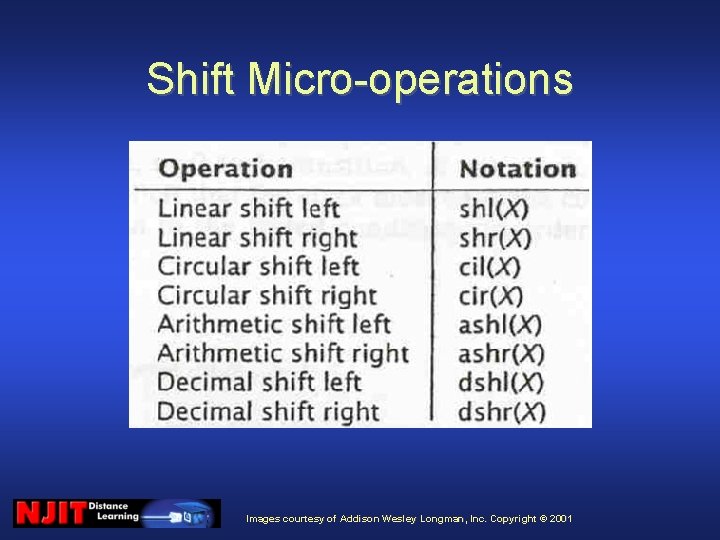

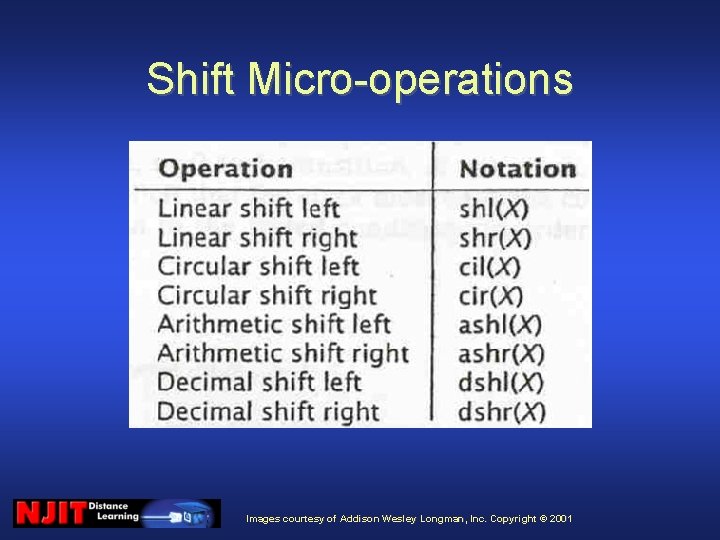

Shift Micro-operations Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

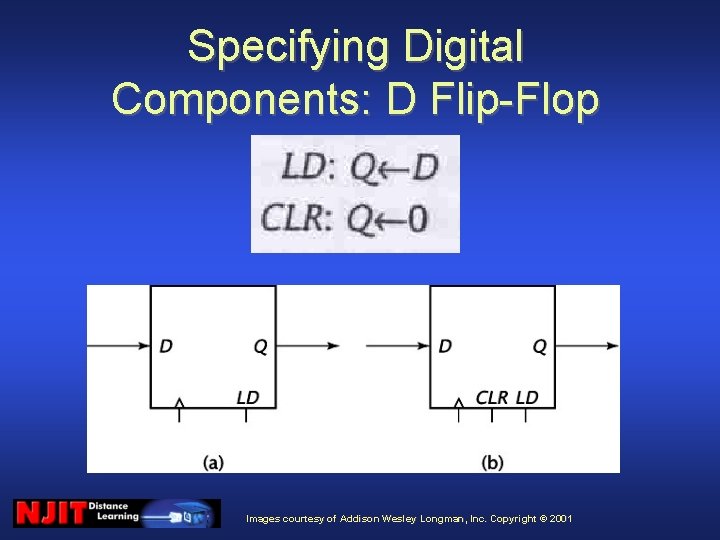

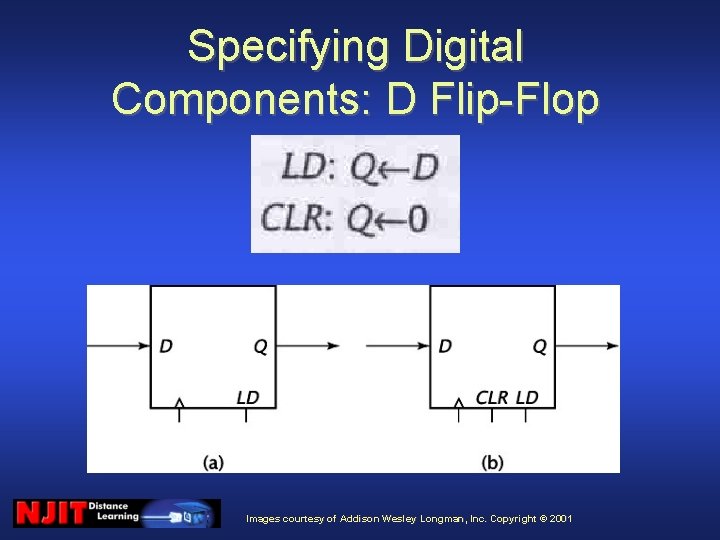

Specifying Digital Components: D Flip-Flop Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

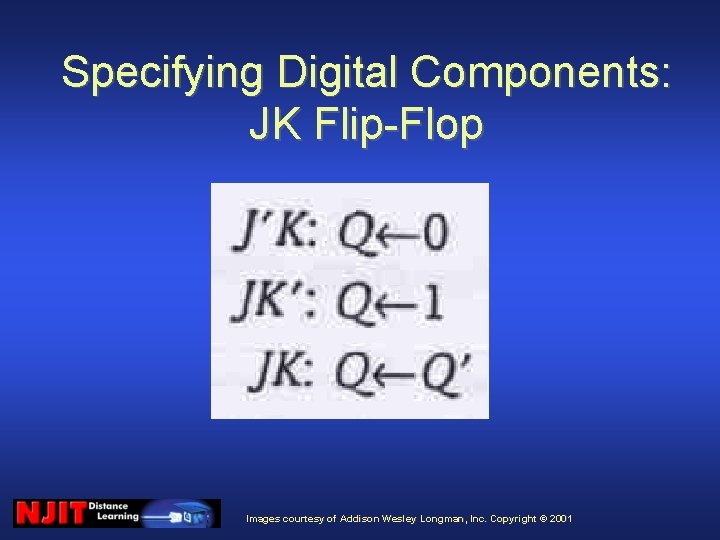

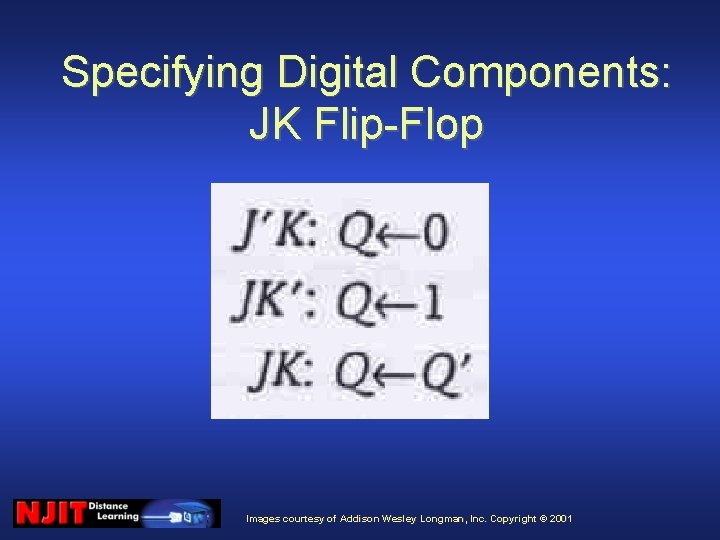

Specifying Digital Components: JK Flip-Flop Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

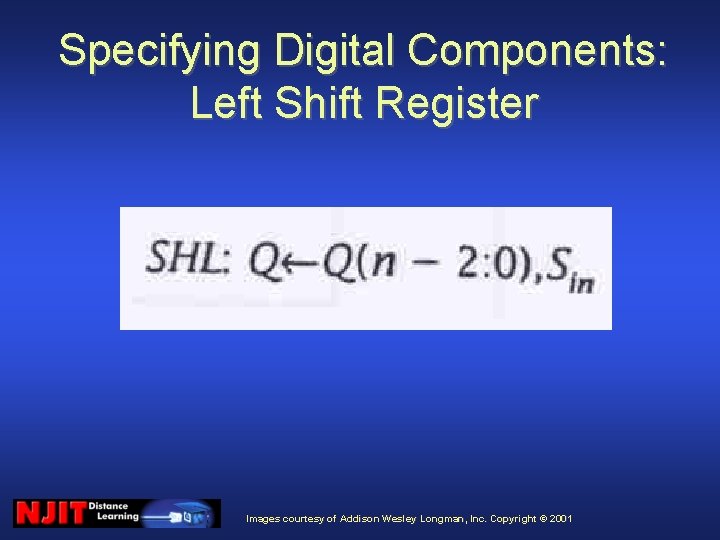

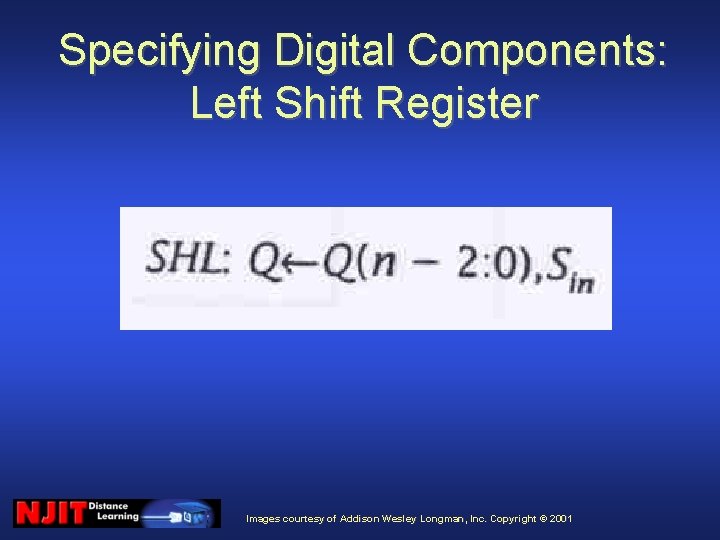

Specifying Digital Components: Left Shift Register Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

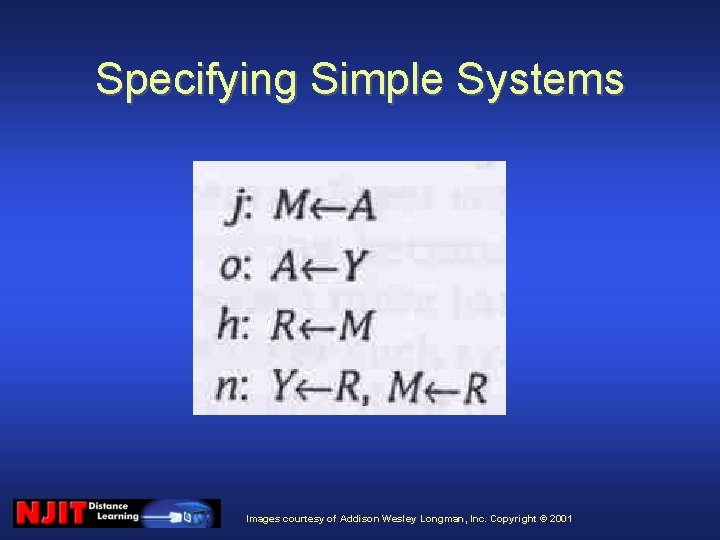

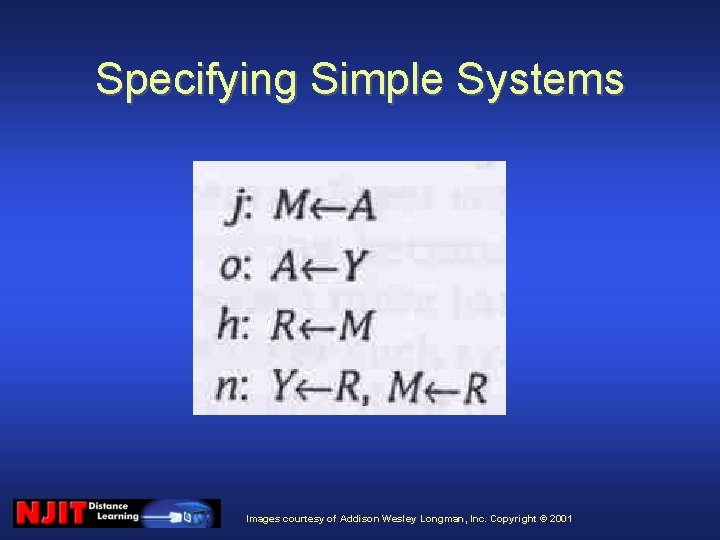

Specifying Simple Systems Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

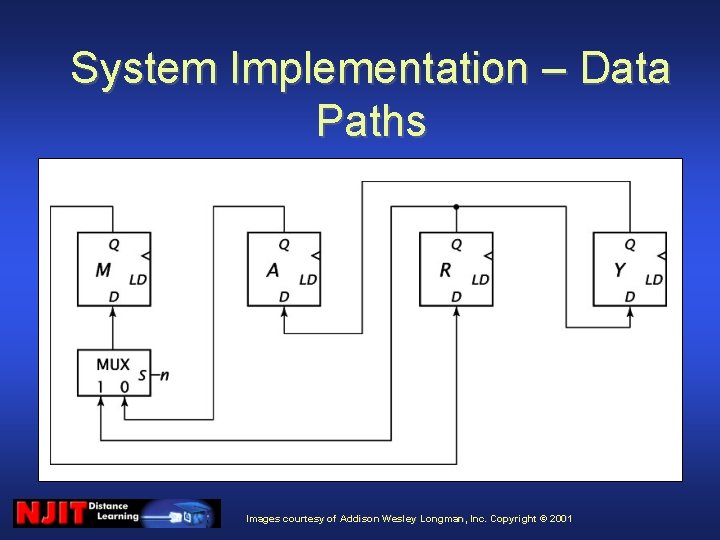

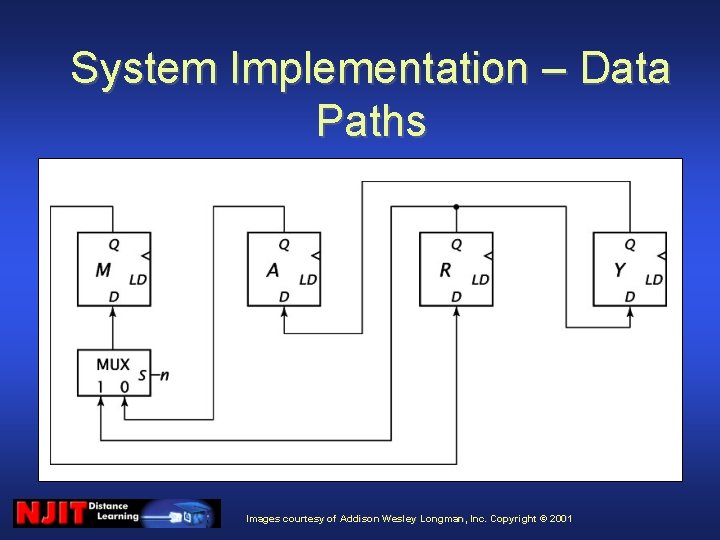

System Implementation – Data Paths Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

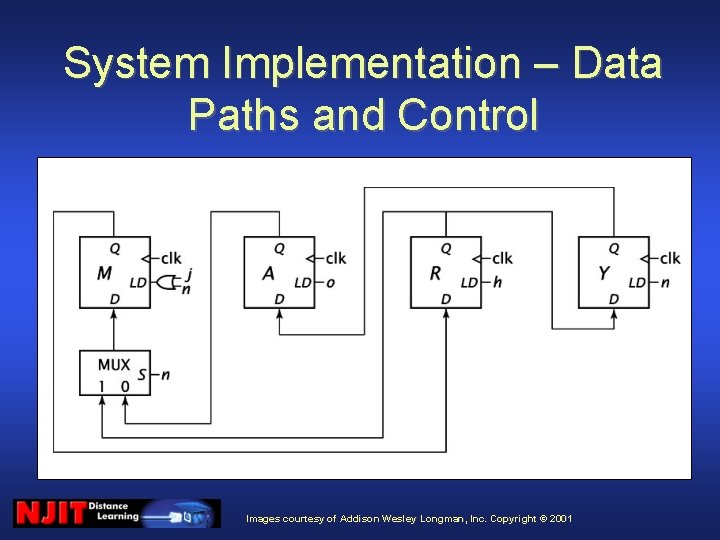

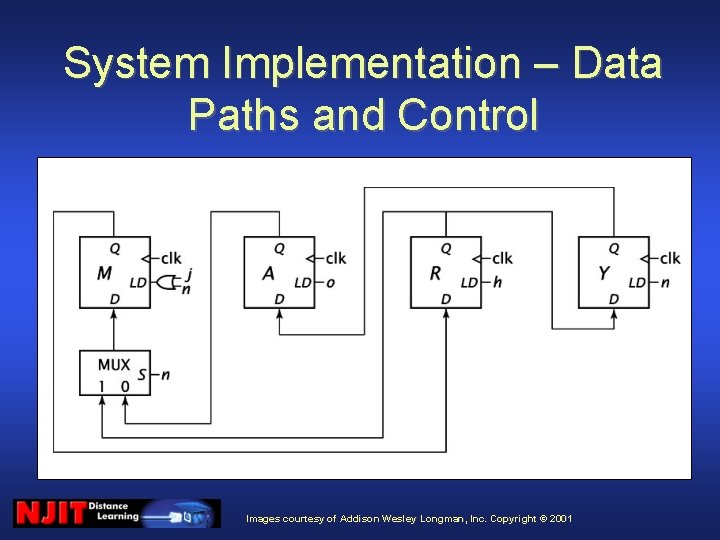

System Implementation – Data Paths and Control Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

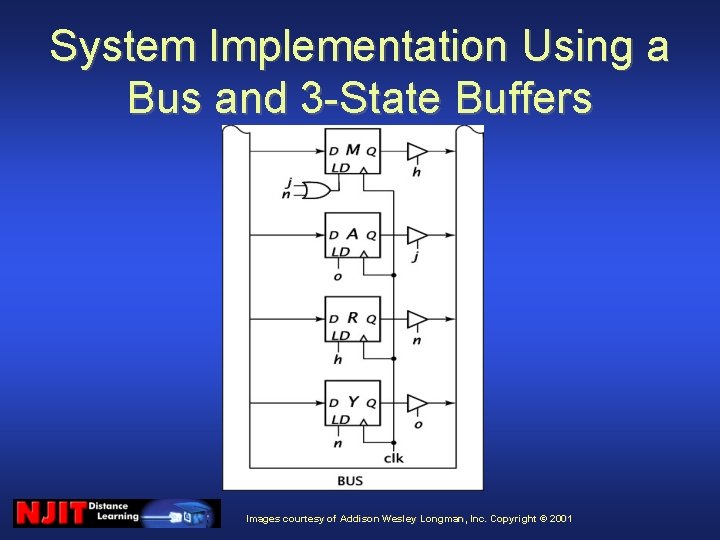

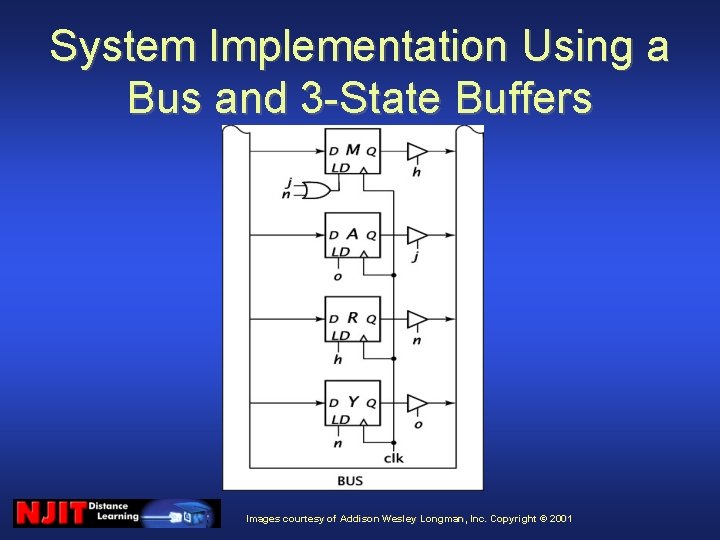

System Implementation Using a Bus and 3 -State Buffers Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

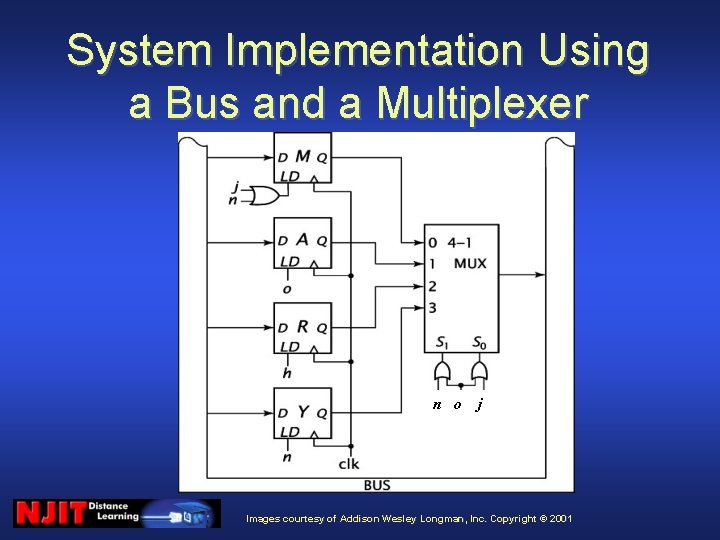

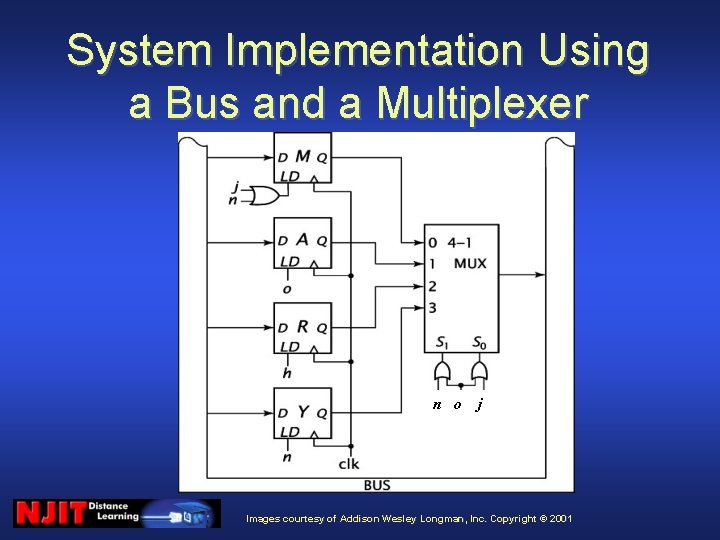

System Implementation Using a Bus and a Multiplexer n o j Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

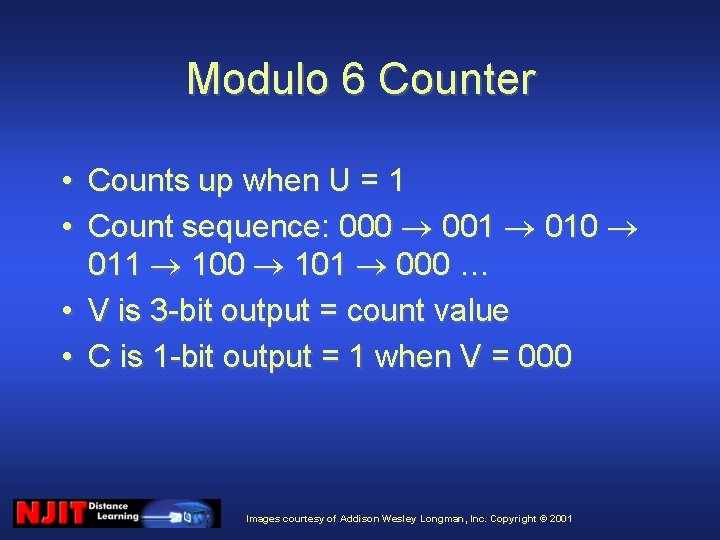

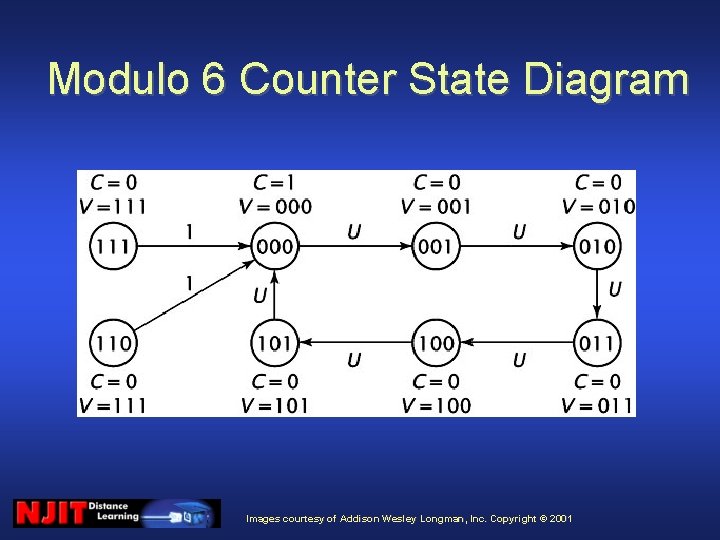

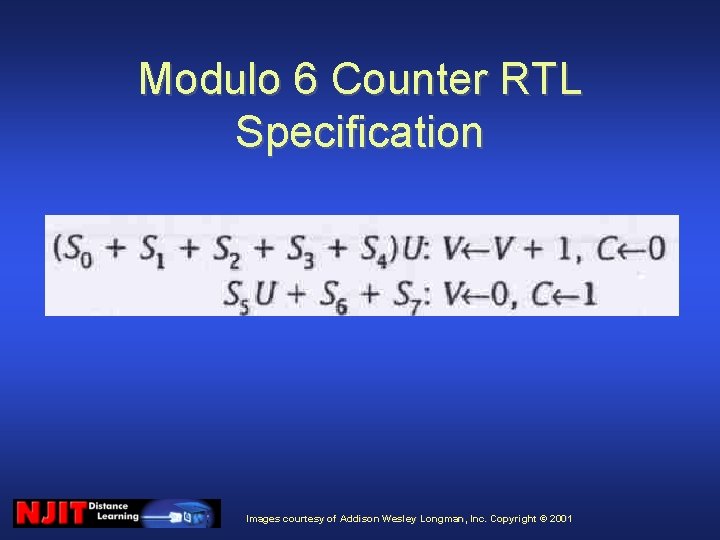

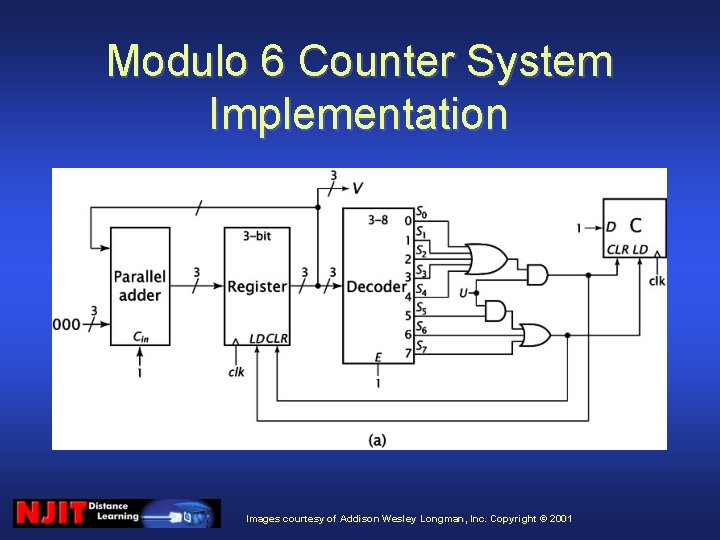

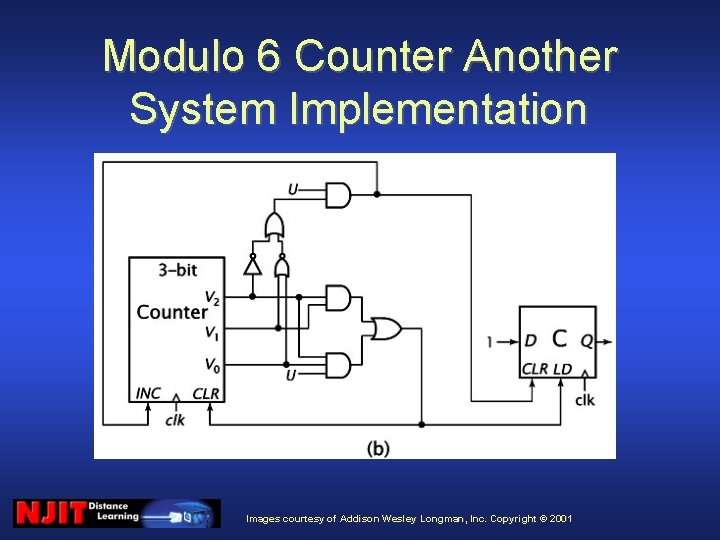

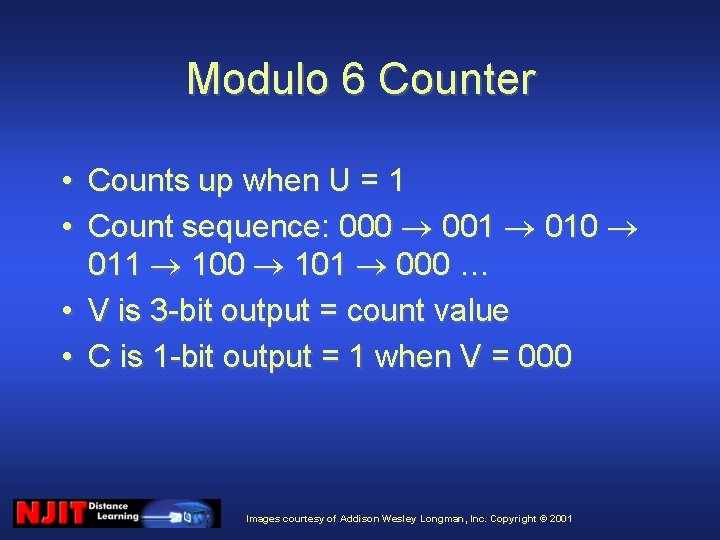

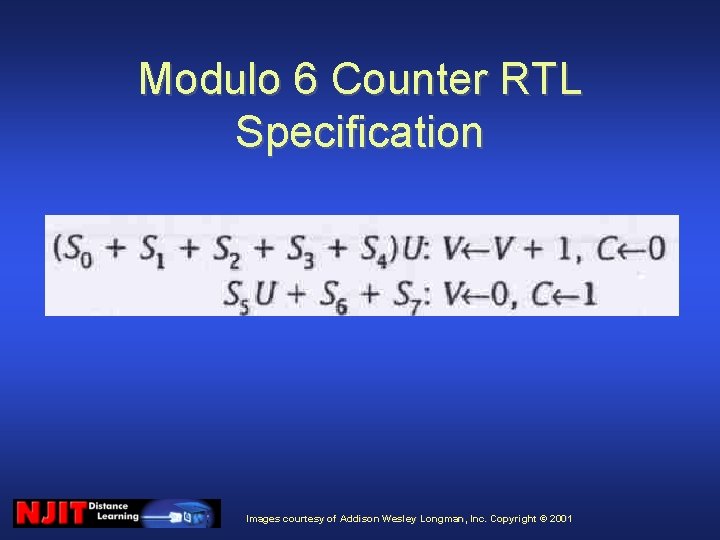

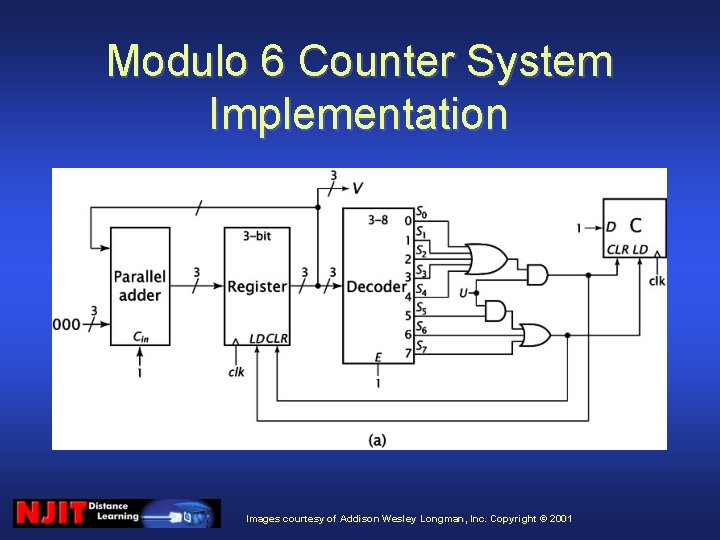

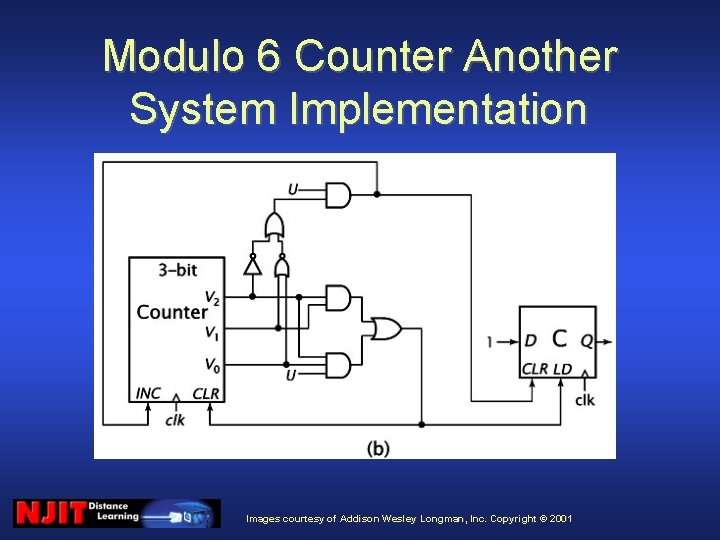

Modulo 6 Counter • Counts up when U = 1 • Count sequence: 000 001 010 011 100 101 000 … • V is 3 -bit output = count value • C is 1 -bit output = 1 when V = 000 Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

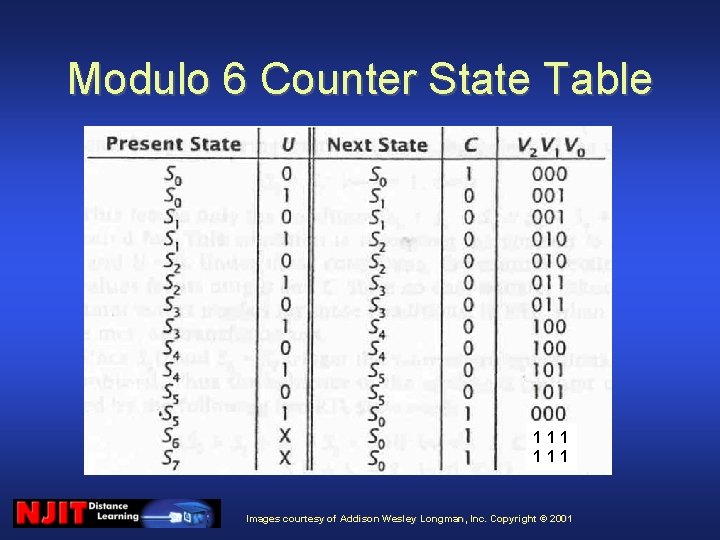

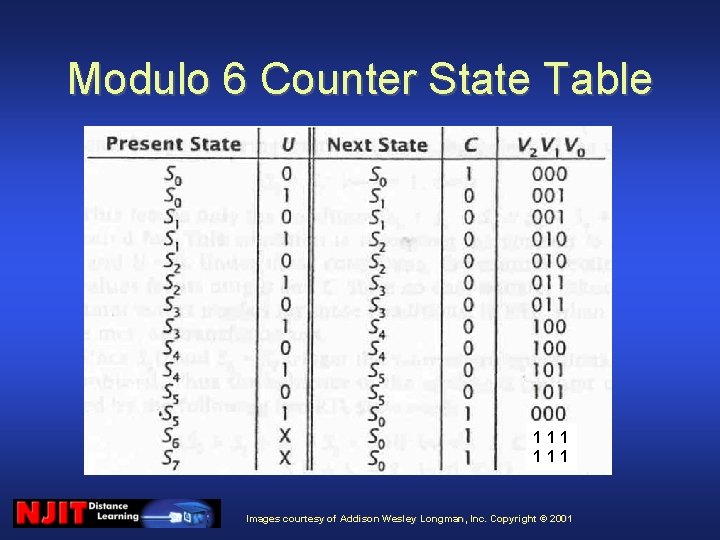

Modulo 6 Counter State Table 111 Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

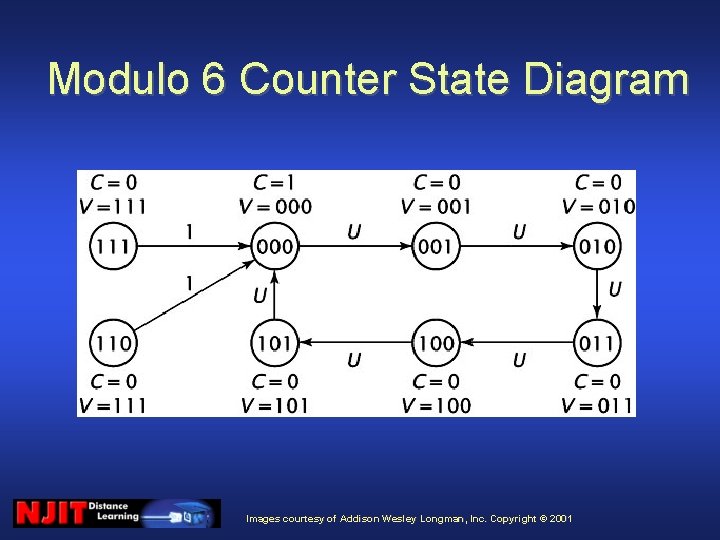

Modulo 6 Counter State Diagram Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

Modulo 6 Counter RTL Specification Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

Modulo 6 Counter System Implementation Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

Modulo 6 Counter Another System Implementation Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

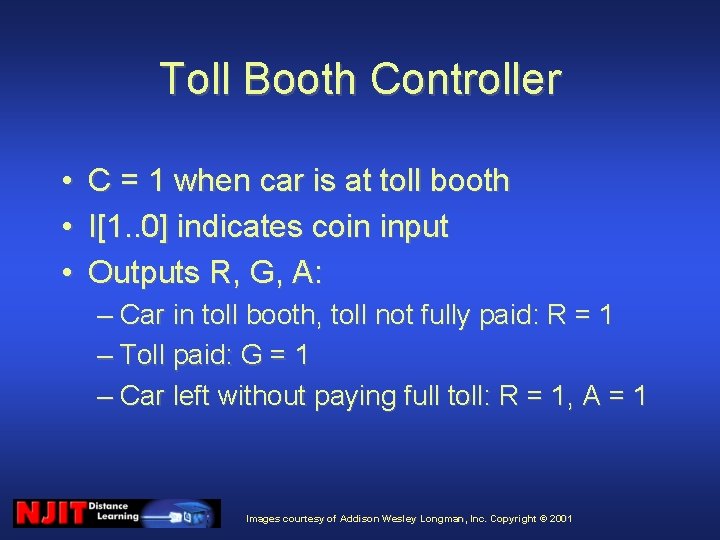

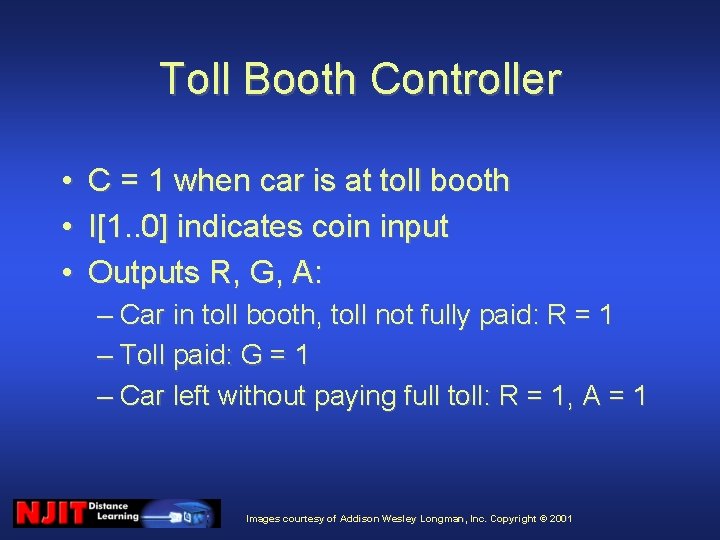

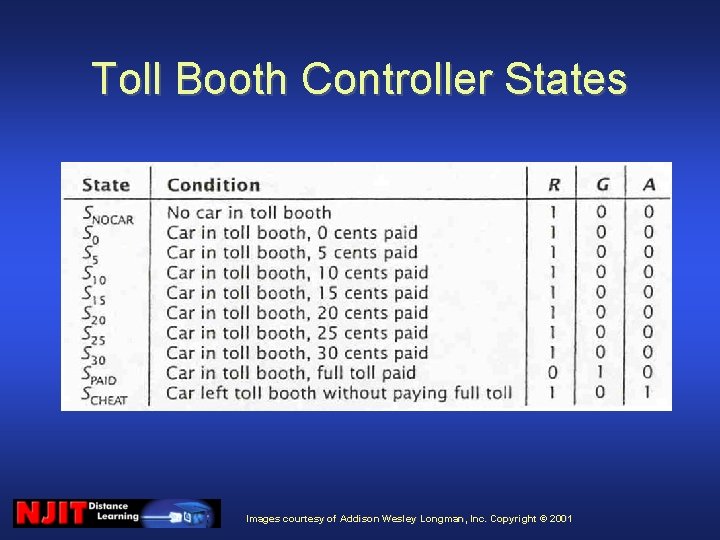

Toll Booth Controller • • • C = 1 when car is at toll booth I[1. . 0] indicates coin input Outputs R, G, A: – Car in toll booth, toll not fully paid: R = 1 – Toll paid: G = 1 – Car left without paying full toll: R = 1, A = 1 Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

Toll Booth Controller States Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

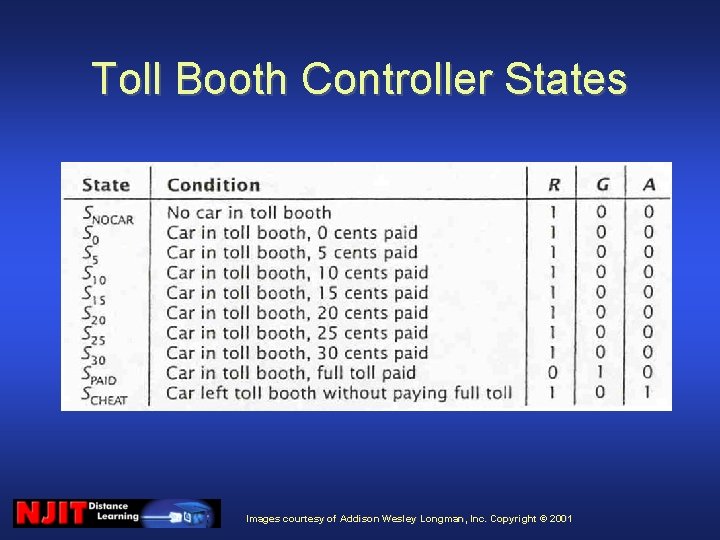

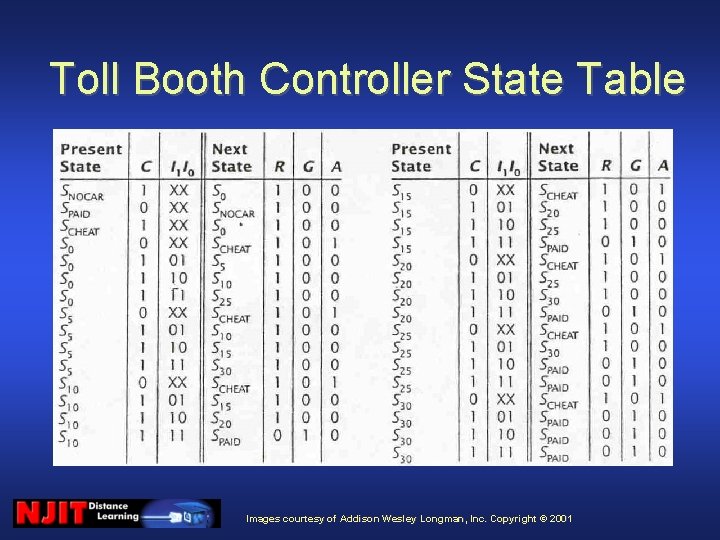

Toll Booth Controller State Table Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

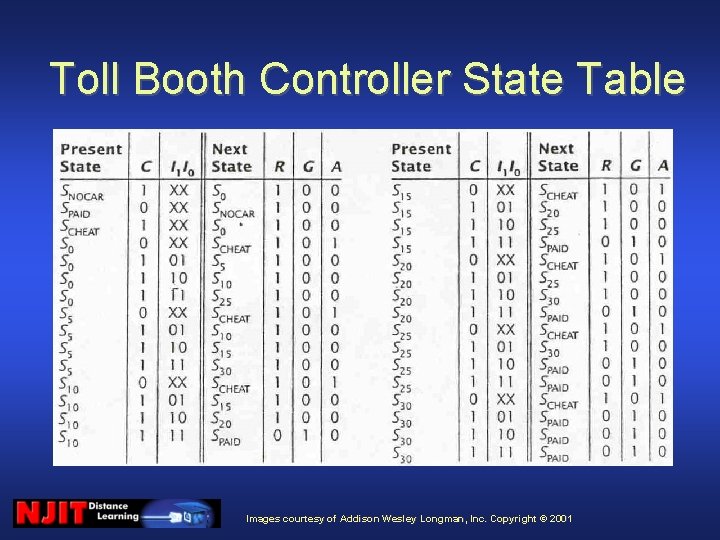

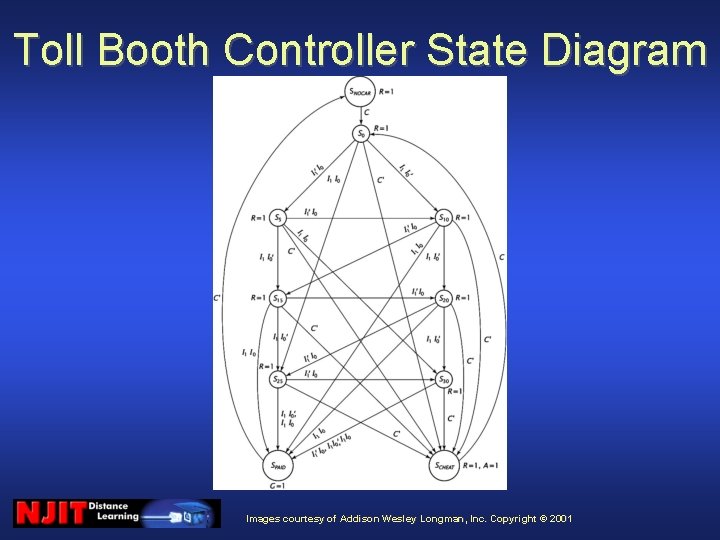

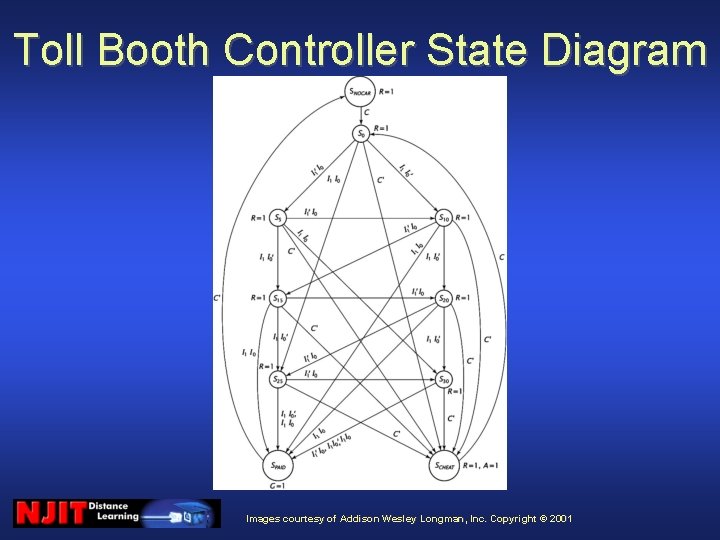

Toll Booth Controller State Diagram Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

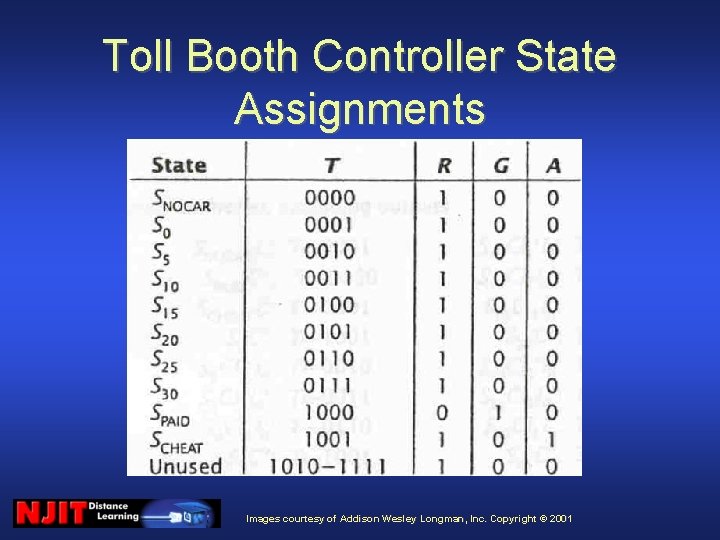

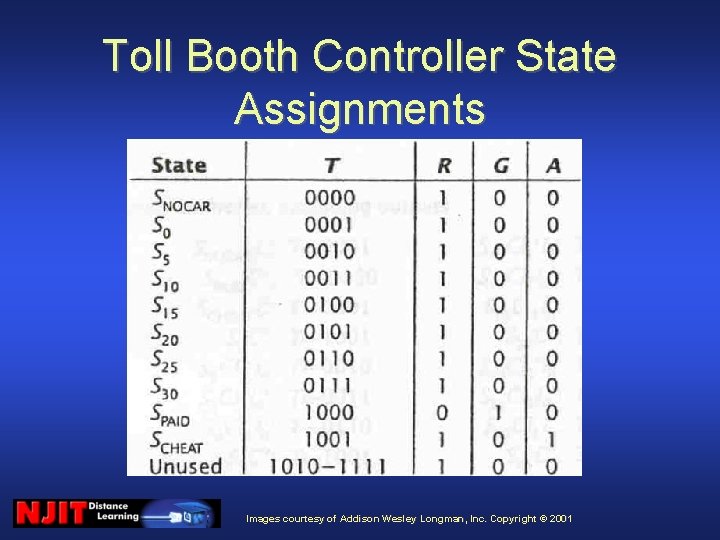

Toll Booth Controller State Assignments Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

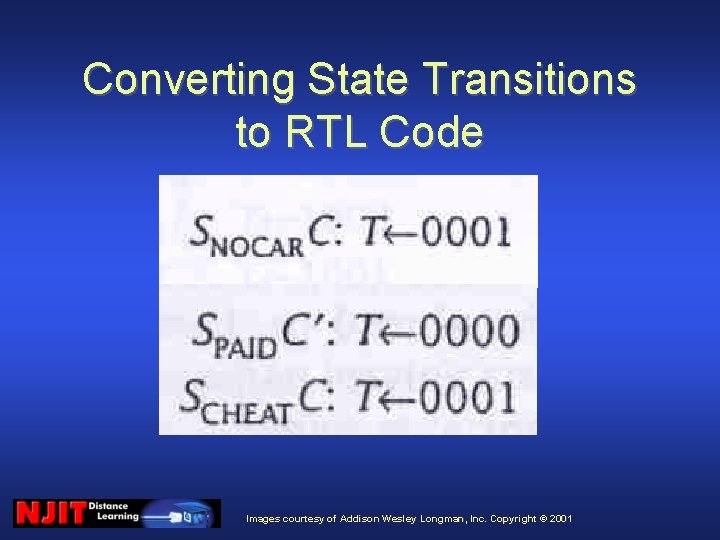

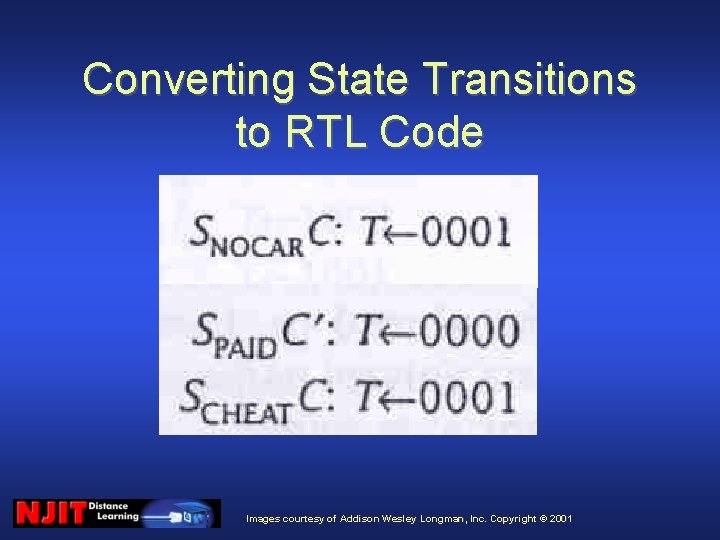

Converting State Transitions to RTL Code Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

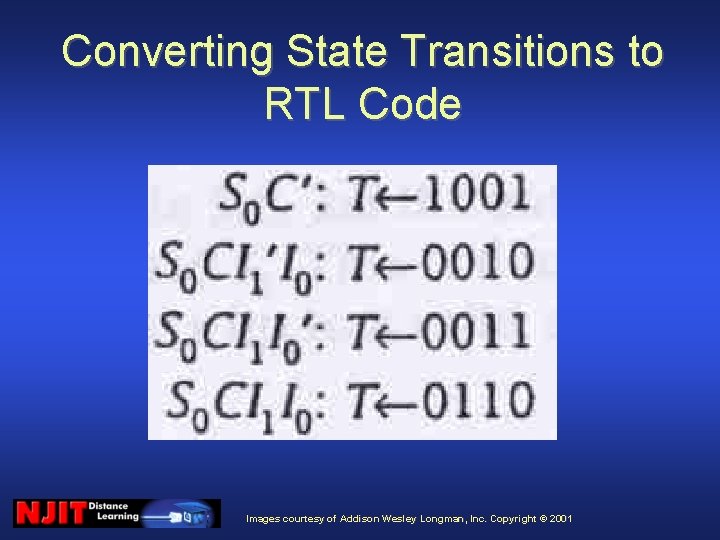

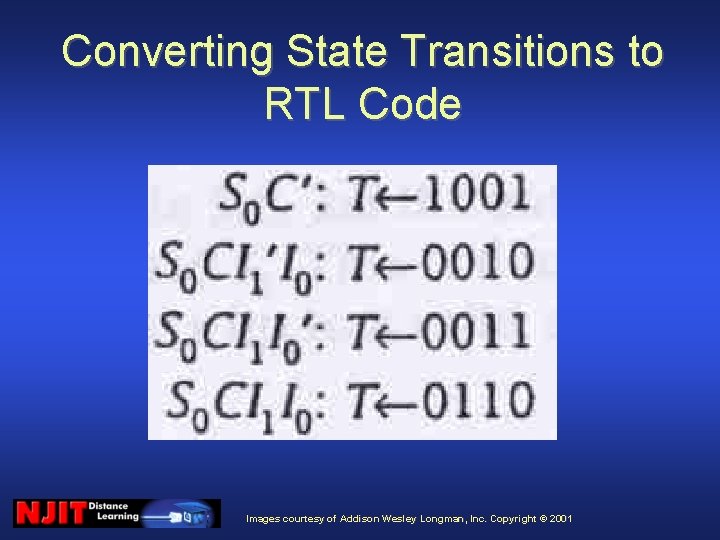

Converting State Transitions to RTL Code Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

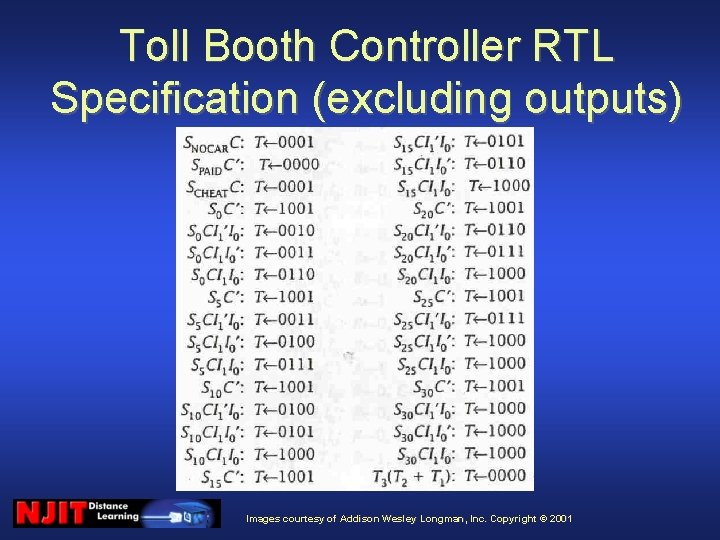

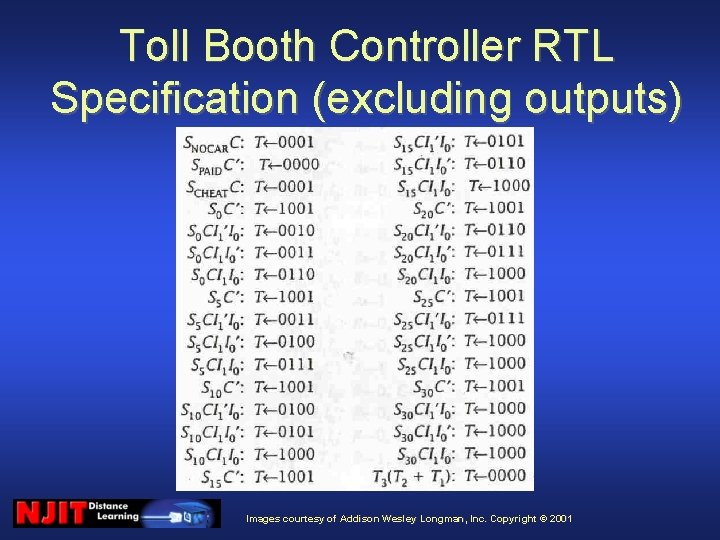

Toll Booth Controller RTL Specification (excluding outputs) Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

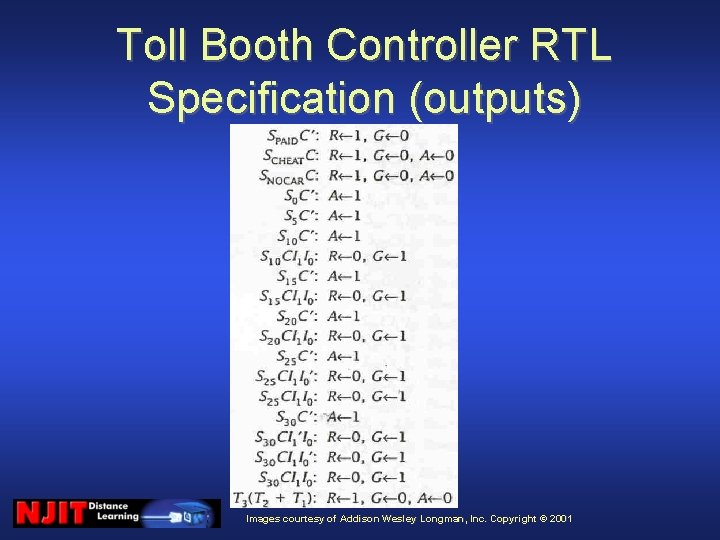

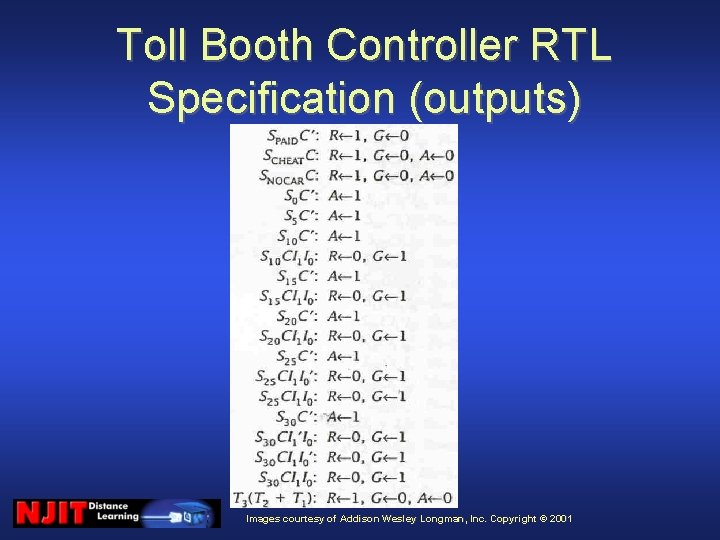

Toll Booth Controller RTL Specification (outputs) Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

VHDL – VHSIC Hardware Description Language • • • Formal syntax – portable Platform independent Design for PLDs, ASICs, or custom chips • Simulate designs • Different levels of abstraction Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

VHDL Design Structure • • • Library section Entity section Architecture section Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

VHDL Library Section library IEEE; use IEEE. std_logic_1164. all; Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

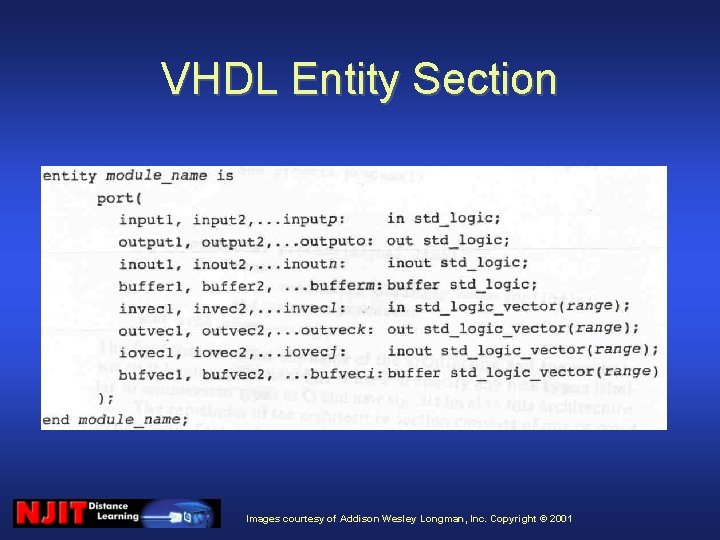

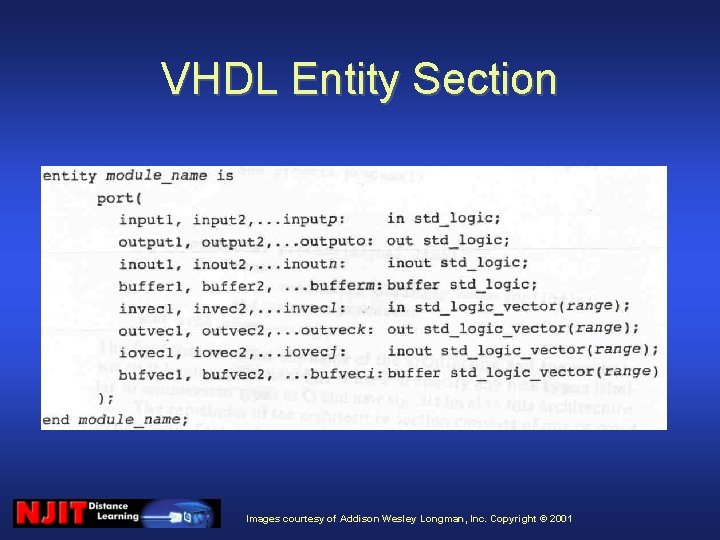

VHDL Entity Section Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

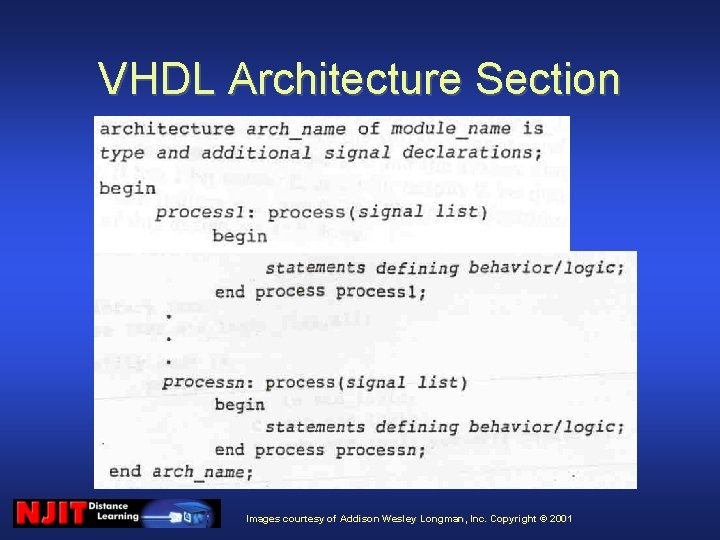

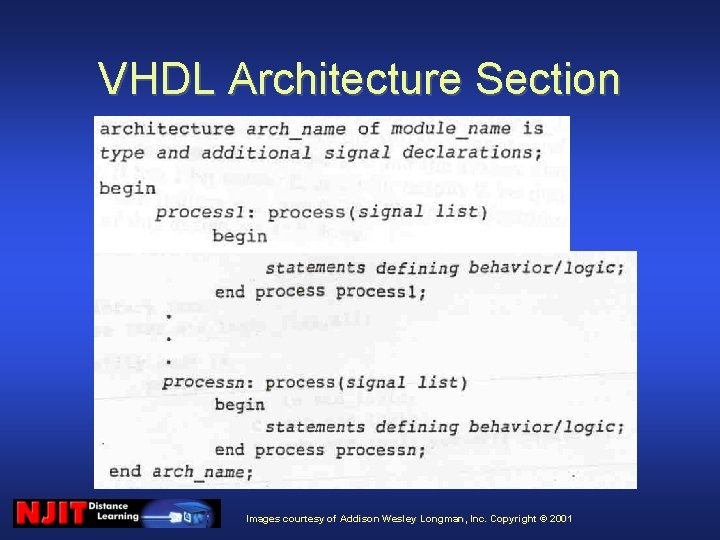

VHDL Architecture Section Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

VHDL – High Level of Abstraction • Modulo 6 counter • Designed as a state machine Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

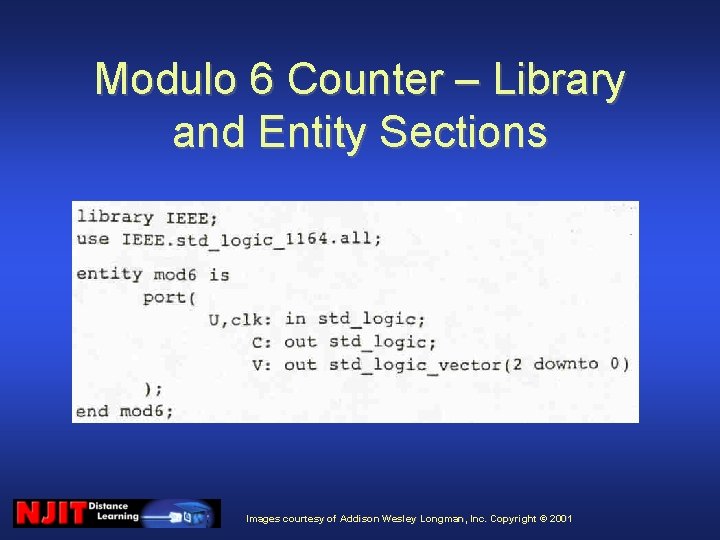

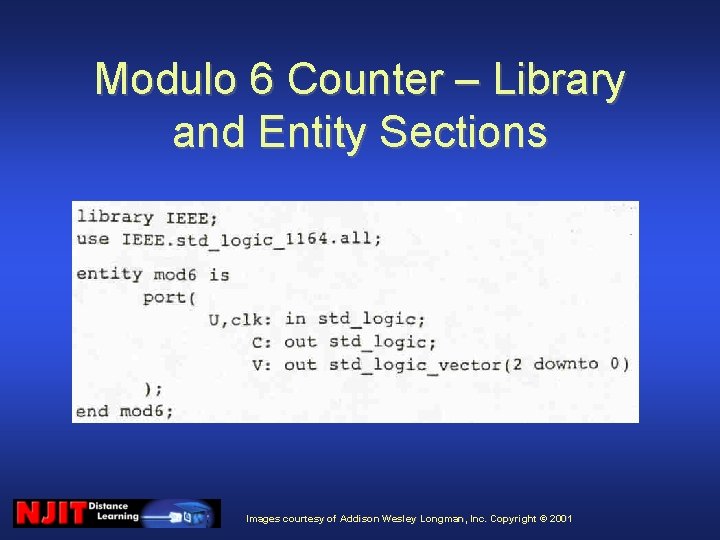

Modulo 6 Counter – Library and Entity Sections Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

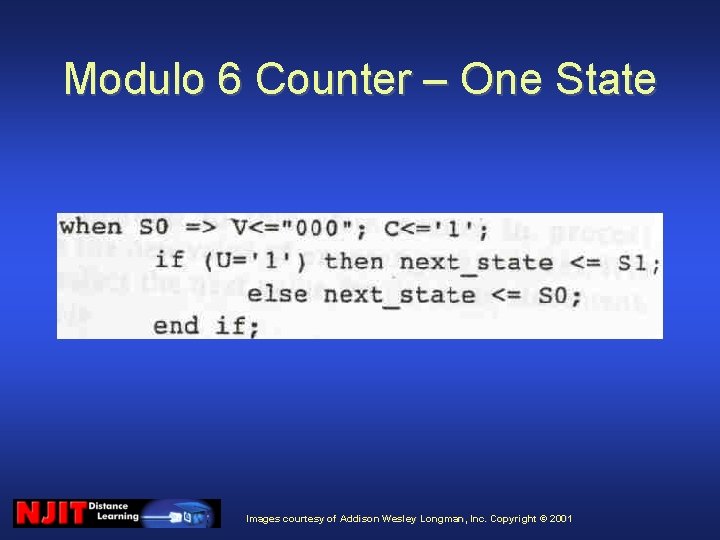

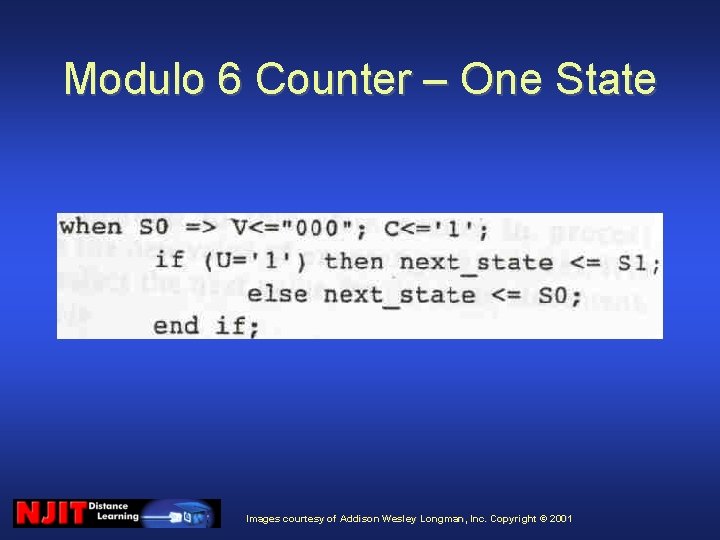

Modulo 6 Counter – One State Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

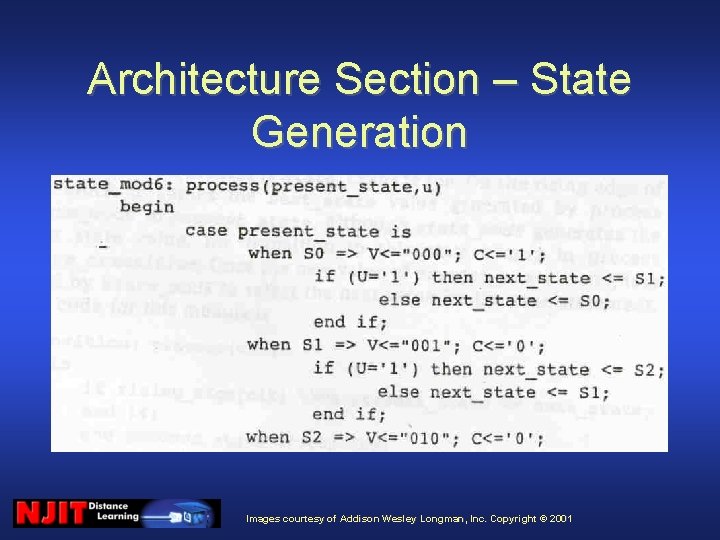

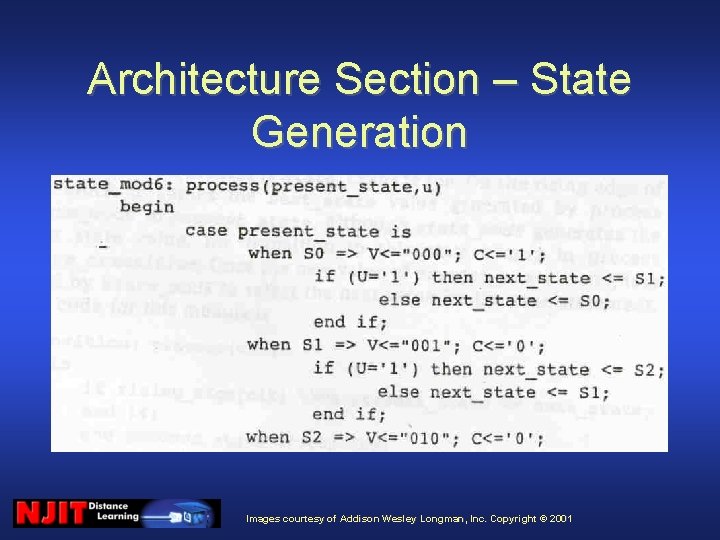

Architecture Section – State Generation Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

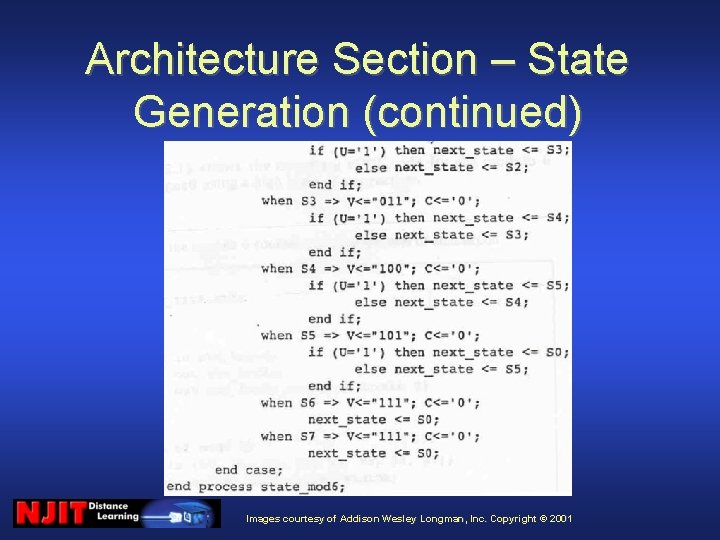

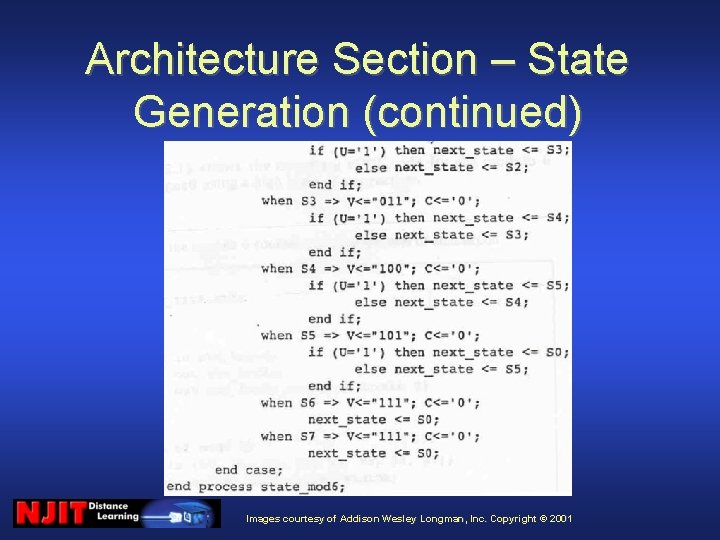

Architecture Section – State Generation (continued) Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

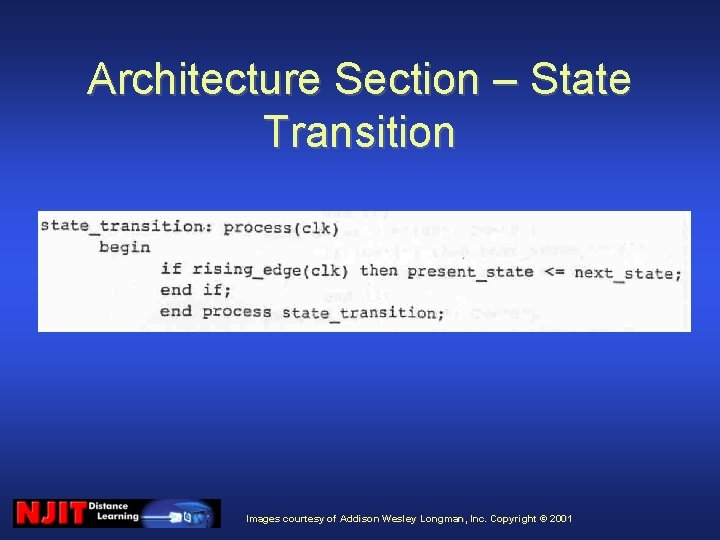

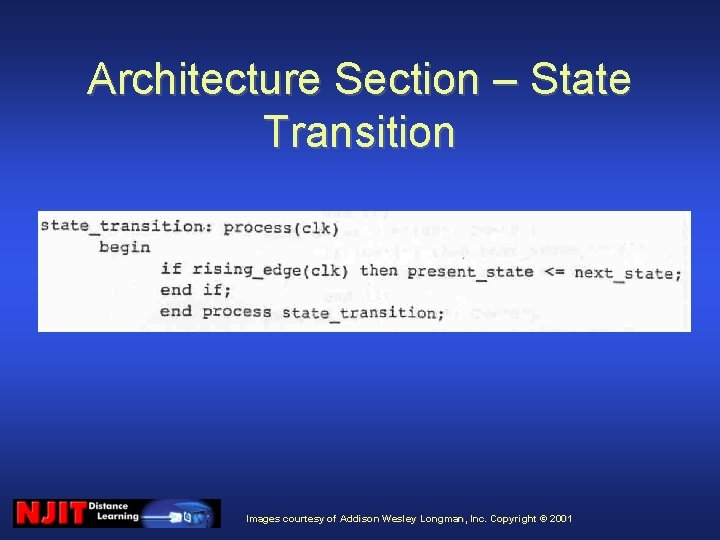

Architecture Section – State Transition Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

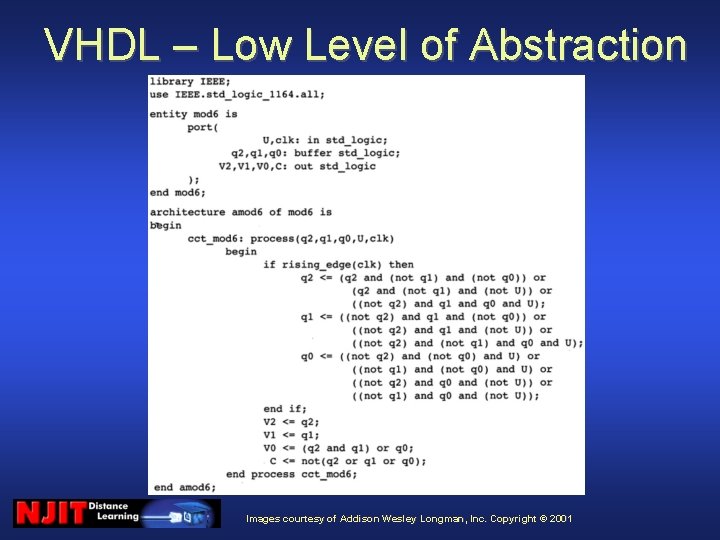

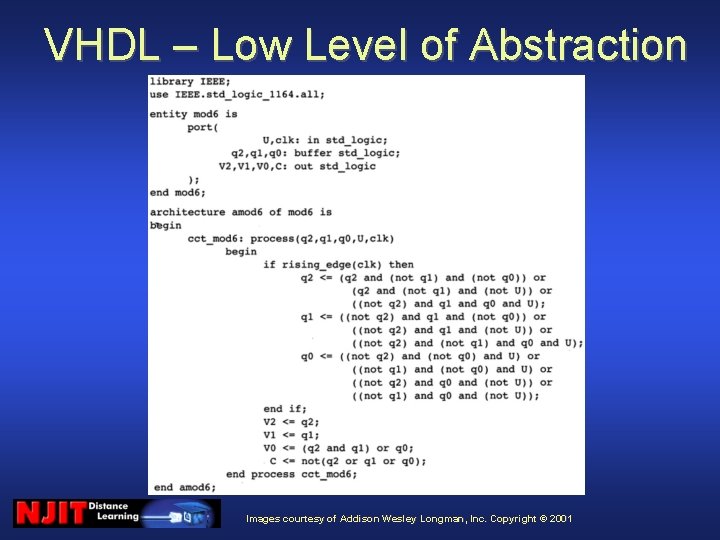

VHDL – Low Level of Abstraction Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

VHDL – Advanced Capabilities • • • Components Timing Simulation Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001

Summary • • • Micro-operations RTL specifications Realizing RTL specifications VHDL Images courtesy of Addison Wesley Longman, Inc. Copyright © 2001