CEC 220 Digital Circuit Design Dice Game Wed

- Slides: 15

CEC 220 Digital Circuit Design Dice Game Wed, April 06 CEC 220 Digital Circuit Design Slide 1 of 15

Lecture Outline • Dice Game § A complex Word Problem Wed, April 06 CEC 220 Digital Circuit Design Slide 2 of 5

Dice Game • Implement the following dice game: 1. First Roll: Two die are thrown § § § The player wins if the sum is 7 or 11, The player loses if the sum is 2, 3, or 12, otherwise The sum is stored and referred to as the “point” and he/she must throw again. o Las Vegas Rules: The point remains fixed. 2. Second or Subsequent Roll: Two die are thrown § § § The player wins if the sum is equal to his/her point, The player loses if the sum is equal to 7, otherwise He/she must roll again until a win or loss. Wed, April 06 CEC 220 Digital Circuit Design Slide 3 of 5

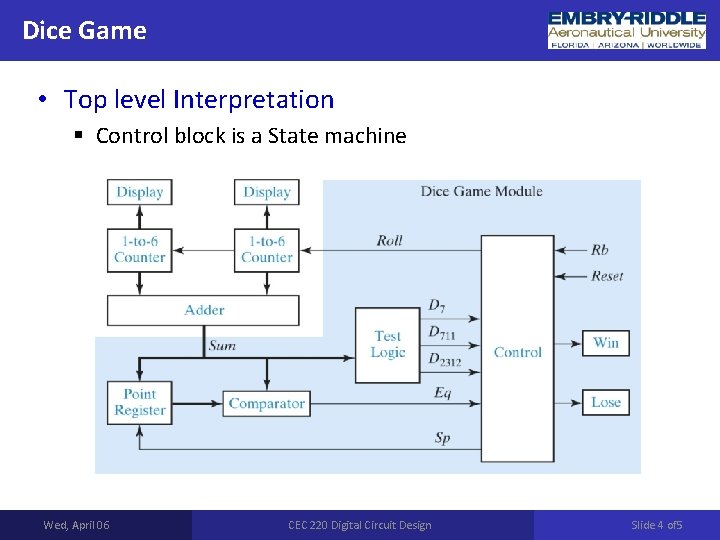

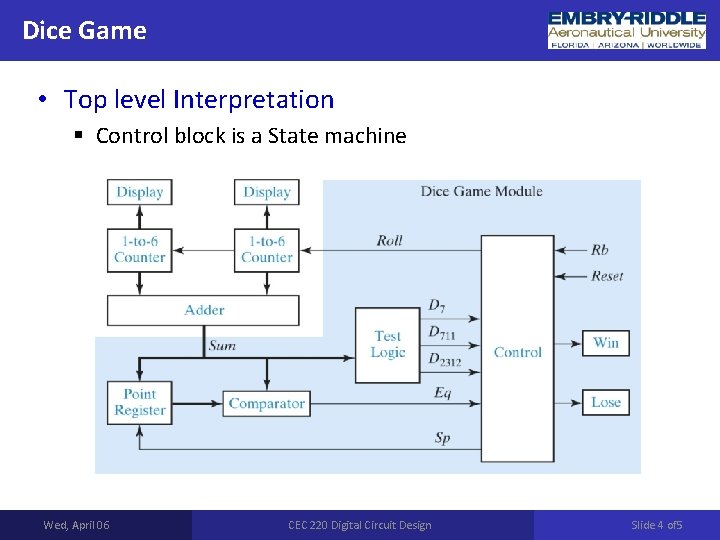

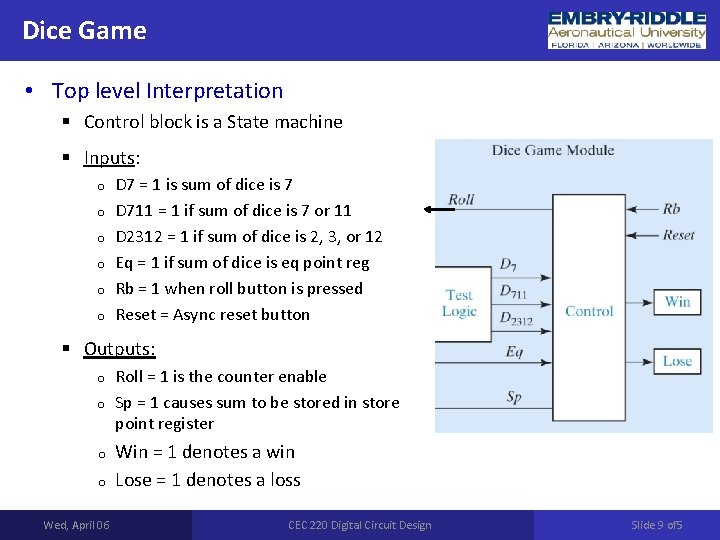

Dice Game • Top level Interpretation § Control block is a State machine Wed, April 06 CEC 220 Digital Circuit Design Slide 4 of 5

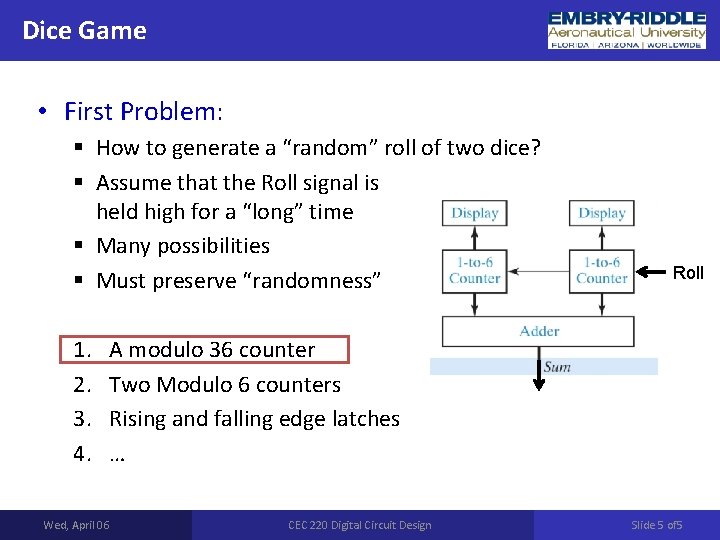

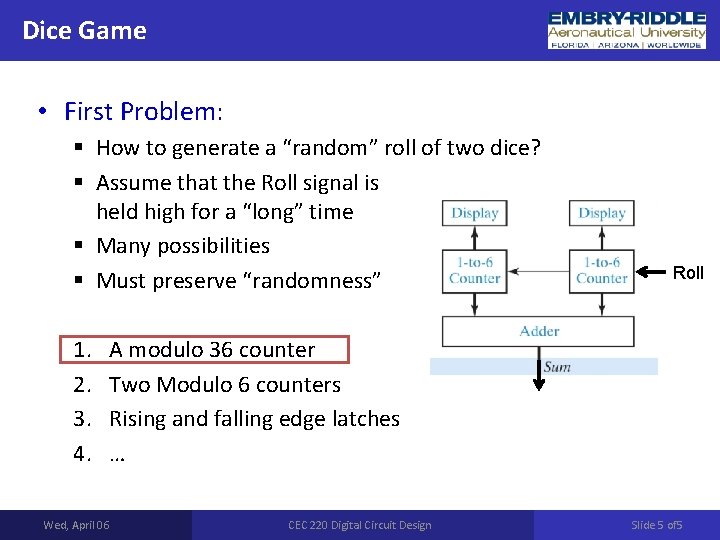

Dice Game • First Problem: § How to generate a “random” roll of two dice? § Assume that the Roll signal is held high for a “long” time § Many possibilities § Must preserve “randomness” 1. 2. 3. 4. Roll A modulo 36 counter Two Modulo 6 counters Rising and falling edge latches … Wed, April 06 CEC 220 Digital Circuit Design Slide 5 of 5

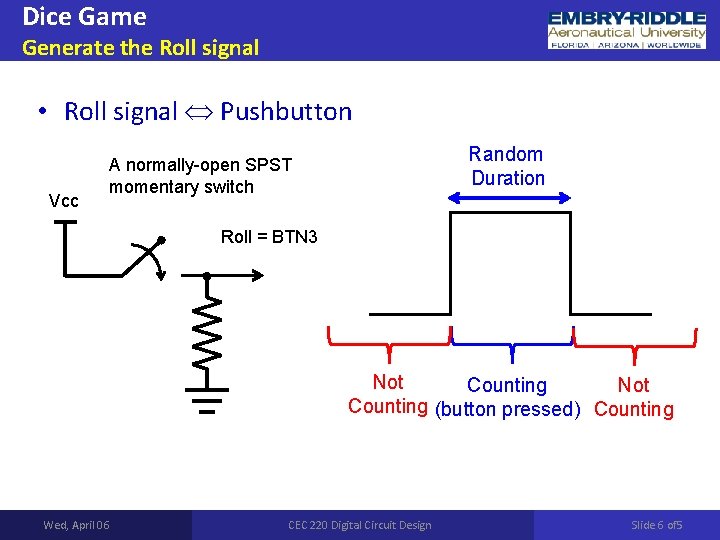

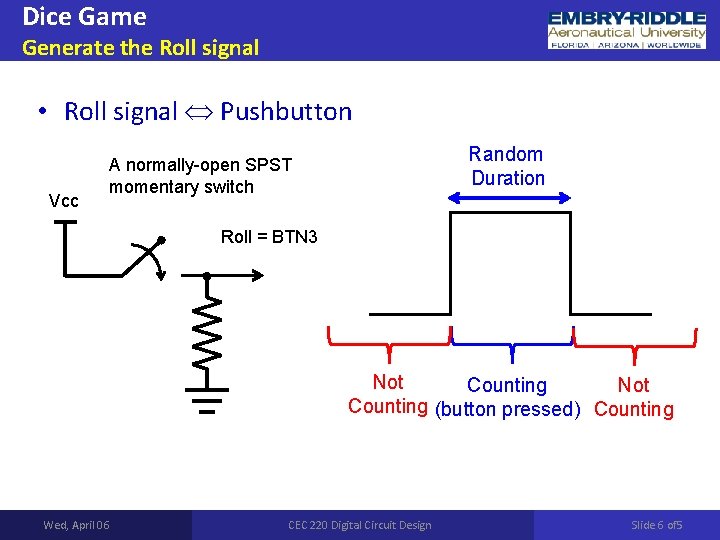

Dice Game Generate the Roll signal • Roll signal Pushbutton Vcc Random Duration A normally-open SPST momentary switch Roll = BTN 3 Not Counting (button pressed) Counting Wed, April 06 CEC 220 Digital Circuit Design Slide 6 of 5

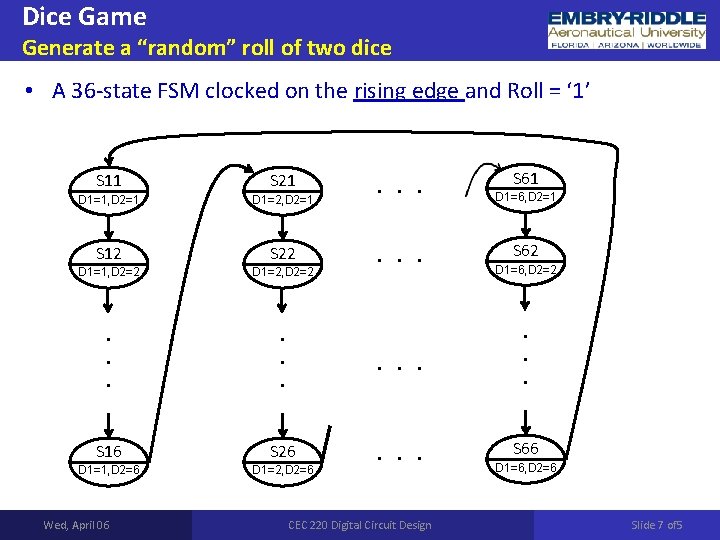

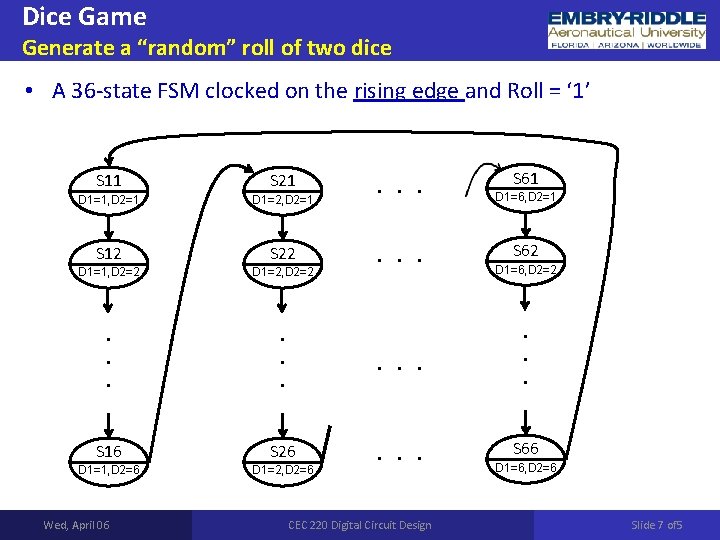

Dice Game Generate a “random” roll of two dice • A 36 -state FSM clocked on the rising edge and Roll = ‘ 1’ S 61 S 11 S 21 D 1=1, D 2=1 D 1=2, D 2=1 S 12 S 22 D 1=1, D 2=2 D 1=2, D 2=2 . . . S 16 S 26 S 66 D 1=1, D 2=6 D 1=2, D 2=6 . . . Wed, April 06 . . . CEC 220 Digital Circuit Design D 1=6, D 2=1 S 62 D 1=6, D 2=6 Slide 7 of 5

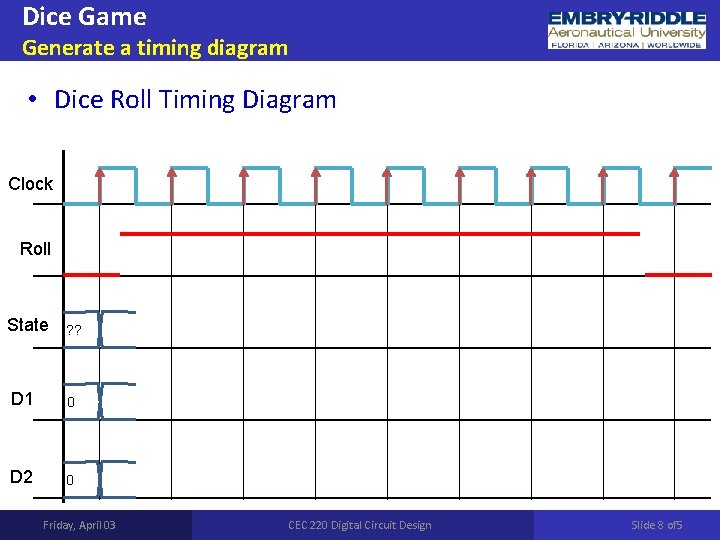

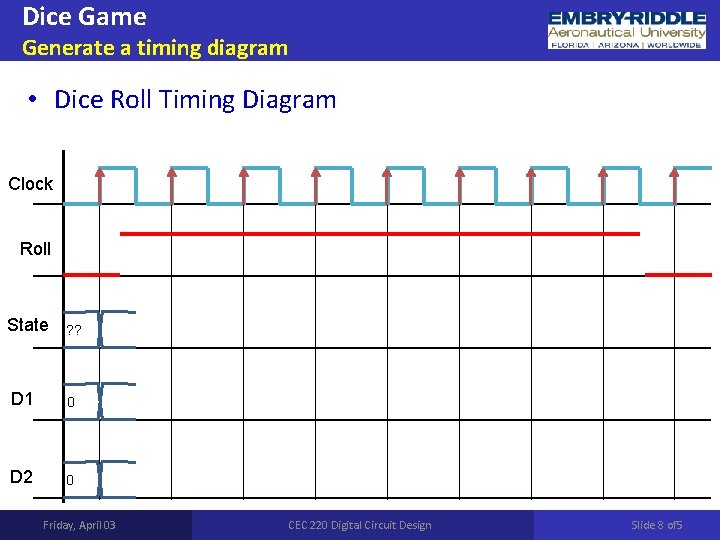

Dice Game Generate a timing diagram • Dice Roll Timing Diagram Clock Roll State ? ? D 1 0 D 2 0 Friday, April 03 CEC 220 Digital Circuit Design Slide 8 of 5

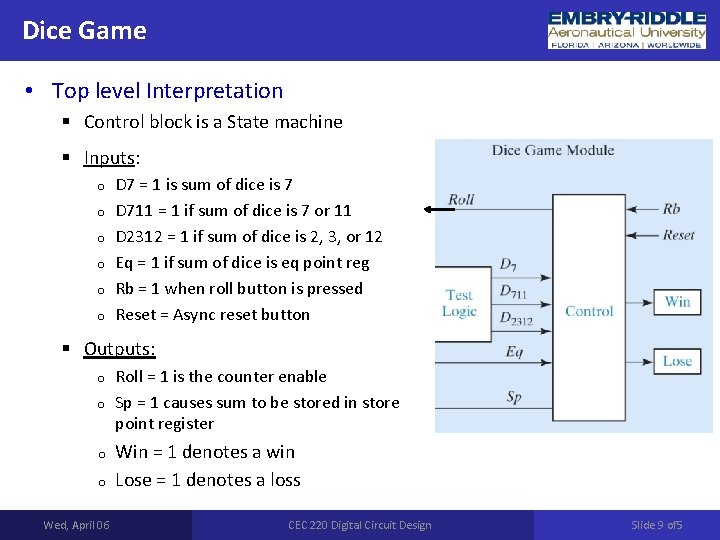

Dice Game • Top level Interpretation § Control block is a State machine § Inputs: o o o D 7 = 1 is sum of dice is 7 D 711 = 1 if sum of dice is 7 or 11 D 2312 = 1 if sum of dice is 2, 3, or 12 Eq = 1 if sum of dice is eq point reg Rb = 1 when roll button is pressed Reset = Async reset button § Outputs: o o Wed, April 06 Roll = 1 is the counter enable Sp = 1 causes sum to be stored in store point register Win = 1 denotes a win Lose = 1 denotes a loss CEC 220 Digital Circuit Design Slide 9 of 5

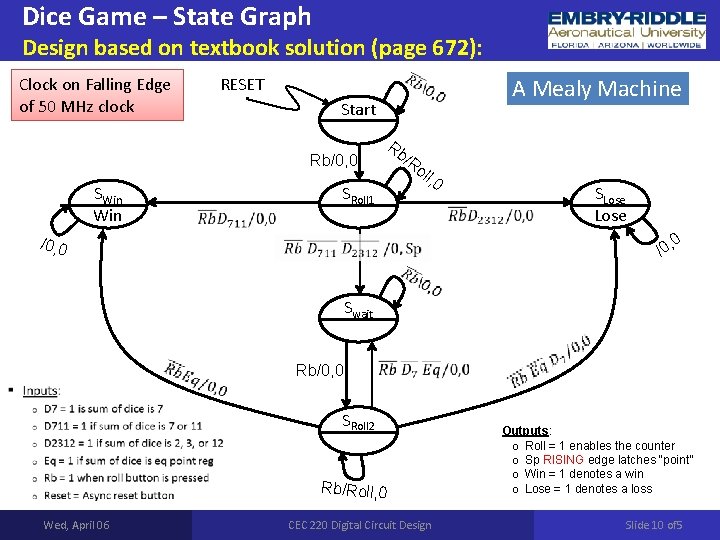

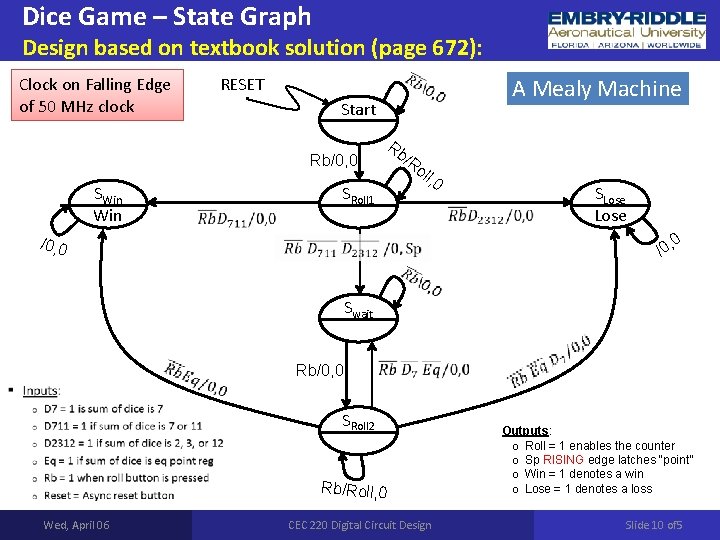

Dice Game – State Graph Design based on textbook solution (page 672): RESET Clock on Falling Edge of 50 MHz clock Start Rb / Ro Rb/0, 0 SWin SRoll 1 ll, 0 SLose /0, 0 A Mealy Machine , 0 /0 Swait Rb/0, 0 SRoll 2 Rb/Roll, 0 Wed, April 06 CEC 220 Digital Circuit Design Outputs: o Roll = 1 enables the counter o Sp RISING edge latches “point” o Win = 1 denotes a win o Lose = 1 denotes a loss Slide 10 of 5

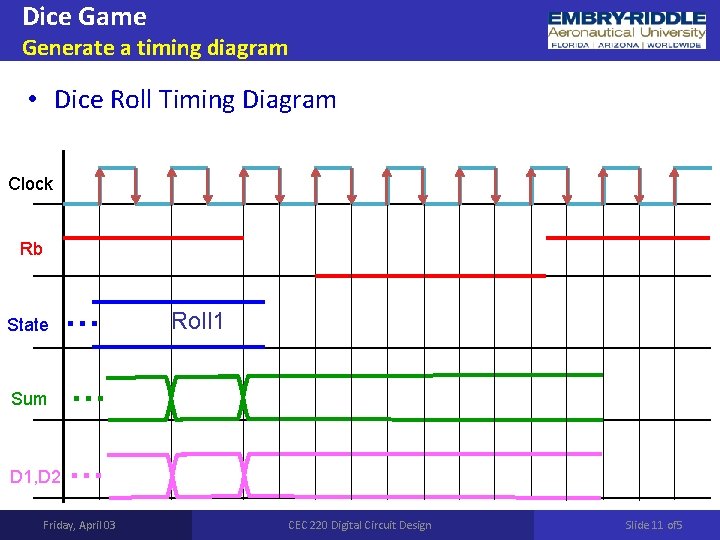

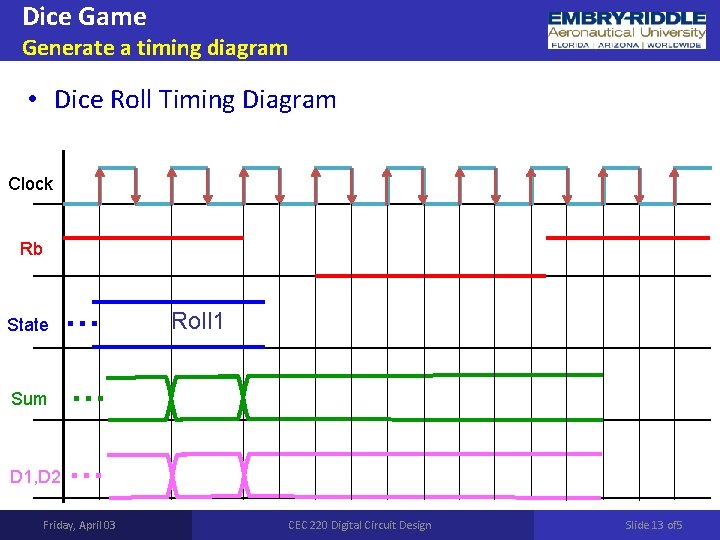

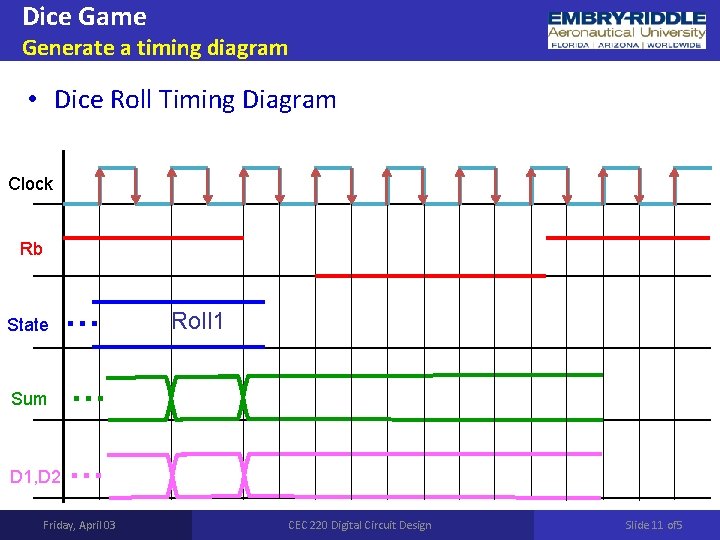

Dice Game Generate a timing diagram • Dice Roll Timing Diagram Clock Rb State … Sum … D 1, D 2 … Friday, April 03 Roll 1 CEC 220 Digital Circuit Design Slide 11 of 5

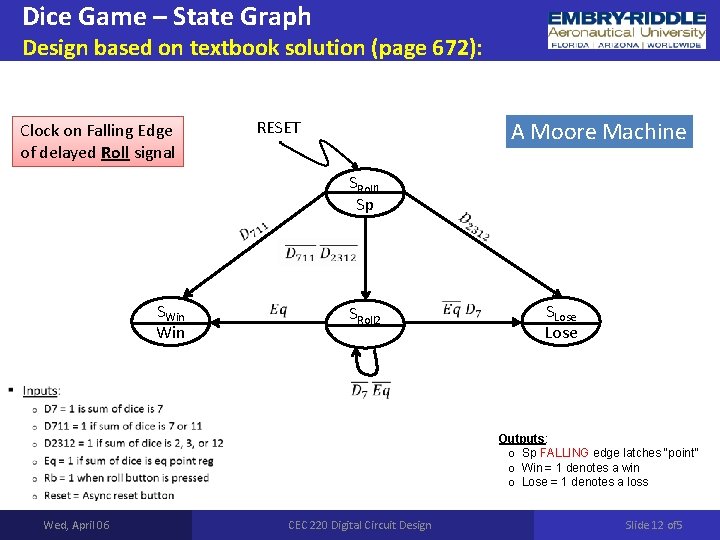

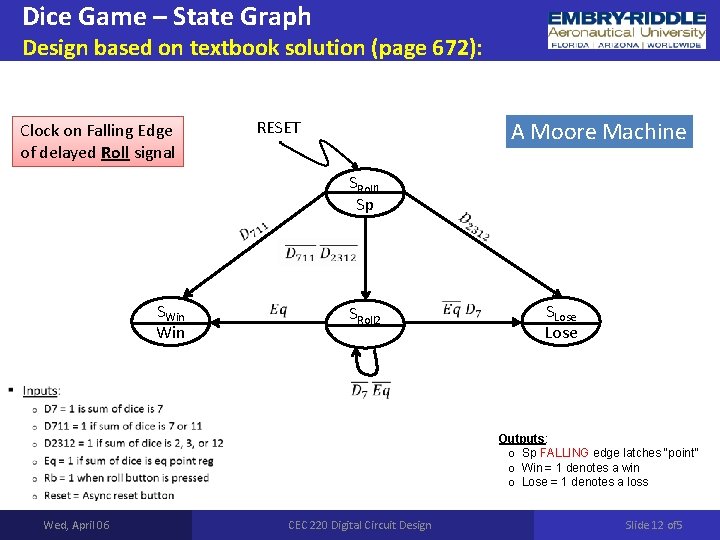

Dice Game – State Graph Design based on textbook solution (page 672): RESET Clock on Falling Edge of delayed Roll signal A Moore Machine SRoll 1 Sp SWin SRoll 2 SLose Outputs: o Sp FALLING edge latches “point” o Win = 1 denotes a win o Lose = 1 denotes a loss Wed, April 06 CEC 220 Digital Circuit Design Slide 12 of 5

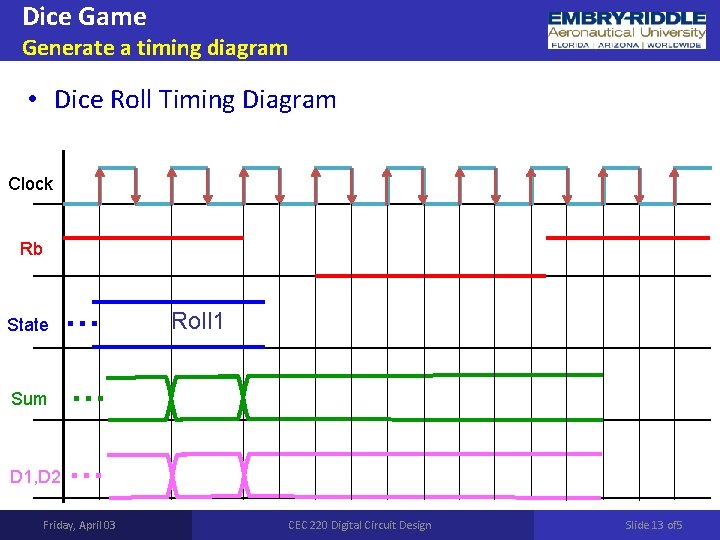

Dice Game Generate a timing diagram • Dice Roll Timing Diagram Clock Rb State … Sum … D 1, D 2 … Friday, April 03 Roll 1 CEC 220 Digital Circuit Design Slide 13 of 5

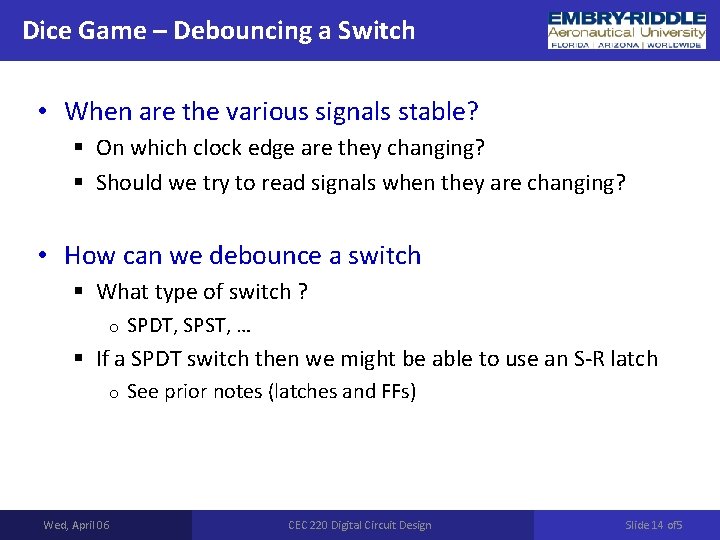

Dice Game – Debouncing a Switch • When are the various signals stable? § On which clock edge are they changing? § Should we try to read signals when they are changing? • How can we debounce a switch § What type of switch ? o SPDT, SPST, … § If a SPDT switch then we might be able to use an S-R latch o Wed, April 06 See prior notes (latches and FFs) CEC 220 Digital Circuit Design Slide 14 of 5

Next Lecture • State Machine Design with SM Charts Wed, April 06 CEC 220 Digital Circuit Design Slide 15 of 5