BuiltIn SelfTest and Calibration of Mixedsignal Devices Wei

Built-In Self-Test and Calibration of Mixed-signal Devices Wei Jiang Ph. D. Dissertation Proposal June 11, 2009 Advisor: Vishwani D. Agrawal Committee Members: Fa F. Dai Victor P. Nelson Adit D. Singh

Outline • • • Overview Background Built-in Test and Calibration Approach Current Progress Future Work Conclusion Wei Jiang General Oral Examination 2

Overview • Issues – Parameter deviation – Process variation • Problem – Design variation-tolerant process-independent technique for mixed-signal devices • Approach – Test and characterization of mixed-signal devices – Output calibration Wei Jiang General Oral Examination 3

Mixed-signal Device • Analog and digital circuitry • Digital controllable • Typical devices – Converters, digital-to-analog/analog-to-digital – Amplifier Wei Jiang General Oral Examination 4

Testing of Mixed-signal Devices • Defects and faults – Catastrophic faults (hard faults) – Parametric faults (soft faults) • Test approaches – Functional test (specification oriented) – Structural test (defect oriented) Wei Jiang General Oral Examination 5

Challenges • Analog circuitry – No convincing fault models – Difficult to identify faults – Device parameters more susceptible to process variation than digital circuitry – Fault-free behavior based on a known range of acceptable values for component parameters • Large statistical process variation effects in deep sub-micron MOSFET devices Wei Jiang General Oral Examination 6

Process Variation • Parameter variation in nanoscale process • Yield, reliability and cost • Feature size scaling down and performance improvement • Effects on digital and analog circuitry – Analog circuitry more affected by process variation – Parameter deviation severed in nanoscale process – System performance degraded when parameter Wei Jiang General Oral Examination deviation exceeds beyond tolerant limits 7

Outline • • • Overview Background Built-in Test and Calibration Approach Current Progress Future Work Conclusion Wei Jiang General Oral Examination 8

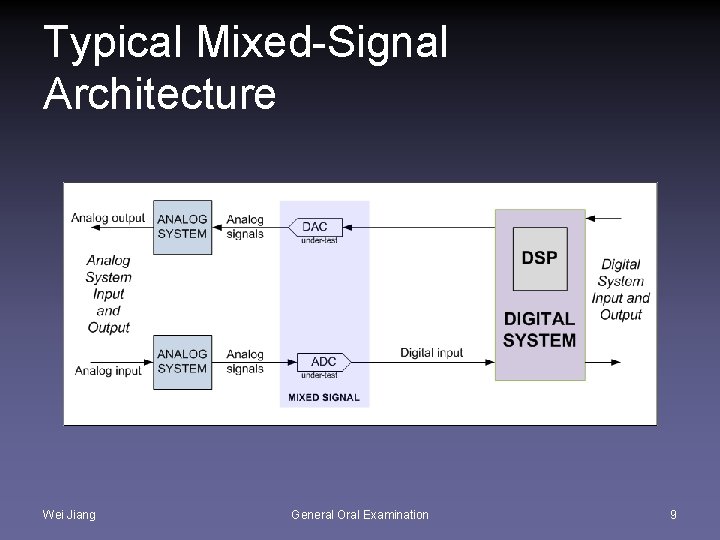

Typical Mixed-Signal Architecture Wei Jiang General Oral Examination 9

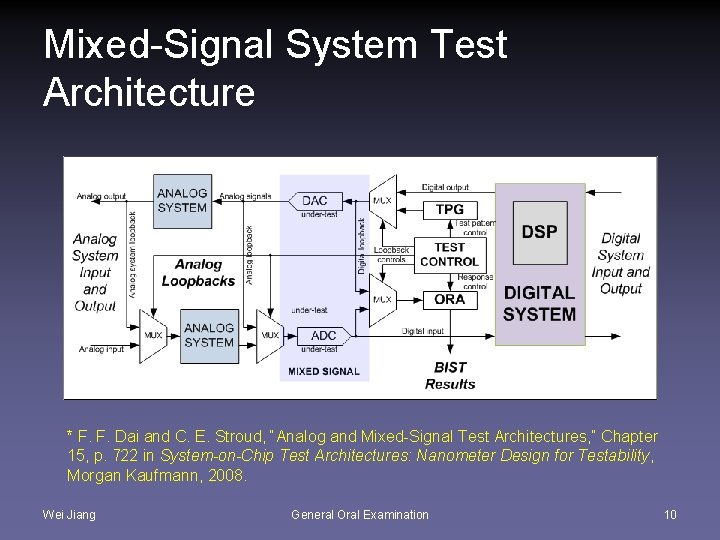

Mixed-Signal System Test Architecture * F. F. Dai and C. E. Stroud, “Analog and Mixed-Signal Test Architectures, ” Chapter 15, p. 722 in System-on-Chip Test Architectures: Nanometer Design for Testability, Morgan Kaufmann, 2008. Wei Jiang General Oral Examination 10

Mixed-Signal System Test Architecture • Digital system – – Digital I/O Digital signal processor (DSP) TPG and ORA and test control unit Digital loopback • Mixed-signal system – DAC and ADC – Analog loopback • Analog system – Analog circuitry – Analog signal I/O – Analog I/O loopback Wei Jiang General Oral Examination 11

Test Criteria • Digital circuitry test – Defect-oriented test – Defects cat be detected by wrong output response for specific test pattern • Analog circuitry test – Specific-oriented test – Parameter deviations vs. the acceptable tolerant limit Wei Jiang General Oral Examination 12

Typical Mixed-Signal Devices • DAC – digital-to-analog converter – Digital inputs; analog outputs • ADC – analog-to-digital converter – Analog inputs; digital inputs • Digital Controlled Amplifier – Analog inputs/outputs with digital controlling inputs – Analog transfer function controlled by digital device, e. g. microcontroller – Gain/distortion/nonlinearity respond to digital controlling signal Wei Jiang General Oral Examination 13

Existing Testing Approach • Oscillation BIST • LFSR-based TPG • FFT-based BIST Wei Jiang General Oral Examination 14

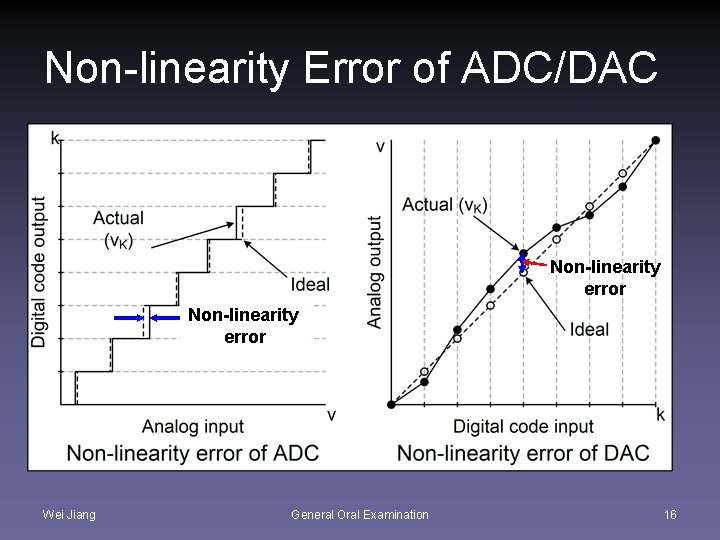

Linearity Problem • LSB – least significant bit – The minimum measurement for of analog value – Represented by 1 digital bit • Non-linearity Error – DNL – differential non-linearity – INL – integral non-linearity Wei Jiang General Oral Examination 15

Non-linearity Error of ADC/DAC Non-linearity error Wei Jiang General Oral Examination 16

Other Characteristics • Frequency response – Bandwidth • Noise – SNR – signal-to-noise ratio – SINAD – signal-to-noise and distortion ratio • Offset, gain, harmonic distortion • Intermodulation distortion Wei Jiang General Oral Examination 17

Outline • • • Overview Background Built-in Test and Calibration Approach Current Progress Future Work Conclusion Wei Jiang General Oral Examination 18

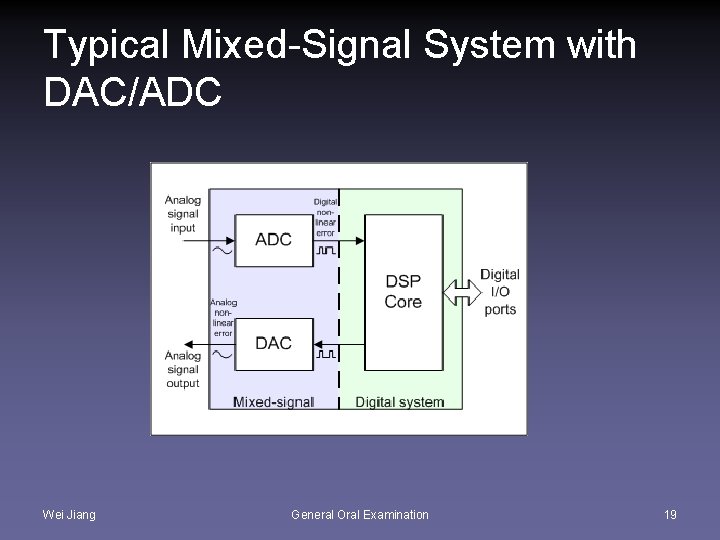

Typical Mixed-Signal System with DAC/ADC Wei Jiang General Oral Examination 19

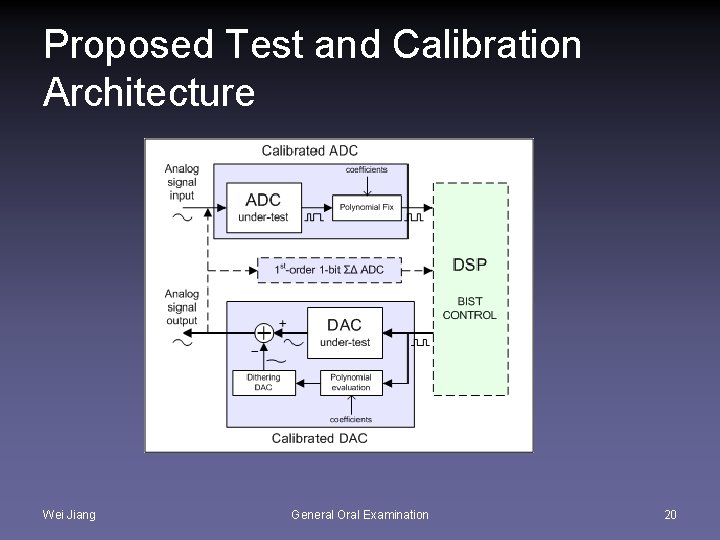

Proposed Test and Calibration Architecture Wei Jiang General Oral Examination 20

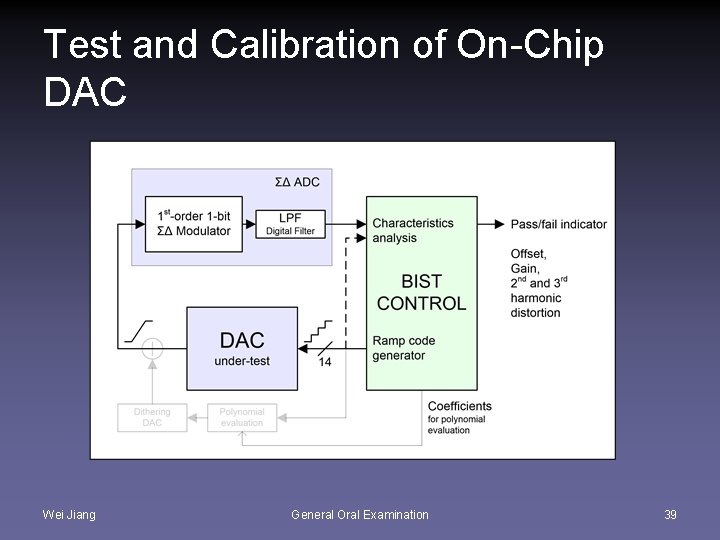

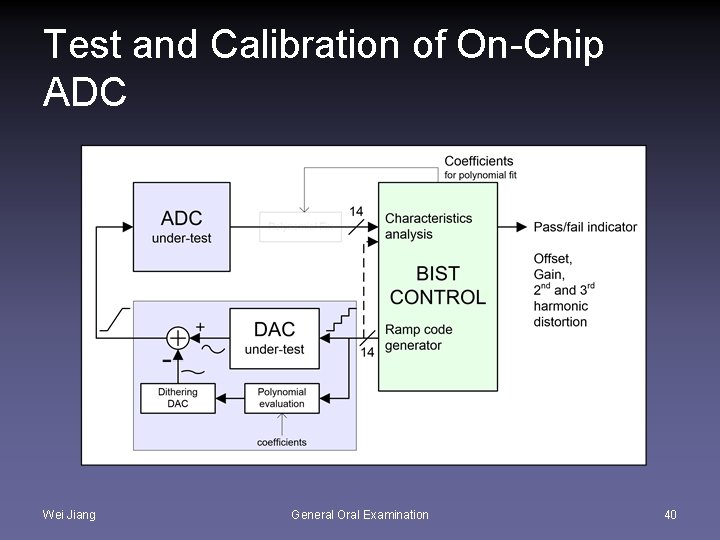

Components Description • Digital circuitry (including DSP) as BIST control unit – Test pattern generation (TPG) and output response analysis (ORA) • Measuring ADC – First-order 1 -bit Sigma-Delta modulator – Digital low-pass filter – Measuring outputs of DAC-under-test • Dither DAC – Low resolution DAC – Generating correcting signal for calibration – Calibrated DAC for test of ADC-under-test • ADC Polynomial Fix – Digital process to revise ADC output codes Wei Jiang General Oral Examination 21

Testing Procedure • Self-test of testing and calibrating components – Self-test of BIST control unit (including DSP, TPG/ORA) – Self-test of measuring ADC – Test of dithering DAC by measuring ADC • Test of On-chip DAC – Ramp test of on-chip DAC – Characterizing on-chip DAC by DSP – Calibration of on-chip DAC by dithering DAC • Test of on-chip ADC – Ramp test of on-chip ADC – Characterizing and fixing on-chip ADC outputs by DSP Wei Jiang General Oral Examination 22

Faulty Mixed-Signal Circuitry • Good circuitry – All parameters and characteristics are within pre-defined specified range • Fault-tolerant factor – Post-fabrication and software-controllable – Fault-tolerant factor varies for different application – Trade-off between fault-tolerance of parameter deviation and calibration resolution Wei Jiang General Oral Examination 23

Determine Faulty DAC/ADC • Coefficients representing offset, gain and harmonic distortion exceeding specific limit • Maximum INL error exceeding calibration range (depending on fault-tolerant factor) – ± 4 LSB for fault-tolerant factor 3 • INL errors of all calibrated outputs must be within ± 0. 5 LSB Wei Jiang General Oral Examination 24

Device Test and Calibration • During BIST – Test DAC/ADC with ramp signals – Measure response of each test code – Obtain INL error for each code – Characterize device by INL error • After BIST – Determine faulty devices by deviation of parameters – Generate correcting signal/data (identical to INL error) for each code – Calibrate DAC/ADC output using correcting signal/data by removing INL error Wei Jiang General Oral Examination 25

The ONLY Problem • Storing all INL errors for every input code of DAC/ADC is impossible – Requiring huge amount of memory – Needing lots of access time to retrieve specific data from memory – Prohibiting cost • Solution – Polynomial fitting – Storing several coefficients instead of all data Wei Jiang General Oral Examination 26

Test Pattern • Test pattern – Ramp code – Least value to most value – Testing time for each pattern depends on the converting speed of measuring ADC • Single-tone and multi-tone test patterns can also be used Wei Jiang General Oral Examination 27

Test of Digital Circuitry • Conventional digital BIST technology • LFSR-based random test; Scan-based deterministic test • Digital loopback conducted • Fault-free digital circuitry then used for mixed-signal test • May be hardware- or software-based Wei Jiang General Oral Examination 28

Measuring ADC • First-order 1 -bit sigma-delta ADC • Perform self-test before any other mixedsignal test • Make sure each components of sigmadelta ADC working • Quantization noise • Bit-stream output pattern Wei Jiang General Oral Examination 29

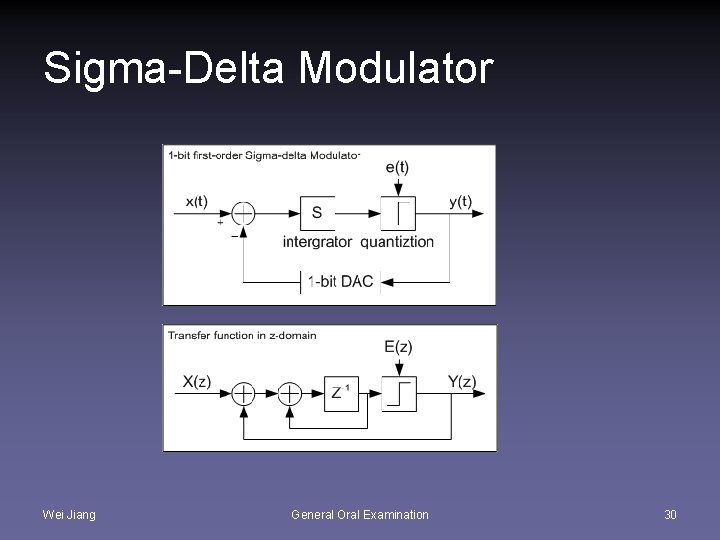

Sigma-Delta Modulator Wei Jiang General Oral Examination 30

Sigma-Delta Modulator (cont. ) • Advantage – Oversampling and noise-shaping – High resolution and linear results – Resolution depends on OSR (oversampling ratio) – Simple structure and low cost • Disadvantage – Very slow converting speed – Bit-stream output pattern issue for low-order modulation – Requiring high-speed clock • Higher order and/or multi-bit modulation Wei Jiang General Oral Examination 31

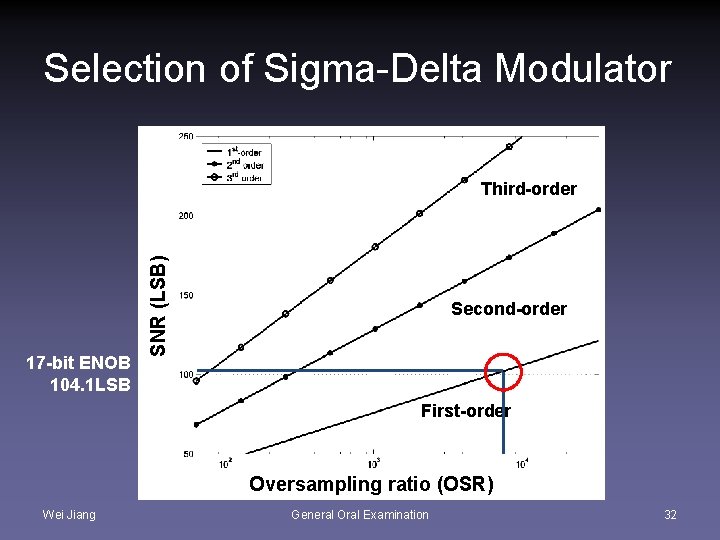

Selection of Sigma-Delta Modulator 17 -bit ENOB 104. 1 LSB SNR (LSB) Third-order Second-order First-order Oversampling ratio (OSR) Wei Jiang General Oral Examination 32

Digital Filter • Sigma-delta ADC consists of sigma-delta modulator and digital filter • Low-pass filter (LPF) • Integrator • Comb filter Wei Jiang General Oral Examination 33

Dithering DAC • Low-cost low-resolution DAC • Better linearity output with DEM technique • Must be tested by measuring ADC before test of on-chip mixed-signal devices Wei Jiang General Oral Examination 34

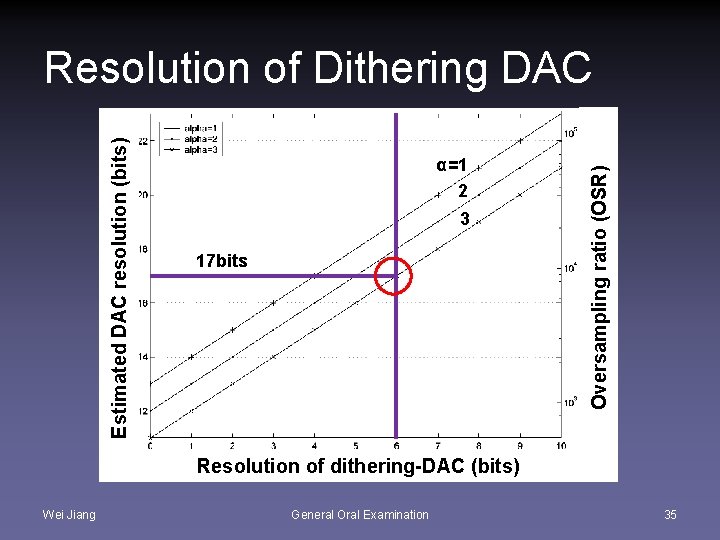

α=1 2 3 17 bits Oversampling ratio (OSR) Estimated DAC resolution (bits) Resolution of Dithering DAC Resolution of dithering-DAC (bits) Wei Jiang General Oral Examination 35

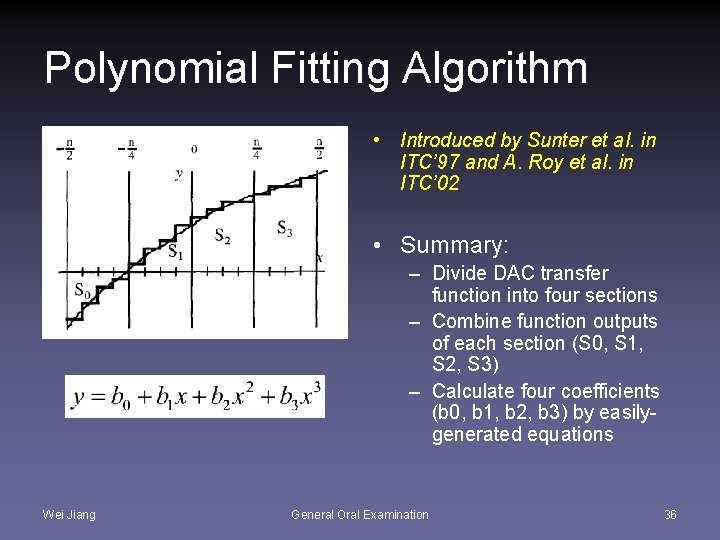

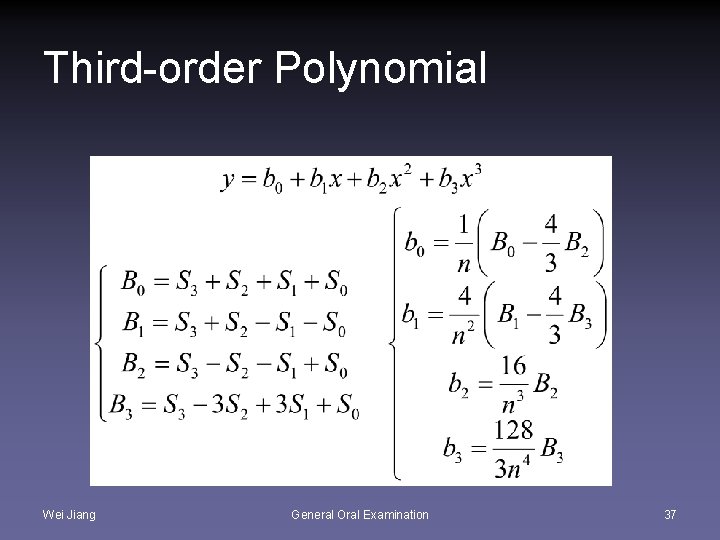

Polynomial Fitting Algorithm • Introduced by Sunter et al. in ITC’ 97 and A. Roy et al. in ITC’ 02 • Summary: – Divide DAC transfer function into four sections – Combine function outputs of each section (S 0, S 1, S 2, S 3) – Calculate four coefficients (b 0, b 1, b 2, b 3) by easilygenerated equations Wei Jiang General Oral Examination 36

Third-order Polynomial Wei Jiang General Oral Examination 37

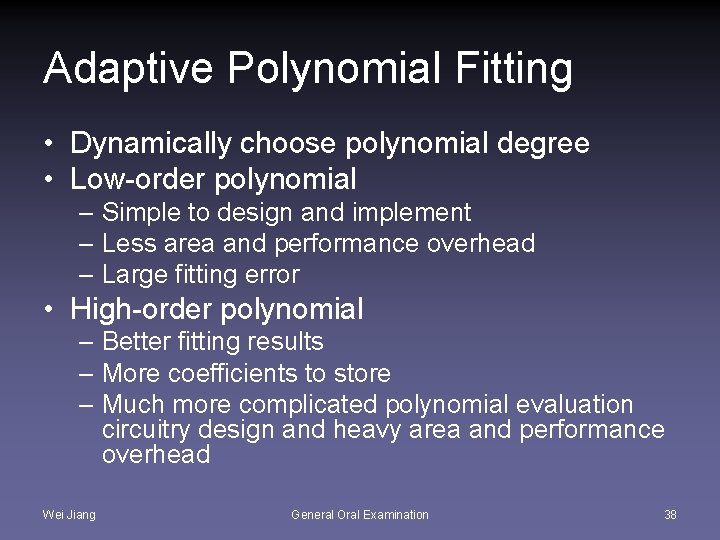

Adaptive Polynomial Fitting • Dynamically choose polynomial degree • Low-order polynomial – Simple to design and implement – Less area and performance overhead – Large fitting error • High-order polynomial – Better fitting results – More coefficients to store – Much more complicated polynomial evaluation circuitry design and heavy area and performance overhead Wei Jiang General Oral Examination 38

Test and Calibration of On-Chip DAC Wei Jiang General Oral Examination 39

Test and Calibration of On-Chip ADC Wei Jiang General Oral Examination 40

General Mixed-Signal Test • • • Variation-tolerant design Digital controlled BIST Digitalized TPG/ORA Self-testable measuring components Characterization of device-under-test by DSP Faulty circuitry determined by characterized parameters • Coefficients of output fix/correction signals calculated by DSP Wei Jiang General Oral Examination 41

Outline • • • Overview Background Built-in Test and Calibration Approach Current Progress Future Work Conclusion Wei Jiang General Oral Examination 42

Publications • W. Jiang and V. D. Agrawal, “Built-In Test and Calibration of DAC/ADC Using A Low-Resolution Dithering DAC, ” NATW’ 08, pp. 61 -68. • W. Jiang and V. D. Agrawal, “Built-in Self. Calibration of On-Chip DAC and ADC, ” ITC’ 08, paper 32. 2. • W. Jiang and V. D. Agrawal, “Built-in Adaptive Test and Calibration of DAC, ” NATW’ 09, pp. 3 -8. • W. Jiang and V. D. Agrawal, “Designing Variation. Tolerance in Mixed-Signal Components of a System-on-Chip, ” ISCAS’ 09, pp. 126 -129. Wei Jiang General Oral Examination 43

Progress • Presenting a novel approach to test and calibration DAC/ADC • Presenting a method to dynamically determine the order of curve fitting polynomial for INL errors • Proved by Matlab simulation theoretically • Applicable for digitally controllable mixedsignal devices Wei Jiang General Oral Examination 44

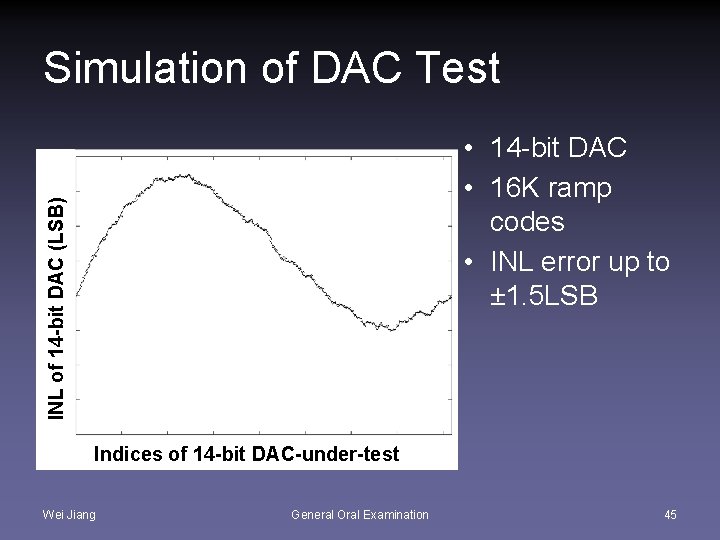

Simulation of DAC Test INL of 14 -bit DAC (LSB) • 14 -bit DAC • 16 K ramp codes • INL error up to ± 1. 5 LSB Indices of 14 -bit DAC-under-test Wei Jiang General Oral Examination 45

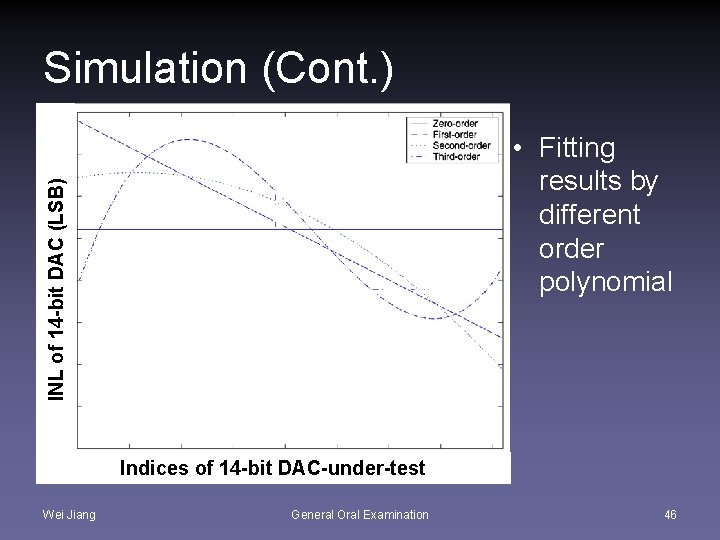

Simulation (Cont. ) INL of 14 -bit DAC (LSB) • Fitting results by different order polynomial Indices of 14 -bit DAC-under-test Wei Jiang General Oral Examination 46

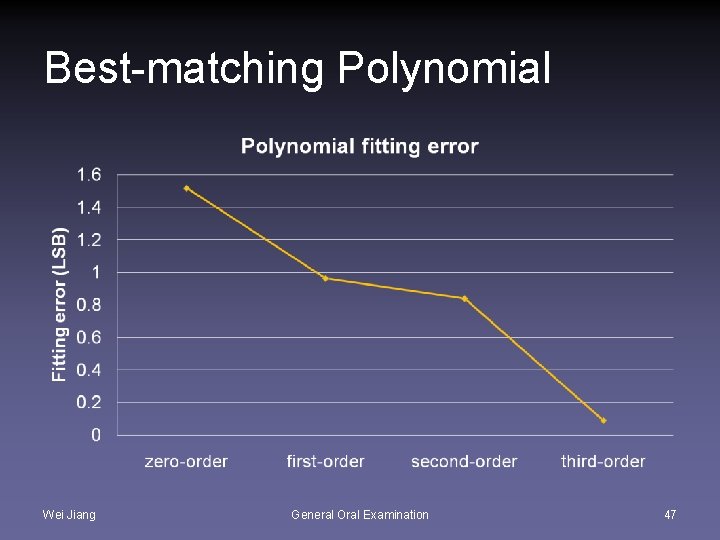

Best-matching Polynomial Wei Jiang General Oral Examination 47

Fitting Algorithm • Third-order polynomial fitting algorithm • Adaptive polynomial fitting algorithm • Determination of best matching polynomial degree Wei Jiang General Oral Examination 48

Measuring ADC / Dithering DAC • Measuring ADC – First-order 1 -bit Sigma-Delta ADC – Higher-order multi-bit Sigma-Delta ADC – Non-Sigma-Delta ADC – Digital low-pass filter • Dithering DAC – Binary weighted DAC Wei Jiang General Oral Examination 49

Current Tasks • Modeling and hardware verification of proposed testing approach • Programming of third-order polynomial fitting algorithm • Implementation and optimization of digital polynomial evaluation circuit • Design and verification of the whole test and calibration system Wei Jiang General Oral Examination 50

Outline • • • Overview Background Built-in Test and Calibration Approach Current Progress Future Work Conclusion Wei Jiang General Oral Examination 51

Future Tasks and Schedule • • • Testability of measuring ADC (~2 months) Best matching polynomial (~2 months) At-speed characterization (~1 month) Dynamic Element Matching (~1 month) Other testing techniques (~2 months) Dissertation and defending (~2 months) Wei Jiang General Oral Examination 52

Testability of Measuring ADC • Measuring ADC must be self-testable • Testability of Sigma-Delta modulator • Problem – Using digital circuitry and DSP to test analog circuitry – Measuring ADC must tell faulty or healthy by itself – Test of measuring ADC must be done before test of all other mixed-signal components Wei Jiang General Oral Examination 53

Best Matching Polynomial • Degree determination of best matching polynomial • Problem – Find cut-off degree of INL errors – Higher-order polynomial brings heavy hardware overhead – Lower-order polynomial gives more fitting error Wei Jiang General Oral Examination 54

At-Speed Characterization • An approach to utilize idle time of DSP to recalibrate mixed-signal devices • Performance of analog components varies by environment, i. e. temperature, usage time • Characterization during boot time may be inaccurate and need continuous revision during its lifetime • Dynamic re-characterization of mixed-signal devices may reflect real condition of the devices and generate better results Wei Jiang General Oral Examination 55

Dynamic Element Matching (DEM) • Reduce non-linearity error of DAC/ADC • Fault-tolerant for analog elements • Approaches – Dynamically change/rotate matching elements to generate desired outputs for specific inputs – Reduce non-linearity of mismatching elements • Disadvantage – Output pattern issue for low-order matching algorithm – Requiring high-speed clock Wei Jiang General Oral Examination 56

Other Things… • • Frequency response test Noise test and removal Delay test Single-tone and multi-tone test Wei Jiang General Oral Examination 57

Outline • • • Overview Background Built-in Test and Calibration Approach Current Progress Future Work Conclusion Wei Jiang General Oral Examination 58

Conclusion • A post-fabrication built-in test and calibration approach for mixed-signal devices is proposed • This approach relies on digital circuitry and DSP for TPG/ORA and BIST control • Digital circuitry is testable by conventional digital testing approaches and therefore guarantee the testability of analog circuitry • The approach has been applied to test of DAC/ADC • The same idea can be widely used for other digitalcontrolled mixed-signal devices • Calibration on mixed-signal devices will significantly reduce defects, improve die yield and lower manufacturing cost Wei Jiang General Oral Examination 59

THANKS Q&A Wei Jiang General Oral Examination 60

- Slides: 60