BuiltIn SelfTest of Programmable IO Cells in Virtex4

Built-In Self-Test of Programmable I/O Cells in Virtex-4 FPGAs Bradley F. Dutton, Lee W. Lerner, and Charles E. Stroud Dept. of Electrical & Computer Engineering Auburn University B. Dutton 5/15/08 North Atlantic Test Workshop

Outline of Presentation q. Previous Work q. Overview of Virtex-4 I/O Tiles q. Virtex-4 I/O BIST architecture v. ILOGIC/OLOGIC (input/output logic) v. SERDES (serialization/deserialization) v. I/O Standards q. Capabilities and Limitations q. Conclusion B. Dutton 5/15/08 North Atlantic Test Workshop 2

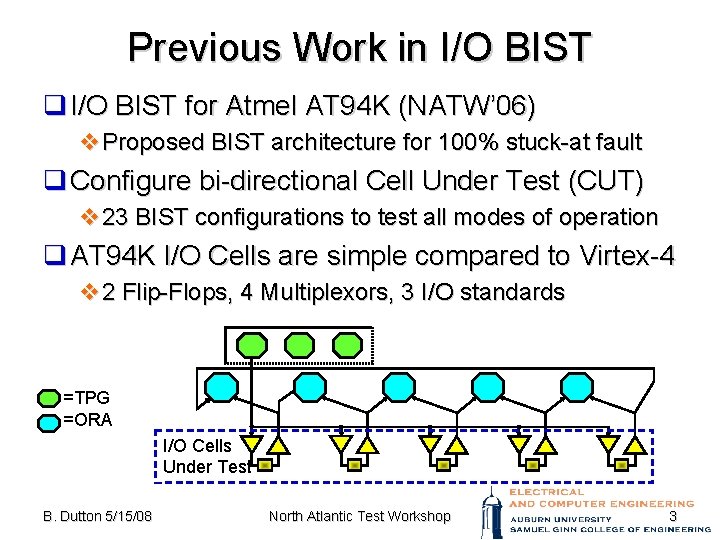

Previous Work in I/O BIST q I/O BIST for Atmel AT 94 K (NATW’ 06) v. Proposed BIST architecture for 100% stuck-at fault q Configure bi-directional Cell Under Test (CUT) v 23 BIST configurations to test all modes of operation q AT 94 K I/O Cells are simple compared to Virtex-4 v 2 Flip-Flops, 4 Multiplexors, 3 I/O standards =TPG =ORA I/O Cells Under Test B. Dutton 5/15/08 North Atlantic Test Workshop 3

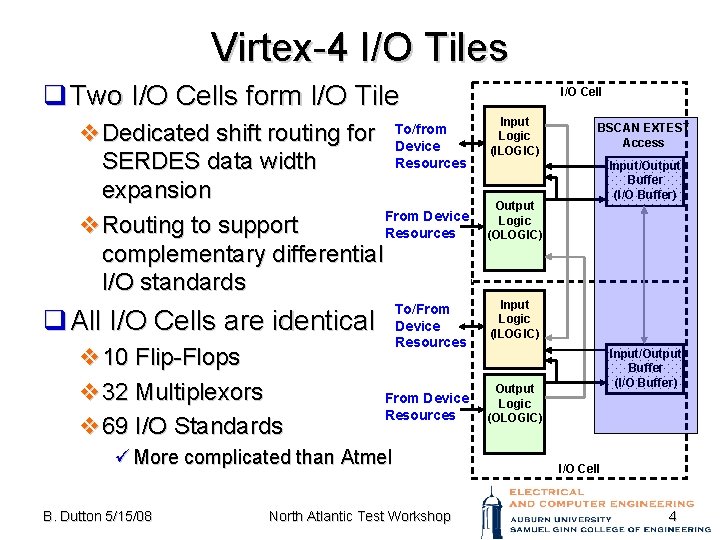

Virtex-4 I/O Tiles q Two I/O Cells form I/O Tile v. Dedicated shift routing for SERDES data width expansion From Device v. Routing to support Resources complementary differential I/O standards To/from Device Resources To/From Device Resources q All I/O Cells are identical v 10 Flip-Flops v 32 Multiplexors v 69 I/O Standards From Device Resources ü More complicated than Atmel B. Dutton 5/15/08 North Atlantic Test Workshop I/O Cell Input Logic (ILOGIC) BSCAN EXTEST Access Input/Output Buffer (I/O Buffer) Output Logic (OLOGIC) Input Logic (ILOGIC) Input/Output Buffer (I/O Buffer) Output Logic (OLOGIC) I/O Cell 4

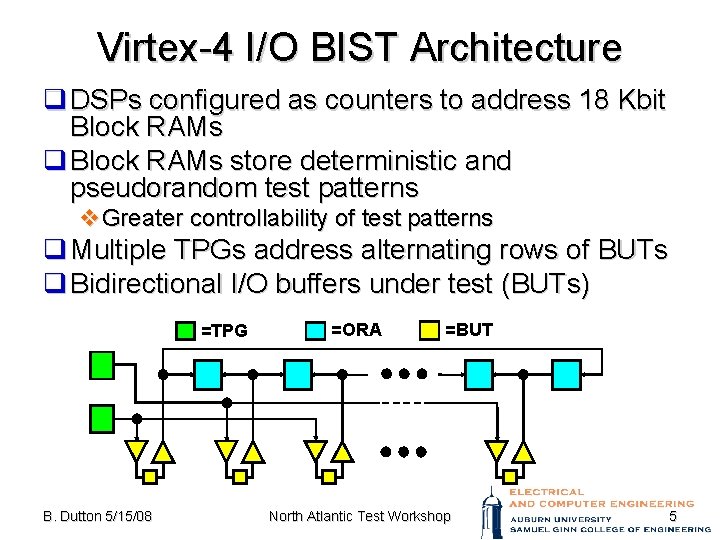

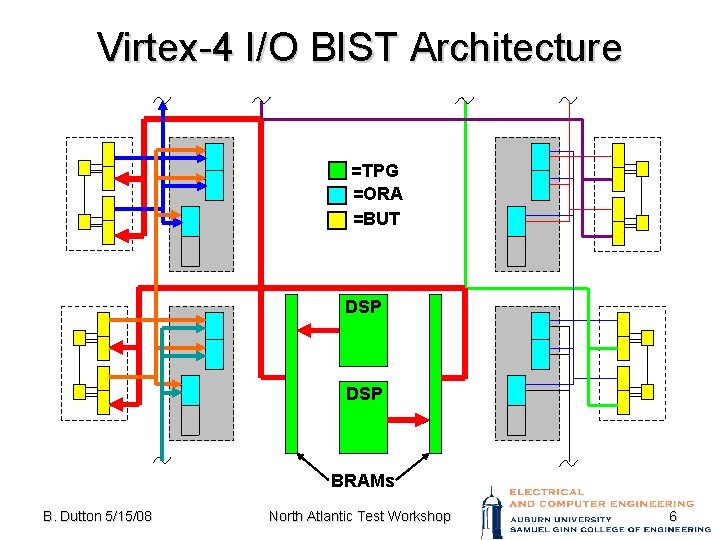

Virtex-4 I/O BIST Architecture q DSPs configured as counters to address 18 Kbit Block RAMs q Block RAMs store deterministic and pseudorandom test patterns v. Greater controllability of test patterns q Multiple TPGs address alternating rows of BUTs q Bidirectional I/O buffers under test (BUTs) =TPG B. Dutton 5/15/08 =ORA =BUT North Atlantic Test Workshop 5

Virtex-4 I/O BIST Architecture =TPG =ORA =BUT DSP BRAMs B. Dutton 5/15/08 North Atlantic Test Workshop 6

ILOGIC/OLOGIC Fault Coverage q. Can only test bi-directional buffer modes v. Two undetected faults result B. Dutton 5/15/08 North Atlantic Test Workshop 7

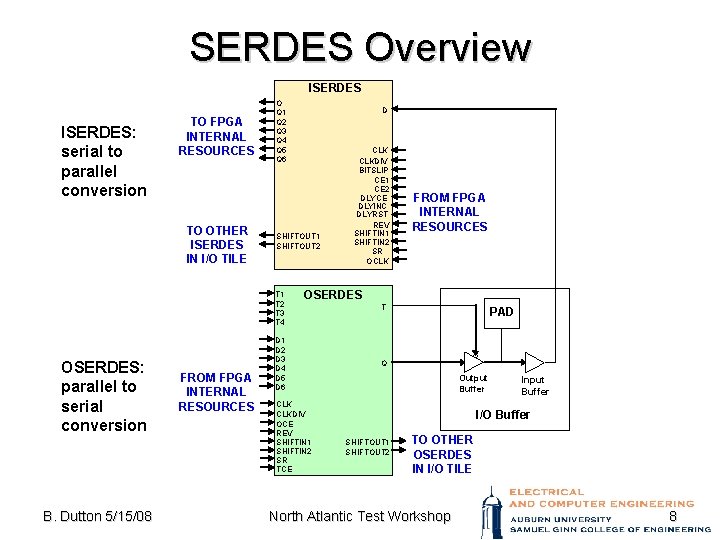

SERDES Overview ISERDES: serial to parallel conversion TO FPGA INTERNAL RESOURCES TO OTHER ISERDES IN I/O TILE O Q 1 Q 2 Q 3 Q 4 Q 5 Q 6 SHIFTOUT 1 SHIFTOUT 2 T 1 T 2 T 3 T 4 OSERDES: parallel to serial conversion B. Dutton 5/15/08 FROM FPGA INTERNAL RESOURCES D CLKDIV BITSLIP CE 1 CE 2 DLYCE DLYINC DLYRST REV SHIFTIN 1 SHIFTIN 2 SR OCLK FROM FPGA INTERNAL RESOURCES OSERDES D 1 D 2 D 3 D 4 D 5 D 6 CLKDIV OCE REV SHIFTIN 1 SHIFTIN 2 SR TCE T PAD Q Output Buffer Input Buffer I/O Buffer SHIFTOUT 1 SHIFTOUT 2 TO OTHER OSERDES IN I/O TILE North Atlantic Test Workshop 8

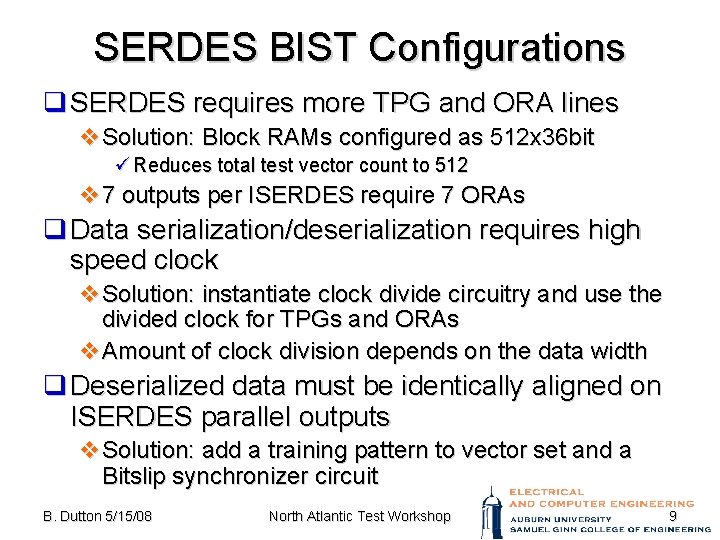

SERDES BIST Configurations q SERDES requires more TPG and ORA lines v. Solution: Block RAMs configured as 512 x 36 bit ü Reduces total test vector count to 512 v 7 outputs per ISERDES require 7 ORAs q Data serialization/deserialization requires high speed clock v. Solution: instantiate clock divide circuitry and use the divided clock for TPGs and ORAs v. Amount of clock division depends on the data width q Deserialized data must be identically aligned on ISERDES parallel outputs v. Solution: add a training pattern to vector set and a Bitslip synchronizer circuit B. Dutton 5/15/08 North Atlantic Test Workshop 9

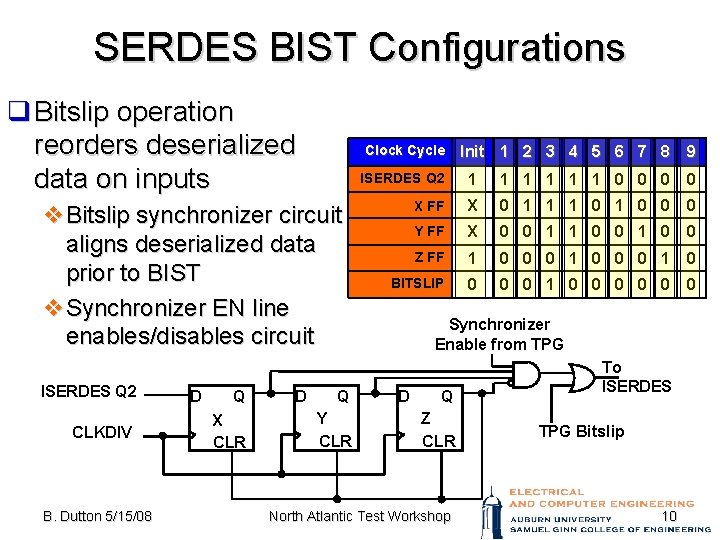

SERDES BIST Configurations q Bitslip operation reorders deserialized data on inputs Clock Cycle v. Bitslip synchronizer circuit aligns deserialized data prior to BIST v. Synchronizer EN line enables/disables circuit ISERDES Q 2 CLKDIV B. Dutton 5/15/08 D Q X CLR D Q Y CLR Init 1 2 3 4 5 6 7 8 9 ISERDES Q 2 1 1 1 0 0 X FF X 0 1 1 1 0 0 0 Y FF X 0 0 1 1 0 0 Z FF 1 0 0 0 1 0 BITSLIP 0 0 0 1 0 0 0 Synchronizer Enable from TPG D Q Z CLR North Atlantic Test Workshop To ISERDES TPG Bitslip 10

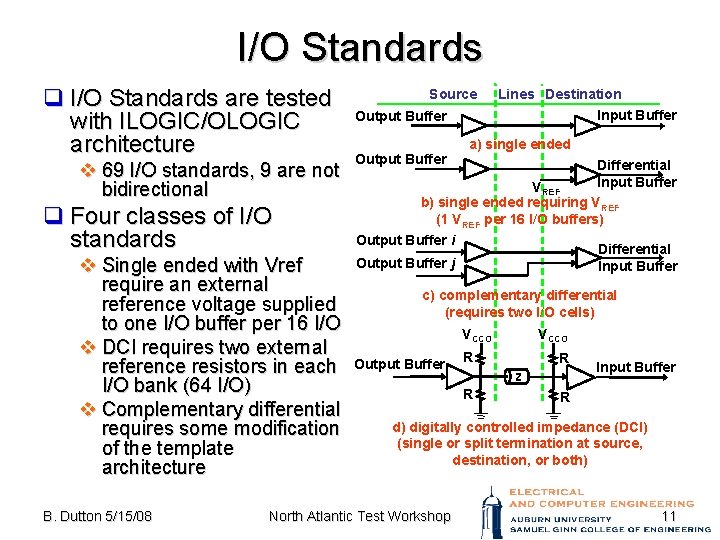

I/O Standards q I/O Standards are tested with ILOGIC/OLOGIC architecture v 69 I/O standards, 9 are not bidirectional q Four classes of I/O standards v Single ended with Vref require an external reference voltage supplied to one I/O buffer per 16 I/O v DCI requires two external reference resistors in each I/O bank (64 I/O) v Complementary differential requires some modification of the template architecture B. Dutton 5/15/08 Source Output Buffer Lines Destination Input Buffer a) single ended Differential Input Buffer VREF b) single ended requiring VREF (1 VREF per 16 I/O buffers) Output Buffer i Differential Output Buffer j Input Buffer c) complementary differential (requires two I/O cells) VCCO Output Buffer VCCO R R z R Input Buffer R d) digitally controlled impedance (DCI) (single or split termination at source, destination, or both) North Atlantic Test Workshop 11

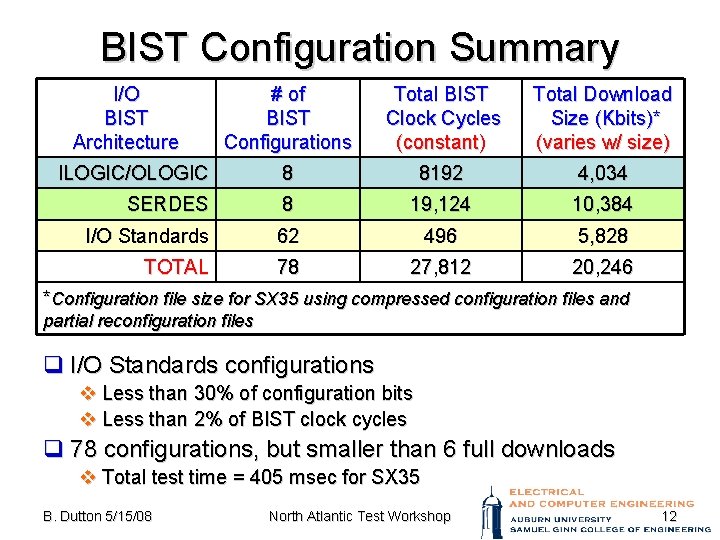

BIST Configuration Summary I/O BIST Architecture # of BIST Configurations Total BIST Clock Cycles (constant) Total Download Size (Kbits)* (varies w/ size) ILOGIC/OLOGIC 8 8192 4, 034 SERDES 8 19, 124 10, 384 I/O Standards 62 496 5, 828 TOTAL 78 27, 812 20, 246 *Configuration file size for SX 35 using compressed configuration files and partial reconfiguration files q I/O Standards configurations v Less than 30% of configuration bits v Less than 2% of BIST clock cycles q 78 configurations, but smaller than 6 full downloads v Total test time = 405 msec for SX 35 B. Dutton 5/15/08 North Atlantic Test Workshop 12

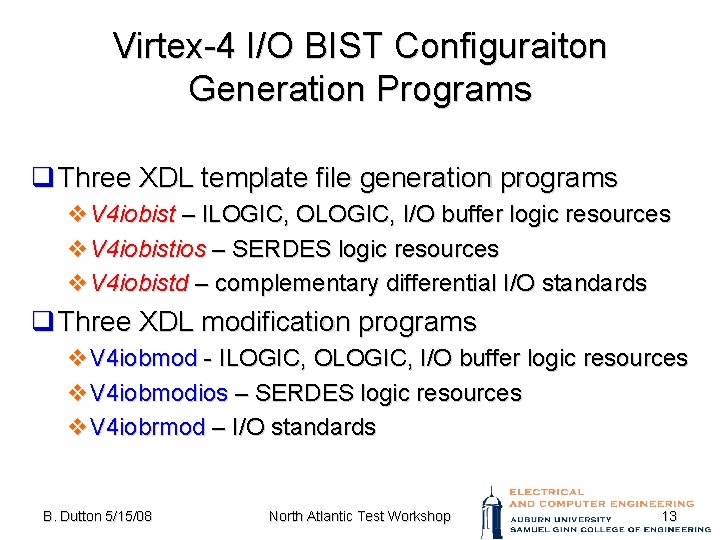

Virtex-4 I/O BIST Configuraiton Generation Programs q Three XDL template file generation programs v. V 4 iobist – ILOGIC, OLOGIC, I/O buffer logic resources v. V 4 iobistios – SERDES logic resources v. V 4 iobistd – complementary differential I/O standards q Three XDL modification programs v. V 4 iobmod - ILOGIC, OLOGIC, I/O buffer logic resources v. V 4 iobmodios – SERDES logic resources v. V 4 iobrmod – I/O standards B. Dutton 5/15/08 North Atlantic Test Workshop 13

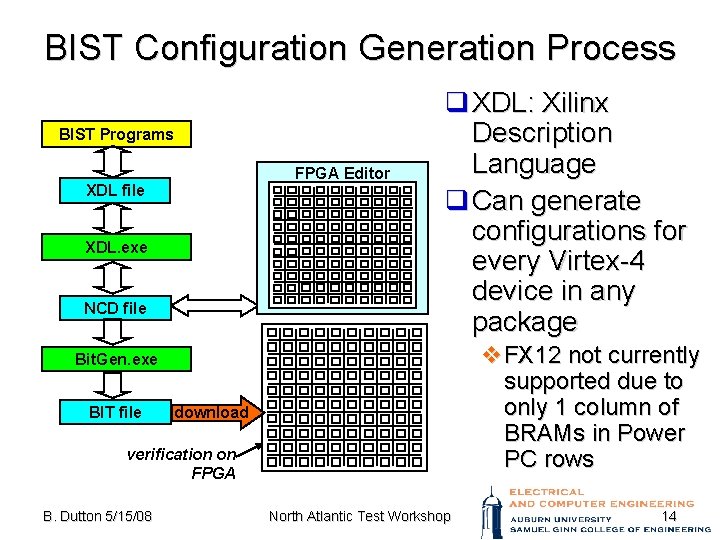

BIST Configuration Generation Process BIST Programs FPGA Editor XDL file XDL. exe NCD file q XDL: Xilinx Description Language q Can generate configurations for every Virtex-4 device in any package v. FX 12 not currently supported due to only 1 column of BRAMs in Power PC rows Bit. Gen. exe BIT file download verification on FPGA B. Dutton 5/15/08 North Atlantic Test Workshop 14

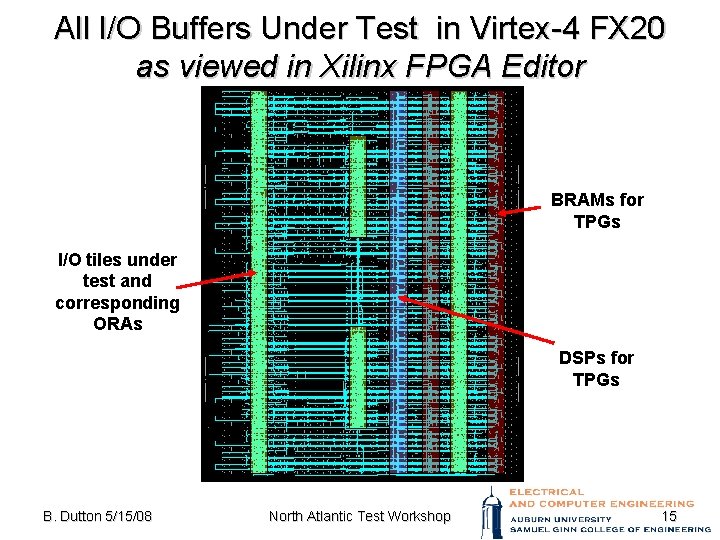

All I/O Buffers Under Test in Virtex-4 FX 20 as viewed in Xilinx FPGA Editor BRAMs for TPGs I/O tiles under test and corresponding ORAs DSPs for TPGs B. Dutton 5/15/08 North Atlantic Test Workshop 15

Summary q 3 architectures in 78 configurations to test I/O cells in every mode of operation v. ILOGIC/OLOGIC v. ISERDES/OSERDES v. I/O Standards q. Tests both bonded and unbonded I/O cells q. Can be used for manufacturing or system level testing v. Connecting devices should be tri-stated q. Allows for testing at system frequencies B. Dutton 5/15/08 North Atlantic Test Workshop 16

- Slides: 16