An IEEE 1149 7 Update Standard Reducedpin and

- Slides: 28

An IEEE 1149. 7 Update: Standard Reduced-pin and Enhanced-functionality Test Access Port and Boundary-Scan Architecture Adam W Ley ASSET Inter. Tech, Inc. BTW 2010 Sep 15

Acknowledgements Ø the P 1149. 7 working group Ø Stephen Lau of Texas Instruments Ø Gary Swoboda of Texas Instruments • who shall be recognized as the technical architect and principal author of 1149. 7 BTW 2010 2

Outline Ø What is IEEE 1149. 7? Ø IEEE 1149. 7 Key Objectives Ø How it Works • Selection Hierarchy • Capability Classes BTW 2010 3

What is IEEE 1149. 7? BTW 2010

What is IEEE 1149. 7 ? Ø Formally, Standard for Reduced-pin and Enhancedfunctionality Test Access Port and Boundary-Scan Architecture BTW 2010 6

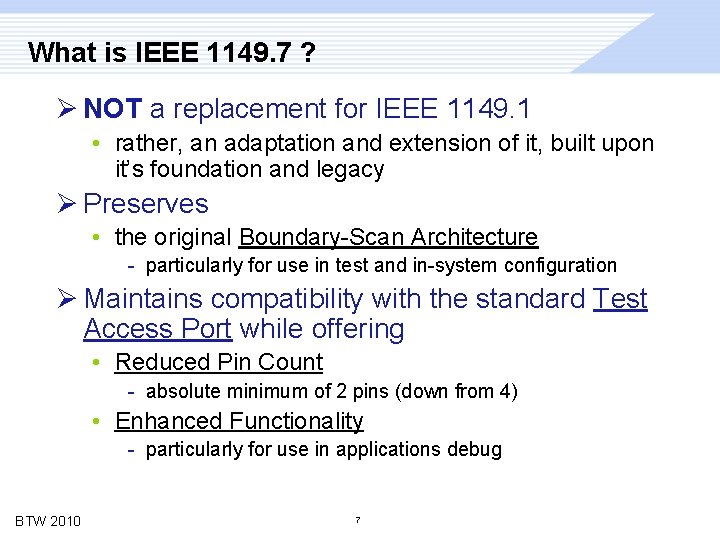

What is IEEE 1149. 7 ? Ø NOT a replacement for IEEE 1149. 1 • rather, an adaptation and extension of it, built upon it’s foundation and legacy Ø Preserves • the original Boundary-Scan Architecture - particularly for use in test and in-system configuration Ø Maintains compatibility with the standard Test Access Port while offering • Reduced Pin Count - absolute minimum of 2 pins (down from 4) • Enhanced Functionality - particularly for use in applications debug BTW 2010 7

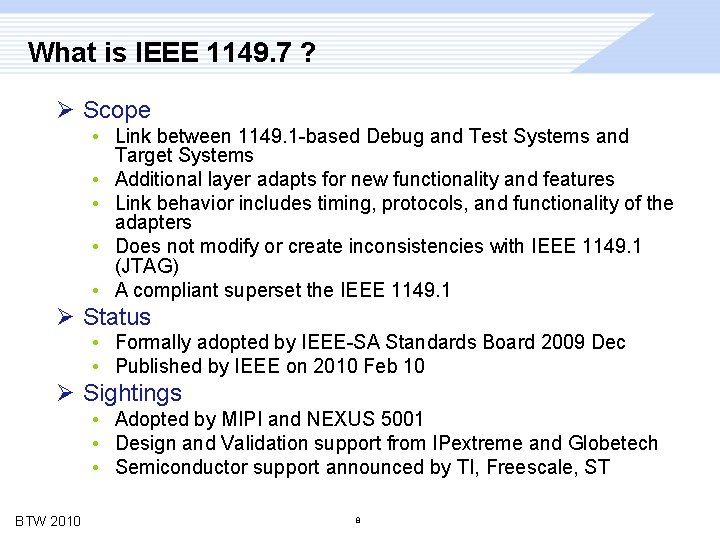

What is IEEE 1149. 7 ? Ø Scope • Link between 1149. 1 -based Debug and Test Systems and Target Systems • Additional layer adapts for new functionality and features • Link behavior includes timing, protocols, and functionality of the adapters • Does not modify or create inconsistencies with IEEE 1149. 1 (JTAG) • A compliant superset the IEEE 1149. 1 Ø Status • Formally adopted by IEEE-SA Standards Board 2009 Dec • Published by IEEE on 2010 Feb 10 Ø Sightings • Adopted by MIPI and NEXUS 5001 • Design and Validation support from IPextreme and Globetech • Semiconductor support announced by TI, Freescale, ST BTW 2010 8

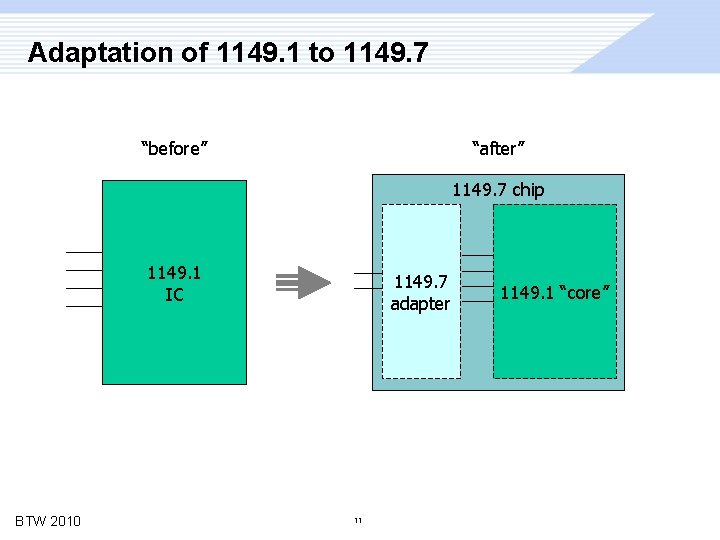

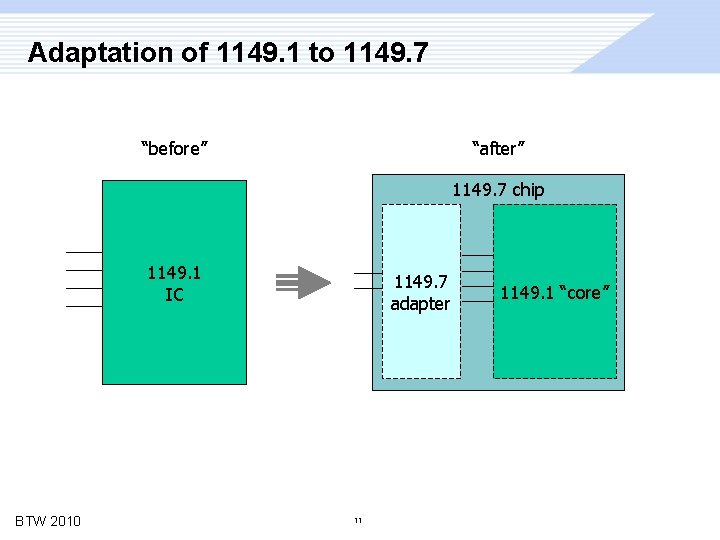

Adaptation of 1149. 1 to 1149. 7 “before” “after” 1149. 7 chip 1149. 1 IC BTW 2010 1149. 7 adapter 11 1149. 1 “core”

IEEE 1149. 7 Key Objectives BTW 2010

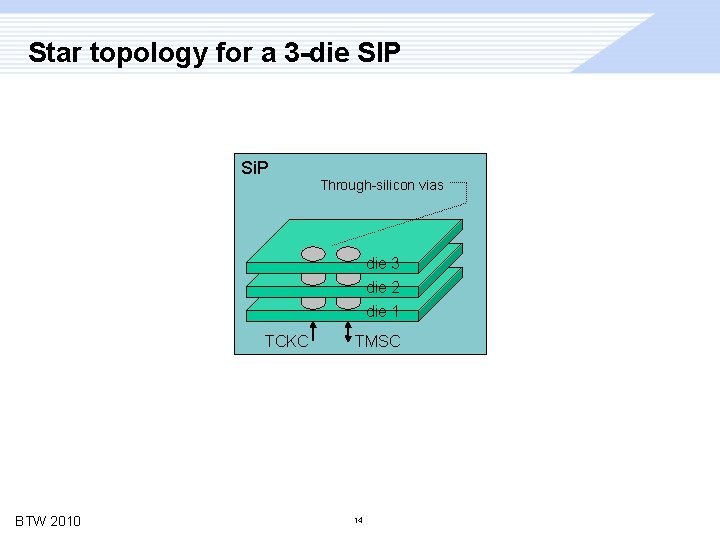

IEEE 1149. 7 Key Objectives Ø For Test • Maintain compliance with 1149. 1 to preserve the industry test infrastructure Ø For Applications Debug • Extend/ Advance capability to provide: - Reduced Power Modes – Defined test logic power down - Improved Performance – Shortened multi-chip chains – Glueless “star” configuration - Reduced Pins - Links to “Instrumentation” BTW 2010 13

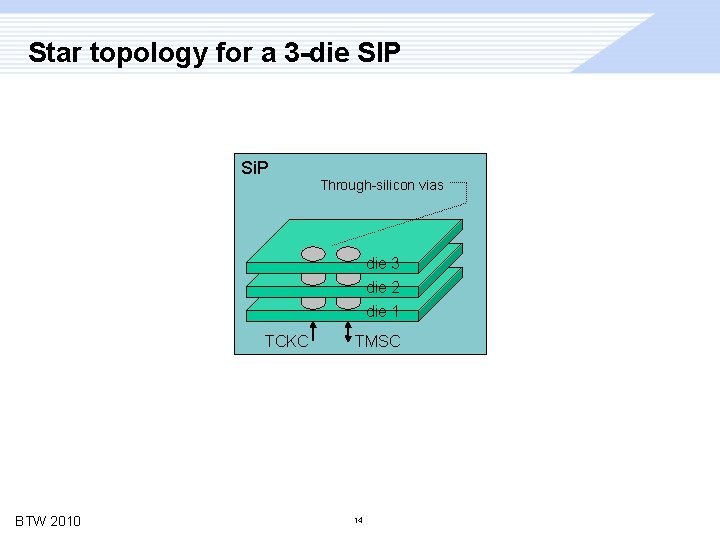

Star topology for a 3 -die SIP Si. P Through-silicon vias die 3 die 2 die 1 TCKC BTW 2010 TMSC 14

How it Works BTW 2010

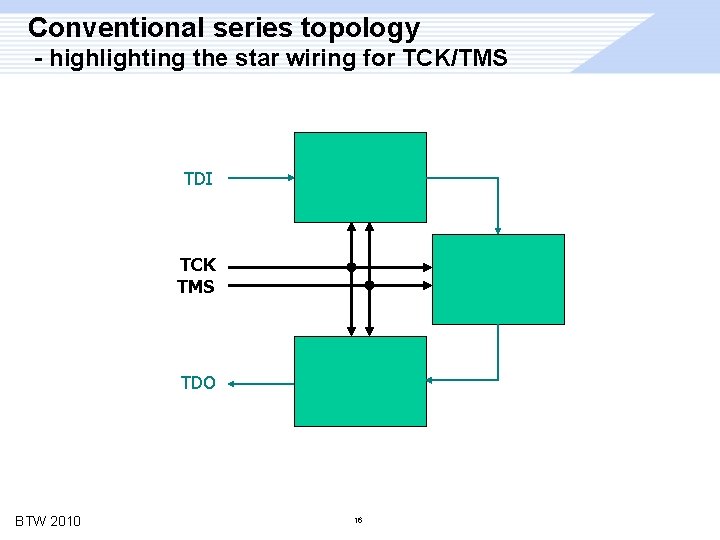

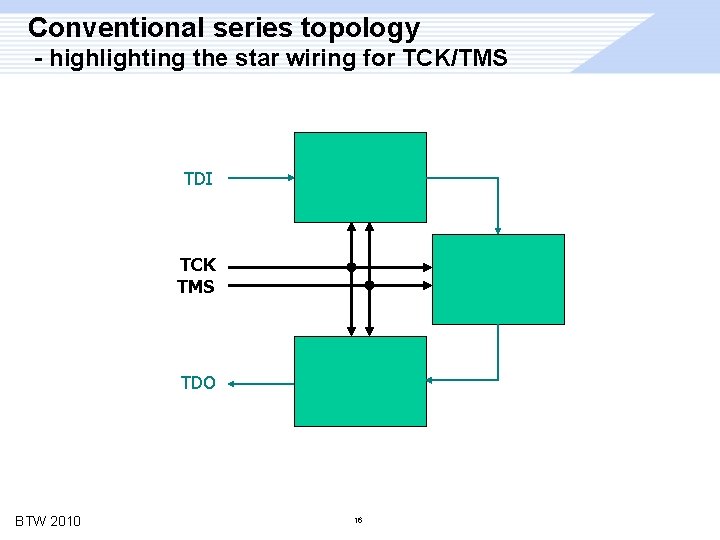

Conventional series topology - highlighting the star wiring for TCK/TMS TDI TCK TMS TDO BTW 2010 16

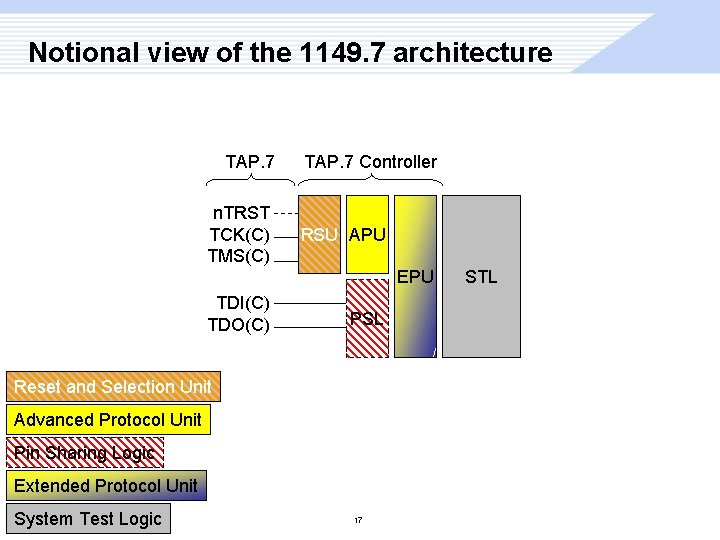

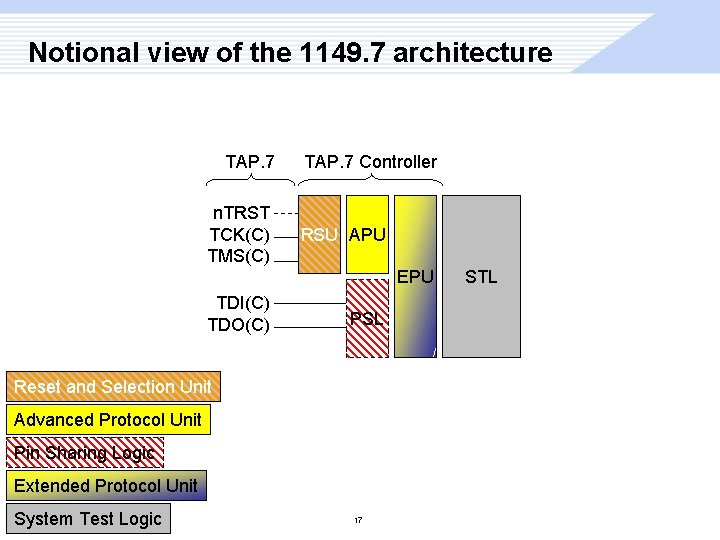

Notional view of the 1149. 7 architecture TAP. 7 n. TRST TCK(C) TMS(C) TAP. 7 Controller RSU APU EPU TDI(C) TDO(C) PSL Reset and Selection Unit Advanced Protocol Unit Pin Sharing Logic Extended Protocol Unit System BTW 2010 Test Logic 17 STL

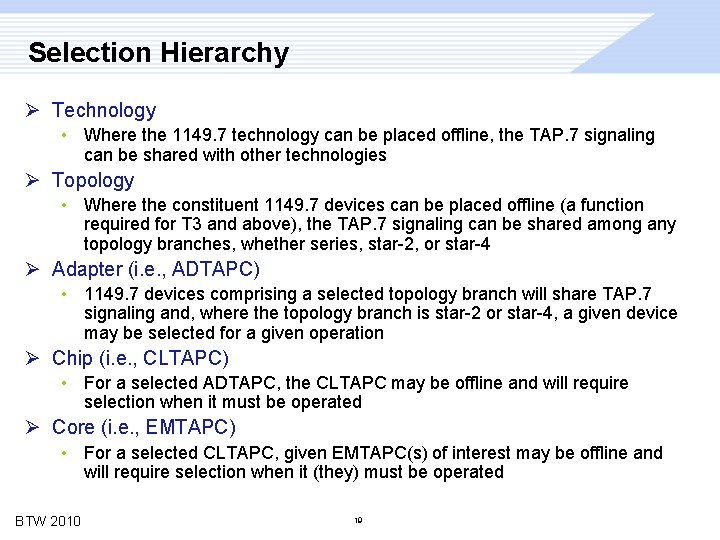

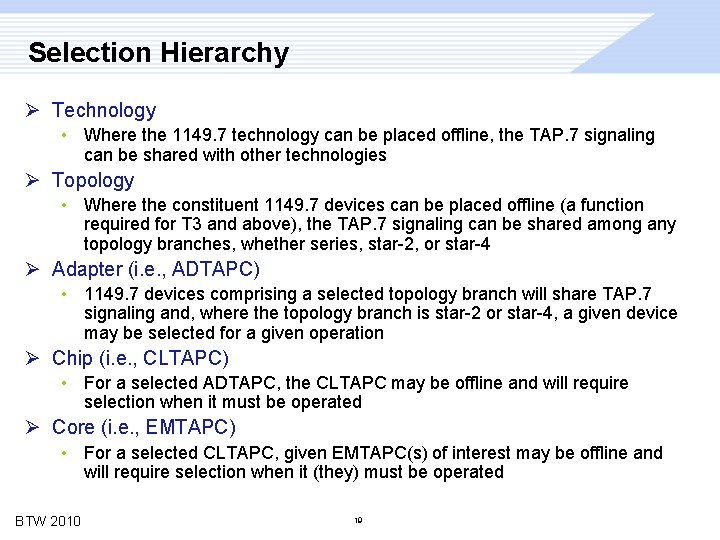

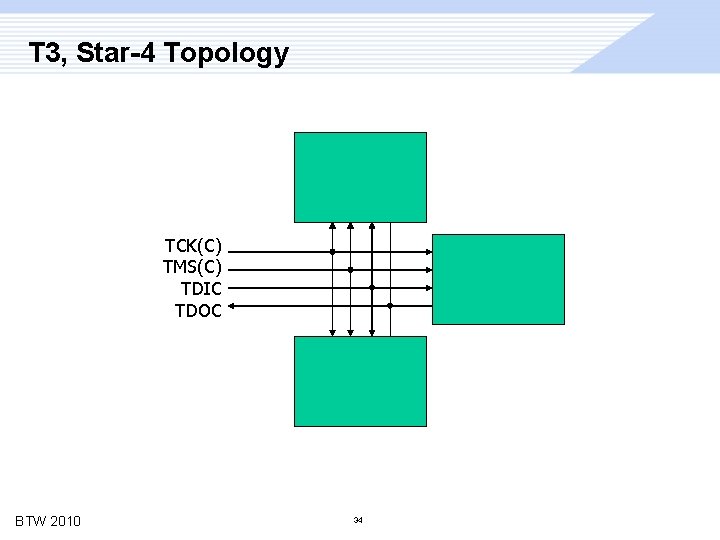

Selection Hierarchy Ø Technology • Where the 1149. 7 technology can be placed offline, the TAP. 7 signaling can be shared with other technologies Ø Topology • Where the constituent 1149. 7 devices can be placed offline (a function required for T 3 and above), the TAP. 7 signaling can be shared among any topology branches, whether series, star-2, or star-4 Ø Adapter (i. e. , ADTAPC) • 1149. 7 devices comprising a selected topology branch will share TAP. 7 signaling and, where the topology branch is star-2 or star-4, a given device may be selected for a given operation Ø Chip (i. e. , CLTAPC) • For a selected ADTAPC, the CLTAPC may be offline and will require selection when it must be operated Ø Core (i. e. , EMTAPC) • For a selected CLTAPC, given EMTAPC(s) of interest may be offline and will require selection when it (they) must be operated BTW 2010 19

Key Features of the Capability Classes Ø Six classes of 1149. 7 test access ports (TAP. 7 s), T 0 - T 5 Ø Incremental capability, each higher builds upon the lower Ø Class T 0 – foundation • 1149. 1 behavior from start-up, even where multiple on-chip TAPs Ø Class T 1 – commands and registers • common debug functions, features to minimize power consumption Ø Class T 2 – scan formats • improved scan performance, optional hot-connection capability Ø Class T 3 – direct addressability • operation in four-wire Series or Star Scan Topology Ø Class T 4 – packetization of scan data (2 -pin scan formats) • two-pin or four-pin interface; two-pin operation serializes 1149. 1 transactions and provides for higher test clock rates Ø Class T 5 – transport of non-scan data (2 -pin mode) • data transfers concurrent with scan, utilization of functions other than scan, and control of TAP. 7 pins for custom debug technologies BTW 2010 21

IEEE 1149. 7 hierarchy of classes BTW 2010 22

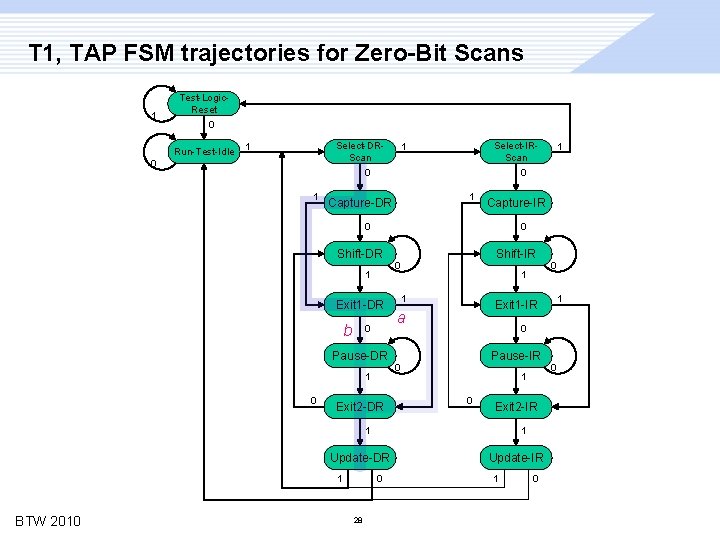

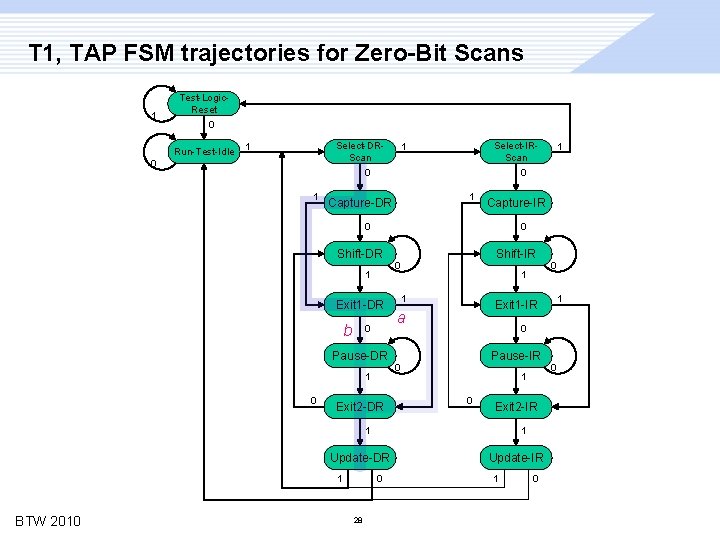

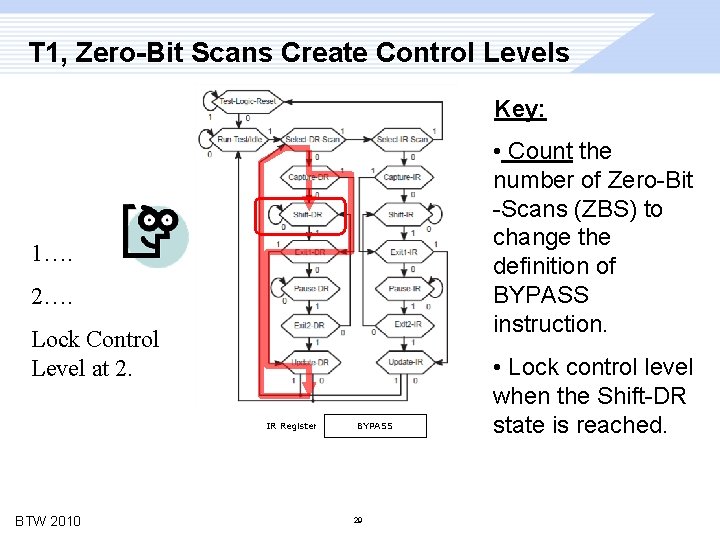

T 1, TAP FSM trajectories for Zero-Bit Scans 1 Test-Logic. Reset 0 Run-Test-Idle Select-DRScan 0 1 Select-IRScan 0 1 1 Capture-DR Capture-IR 0 0 Shift-DR 1 Exit 1 -DR b 0 Pause-DR 1 0 Exit 2 -DR Shift-IR 0 1 1 a BTW 2010 0 28 1 0 Pause-IR 0 1 0 Exit 2 -IR 1 Update-DR 0 Exit 1 -IR 1 1 1 Update-IR 1 0 0

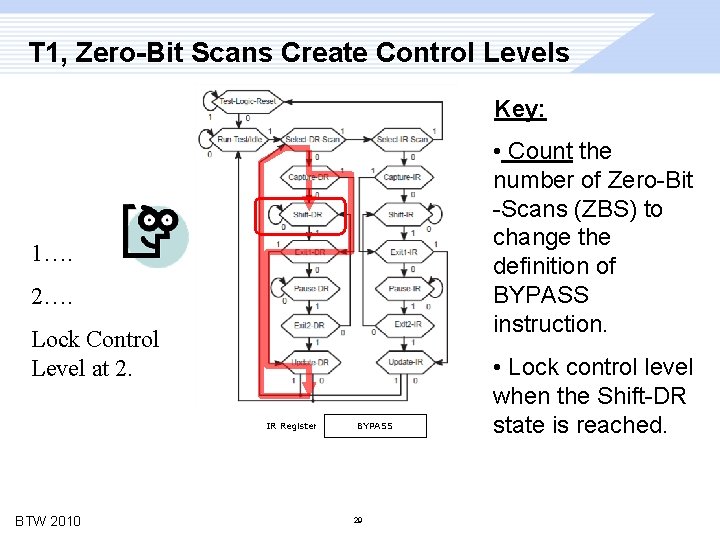

T 1, Zero-Bit Scans Create Control Levels Key: • Count the number of Zero-Bit -Scans (ZBS) to change the definition of BYPASS instruction. 1…. 2…. Lock Control Level at 2. IR Register BTW 2010 BYPASS 29 • Lock control level when the Shift-DR state is reached.

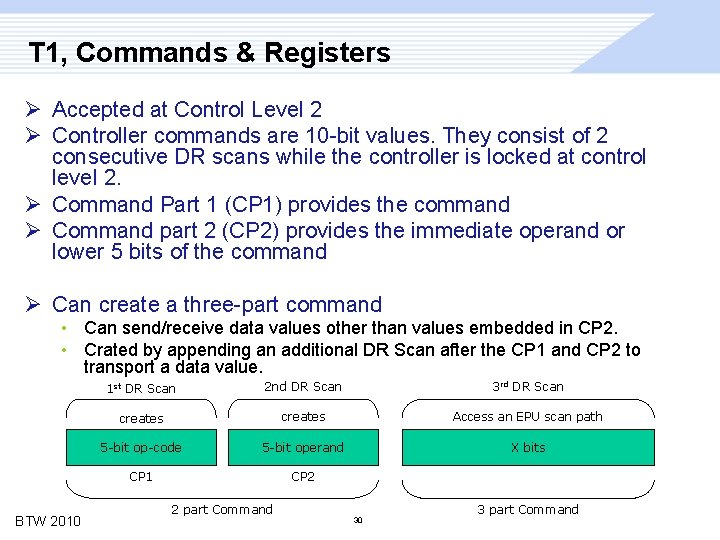

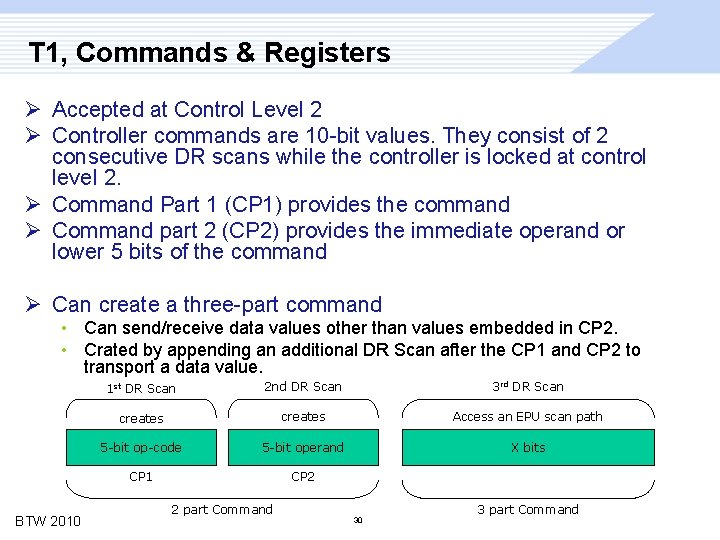

T 1, Commands & Registers Ø Accepted at Control Level 2 Ø Controller commands are 10 -bit values. They consist of 2 consecutive DR scans while the controller is locked at control level 2. Ø Command Part 1 (CP 1) provides the command Ø Command part 2 (CP 2) provides the immediate operand or lower 5 bits of the command Ø Can create a three-part command • Can send/receive data values other than values embedded in CP 2. • Crated by appending an additional DR Scan after the CP 1 and CP 2 to transport a data value. BTW 2010 1 st DR Scan 2 nd DR Scan 3 rd DR Scan creates Access an EPU scan path 5 -bit op-code 5 -bit operand X bits CP 1 CP 2 2 part Command 30 3 part Command

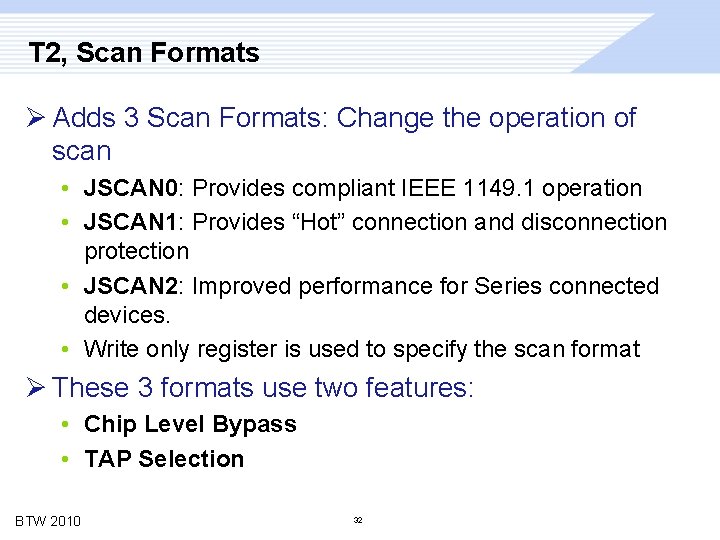

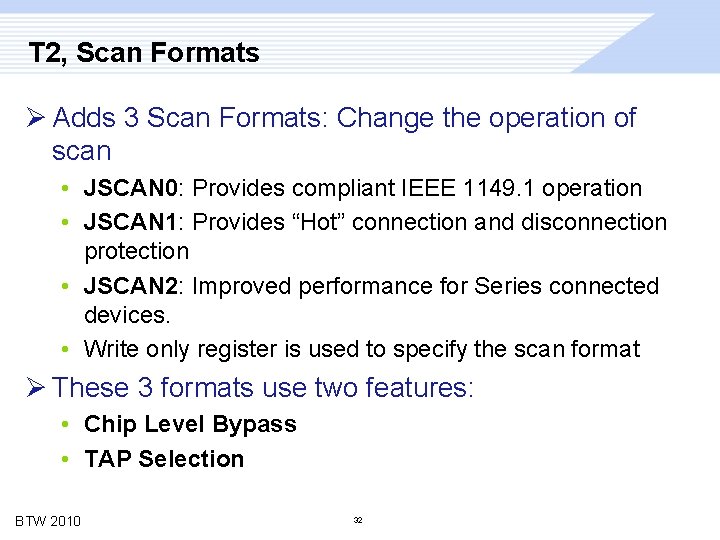

T 2, Scan Formats Ø Adds 3 Scan Formats: Change the operation of scan • JSCAN 0: Provides compliant IEEE 1149. 1 operation • JSCAN 1: Provides “Hot” connection and disconnection protection • JSCAN 2: Improved performance for Series connected devices. • Write only register is used to specify the scan format Ø These 3 formats use two features: • Chip Level Bypass • TAP Selection BTW 2010 32

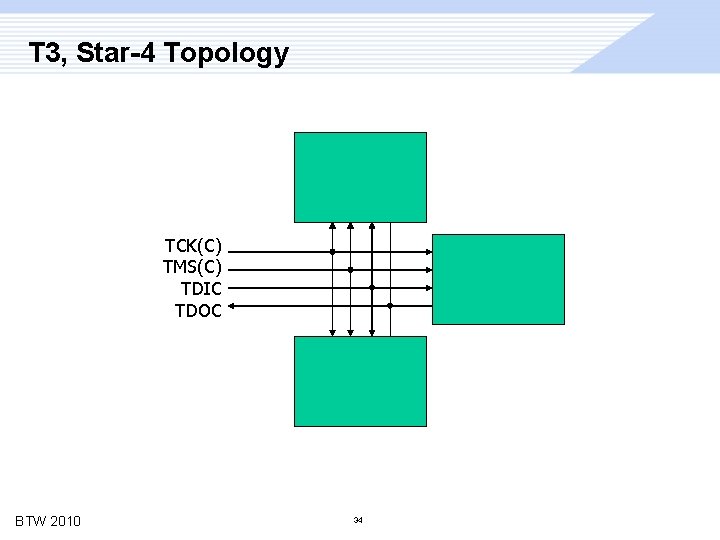

T 3, Star-4 Topology TCK(C) TMS(C) TDIC TDOC BTW 2010 34

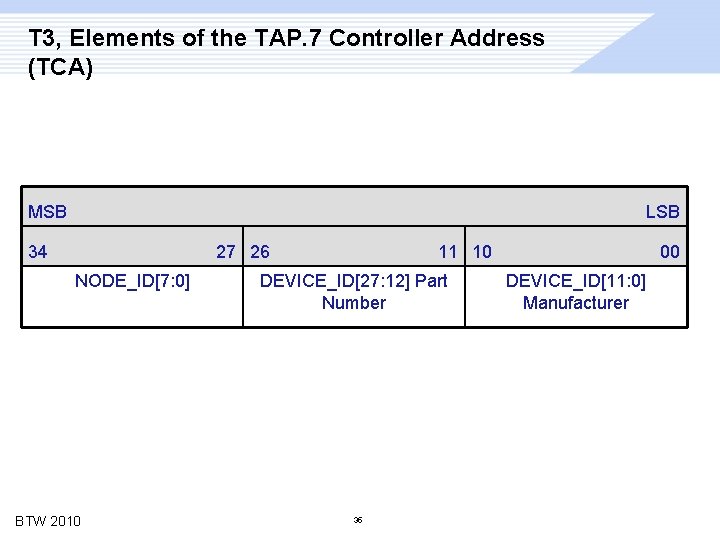

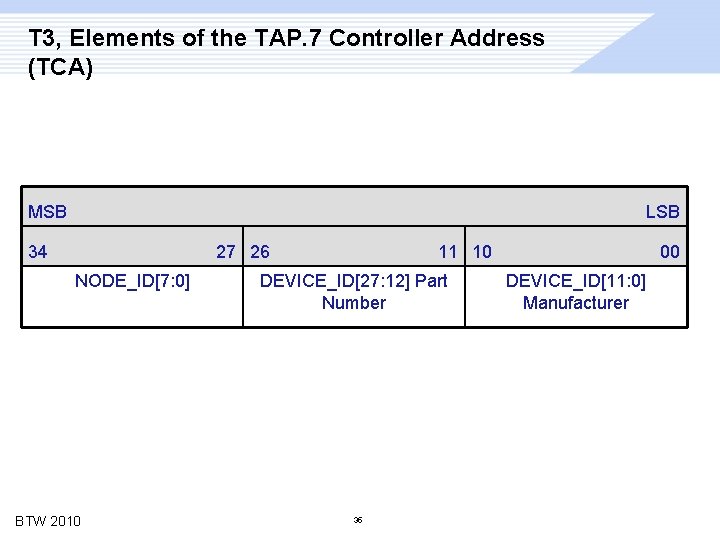

T 3, Elements of the TAP. 7 Controller Address (TCA) MSB LSB 34 27 26 NODE_ID[7: 0] BTW 2010 11 10 DEVICE_ID[27: 12] Part Number 35 00 DEVICE_ID[11: 0] Manufacturer

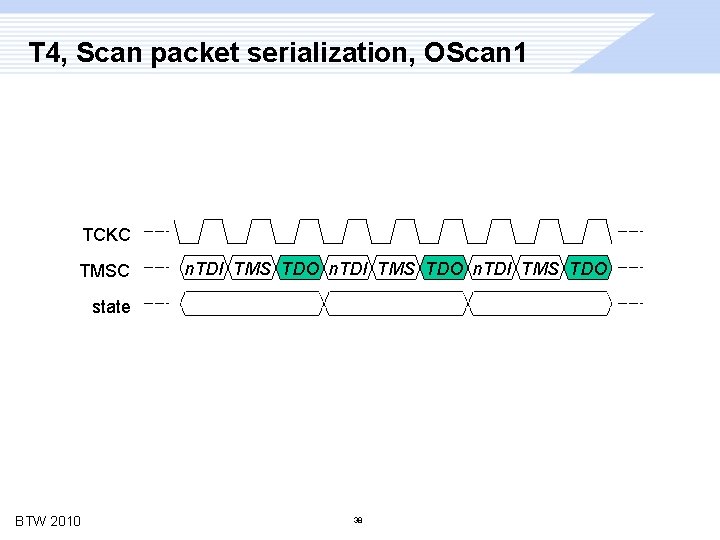

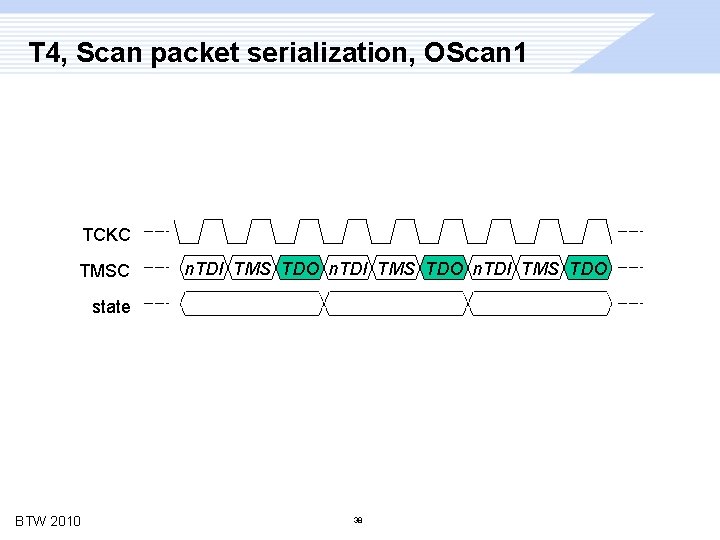

T 4, Scan packet serialization, OScan 1 TCKC TMSC n. TDI TMS TDO state BTW 2010 38

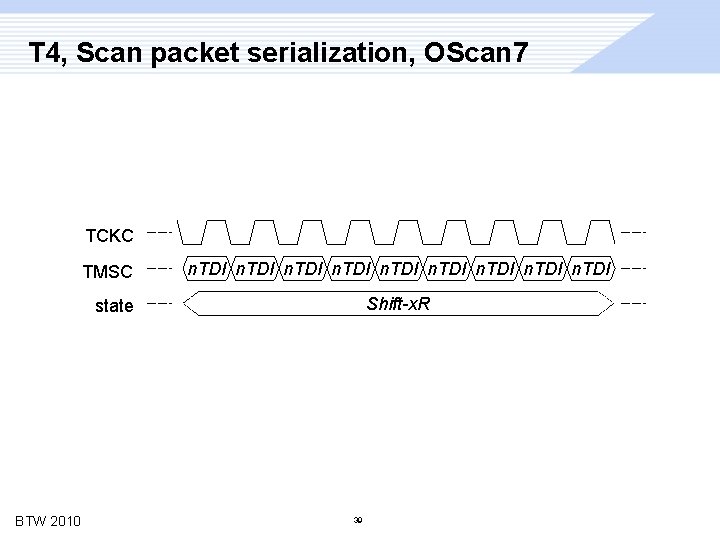

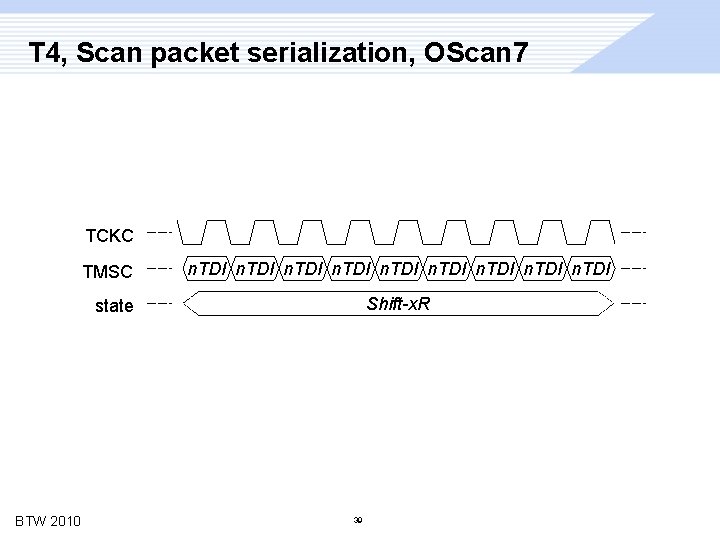

T 4, Scan packet serialization, OScan 7 TCKC TMSC n. TDI n. TDI Shift-x. R state BTW 2010 39

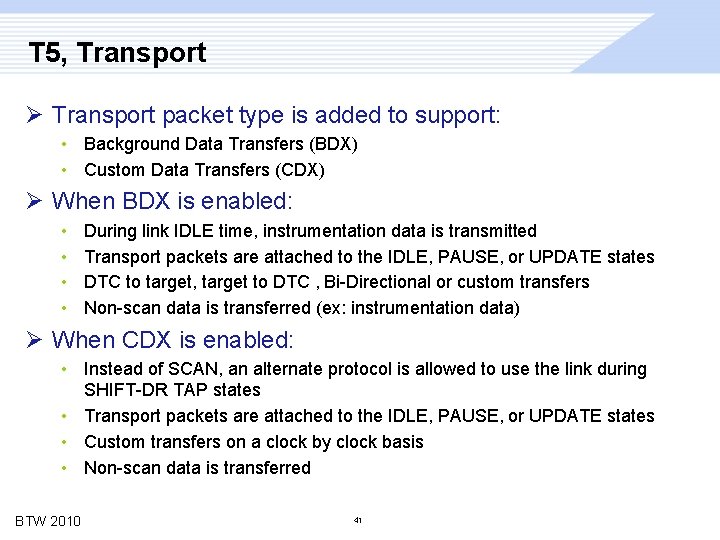

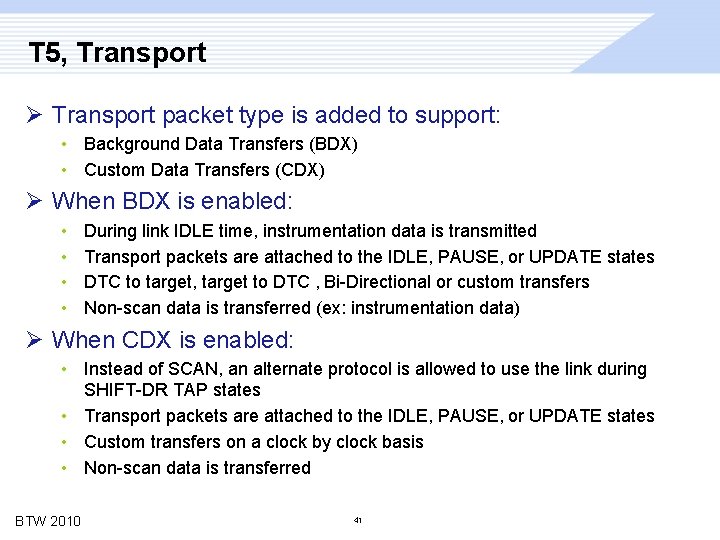

T 5, Transport Ø Transport packet type is added to support: • Background Data Transfers (BDX) • Custom Data Transfers (CDX) Ø When BDX is enabled: • • During link IDLE time, instrumentation data is transmitted Transport packets are attached to the IDLE, PAUSE, or UPDATE states DTC to target, target to DTC , Bi-Directional or custom transfers Non-scan data is transferred (ex: instrumentation data) Ø When CDX is enabled: • Instead of SCAN, an alternate protocol is allowed to use the link during SHIFT-DR TAP states • Transport packets are attached to the IDLE, PAUSE, or UPDATE states • Custom transfers on a clock by clock basis • Non-scan data is transferred BTW 2010 41

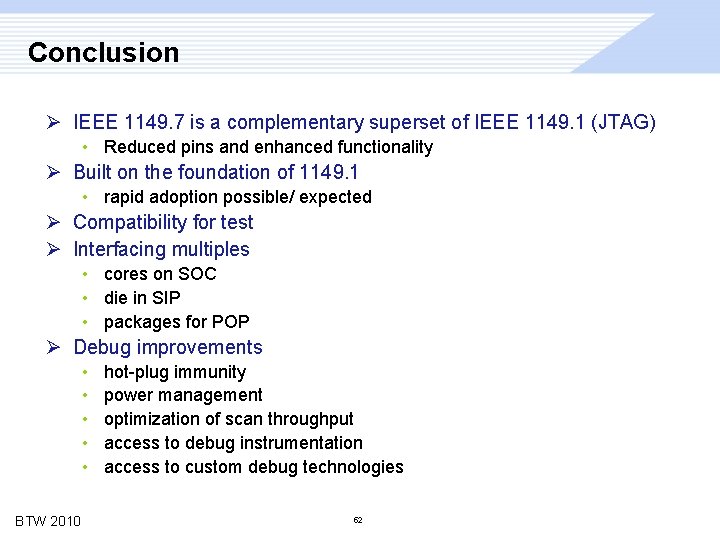

Conclusion Ø IEEE 1149. 7 is a complementary superset of IEEE 1149. 1 (JTAG) • Reduced pins and enhanced functionality Ø Built on the foundation of 1149. 1 • rapid adoption possible/ expected Ø Compatibility for test Ø Interfacing multiples • cores on SOC • die in SIP • packages for POP Ø Debug improvements • • • BTW 2010 hot-plug immunity power management optimization of scan throughput access to debug instrumentation access to custom debug technologies 52

Further Discussion Ø Where have you seen 1149. 7 chips on your boards? Ø Where will you see 1149. 7 chips on your boards? Ø Where would you like to see 1149. 7 chips on your boards? BTW 2010 53