IEEE 1149 4 MixedSignal Test Bus An overview

IEEE 1149. 4 Mixed-Signal Test Bus An overview of this new testability bus standard, along with a discussion of the architecture and how to use it. 1 Mixed-Signal Test Bus IEEE 1149. 4

IEEE 1149. 4: Mixed-signal Test Bus Standard n Development history n Basic guidelines n Test bus requirements n Standard architecture n Measurement example 2 Mixed-Signal Test Bus IEEE 1149. 4

Development History n September 1991 s Informal meeting of 15 companies in San Jose, CA s Draft of mission statement, objectives, request to IEEE n October 1991 s ITC meeting attracted 30 companies s Working Group authorized by Test Bus Steering Committee n Working Group meetings s Since October 1991 s Regular meetings: 3 times per year at major test events 3 Mixed-Signal Test Bus IEEE 1149. 4

Mission Statement To define, document, and promote the use of a standard mixed-signal test bus that can be used at the device, sub-assembly, and system levels to improve the controllability and observability of mixed-signal designs and to support mixed-signal built-in test structures in order to reduce test development time and costs, and improve test quality. 4 Mixed-Signal Test Bus IEEE 1149. 4

Basic Guidelines n Providing test bus facilities to meet the mission objectives n Oriented toward industry: design, test, and manufacturing n Maintaining compatibility with 1149. 1 test bus features n Coordinating with s IEEE 1149. 1 and mainly the IEEE 1149. 1 B-1994 s International industry and academic experts 5 Mixed-Signal Test Bus IEEE 1149. 4

Basic Guidelines n IEEE 1149. 4 does NOT seek to s Solve all mixed-signal test problems s Dictate mixed-signal test strategies n IEEE 1149. 4 DOES intend to s REDUCE the difficulty in mixed-signal testing s FACILITATE design-for-test s PROMOTE concurrent design & test approaches 6 Mixed-Signal Test Bus IEEE 1149. 4

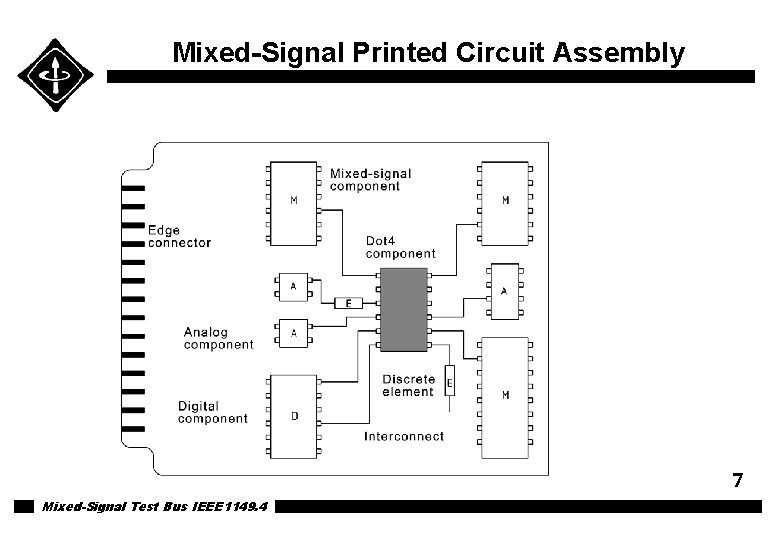

Mixed-Signal Printed Circuit Assembly 7 Mixed-Signal Test Bus IEEE 1149. 4

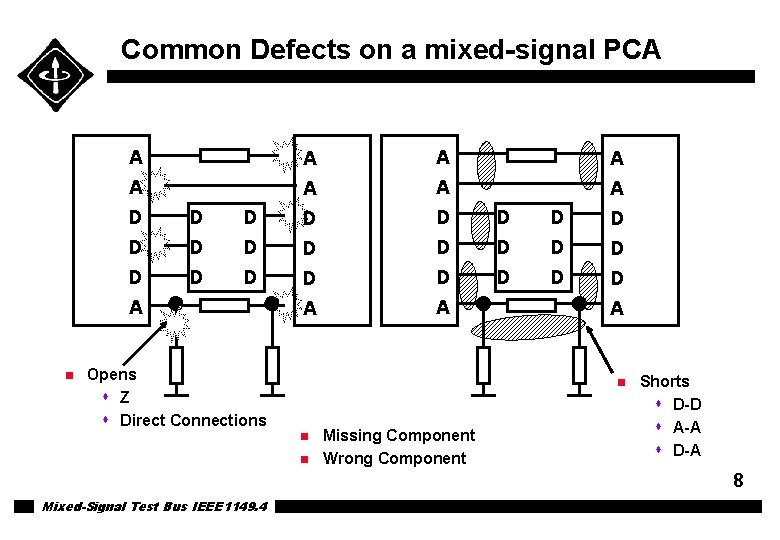

Common Defects on a mixed-signal PCA A A A A D D D D D D A A A n Opens s Z s Direct Connections n n n Mixed-Signal Test Bus IEEE 1149. 4 A Missing Component Wrong Component Shorts s D-D s A-A s D-A 8

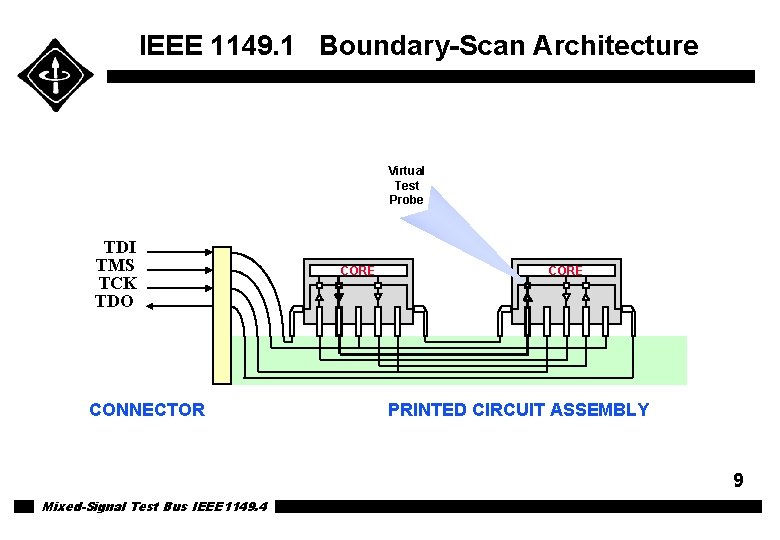

IEEE 1149. 1 Boundary-Scan Architecture Virtual Test Probe TDI TMS TCK TDO CONNECTOR CORE PRINTED CIRCUIT ASSEMBLY 9 Mixed-Signal Test Bus IEEE 1149. 4

Simple, Extended and Differential Interconnects 10 Mixed-Signal Test Bus IEEE 1149. 4

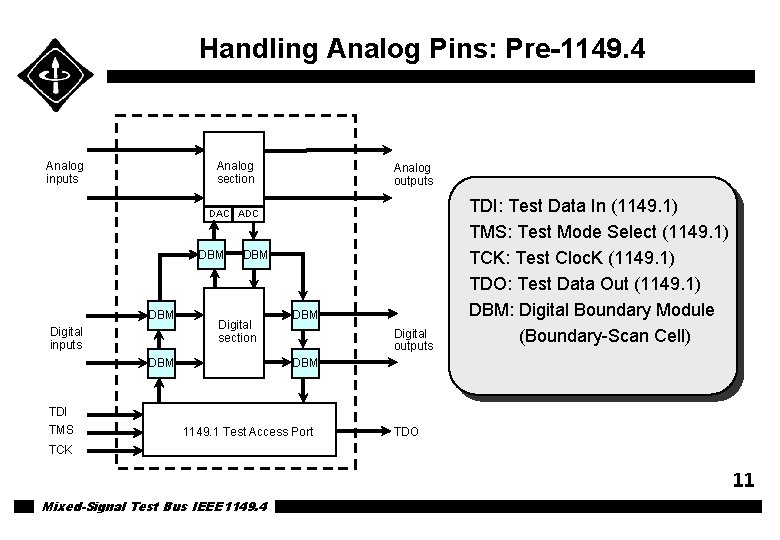

Handling Analog Pins: Pre-1149. 4 Analog inputs Analog section Analog outputs DAC ADC DBM Digital inputs DBM Digital section DBM TDI TMS DBM Digital outputs TDI: Test Data In (1149. 1) TMS: Test Mode Select (1149. 1) TCK: Test Cloc. K (1149. 1) TDO: Test Data Out (1149. 1) DBM: Digital Boundary Module (Boundary-Scan Cell) DBM 1149. 1 Test Access Port TDO TCK 11 Mixed-Signal Test Bus IEEE 1149. 4

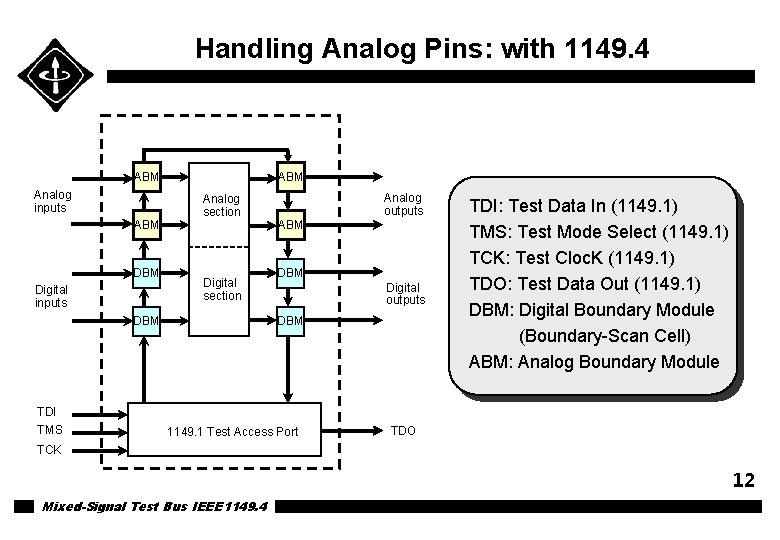

Handling Analog Pins: with 1149. 4 ABM Analog inputs ABM Digital inputs ABM Analog section Digital section DBM TDI TMS Analog outputs ABM Digital outputs DBM 1149. 1 Test Access Port TDI: Test Data In (1149. 1) TMS: Test Mode Select (1149. 1) TCK: Test Cloc. K (1149. 1) TDO: Test Data Out (1149. 1) DBM: Digital Boundary Module (Boundary-Scan Cell) ABM: Analog Boundary Module TDO TCK 12 Mixed-Signal Test Bus IEEE 1149. 4

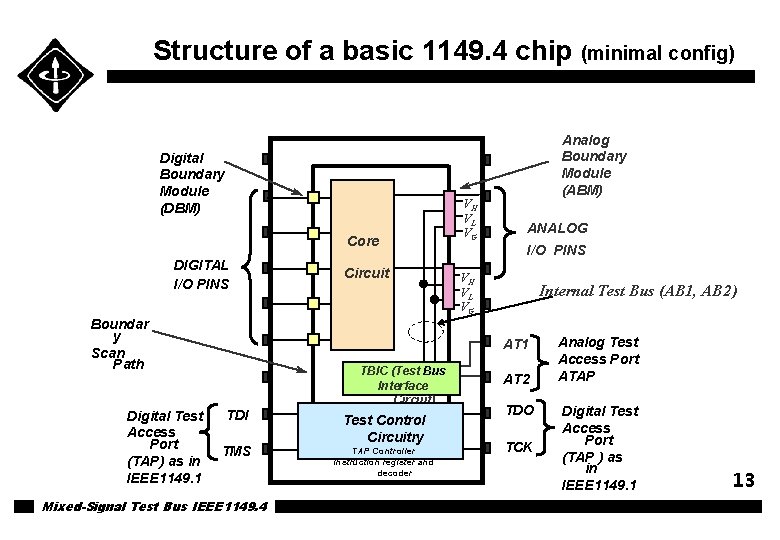

Structure of a basic 1149. 4 chip (minimal config) Digital Boundary Module (DBM) Core DIGITAL I/O PINS Boundar y Scan Path Digital Test Access Port (TAP) as in IEEE 1149. 1 Circuit VH VL VG Analog Boundary Module (ABM) ANALOG I/O PINS VH VL VG Internal Test Bus (AB 1, AB 2 ) AT 1 TBIC (Test Bus Interface Circuit) TDI TMS Mixed-Signal Test Bus IEEE 1149. 4 Test Control Circuitry TAP Controller Instruction register and decoder AT 2 TDO TCK Analog Test Access Port ATAP Digital Test Access Port (TAP ) as in IEEE 1149. 1 13

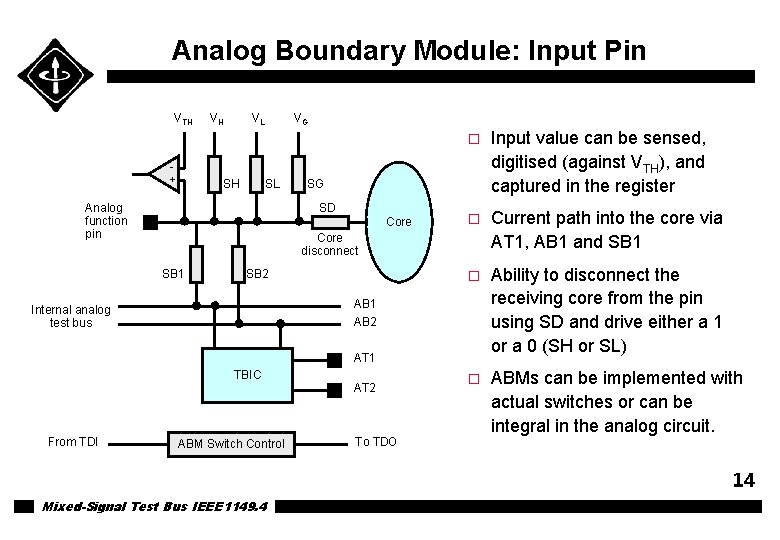

Analog Boundary Module: Input Pin VTH + VH VL SH VG SL Analog function pin o Input value can be sensed, digitised (against VTH), and captured in the register o Current path into the core via AT 1, AB 1 and SB 1 o Ability to disconnect the receiving core from the pin using SD and drive either a 1 or a 0 (SH or SL) o ABMs can be implemented with actual switches or can be integral in the analog circuit. SG SD Core disconnect SB 1 SB 2 AB 1 AB 2 Internal analog test bus AT 1 TBIC From TDI ABM Switch Control AT 2 To TDO 14 Mixed-Signal Test Bus IEEE 1149. 4

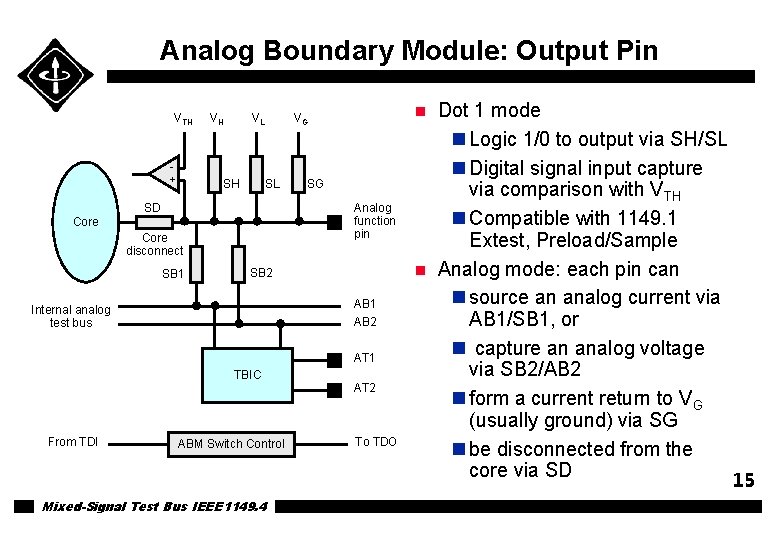

Analog Boundary Module: Output Pin VTH + VH VL SH SL SD SG Analog function pin Core disconnect SB 1 n VG n SB 2 AB 1 AB 2 Internal analog test bus AT 1 TBIC From TDI ABM Switch Control Mixed-Signal Test Bus IEEE 1149. 4 AT 2 To TDO Dot 1 mode n Logic 1/0 to output via SH/SL n Digital signal input capture via comparison with VTH n Compatible with 1149. 1 Extest, Preload/Sample Analog mode: each pin can n source an analog current via AB 1/SB 1, or n capture an analog voltage via SB 2/AB 2 n form a current return to VG (usually ground) via SG n be disconnected from the core via SD 15

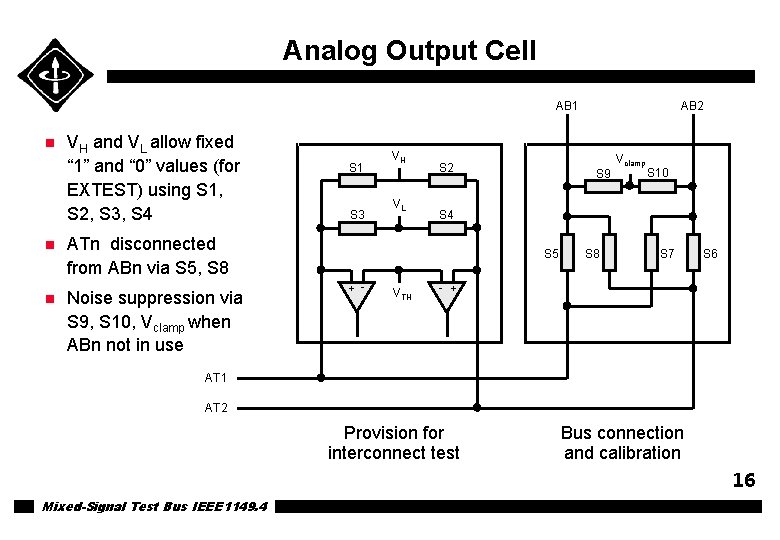

Analog Output Cell AB 1 n VH and VL allow fixed “ 1” and “ 0” values (for EXTEST) using S 1, S 2, S 3, S 4 n ATn disconnected from ABn via S 5, S 8 n Noise suppression via S 9, S 10, Vclamp when ABn not in use S 1 S 3 VH VL S 2 S 9 VTH Vclamp S 10 S 4 S 5 + - AB 2 S 8 S 7 S 6 - + AT 1 AT 2 Provision for interconnect test Bus connection and calibration 16 Mixed-Signal Test Bus IEEE 1149. 4

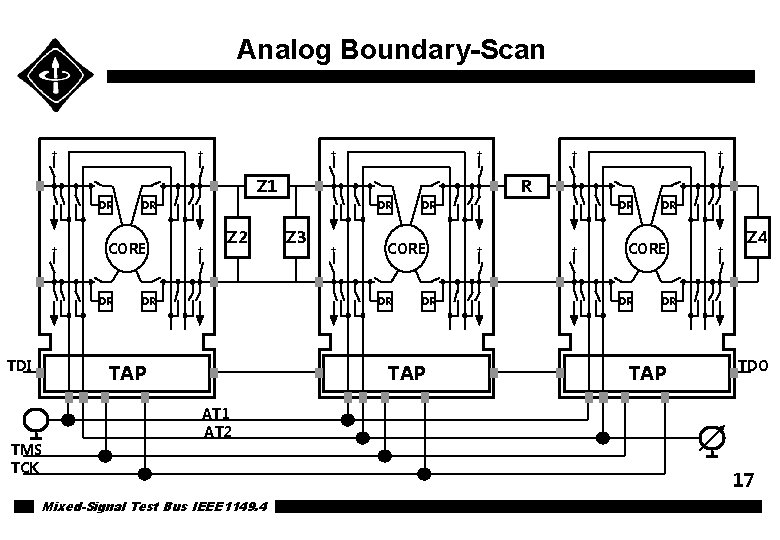

Analog Boundary-Scan + + Z 1 DR + DR TDI DR + Z 2 DR TMS TCK Z 3 + DR CORE DR TAP + R DR CORE + DR TAP DR + + DR CORE DR + Z 4 DR TAP TDO AT 1 AT 2 Mixed-Signal Test Bus IEEE 1149. 4 17

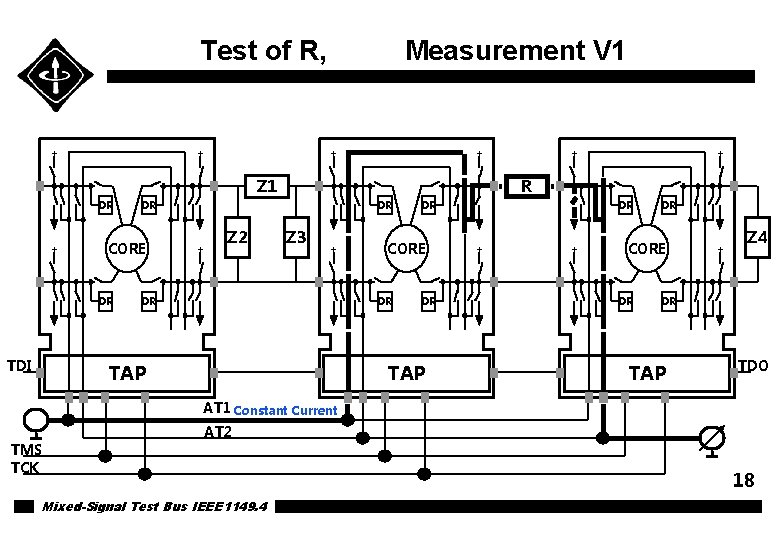

Test of R, + + Measurement V 1 + + Z 1 DR + DR TDI DR + Z 2 + R DR CORE + Z 3 + DR CORE DR TAP DR + + DR CORE DR + Z 4 DR TAP TDO AT 1 Constant Current TMS TCK AT 2 Mixed-Signal Test Bus IEEE 1149. 4 18

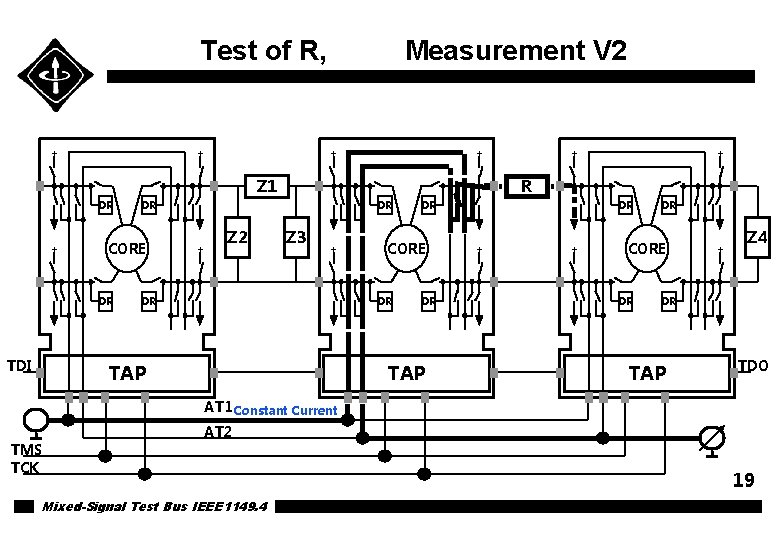

Test of R, + + Measurement V 2 + + Z 1 DR + DR TDI DR + Z 2 + R DR CORE + Z 3 + DR CORE DR TAP DR + + DR CORE DR + Z 4 DR TAP TDO AT 1 Constant Current TMS TCK AT 2 Mixed-Signal Test Bus IEEE 1149. 4 19

Test of R, Result n R = (V 2 - V 1) / I n Results for three impedances (Z 1, Z 2, Z 3) can be calculated and checked against correct values! n This metrology was proven and presented at the 1993 ITC by Ken Parker in a paper entitled: “Structure and Metrology for an Analog Testability Bus” by Ken Parker, John Mc. Dermid, and Stig Oresjo of HP. 20 Mixed-Signal Test Bus IEEE 1149. 4

IEEE 1149. 4 Types of Testing n Interconnect : Short, Open n Parametric Testing : Passive Element measurement n Internal Testing : Df. T (Design for Test) , BIST (Built-In Self-Test) 21 Mixed-Signal Test Bus IEEE 1149. 4

For Further Information Officers: n n n Adam Osseiran, IEEE 1149. 4 Working Group Chair Fluence Technology (Europe) osseiran@fluence. com Stephen Sunter, Vice Chair Logic. Vision, CANADA sunter@lvision. com Adam Cron, Editor (previous Chair) Synopsys, USA acron@synopsys. com Elbert Nhan, Secretary Johns Hopkins University, USA The IEEE 1149. 4 Web page: http: //grouper. ieee. org/groups/1149/4/ 22 Mixed-Signal Test Bus IEEE 1149. 4

To Learn more. . n The IEEE Standard Document 0 -7381 -1755 -2 SH 94761 -NCD; 59$ n ITC 97, P 8. 2; IEEE D&TC, Fall 96, pp. 98 -101 (Cron, Viewlogic) n ITC 93, P 15. 2 (Parker et al, HP); ITC 96, P 15. 1 (Whetsel, TI); ITC 96, P 4. 2 (Lofstrom, KLIC) n K. Parker, “Boundary-Scan Handbook: Analog & Digital”, Kluwer, 1998 (2 nd Edition). Chap. 7 n Perry, “Fundamentals of Mixed-Signal Test”, 1999, <www. soft-test. com> n A. Osseiran, “Analog & Mixed-Signal Boundary Scan: a Guide to the 1149. 4 Test Standard”, Kluwer, 1999, <www. wkap. nl> n Next events : DATE 00 (Paris), VTS 00 (Montreal), ITC 00 (Atlantic City) Mixed-Signal Test Bus IEEE 1149. 4 23

- Slides: 23