The 1149 4 IEEE standard for mixedsignal testing

- Slides: 40

The 1149. 4 IEEE standard for mixed-signal testing José Manuel Martins Ferreira (in co-operation with Telmo Amaral and Gustavo Alves) Faculdade de Engenharia da Universidade do Porto (jmf@fe. up. pt / http: //www. fe. up. pt/~jmf) An ITTF / ALLEGRO seminar (http: //www. fe. up. pt/~allegro) The 1149. 4 IEEE standard for mixed-signal testing HIBU (JMF) – March 16 th, 2001

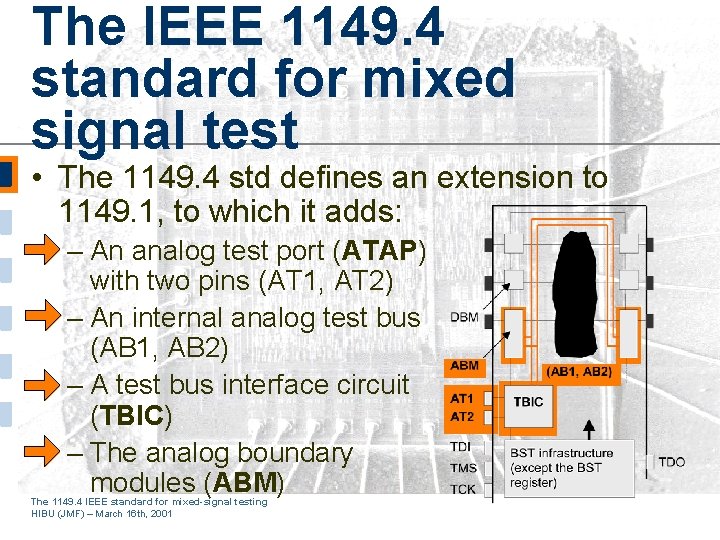

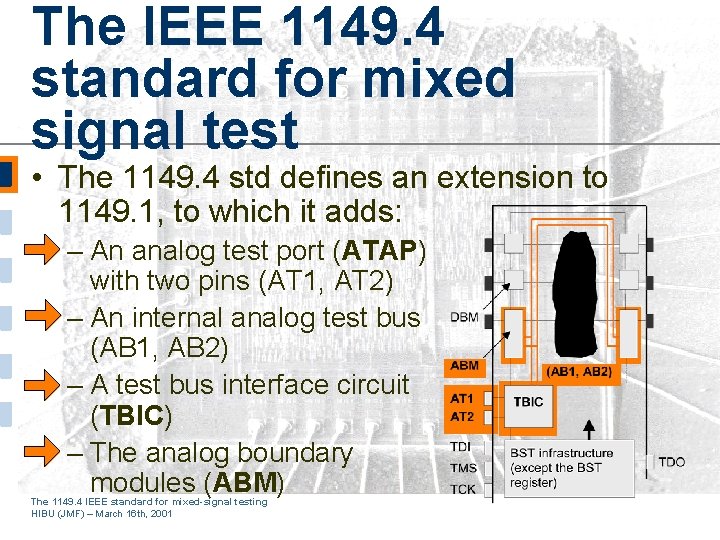

The IEEE 1149. 4 standard for mixed signal test • The 1149. 4 std defines an extension to 1149. 1, to which it adds: – An analog test port (ATAP) with two pins (AT 1, AT 2) – An internal analog test bus (AB 1, AB 2) – A test bus interface circuit (TBIC) – The analog boundary modules (ABM) The 1149. 4 IEEE standard for mixed-signal testing HIBU (JMF) – March 16 th, 2001

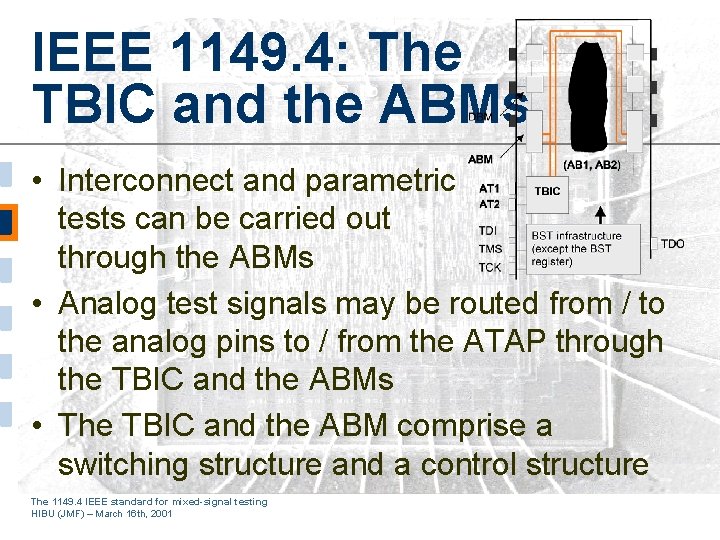

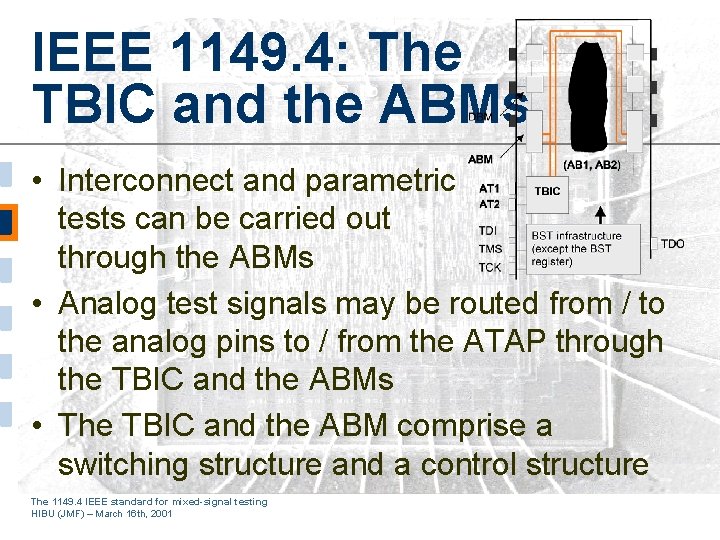

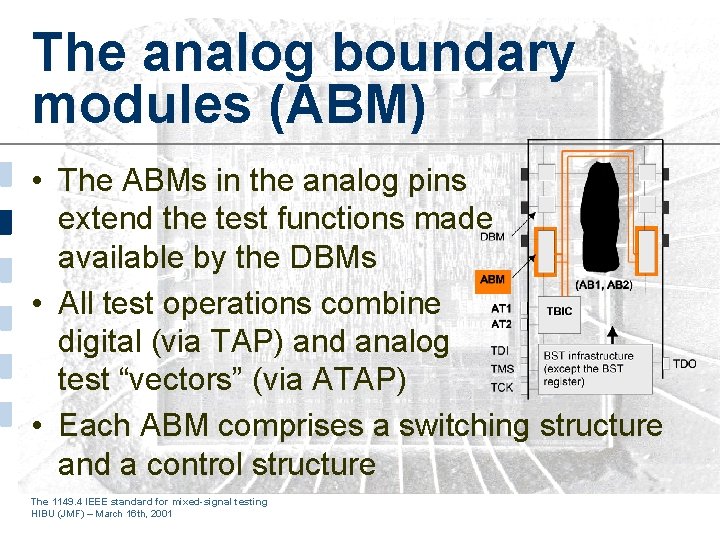

IEEE 1149. 4: The TBIC and the ABMs • Interconnect and parametric tests can be carried out through the ABMs • Analog test signals may be routed from / to the analog pins to / from the ATAP through the TBIC and the ABMs • The TBIC and the ABM comprise a switching structure and a control structure The 1149. 4 IEEE standard for mixed-signal testing HIBU (JMF) – March 16 th, 2001

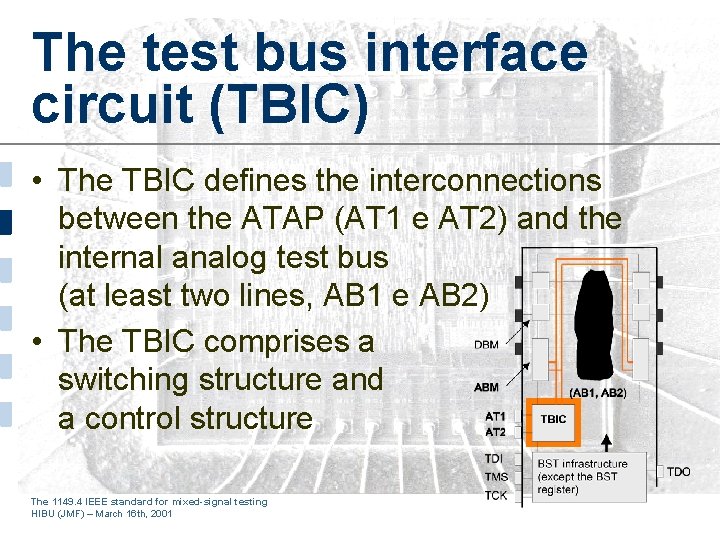

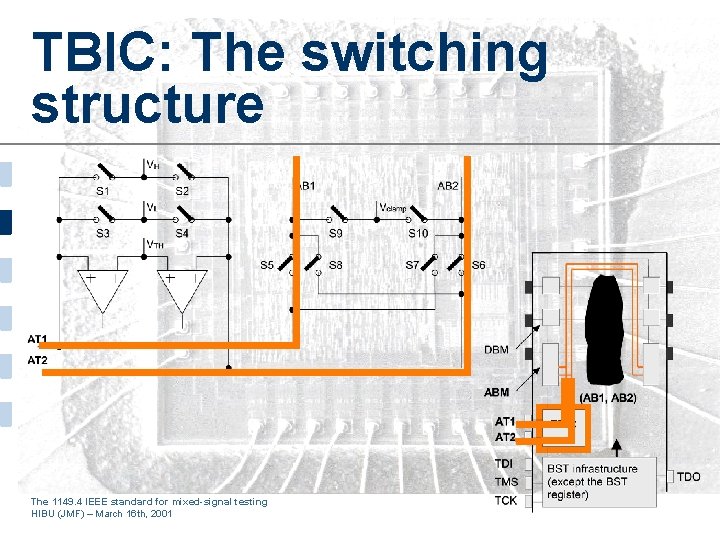

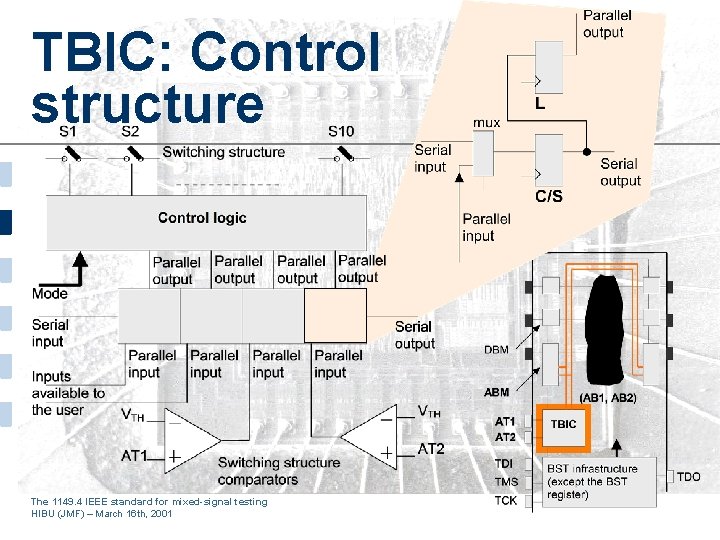

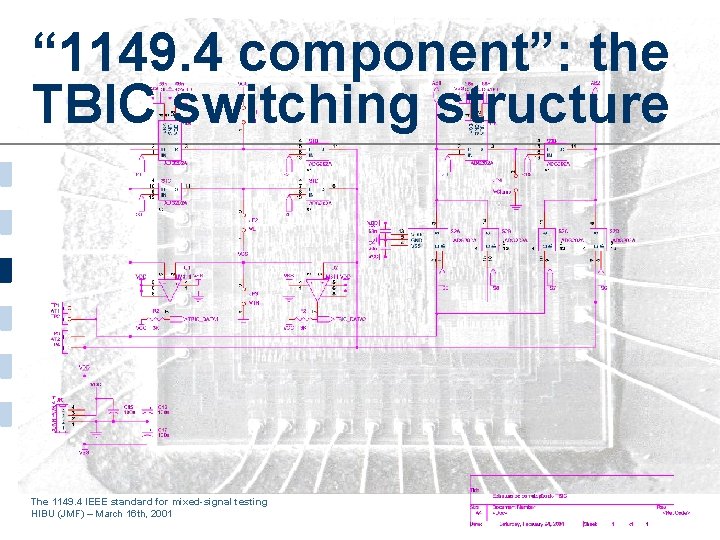

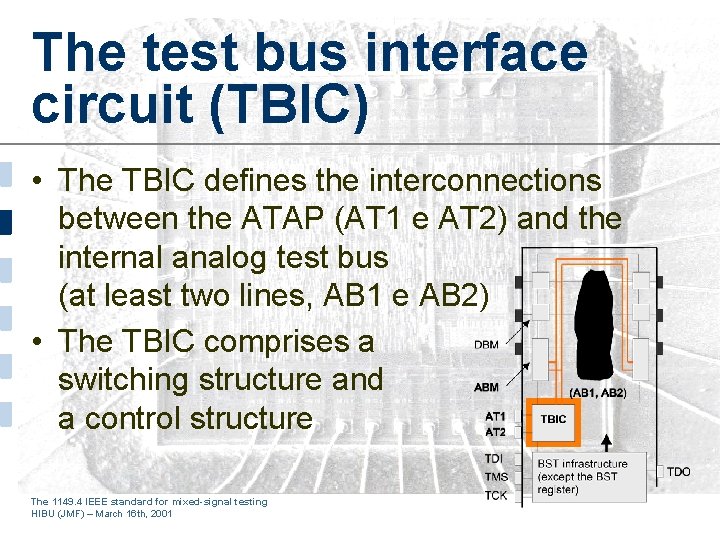

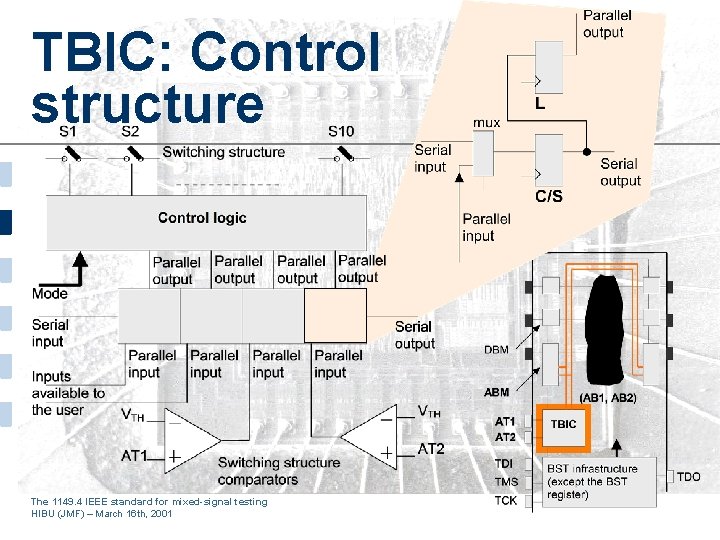

The test bus interface circuit (TBIC) • The TBIC defines the interconnections between the ATAP (AT 1 e AT 2) and the internal analog test bus (at least two lines, AB 1 e AB 2) • The TBIC comprises a switching structure and a control structure The 1149. 4 IEEE standard for mixed-signal testing HIBU (JMF) – March 16 th, 2001

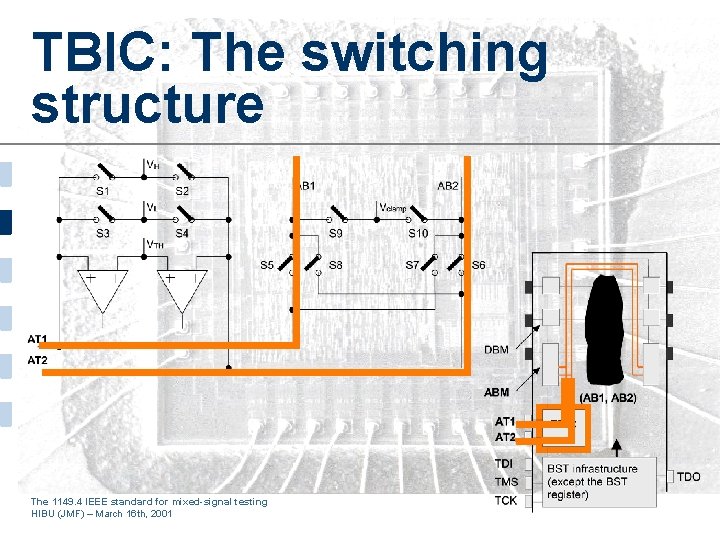

TBIC: The switching structure The 1149. 4 IEEE standard for mixed-signal testing HIBU (JMF) – March 16 th, 2001

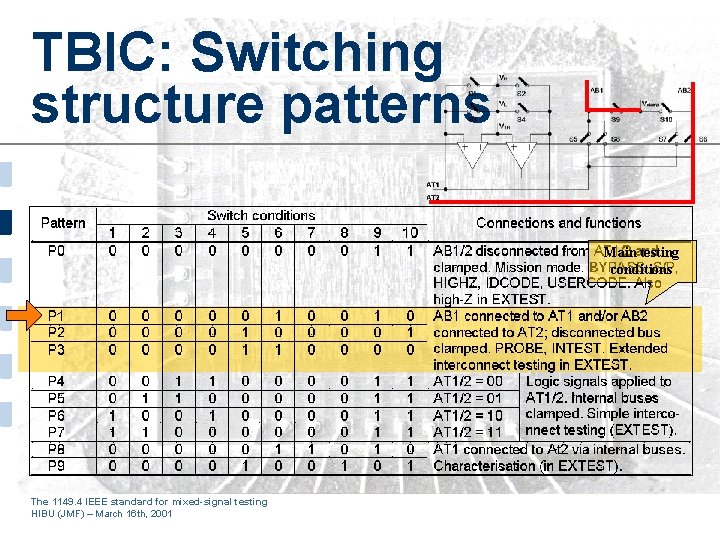

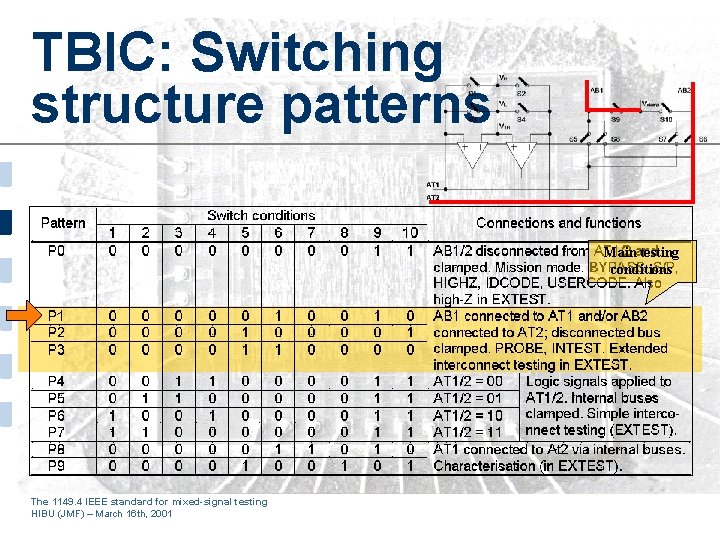

TBIC: Switching structure patterns Main testing conditions The 1149. 4 IEEE standard for mixed-signal testing HIBU (JMF) – March 16 th, 2001

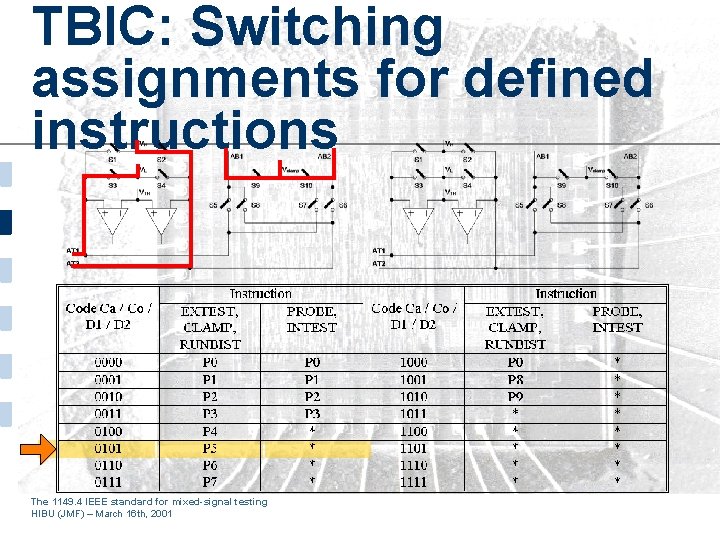

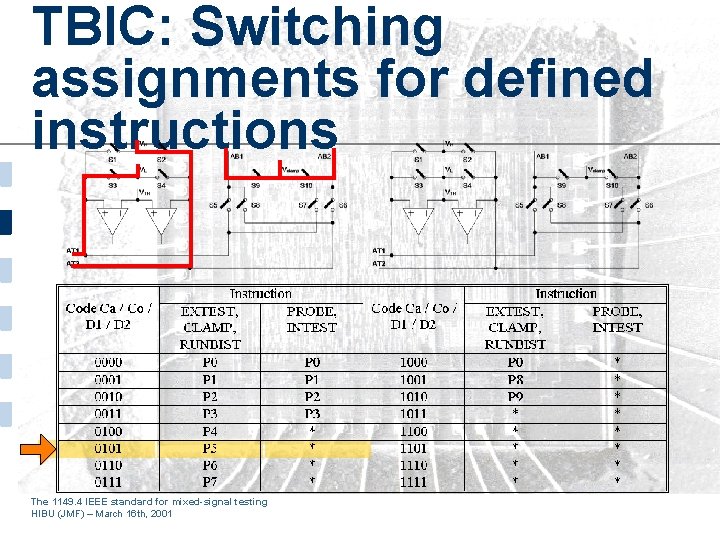

TBIC: Switching assignments for defined instructions The 1149. 4 IEEE standard for mixed-signal testing HIBU (JMF) – March 16 th, 2001

TBIC: Control structure The 1149. 4 IEEE standard for mixed-signal testing HIBU (JMF) – March 16 th, 2001

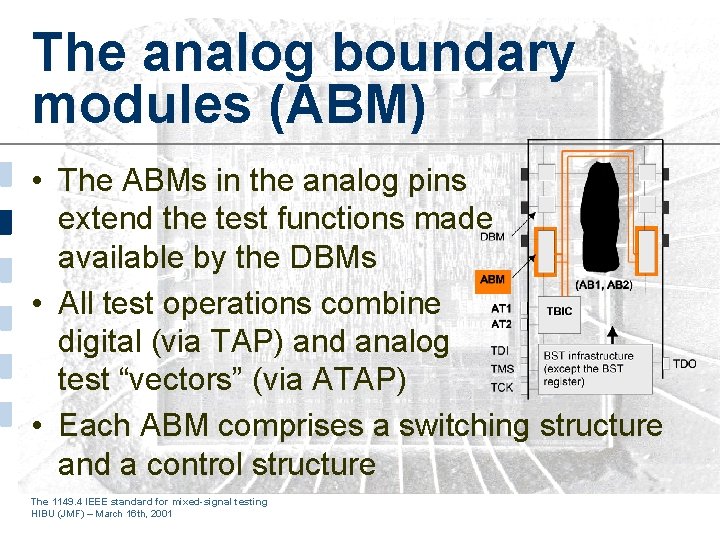

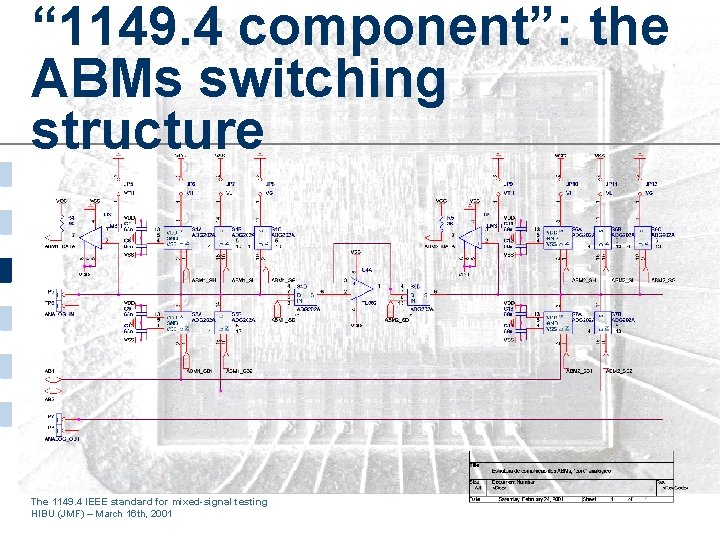

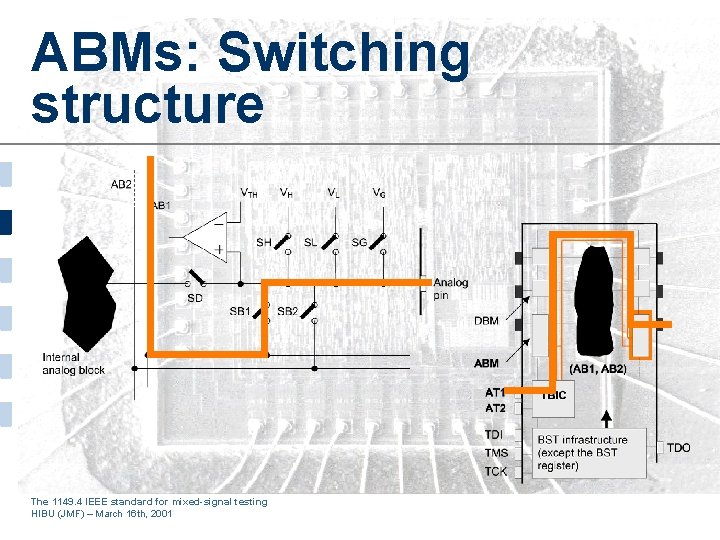

The analog boundary modules (ABM) • The ABMs in the analog pins extend the test functions made available by the DBMs • All test operations combine digital (via TAP) and analog test “vectors” (via ATAP) • Each ABM comprises a switching structure and a control structure The 1149. 4 IEEE standard for mixed-signal testing HIBU (JMF) – March 16 th, 2001

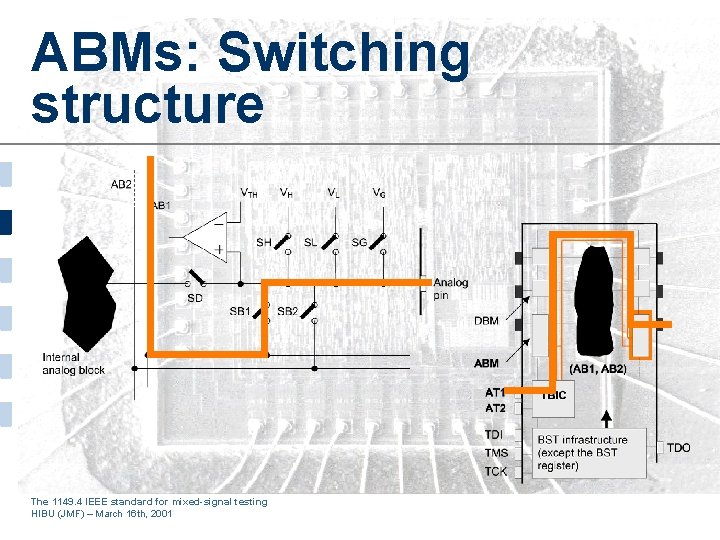

ABMs: Switching structure The 1149. 4 IEEE standard for mixed-signal testing HIBU (JMF) – March 16 th, 2001

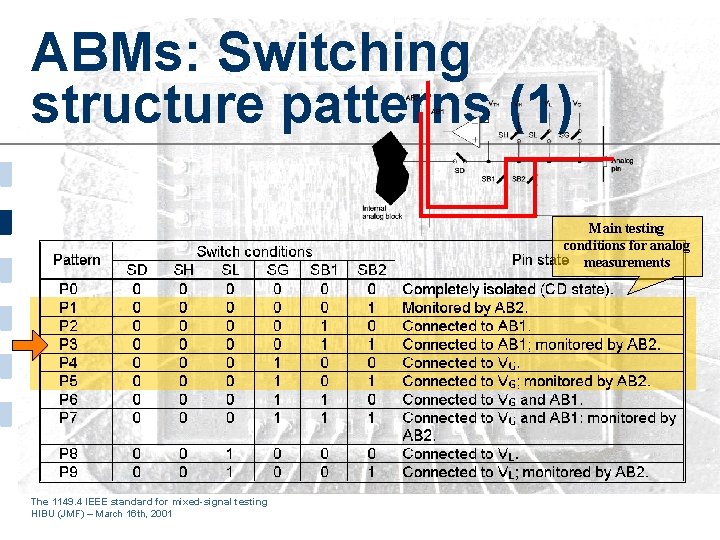

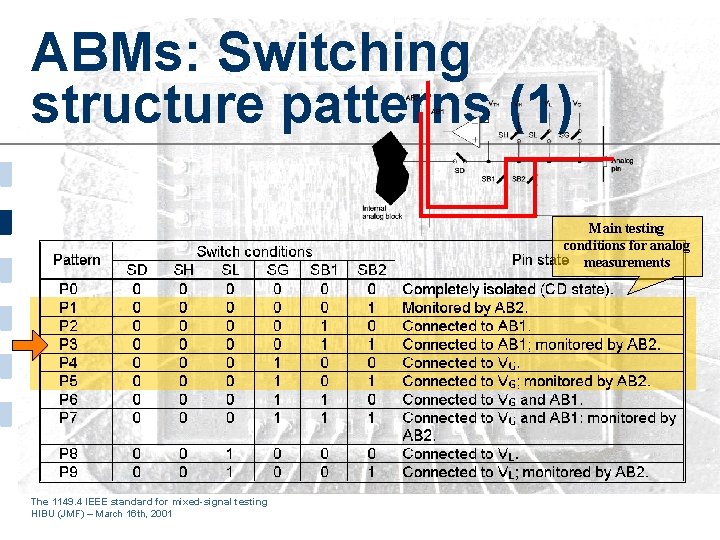

ABMs: Switching structure patterns (1) Main testing conditions for analog measurements The 1149. 4 IEEE standard for mixed-signal testing HIBU (JMF) – March 16 th, 2001

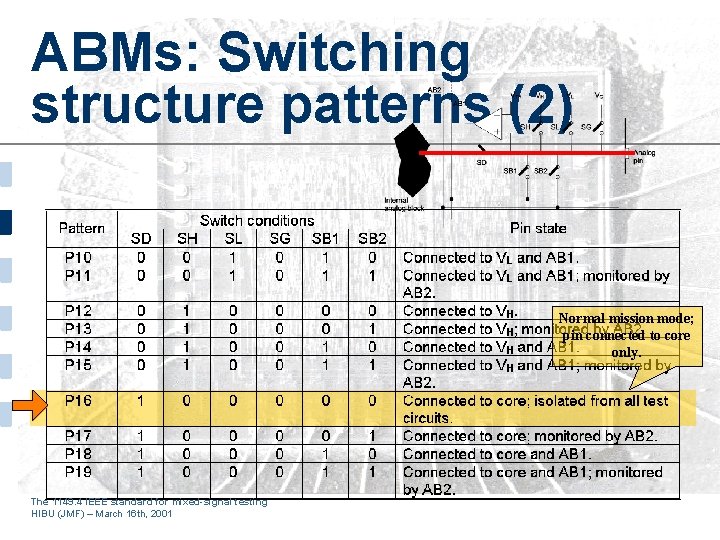

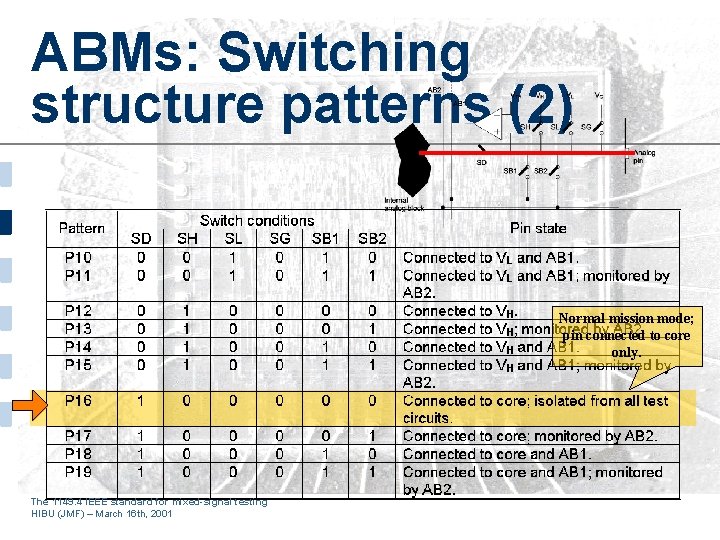

ABMs: Switching structure patterns (2) Normal mission mode; pin connected to core only. The 1149. 4 IEEE standard for mixed-signal testing HIBU (JMF) – March 16 th, 2001

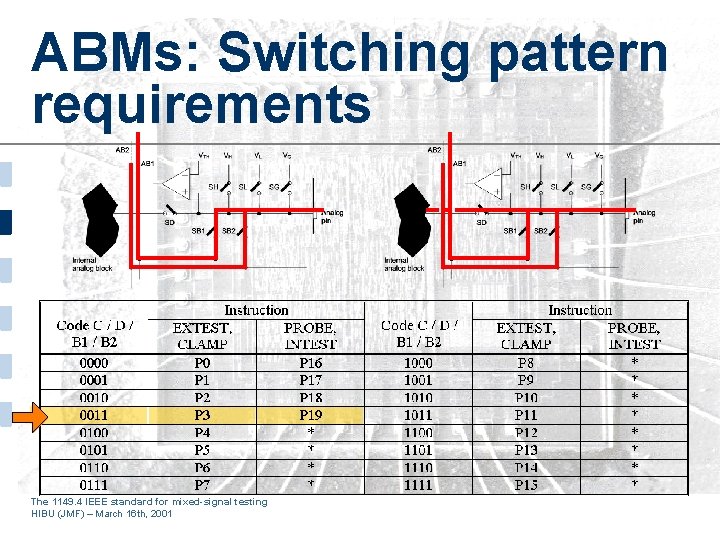

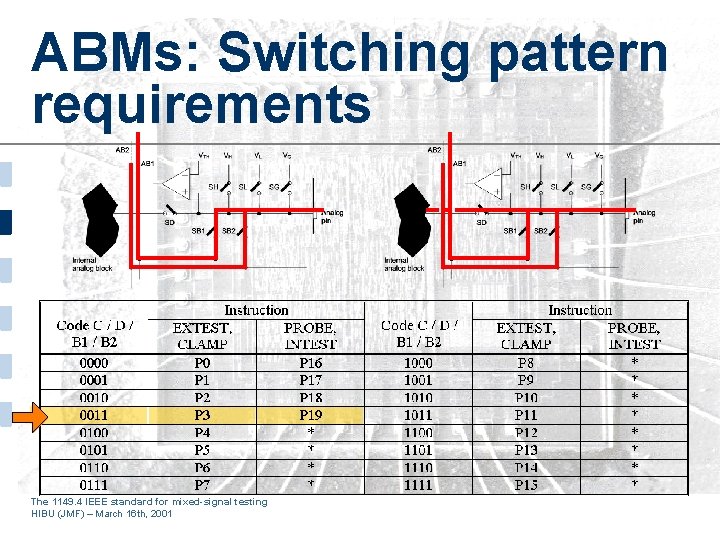

ABMs: Switching pattern requirements The 1149. 4 IEEE standard for mixed-signal testing HIBU (JMF) – March 16 th, 2001

ABMs: Control structure The 1149. 4 IEEE standard for mixed-signal testing HIBU (JMF) – March 16 th, 2001

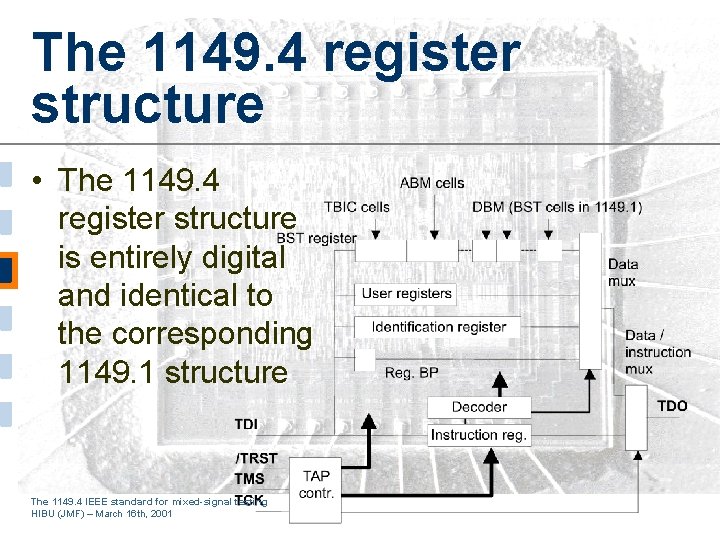

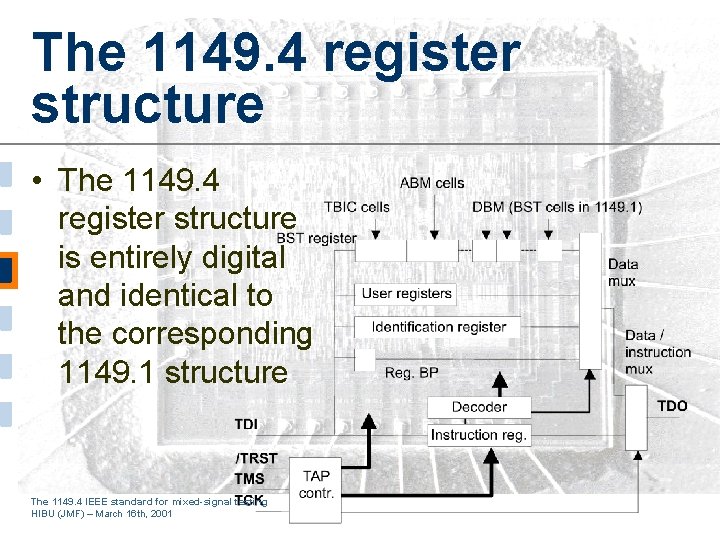

The 1149. 4 register structure • The 1149. 4 register structure is entirely digital and identical to the corresponding 1149. 1 structure The 1149. 4 IEEE standard for mixed-signal testing HIBU (JMF) – March 16 th, 2001

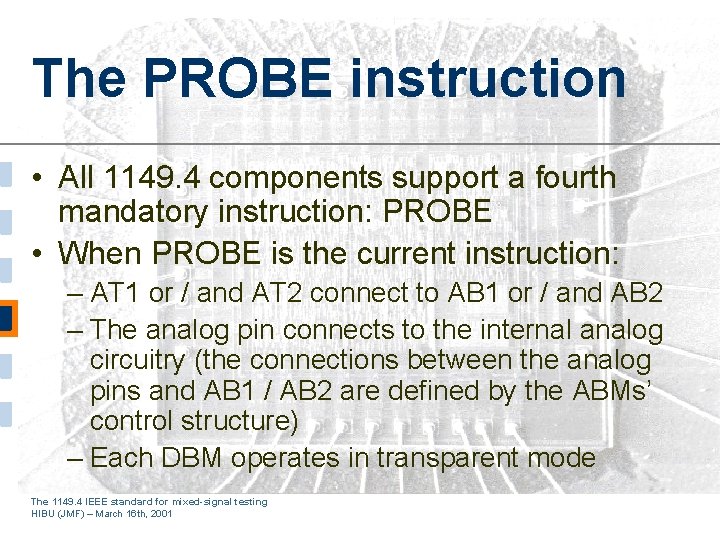

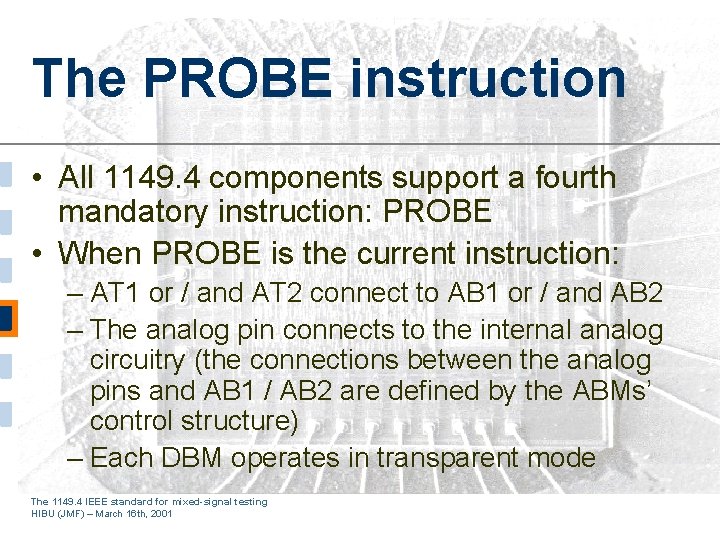

The PROBE instruction • All 1149. 4 components support a fourth mandatory instruction: PROBE • When PROBE is the current instruction: – AT 1 or / and AT 2 connect to AB 1 or / and AB 2 – The analog pin connects to the internal analog circuitry (the connections between the analog pins and AB 1 / AB 2 are defined by the ABMs’ control structure) – Each DBM operates in transparent mode The 1149. 4 IEEE standard for mixed-signal testing HIBU (JMF) – March 16 th, 2001

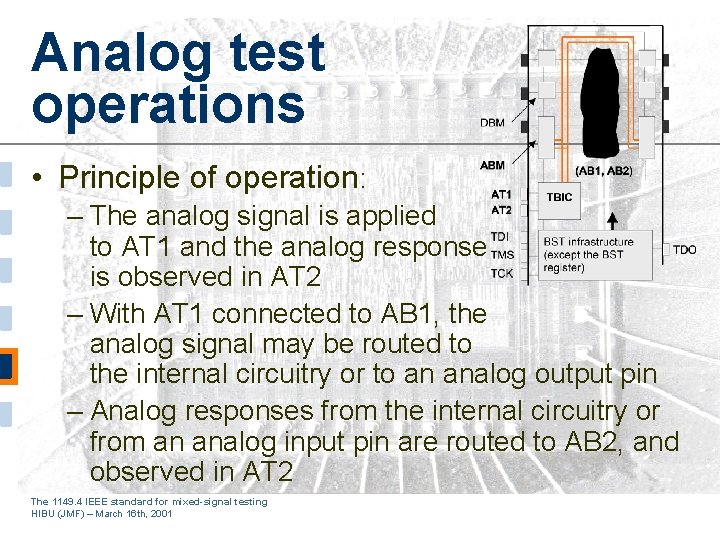

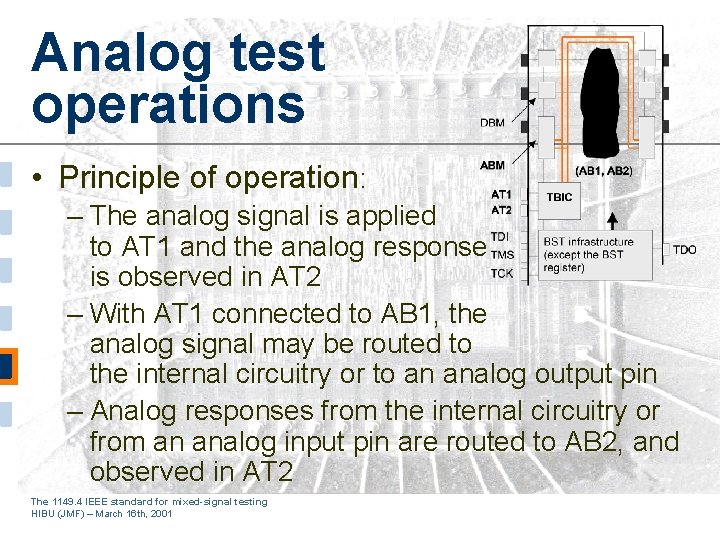

Analog test operations • Principle of operation: – The analog signal is applied to AT 1 and the analog response is observed in AT 2 – With AT 1 connected to AB 1, the analog signal may be routed to the internal circuitry or to an analog output pin – Analog responses from the internal circuitry or from an analog input pin are routed to AB 2, and observed in AT 2 The 1149. 4 IEEE standard for mixed-signal testing HIBU (JMF) – March 16 th, 2001

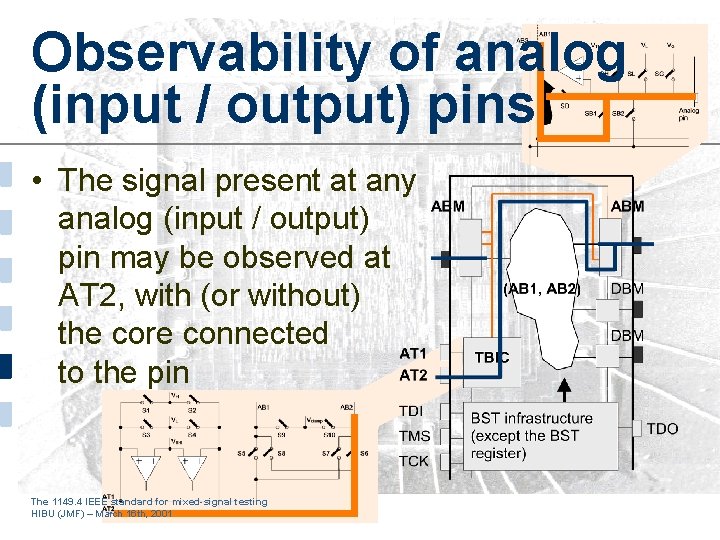

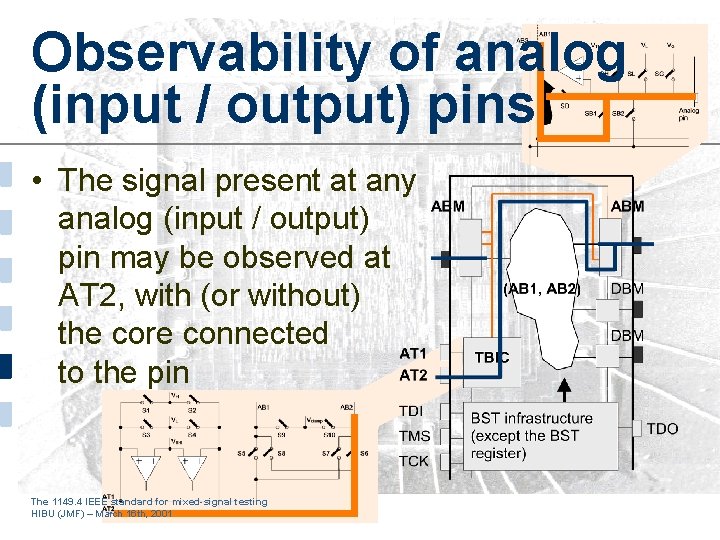

Observability of analog (input / output) pins • The signal present at any analog (input / output) pin may be observed at AT 2, with (or without) the core connected to the pin The 1149. 4 IEEE standard for mixed-signal testing HIBU (JMF) – March 16 th, 2001

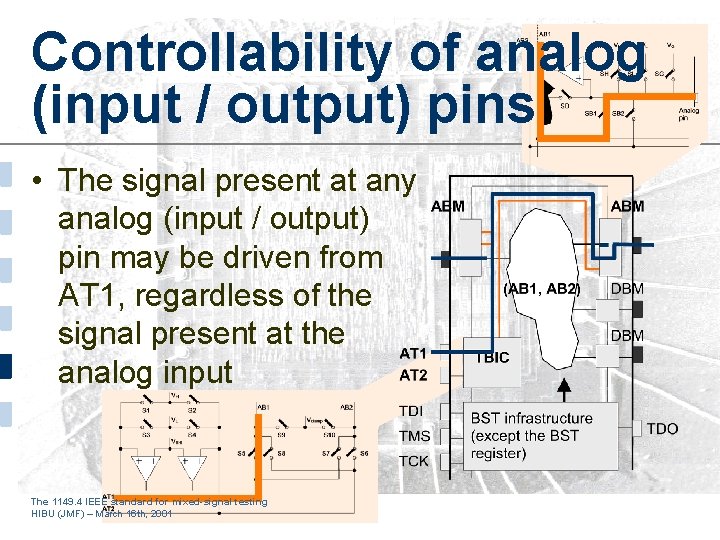

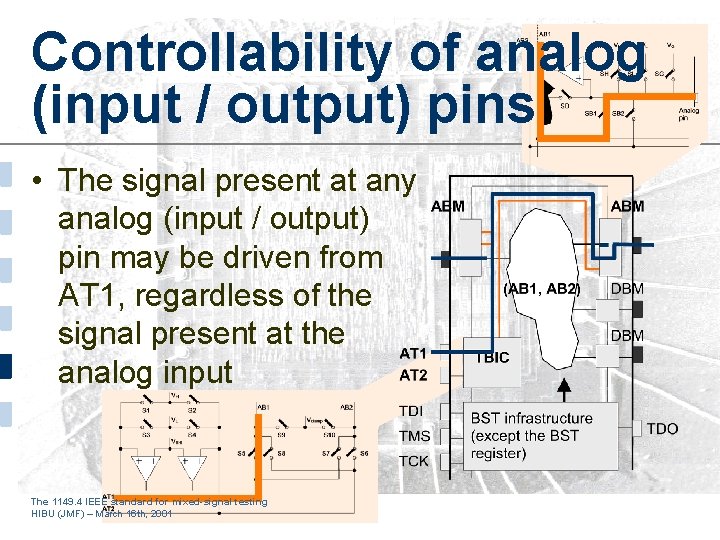

Controllability of analog (input / output) pins • The signal present at any analog (input / output) pin may be driven from AT 1, regardless of the signal present at the analog input The 1149. 4 IEEE standard for mixed-signal testing HIBU (JMF) – March 16 th, 2001

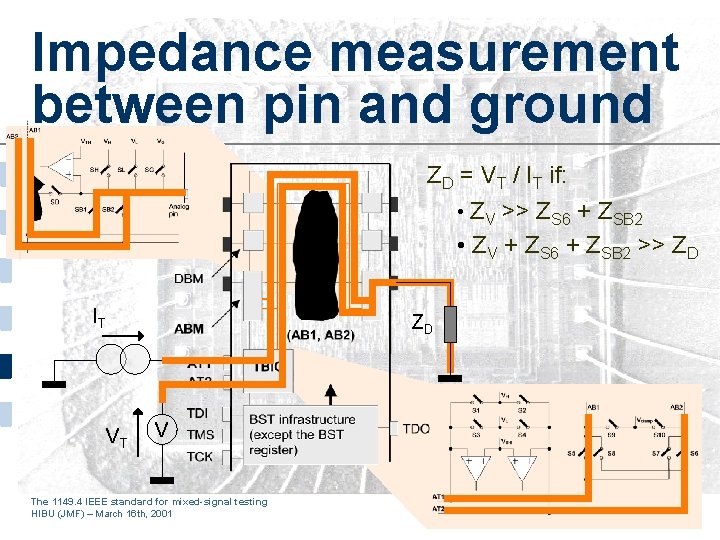

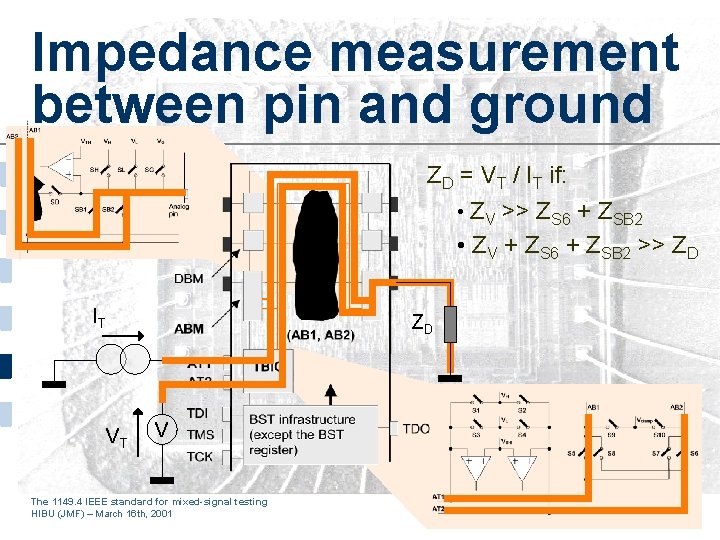

Impedance measurement between pin and ground ZD = VT / IT if: • ZV >> ZS 6 + ZSB 2 • ZV + ZS 6 + ZSB 2 >> ZD IT ZD VT V The 1149. 4 IEEE standard for mixed-signal testing HIBU (JMF) – March 16 th, 2001

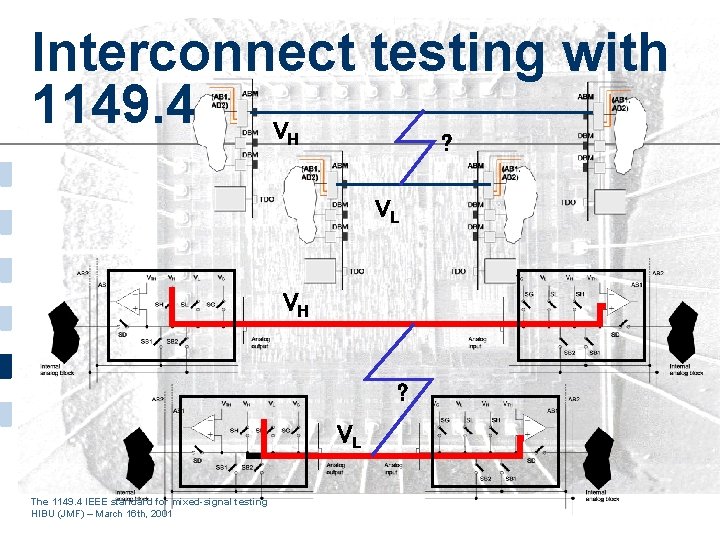

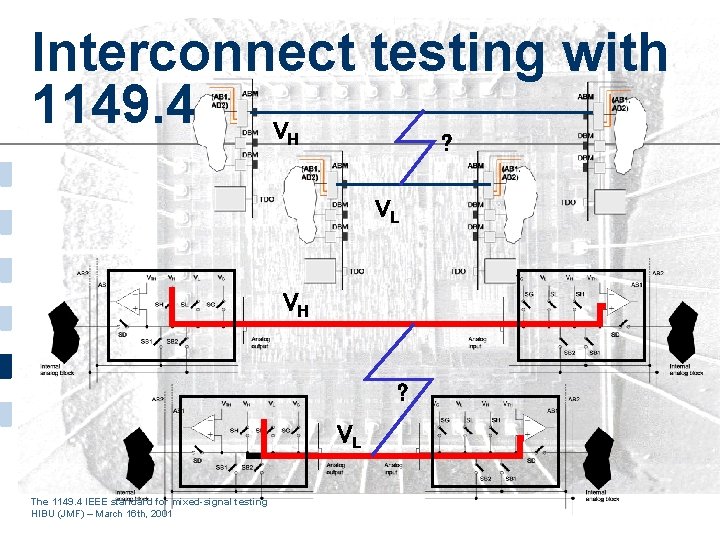

Interconnect testing with 1149. 4 V ? H VL VH ? VL The 1149. 4 IEEE standard for mixed-signal testing HIBU (JMF) – March 16 th, 2001

The IEEE 1149. 4 working group The 1149. 4 IEEE standard for mixed-signal testing HIBU (JMF) – March 16 th, 2001

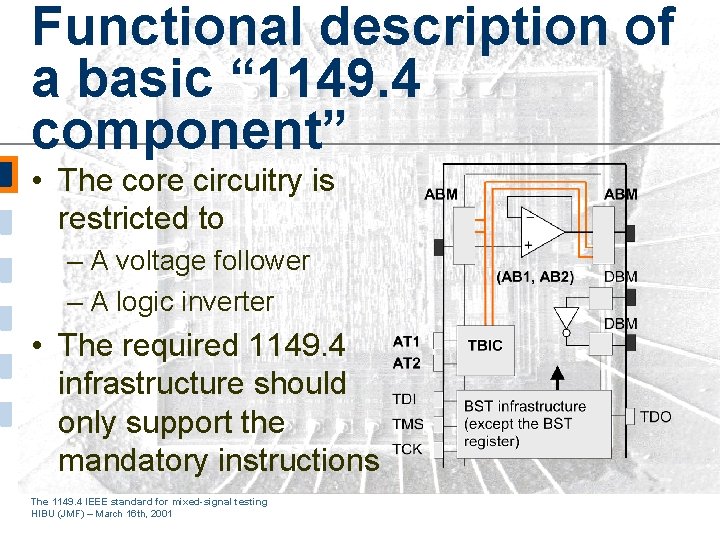

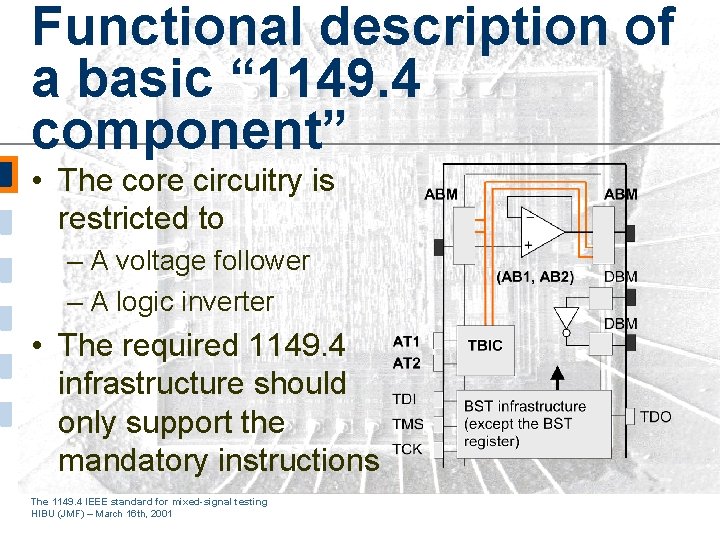

Functional description of a basic “ 1149. 4 component” • The core circuitry is restricted to – A voltage follower – A logic inverter • The required 1149. 4 infrastructure should only support the mandatory instructions The 1149. 4 IEEE standard for mixed-signal testing HIBU (JMF) – March 16 th, 2001

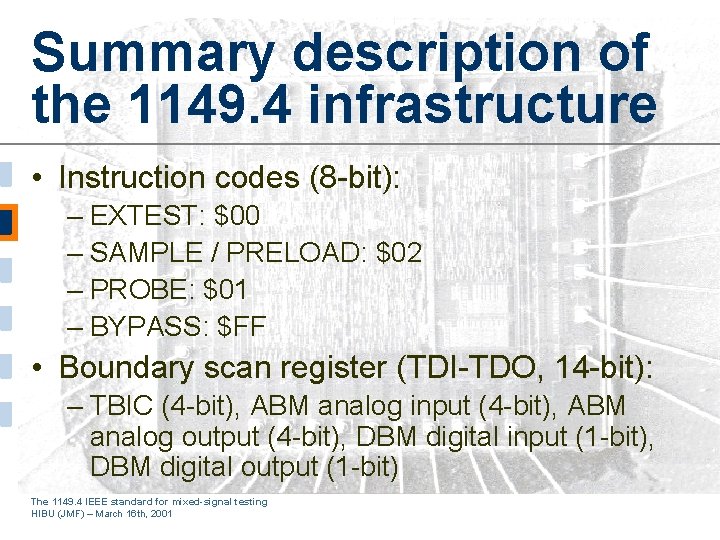

Summary description of the 1149. 4 infrastructure • Instruction codes (8 -bit): – EXTEST: $00 – SAMPLE / PRELOAD: $02 – PROBE: $01 – BYPASS: $FF • Boundary scan register (TDI-TDO, 14 -bit): – TBIC (4 -bit), ABM analog input (4 -bit), ABM analog output (4 -bit), DBM digital input (1 -bit), DBM digital output (1 -bit) The 1149. 4 IEEE standard for mixed-signal testing HIBU (JMF) – March 16 th, 2001

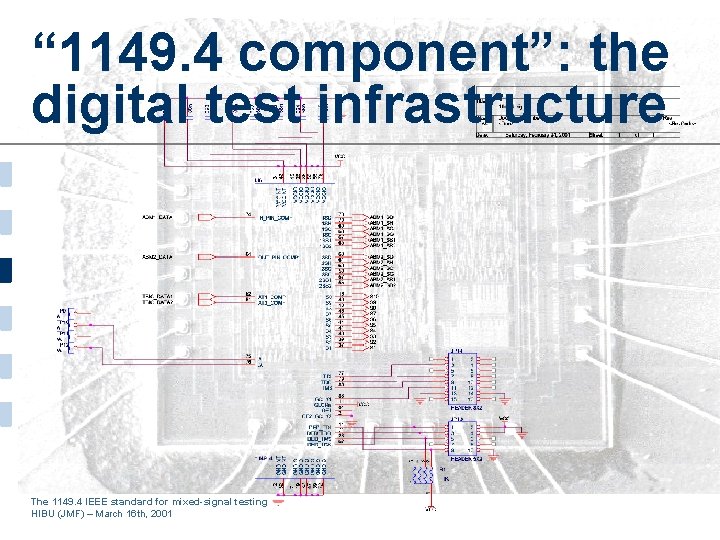

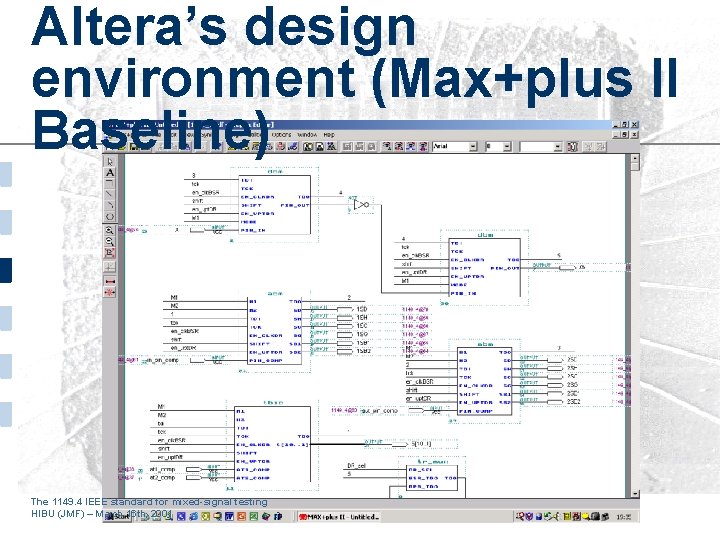

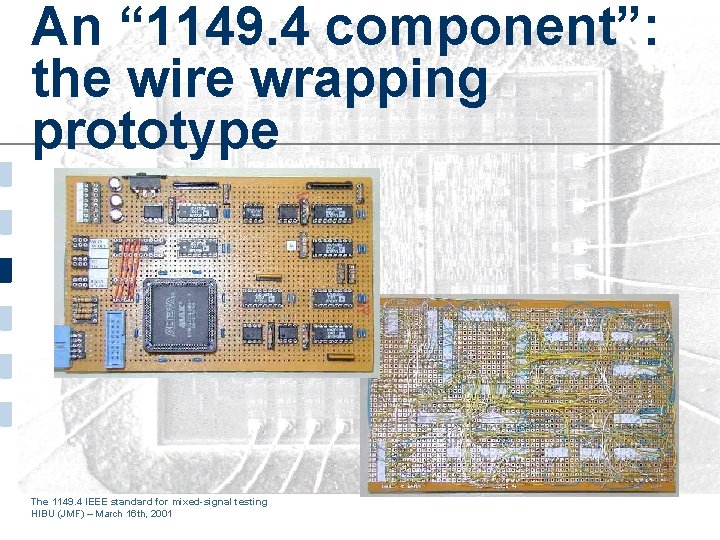

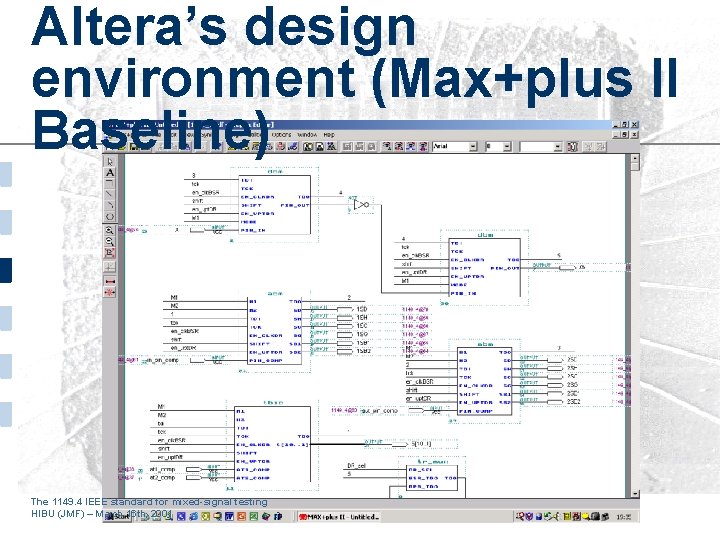

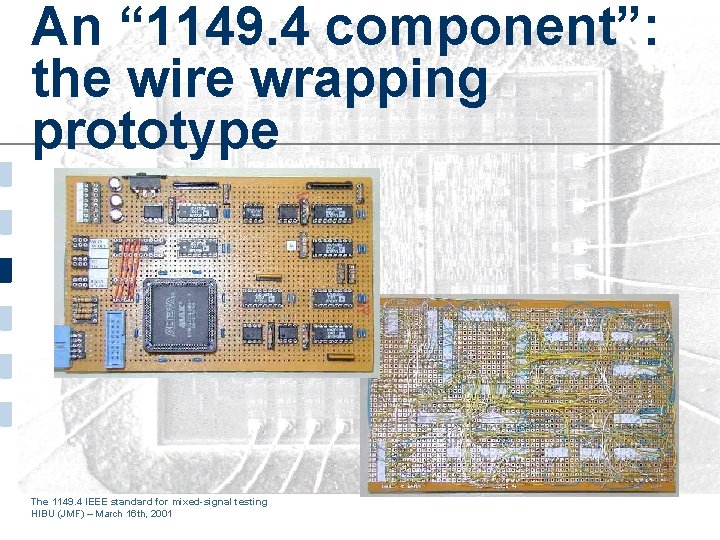

Implementation details • The digital test infrastructure and core logic was implemented in an EPM 7128 Altera PLD (2, 500 usable gates, 128 macrocells, 84 pin PLCC) • All remaining blocks are implemented using discrete components (ADG 452 analog switches, LM 311 comparators, TL 081 Op. Amp) The 1149. 4 IEEE standard for mixed-signal testing HIBU (JMF) – March 16 th, 2001

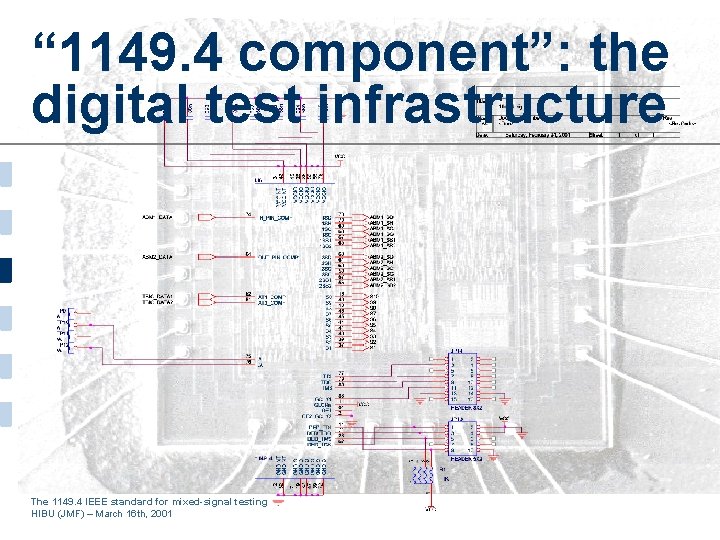

“ 1149. 4 component”: the digital test infrastructure The 1149. 4 IEEE standard for mixed-signal testing HIBU (JMF) – March 16 th, 2001

Altera’s design environment (Max+plus II Baseline) The 1149. 4 IEEE standard for mixed-signal testing HIBU (JMF) – March 16 th, 2001

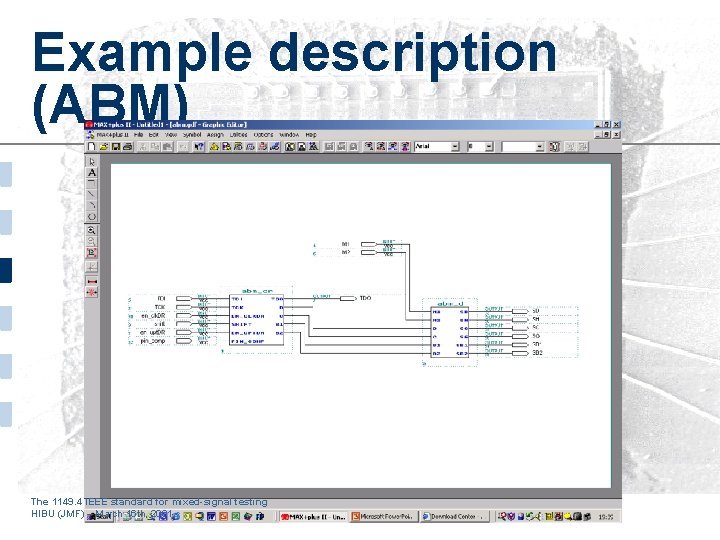

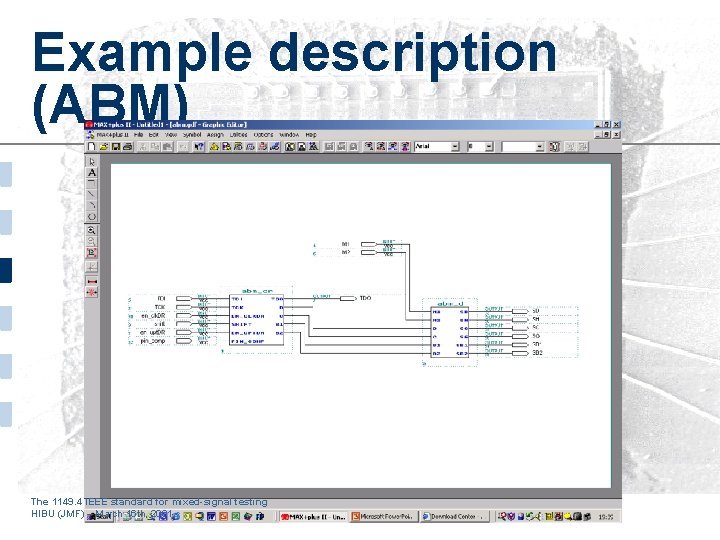

Example description (ABM) The 1149. 4 IEEE standard for mixed-signal testing HIBU (JMF) – March 16 th, 2001

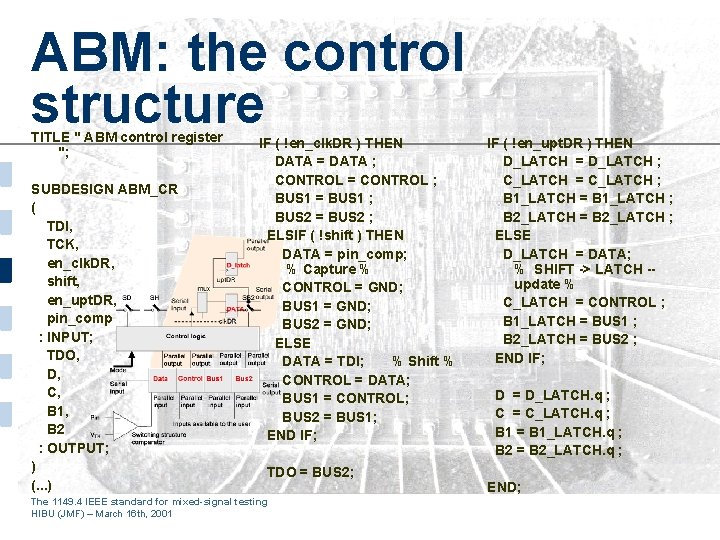

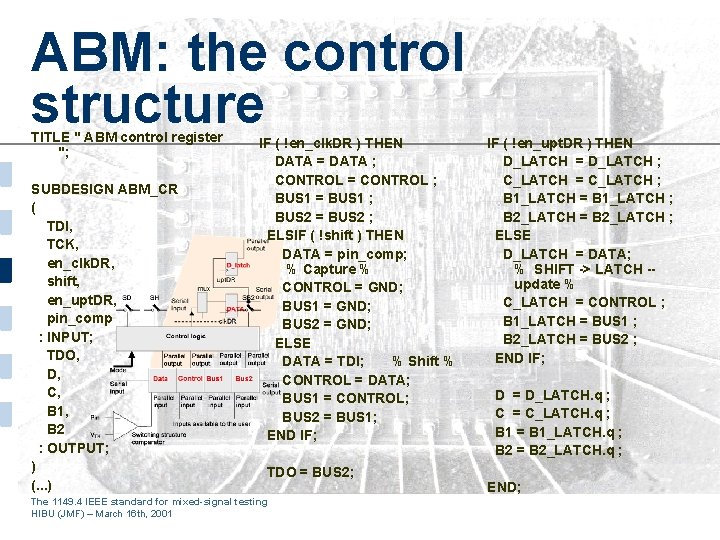

ABM: the control structure TITLE " ABM control register "; SUBDESIGN ABM_CR ( TDI, TCK, en_clk. DR, shift, en_upt. DR, pin_comp : INPUT; TDO, D, C, B 1, B 2 : OUTPUT; ) (. . . ) IF ( !en_clk. DR ) THEN DATA = DATA ; CONTROL = CONTROL ; BUS 1 = BUS 1 ; BUS 2 = BUS 2 ; ELSIF ( !shift ) THEN DATA = pin_comp; % Capture % CONTROL = GND; BUS 1 = GND; BUS 2 = GND; ELSE DATA = TDI; % Shift % CONTROL = DATA; BUS 1 = CONTROL; BUS 2 = BUS 1; END IF; TDO = BUS 2; The 1149. 4 IEEE standard for mixed-signal testing HIBU (JMF) – March 16 th, 2001 IF ( !en_upt. DR ) THEN D_LATCH = D_LATCH ; C_LATCH = C_LATCH ; B 1_LATCH = B 1_LATCH ; B 2_LATCH = B 2_LATCH ; ELSE D_LATCH = DATA; % SHIFT -> LATCH -update % C_LATCH = CONTROL ; B 1_LATCH = BUS 1 ; B 2_LATCH = BUS 2 ; END IF; D = D_LATCH. q ; C = C_LATCH. q ; B 1 = B 1_LATCH. q ; B 2 = B 2_LATCH. q ; END;

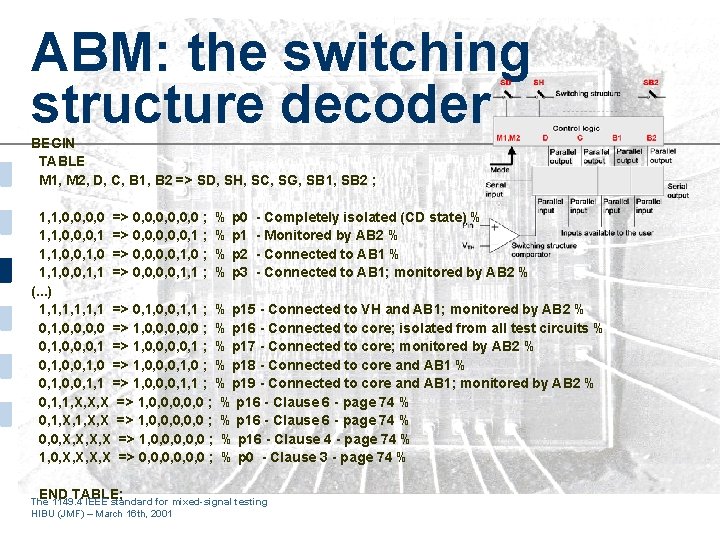

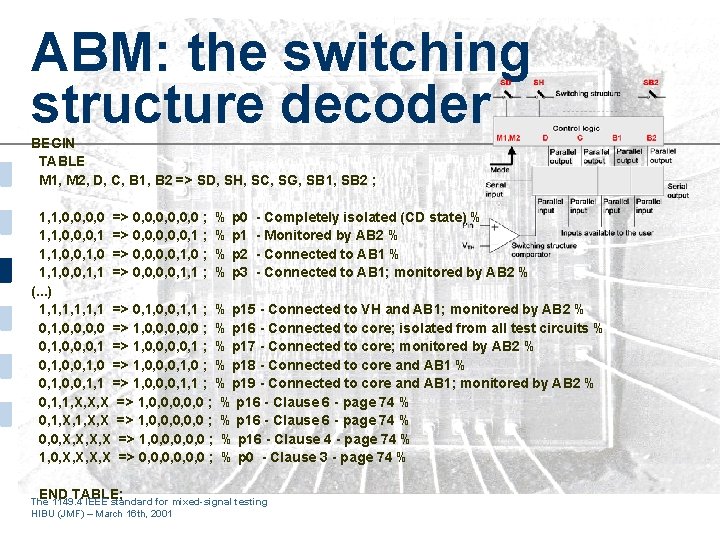

ABM: the switching structure decoder BEGIN TABLE M 1, M 2, D, C, B 1, B 2 => SD, SH, SC, SG, SB 1, SB 2 ; 1, 1, 0, 0 => 0, 0, 0, 0 ; % p 0 - Completely isolated (CD state) % 1, 1, 0, 0, 0, 1 => 0, 0, 0, 1 ; % p 1 - Monitored by AB 2 % 1, 1, 0, 0, 1, 0 => 0, 0, 1, 0 ; % p 2 - Connected to AB 1 % 1, 1, 0, 0, 1, 1 => 0, 0, 1, 1 ; % p 3 - Connected to AB 1; monitored by AB 2 % (. . . ) 1, 1, 1, 1 => 0, 1, 0, 0, 1, 1 ; % p 15 - Connected to VH and AB 1; monitored by AB 2 % 0, 1, 0, 0 => 1, 0, 0, 0 ; % p 16 - Connected to core; isolated from all test circuits % 0, 1, 0, 0, 0, 1 => 1, 0, 0, 1 ; % p 17 - Connected to core; monitored by AB 2 % 0, 1, 0, 0, 1, 0 => 1, 0, 0, 0, 1, 0 ; % p 18 - Connected to core and AB 1 % 0, 1, 0, 0, 1, 1 => 1, 0, 0, 0, 1, 1 ; % p 19 - Connected to core and AB 1; monitored by AB 2 % 0, 1, 1, X, X, X => 1, 0, 0, 0 ; % p 16 - Clause 6 - page 74 % 0, 1, X, X => 1, 0, 0, 0 ; % p 16 - Clause 6 - page 74 % 0, 0, X, X => 1, 0, 0, 0 ; % p 16 - Clause 4 - page 74 % 1, 0, X, X => 0, 0, 0, 0 ; % p 0 - Clause 3 - page 74 % END TABLE; The 1149. 4 IEEE standard for mixed-signal testing HIBU (JMF) – March 16 th, 2001

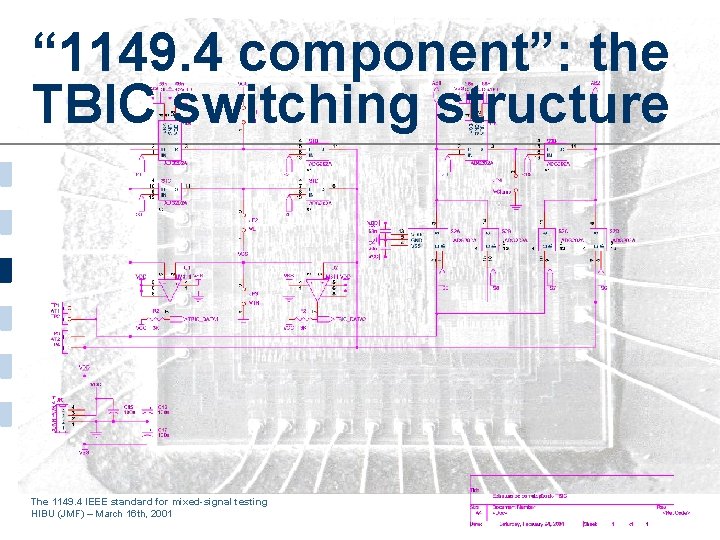

“ 1149. 4 component”: the TBIC switching structure The 1149. 4 IEEE standard for mixed-signal testing HIBU (JMF) – March 16 th, 2001

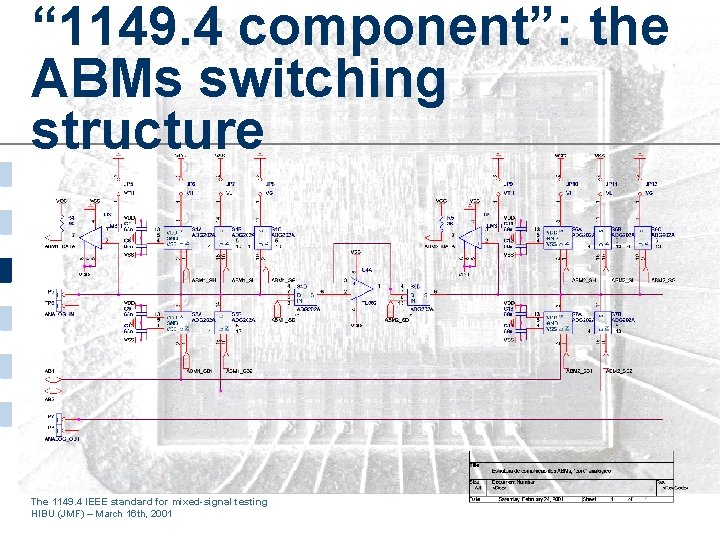

“ 1149. 4 component”: the ABMs switching structure The 1149. 4 IEEE standard for mixed-signal testing HIBU (JMF) – March 16 th, 2001

An “ 1149. 4 component”: the wire wrapping prototype The 1149. 4 IEEE standard for mixed-signal testing HIBU (JMF) – March 16 th, 2001

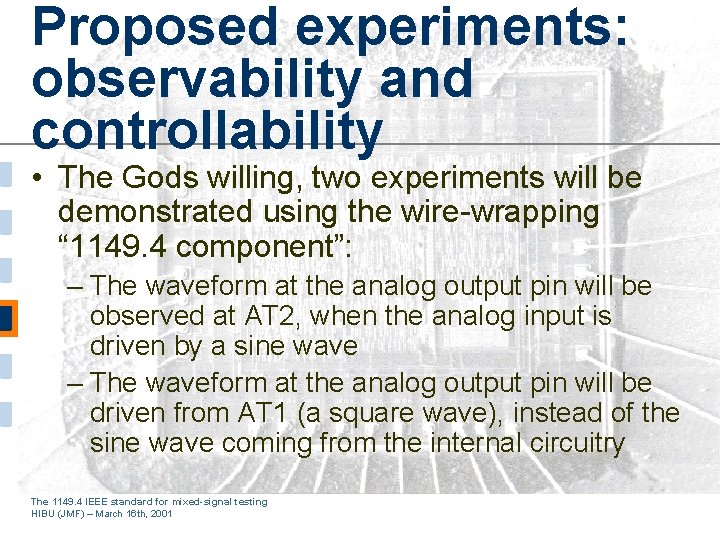

Proposed experiments: observability and controllability • The Gods willing, two experiments will be demonstrated using the wire-wrapping “ 1149. 4 component”: – The waveform at the analog output pin will be observed at AT 2, when the analog input is driven by a sine wave – The waveform at the analog output pin will be driven from AT 1 (a square wave), instead of the sine wave coming from the internal circuitry The 1149. 4 IEEE standard for mixed-signal testing HIBU (JMF) – March 16 th, 2001

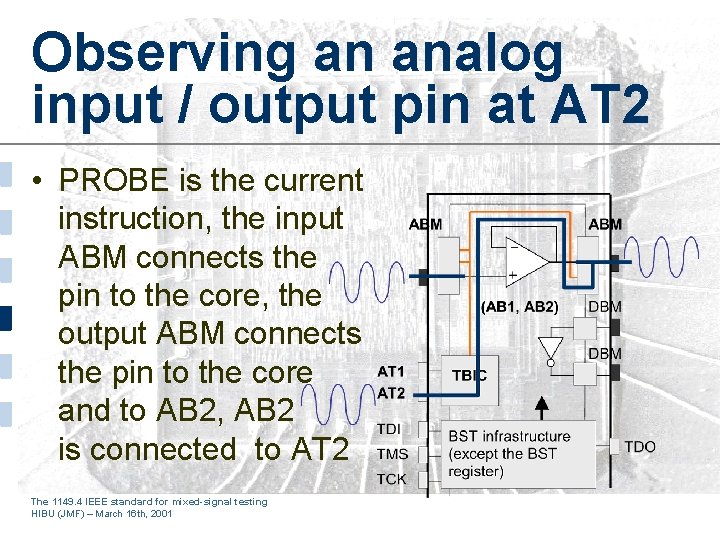

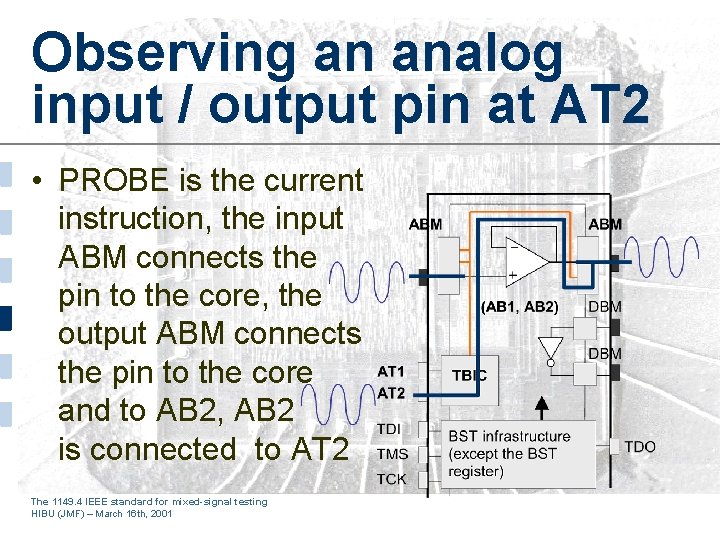

Observing an analog input / output pin at AT 2 • PROBE is the current instruction, the input ABM connects the pin to the core, the output ABM connects the pin to the core and to AB 2, AB 2 is connected to AT 2 The 1149. 4 IEEE standard for mixed-signal testing HIBU (JMF) – March 16 th, 2001

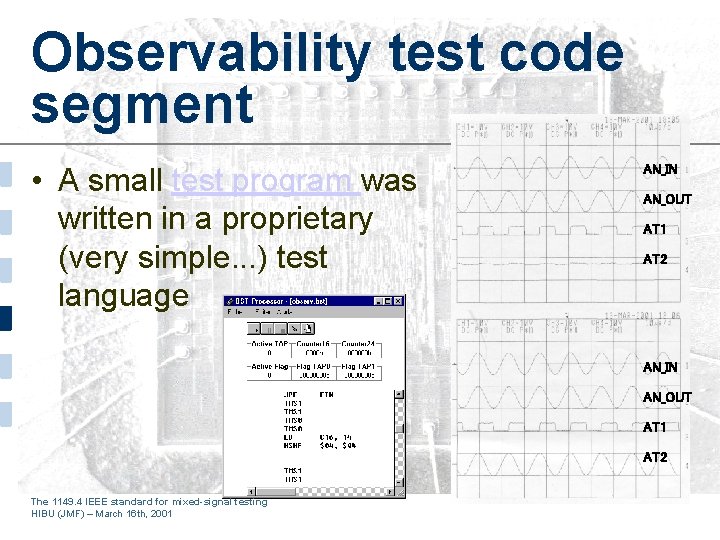

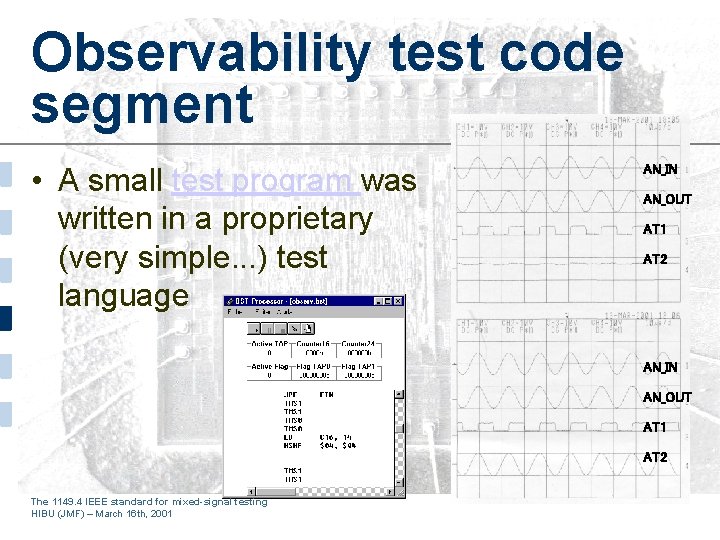

Observability test code segment • A small test program was written in a proprietary (very simple. . . ) test language AN_IN AN_OUT AT 1 AT 2 The 1149. 4 IEEE standard for mixed-signal testing HIBU (JMF) – March 16 th, 2001

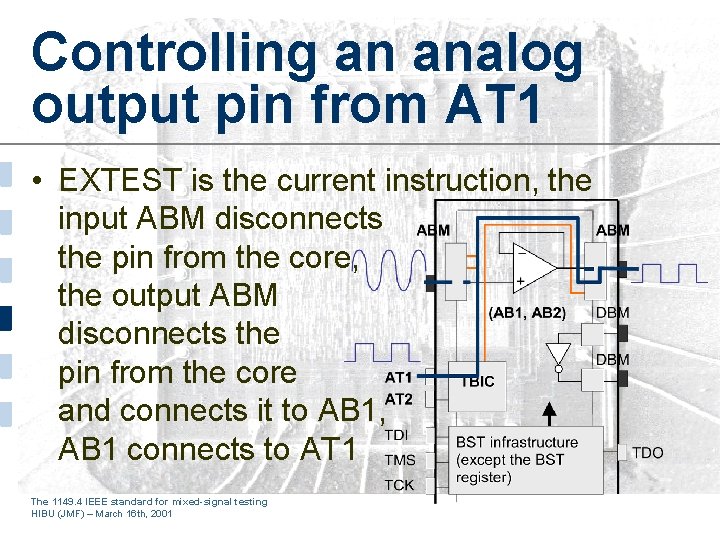

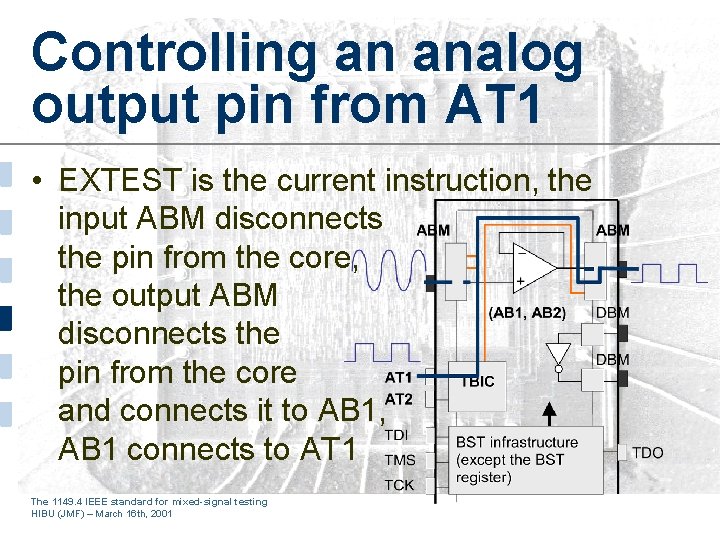

Controlling an analog output pin from AT 1 • EXTEST is the current instruction, the input ABM disconnects the pin from the core, the output ABM disconnects the pin from the core and connects it to AB 1, AB 1 connects to AT 1 The 1149. 4 IEEE standard for mixed-signal testing HIBU (JMF) – March 16 th, 2001

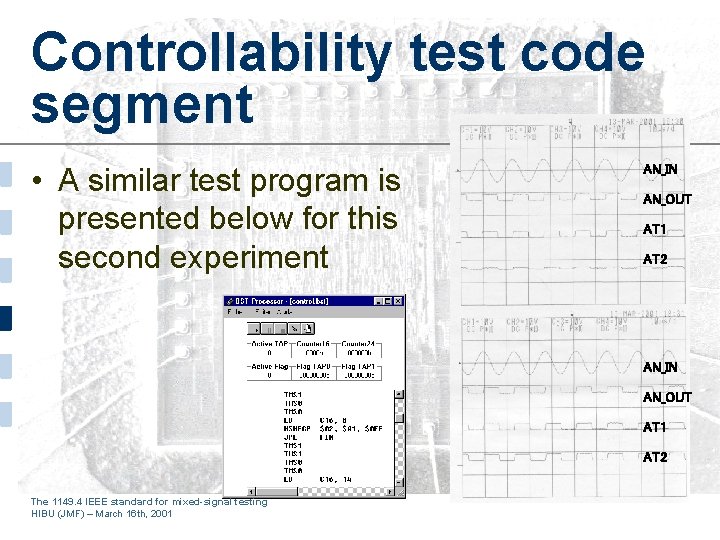

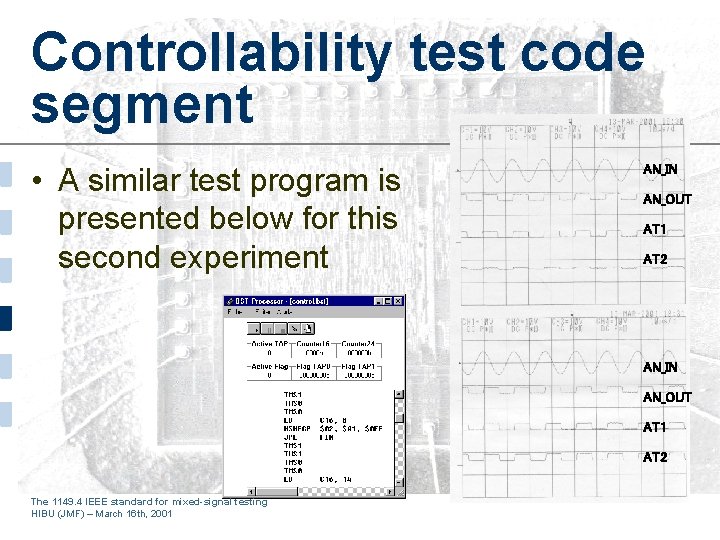

Controllability test code segment • A similar test program is presented below for this second experiment AN_IN AN_OUT AT 1 AT 2 The 1149. 4 IEEE standard for mixed-signal testing HIBU (JMF) – March 16 th, 2001

The ALLEGRO web page to support this course • http: //www. fe. up. pt/~allegro/wp 3. htm The 1149. 4 IEEE standard for mixed-signal testing HIBU (JMF) – March 16 th, 2001

The ALLEGRO Web. CT server for mixed-signal training • http: //pandora. fe. up. pt: 8900 (ittf 1149. 4 as username and password) The 1149. 4 IEEE standard for mixed-signal testing HIBU (JMF) – March 16 th, 2001