A Novel TimingDriven Global Routing Algorithm Considering Coupling

A Novel Timing-Driven Global Routing Algorithm Considering Coupling Effects for High Performance Circuit Design Jingyu Xu, Xianlong Hong, Tong Jing, Yici Cai Dept. of Computer Science & Technology, Tsinghua Univ. Jun Gu Dept. of Computer Science, Hong Kong Univ. of S & T P. R. China ASP-DAC 2003/11/28 THEDA

Agenda l Introduction l Problem Formulation l Timing Analysis l Global Routing Algorithm l Experiment Result l Conclusion 2003/11/28 THEDA 2

Introduction (1/3) l As we move towards VDSM, there are two major concerns for chip performance: 1. The power and ground noise cause by simultaneously switching circuits 2. Increasing aspect ratio of wires and decreasing of interconnect spacing 2003/11/28 THEDA 3

Introduction (2/3) l Previous works did various contributions to timing optimization for global routing, but may have deviations in VDSM. l Delay models such as Elmore delay may not have good estimation in VDSM. 2003/11/28 THEDA 4

Introduction (3/3) l Increasing concern has been raised regarding the coupling effects, and mainly falls into two categories: 1. 2. Minimizing crosstalk effects w/o emphasizing timing constraints Estimating coupling capacitance for optimal wire sizing and spacing w/o carrying out topological optimization No measurements of coupling effects on interconnect delay to guide routing process !! 2003/11/28 THEDA 5

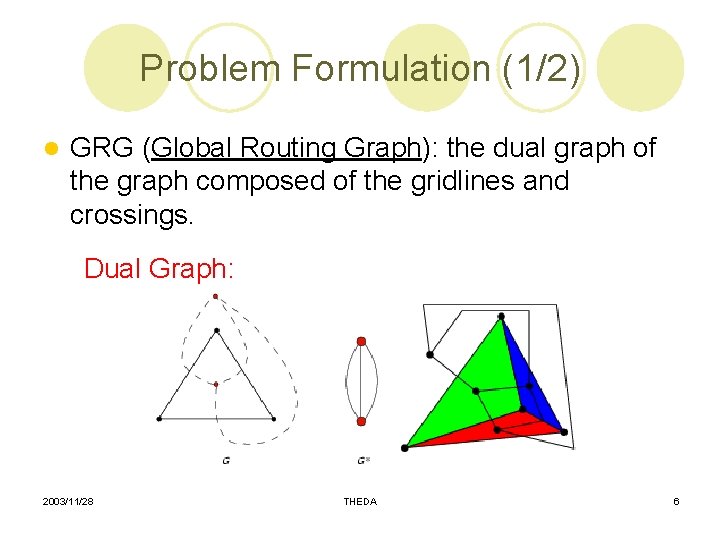

Problem Formulation (1/2) l GRG (Global Routing Graph): the dual graph of the graph composed of the gridlines and crossings. Dual Graph: 2003/11/28 THEDA 6

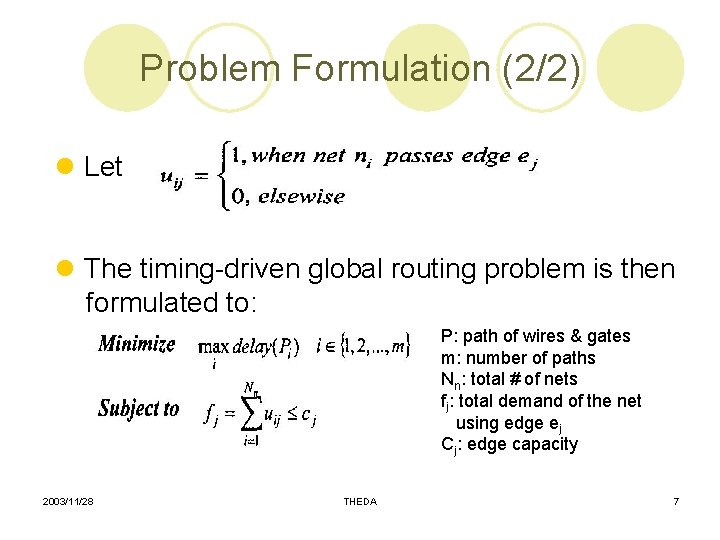

Problem Formulation (2/2) l Let l The timing-driven global routing problem is then formulated to: P: path of wires & gates m: number of paths Nn: total # of nets fj: total demand of the net using edge ej Cj: edge capacity 2003/11/28 THEDA 7

![Timing Analysis (1/4) l Wire-Load-Estimation Model Ref. [12] X. D. Yang, Ph. D. thesis Timing Analysis (1/4) l Wire-Load-Estimation Model Ref. [12] X. D. Yang, Ph. D. thesis](http://slidetodoc.com/presentation_image_h2/e9e19acc0ab04dc613a22344c5789823/image-8.jpg)

Timing Analysis (1/4) l Wire-Load-Estimation Model Ref. [12] X. D. Yang, Ph. D. thesis By simulation and curve-fitting, the largest error in estimation parasitics is 5% With specified information as input, we can extract all capacitance around the conductor 2003/11/28 THEDA 8

![Timing Analysis (2/4) l Interconnect Delay Model Ref. [13] A. Odabasioglu, et al. , Timing Analysis (2/4) l Interconnect Delay Model Ref. [13] A. Odabasioglu, et al. ,](http://slidetodoc.com/presentation_image_h2/e9e19acc0ab04dc613a22344c5789823/image-9.jpg)

Timing Analysis (2/4) l Interconnect Delay Model Ref. [13] A. Odabasioglu, et al. , ICCAD 1997 Reduce the order of large RC net-lists and reach a good trade-off between accuracy and speed The result can be within 1% of SPICE simulation 2003/11/28 THEDA 9

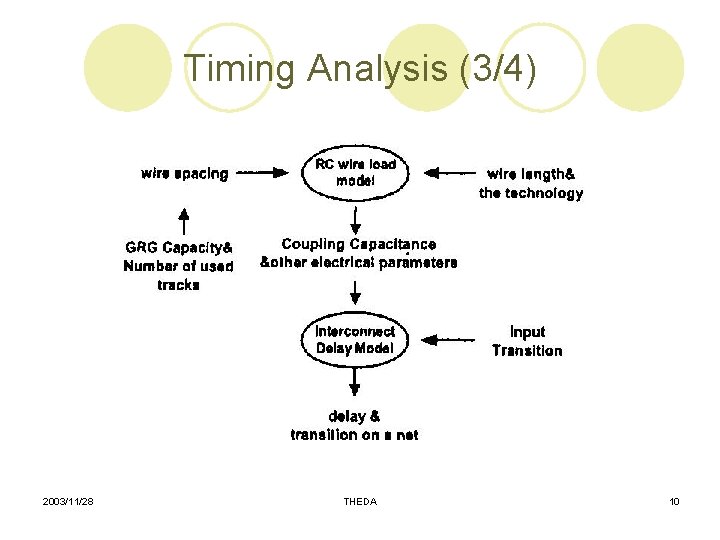

Timing Analysis (3/4) 2003/11/28 THEDA 10

![Timing Analysis (4/4) l Gate delay estimation Ref. [14] J. Lillis, et al. , Timing Analysis (4/4) l Gate delay estimation Ref. [14] J. Lillis, et al. ,](http://slidetodoc.com/presentation_image_h2/e9e19acc0ab04dc613a22344c5789823/image-11.jpg)

Timing Analysis (4/4) l Gate delay estimation Ref. [14] J. Lillis, et al. , DAC 1998 Use table-lookup model The LUTs are all from industrial circuit library 2003/11/28 THEDA 11

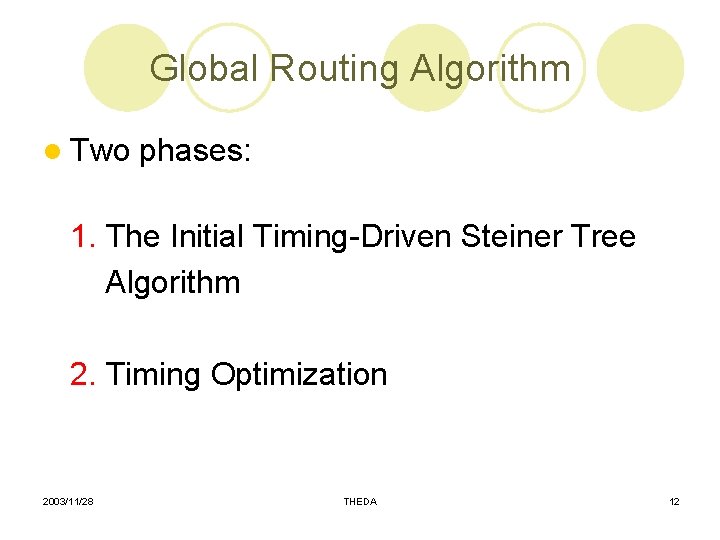

Global Routing Algorithm l Two phases: 1. The Initial Timing-Driven Steiner Tree Algorithm 2. Timing Optimization 2003/11/28 THEDA 12

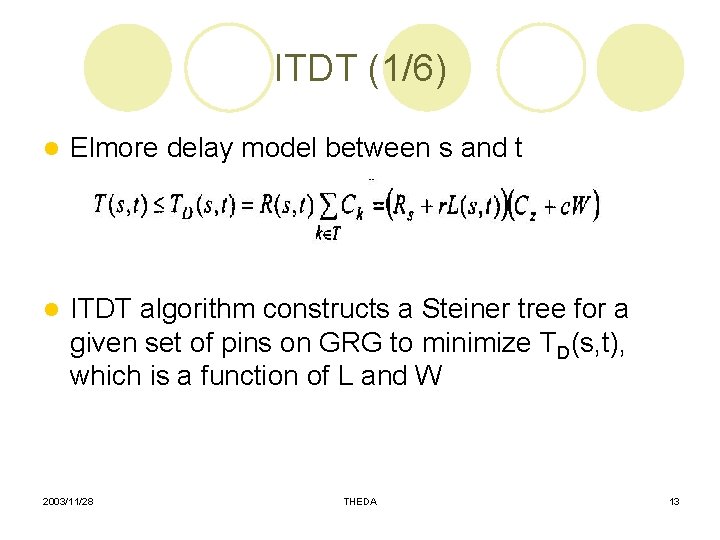

ITDT (1/6) l Elmore delay model between s and t l ITDT algorithm constructs a Steiner tree for a given set of pins on GRG to minimize TD(s, t), which is a function of L and W 2003/11/28 THEDA 13

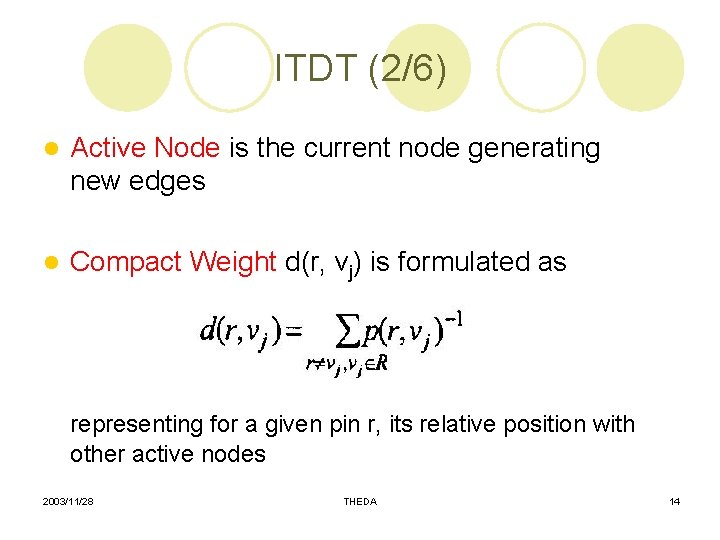

ITDT (2/6) l Active Node is the current node generating new edges l Compact Weight d(r, vj) is formulated as representing for a given pin r, its relative position with other active nodes 2003/11/28 THEDA 14

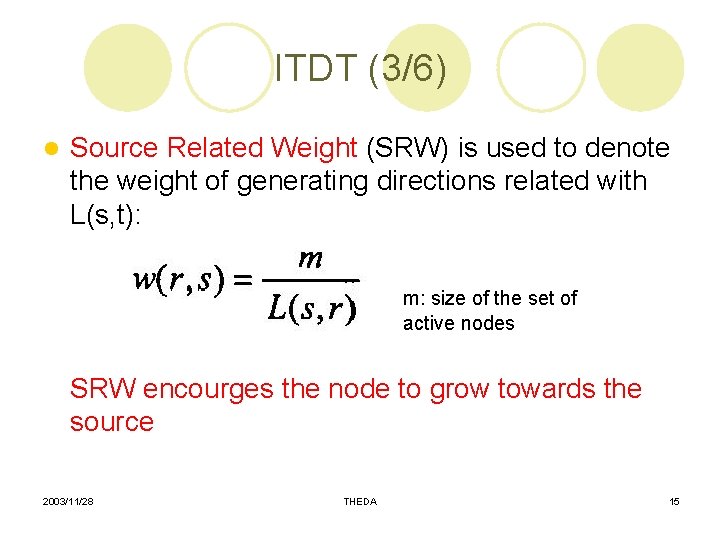

ITDT (3/6) l Source Related Weight (SRW) is used to denote the weight of generating directions related with L(s, t): m: size of the set of active nodes SRW encourges the node to grow towards the source 2003/11/28 THEDA 15

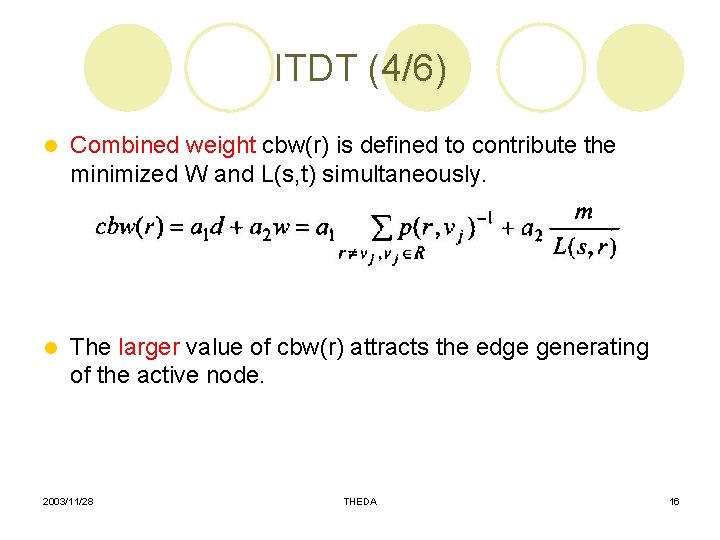

ITDT (4/6) l Combined weight cbw(r) is defined to contribute the minimized W and L(s, t) simultaneously. l The larger value of cbw(r) attracts the edge generating of the active node. 2003/11/28 THEDA 16

ITDT (5/6) 2003/11/28 THEDA 17

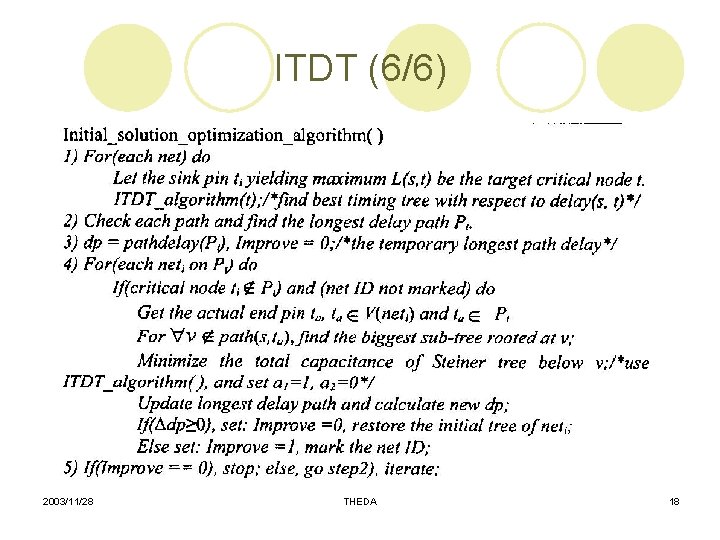

ITDT (6/6) 2003/11/28 THEDA 18

![Timing Optimization (1/8) l [Strategy] Based on initial solution, we optimize the network topology Timing Optimization (1/8) l [Strategy] Based on initial solution, we optimize the network topology](http://slidetodoc.com/presentation_image_h2/e9e19acc0ab04dc613a22344c5789823/image-19.jpg)

Timing Optimization (1/8) l [Strategy] Based on initial solution, we optimize the network topology to adjust most congested area, but keep most critical path for good timing performance 2003/11/28 THEDA 19

Timing Optimization (2/8) l For a neti on the critical path, ti is the proportion of delay contributed by it to the total path delay l Build “forbidden net list” for rerouting by a given threshold t What if t=0? Or if t is small? 2003/11/28 THEDA 20

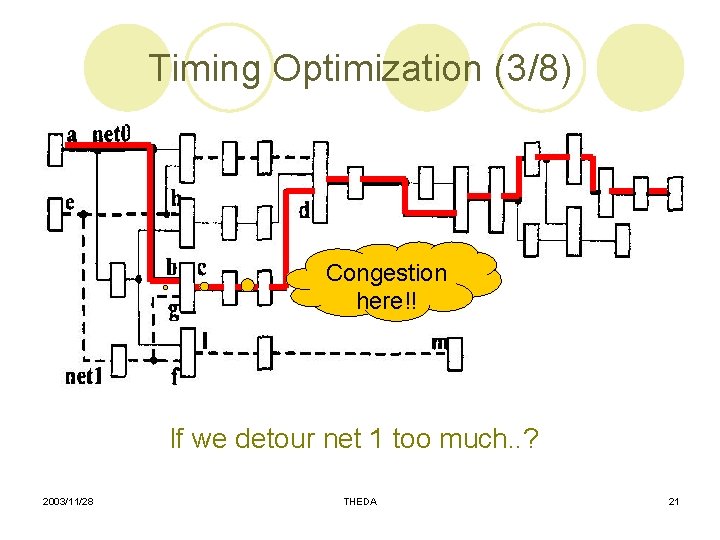

Timing Optimization (3/8) Congestion here!! If we detour net 1 too much. . ? 2003/11/28 THEDA 21

Timing Optimization (4/8) l When applying congestion optimization algorithm, we also do the transference of the coupling capacitance simultaneously 2003/11/28 THEDA 22

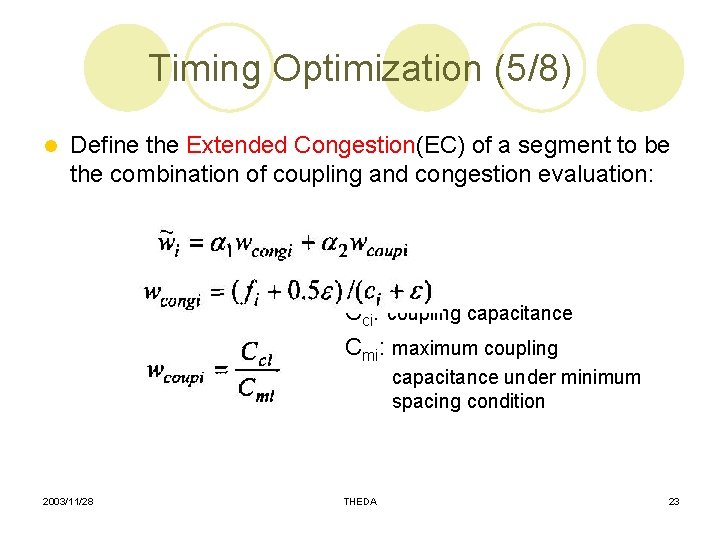

Timing Optimization (5/8) l Define the Extended Congestion(EC) of a segment to be the combination of coupling and congestion evaluation: Cci: coupling capacitance Cmi: maximum coupling capacitance under minimum spacing condition 2003/11/28 THEDA 23

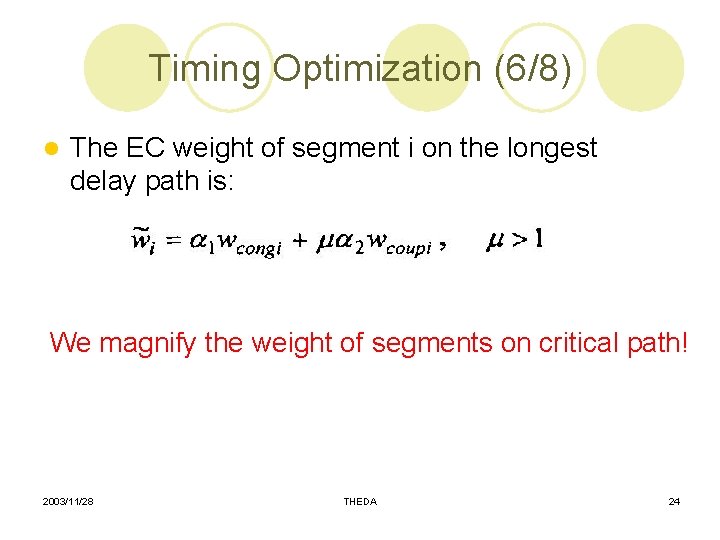

Timing Optimization (6/8) l The EC weight of segment i on the longest delay path is: We magnify the weight of segments on critical path! 2003/11/28 THEDA 24

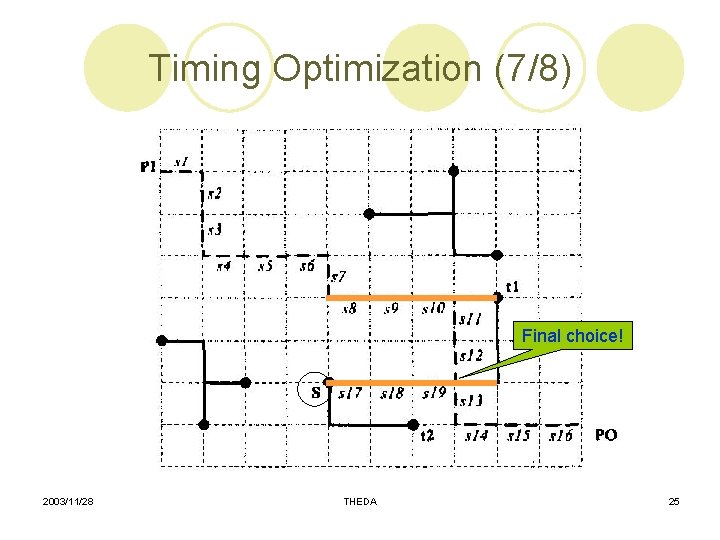

Timing Optimization (7/8) Final choice! 2003/11/28 THEDA 25

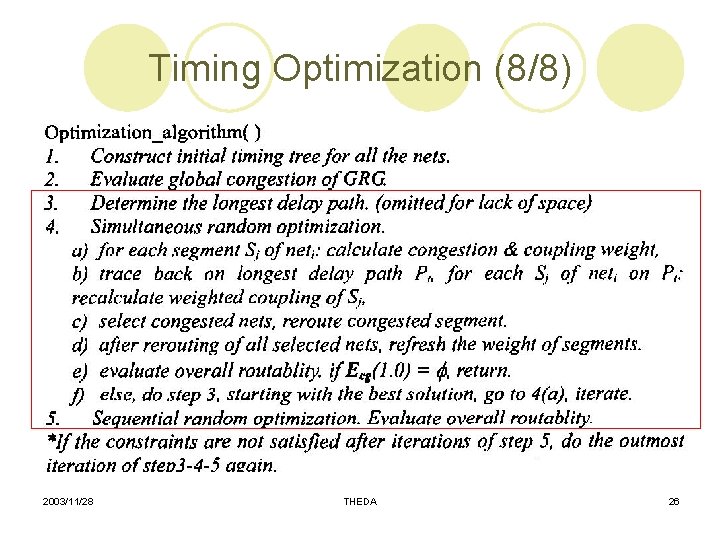

Timing Optimization (8/8) 2003/11/28 THEDA 26

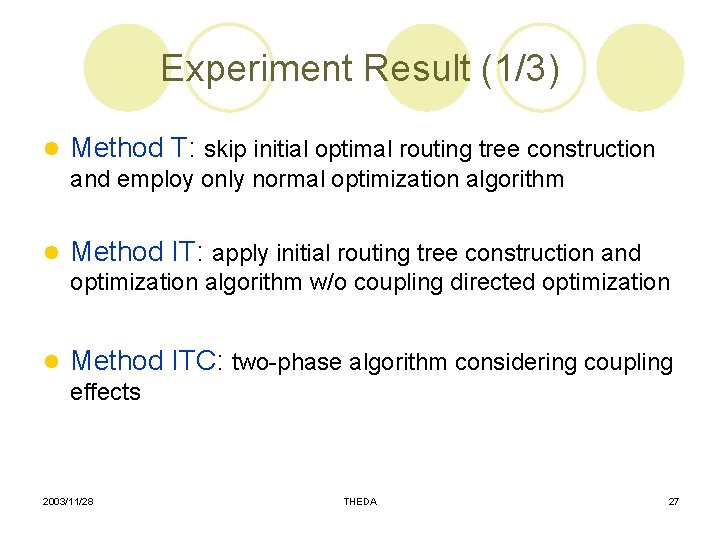

Experiment Result (1/3) l Method T: skip initial optimal routing tree construction and employ only normal optimization algorithm l Method IT: apply initial routing tree construction and optimization algorithm w/o coupling directed optimization l Method ITC: two-phase algorithm considering coupling effects 2003/11/28 THEDA 27

Experiment Result (2/3) 2003/11/28 THEDA 28

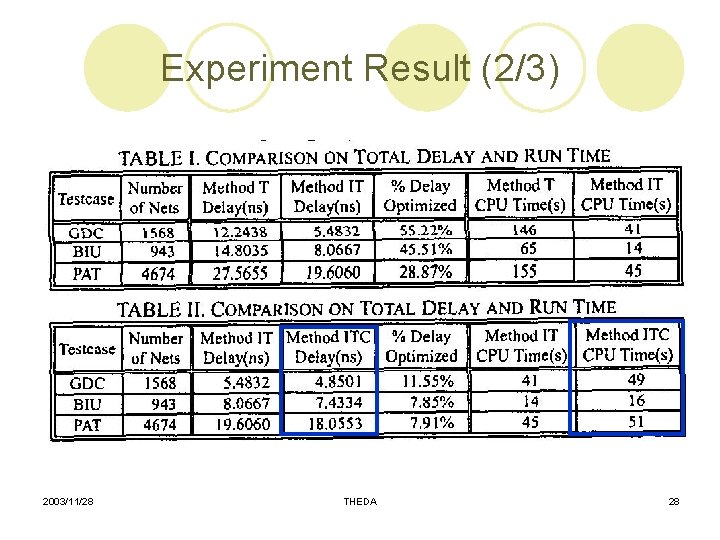

Experiment Result (3/3) 2003/11/28 THEDA 29

Conclusion l A new timing-driven global routing algorithm is proposed l By taking coupling effects into account and utilizing it in optimization process, delay performance is improved l Experimental result shows good trade-off between accuracy and speed 2003/11/28 THEDA 30

- Slides: 30