A Codesign and Cosimulation Environment Based on MATLABSimulink

A Codesign and Cosimulation Environment Based on MATLAB/Simulink Models Application to the design of a Common Rail test bench L. M. Reyneri, E. Bellei, E. Bussolino, L. Mari, F. Renga September 2002 Politecnico di Torino 18/19 September 2002 Code. Simulink: a HW/SW Codesign Environment 1

Part I A Typical Design Framework 18/19 September 2002 Code. Simulink: a HW/SW Codesign Environment 2

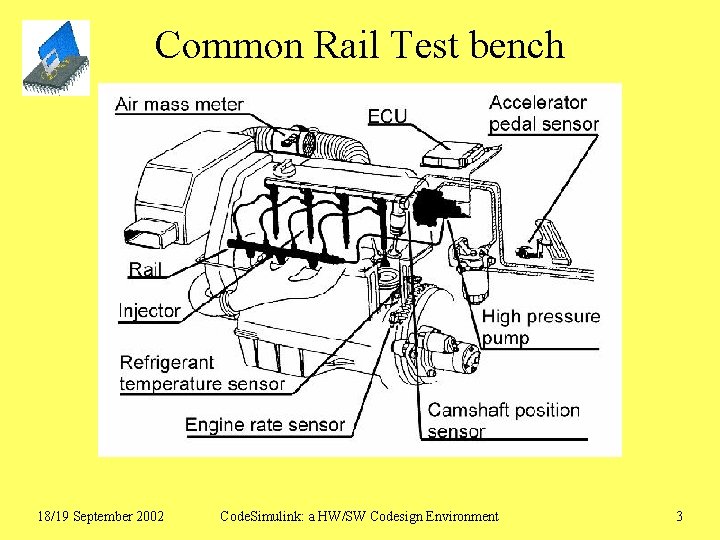

Common Rail Test bench 18/19 September 2002 Code. Simulink: a HW/SW Codesign Environment 3

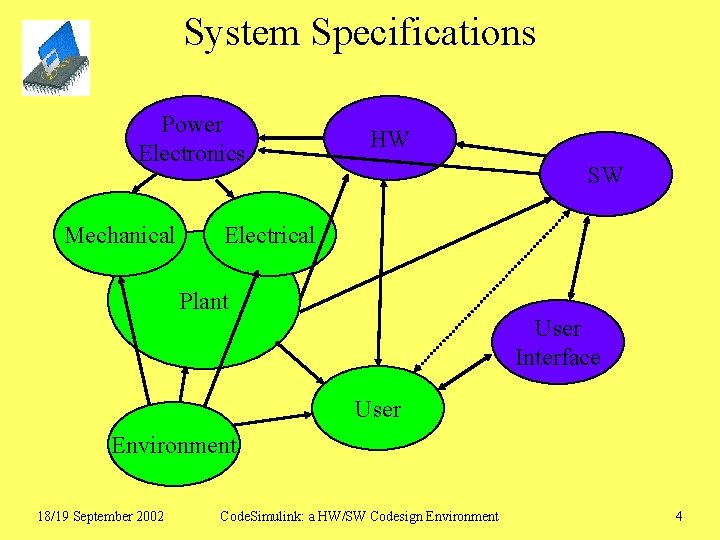

System Specifications Power Electronics Mechanical HW SW Electrical Plant User Interface User Environment 18/19 September 2002 Code. Simulink: a HW/SW Codesign Environment 4

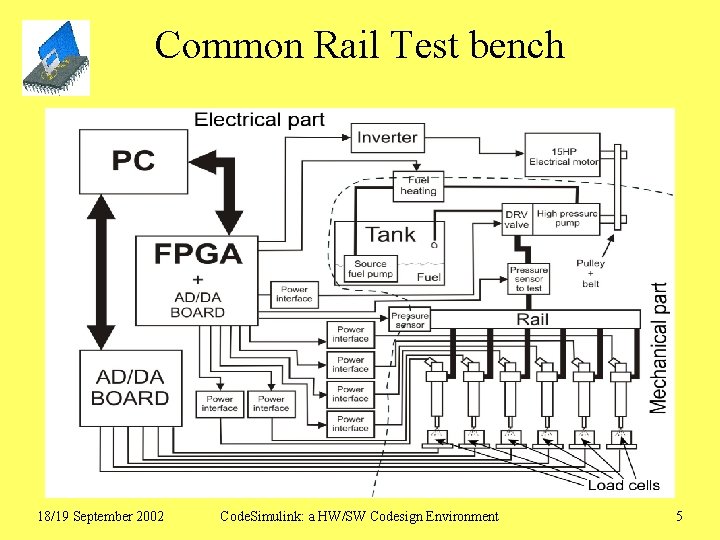

Common Rail Test bench 18/19 September 2002 Code. Simulink: a HW/SW Codesign Environment 5

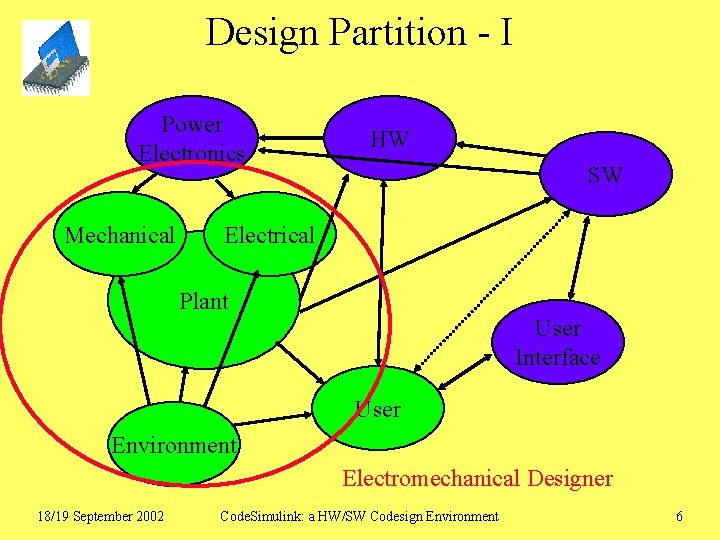

Design Partition - I Power Electronics Mechanical HW SW Electrical Plant User Interface User Environment Electromechanical Designer 18/19 September 2002 Code. Simulink: a HW/SW Codesign Environment 6

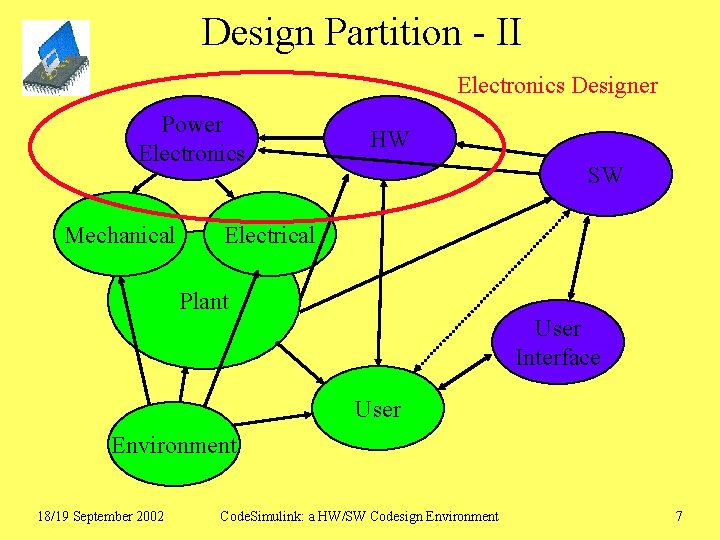

Design Partition - II Electronics Designer Power Electronics Mechanical HW SW Electrical Plant User Interface User Environment 18/19 September 2002 Code. Simulink: a HW/SW Codesign Environment 7

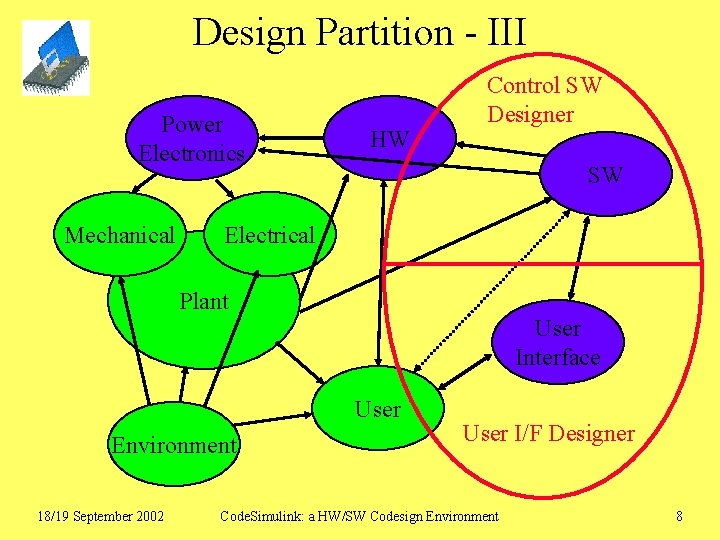

Design Partition - III Power Electronics Mechanical HW Control SW Designer SW Electrical Plant User Interface User Environment 18/19 September 2002 User I/F Designer Code. Simulink: a HW/SW Codesign Environment 8

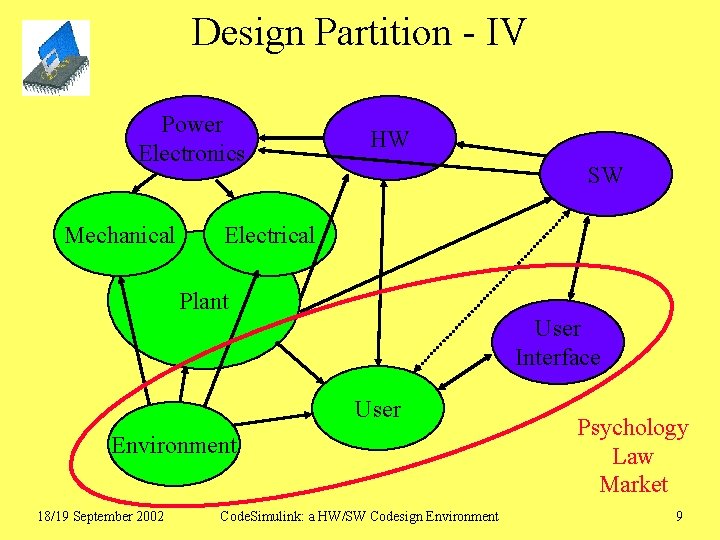

Design Partition - IV Power Electronics Mechanical HW SW Electrical Plant User Interface User Environment 18/19 September 2002 Code. Simulink: a HW/SW Codesign Environment Psychology Law Market 9

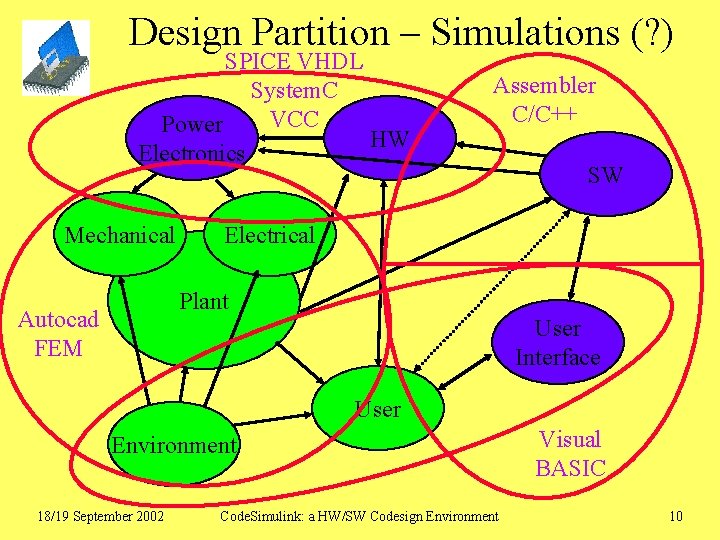

Design Partition – Simulations (? ) SPICE VHDL System. C VCC Power HW Electronics Mechanical Assembler C/C++ SW Electrical Plant Autocad FEM User Interface User Environment 18/19 September 2002 Code. Simulink: a HW/SW Codesign Environment Visual BASIC 10

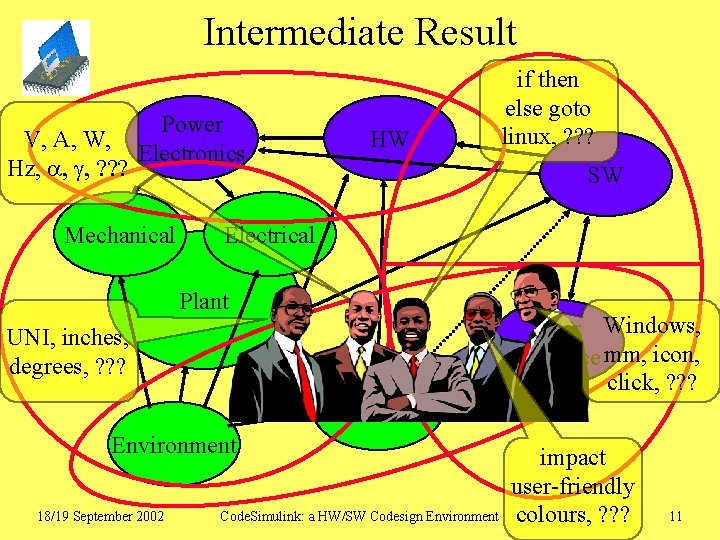

Intermediate Result Power V, A, W, Electronics Hz, a, g, ? ? ? Mechanical HW SW Electrical Plant UNI, inches, degrees, ? ? ? User Environment 18/19 September 2002 if then else goto linux, ? ? ? Code. Simulink: a HW/SW Codesign Environment User Windows, Interface mm, icon, click, ? ? ? impact user-friendly colours, ? ? ? 11

Someone will take decisions… 18/19 September 2002 Code. Simulink: a HW/SW Codesign Environment 12

… and someone will pay for the mistakes 18/19 September 2002 Code. Simulink: a HW/SW Codesign Environment 13

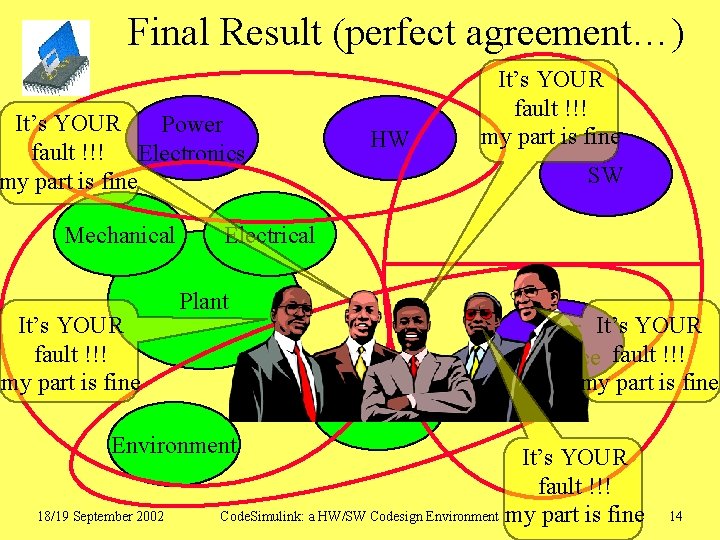

Final Result (perfect agreement…) It’s YOUR Power fault !!! Electronics my part is fine Mechanical It’s YOUR fault !!! my part is fine HW It’s YOUR fault !!! my part is fine SW Electrical Plant User It’s YOUR Interface fault !!! my part is fine Environment 18/19 September 2002 It’s YOUR fault !!! Code. Simulink: a HW/SW Codesign Environment my part is fine 14

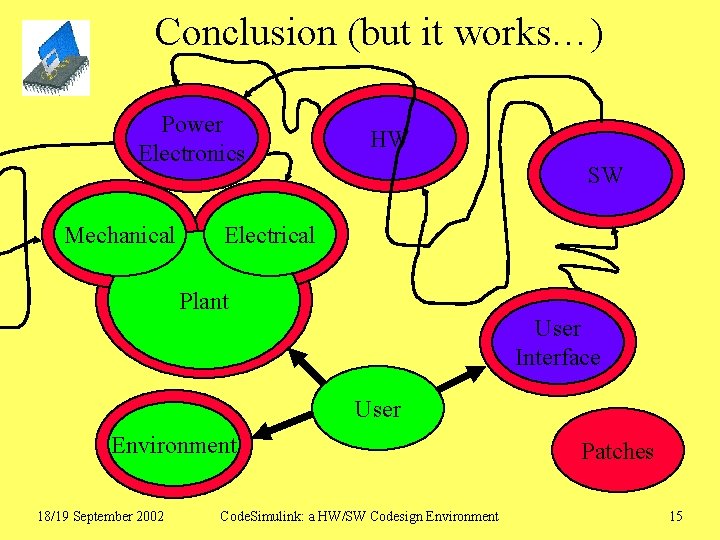

Conclusion (but it works…) Power Electronics Mechanical HW SW Electrical Plant User Interface User Environment 18/19 September 2002 Code. Simulink: a HW/SW Codesign Environment Patches 15

Part II HW vs. SW vs. Analog Integrated Design 18/19 September 2002 Code. Simulink: a HW/SW Codesign Environment 16

HW/SW Design Styles and Languages 18/19 September 2002 Code. Simulink: a HW/SW Codesign Environment 17

Techniques and Platforms 18/19 September 2002 Code. Simulink: a HW/SW Codesign Environment 18

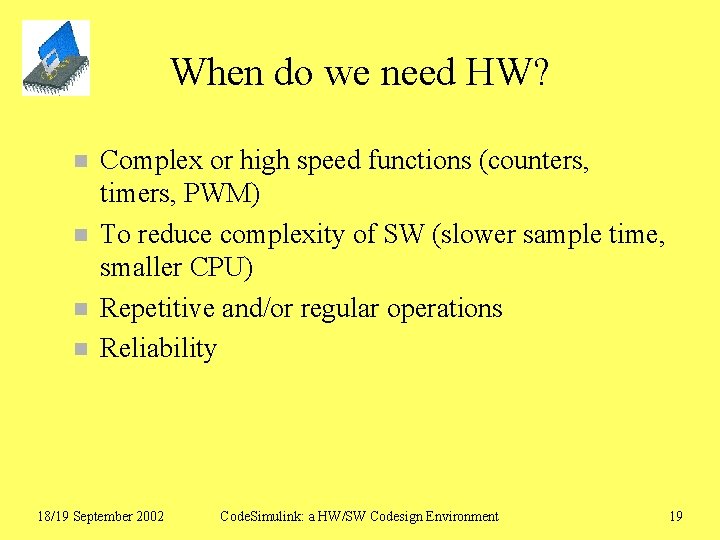

When do we need HW? n n Complex or high speed functions (counters, timers, PWM) To reduce complexity of SW (slower sample time, smaller CPU) Repetitive and/or regular operations Reliability 18/19 September 2002 Code. Simulink: a HW/SW Codesign Environment 19

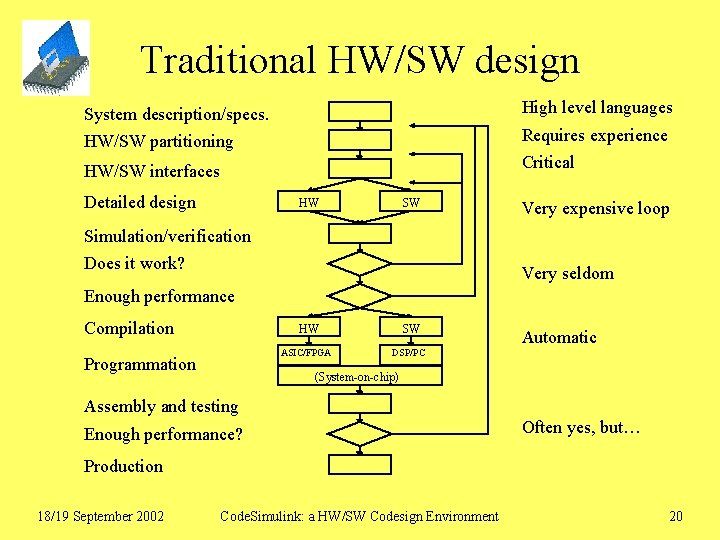

Traditional HW/SW design System description/specs. High level languages HW/SW partitioning Requires experience HW/SW interfaces Critical Detailed design HW SW Very expensive loop Simulation/verification Does it work? Very seldom Enough performance Compilation Programmation HW SW ASIC/FPGA DSP/PC Automatic (System-on-chip) Assembly and testing Enough performance? Often yes, but… Production 18/19 September 2002 Code. Simulink: a HW/SW Codesign Environment 20

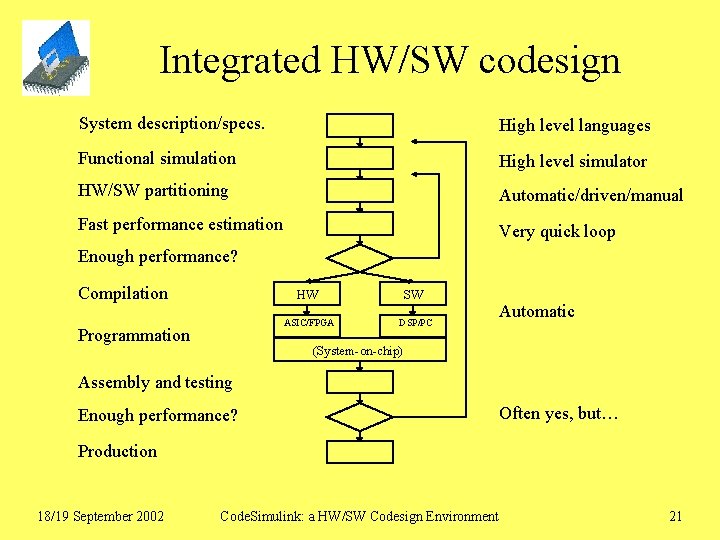

Integrated HW/SW codesign System description/specs. High level languages Functional simulation High level simulator HW/SW partitioning Automatic/driven/manual Fast performance estimation Very quick loop Enough performance? Compilation Programmation HW SW ASIC/FPGA DSP/PC Automatic (System-on-chip) Assembly and testing Enough performance? Often yes, but… Production 18/19 September 2002 Code. Simulink: a HW/SW Codesign Environment 21

Part III Code. Simulink environment for HW/SW/mixed-mode codesign and cosimulation 18/19 September 2002 Code. Simulink: a HW/SW Codesign Environment 22

Existing Codesign tools 18/19 September 2002 Code. Simulink: a HW/SW Codesign Environment 23

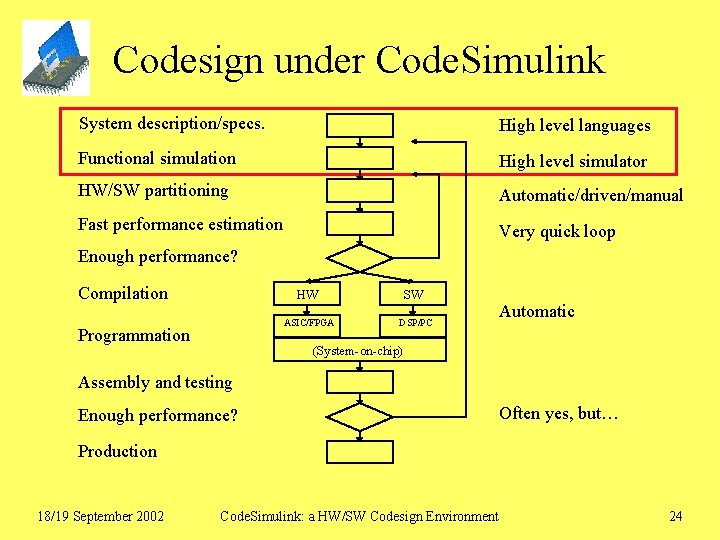

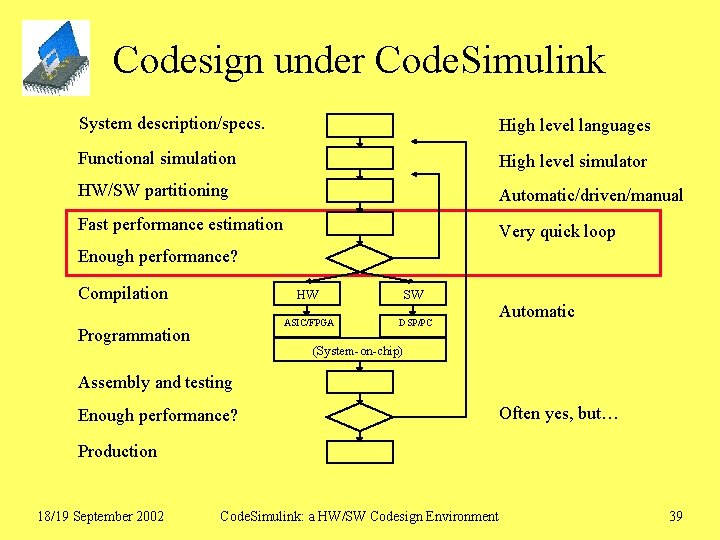

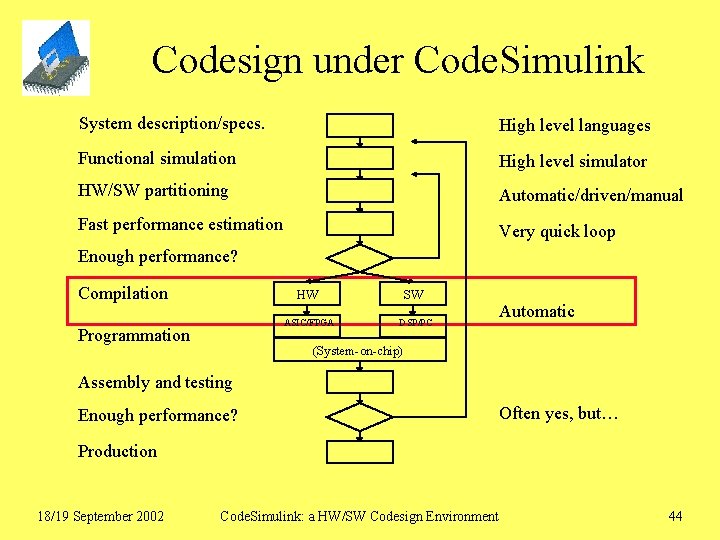

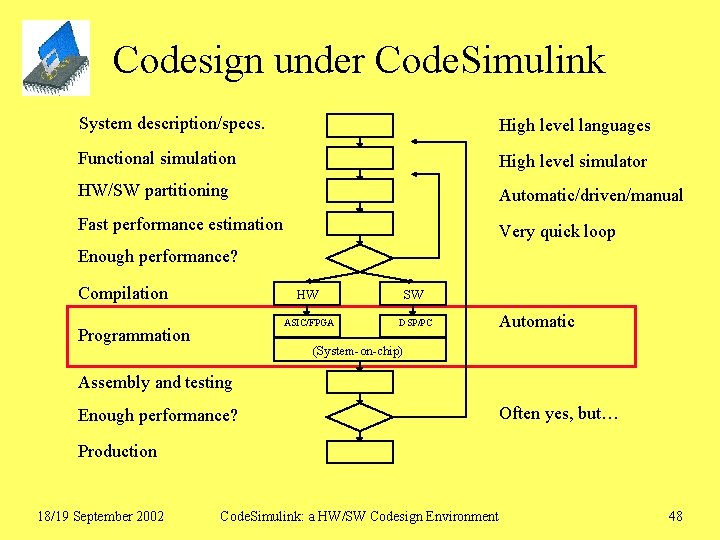

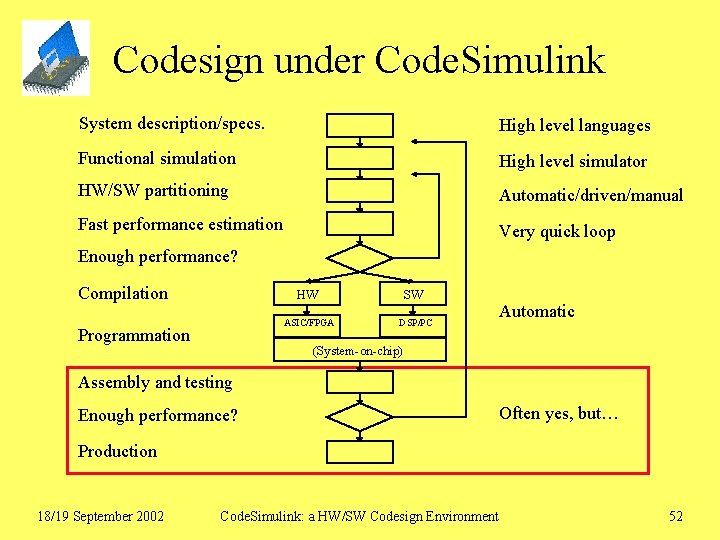

Codesign under Code. Simulink System description/specs. High level languages Functional simulation High level simulator HW/SW partitioning Automatic/driven/manual Fast performance estimation Very quick loop Enough performance? Compilation Programmation HW SW ASIC/FPGA DSP/PC Automatic (System-on-chip) Assembly and testing Enough performance? Often yes, but… Production 18/19 September 2002 Code. Simulink: a HW/SW Codesign Environment 24

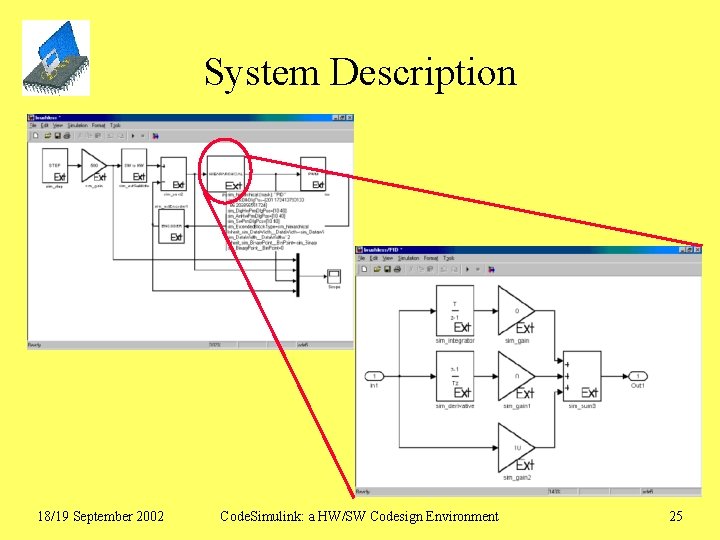

System Description 18/19 September 2002 Code. Simulink: a HW/SW Codesign Environment 25

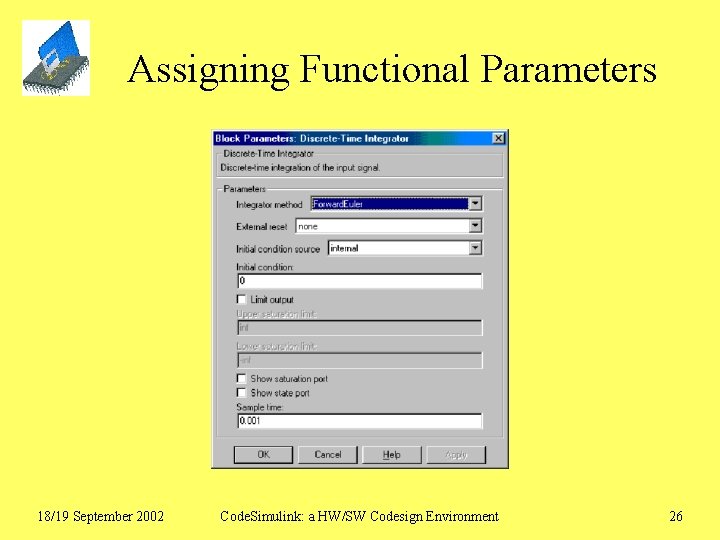

Assigning Functional Parameters 18/19 September 2002 Code. Simulink: a HW/SW Codesign Environment 26

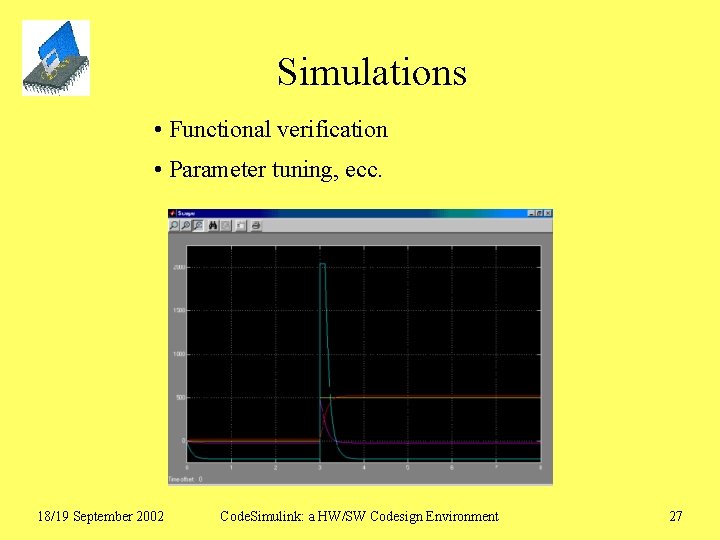

Simulations • Functional verification • Parameter tuning, ecc. 18/19 September 2002 Code. Simulink: a HW/SW Codesign Environment 27

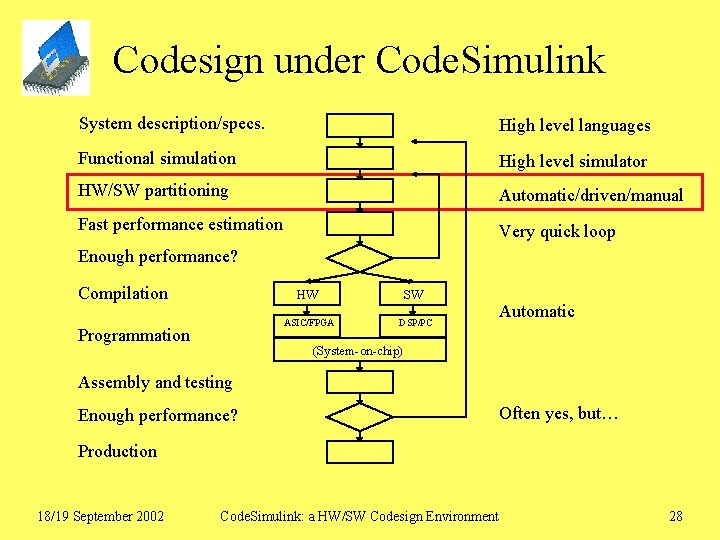

Codesign under Code. Simulink System description/specs. High level languages Functional simulation High level simulator HW/SW partitioning Automatic/driven/manual Fast performance estimation Very quick loop Enough performance? Compilation Programmation HW SW ASIC/FPGA DSP/PC Automatic (System-on-chip) Assembly and testing Enough performance? Often yes, but… Production 18/19 September 2002 Code. Simulink: a HW/SW Codesign Environment 28

Implementations n n Digital HW; different architectures: – Synchronous parallel (base architecture) – bit-serial (smaller, slower) – systolic (faster) – interfaces among architecture Analog HW; different architectures (under developm. ): – Voltage/current single-ended/differential – Frequency/pulse. Width modulation SW: different CPU’s External/Simulink: to simulate “external” world (plant, actuators, sensors, environment, etc. ) 18/19 September 2002 Code. Simulink: a HW/SW Codesign Environment 29

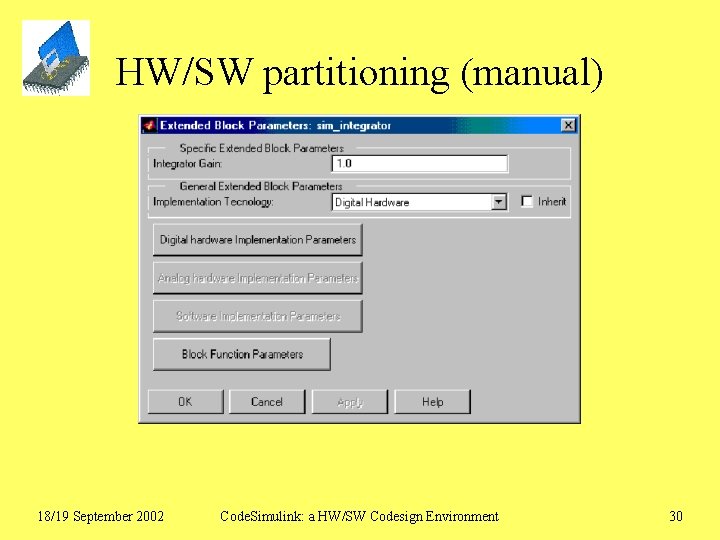

HW/SW partitioning (manual) 18/19 September 2002 Code. Simulink: a HW/SW Codesign Environment 30

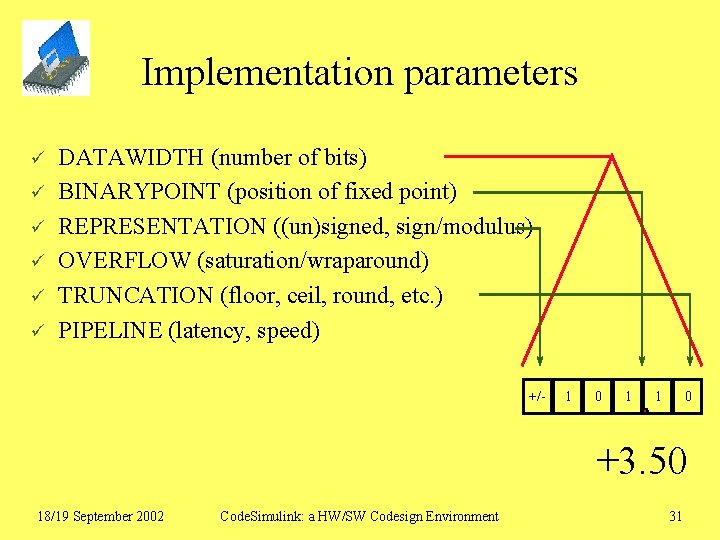

Implementation parameters ü ü ü DATAWIDTH (number of bits) BINARYPOINT (position of fixed point) REPRESENTATION ((un)signed, sign/modulus) OVERFLOW (saturation/wraparound) TRUNCATION (floor, ceil, round, etc. ) PIPELINE (latency, speed) +/- 1 0 1 1 0 +3. 50 18/19 September 2002 Code. Simulink: a HW/SW Codesign Environment 31

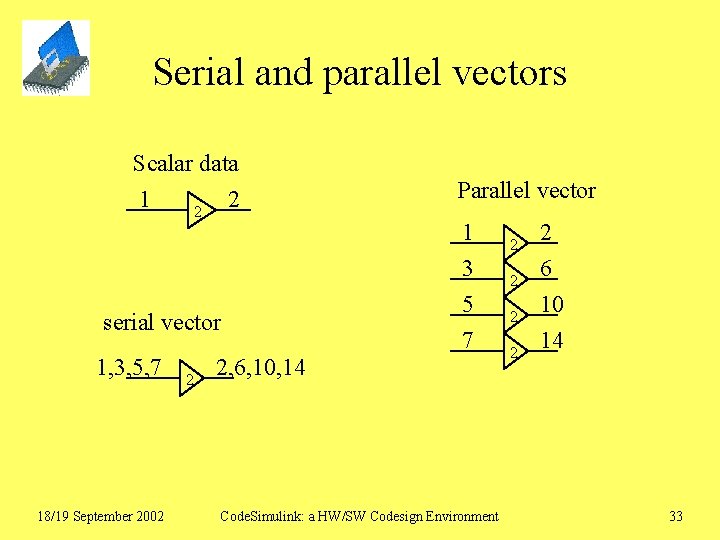

Different Data Types n n n Scalars (one data per sample) Vectors (a vector of data per sample; mux/demux): – serial (data sequentially on a single channel) – parallel (data in parallel on different channels) Matrices (a matrix of data per sample; for instance images in TV or vision): – serial – parallel/serial – serial/parallel 18/19 September 2002 Code. Simulink: a HW/SW Codesign Environment 32

Serial and parallel vectors Scalar data 1 2 2 serial vector 1, 3, 5, 7 18/19 September 2002 2 Parallel vector 1 3 5 7 2, 6, 10, 14 Code. Simulink: a HW/SW Codesign Environment 2 2 2 6 10 14 33

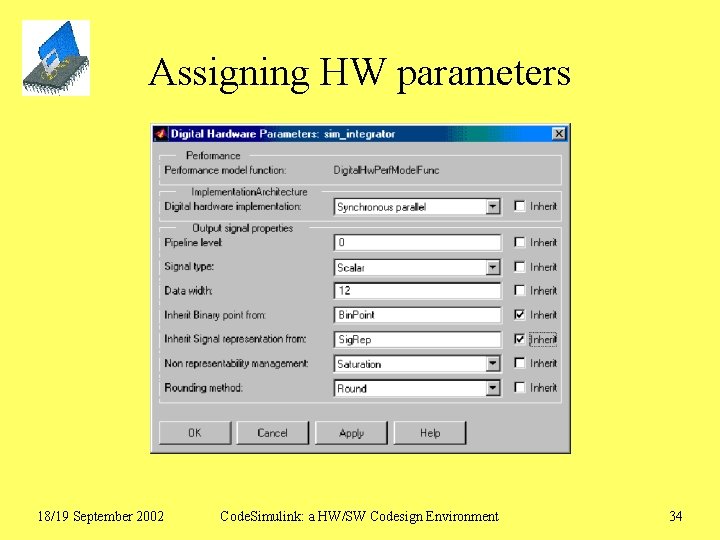

Assigning HW parameters 18/19 September 2002 Code. Simulink: a HW/SW Codesign Environment 34

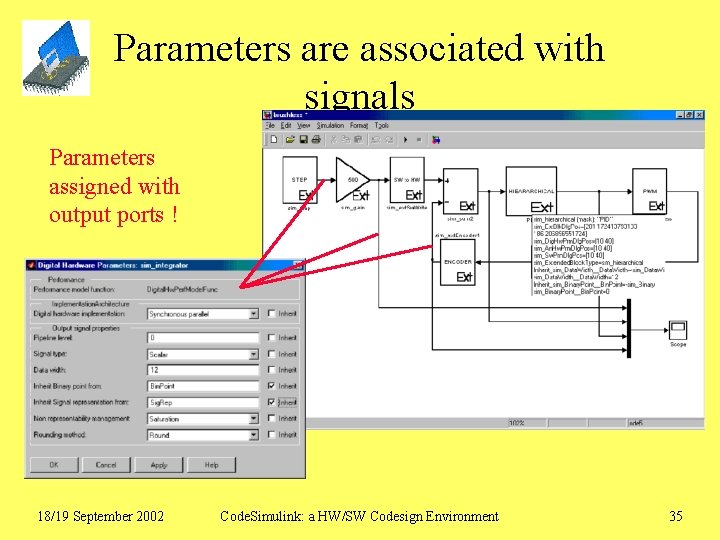

Parameters are associated with signals Parameters assigned with output ports ! 18/19 September 2002 Code. Simulink: a HW/SW Codesign Environment 35

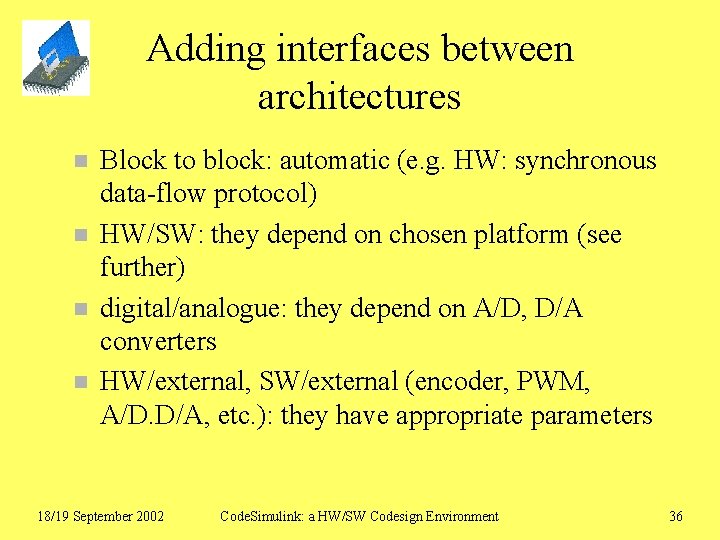

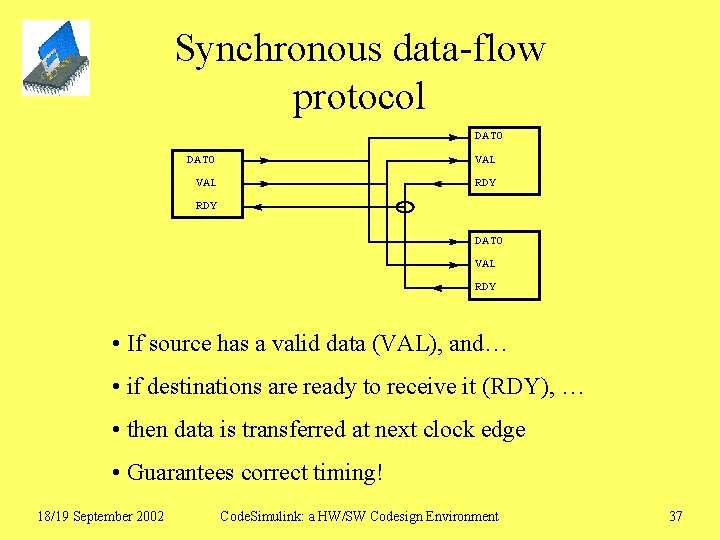

Adding interfaces between architectures n n Block to block: automatic (e. g. HW: synchronous data-flow protocol) HW/SW: they depend on chosen platform (see further) digital/analogue: they depend on A/D, D/A converters HW/external, SW/external (encoder, PWM, A/D. D/A, etc. ): they have appropriate parameters 18/19 September 2002 Code. Simulink: a HW/SW Codesign Environment 36

Synchronous data-flow protocol DATO VAL RDY • If source has a valid data (VAL), and… • if destinations are ready to receive it (RDY), … • then data is transferred at next clock edge • Guarantees correct timing! 18/19 September 2002 Code. Simulink: a HW/SW Codesign Environment 37

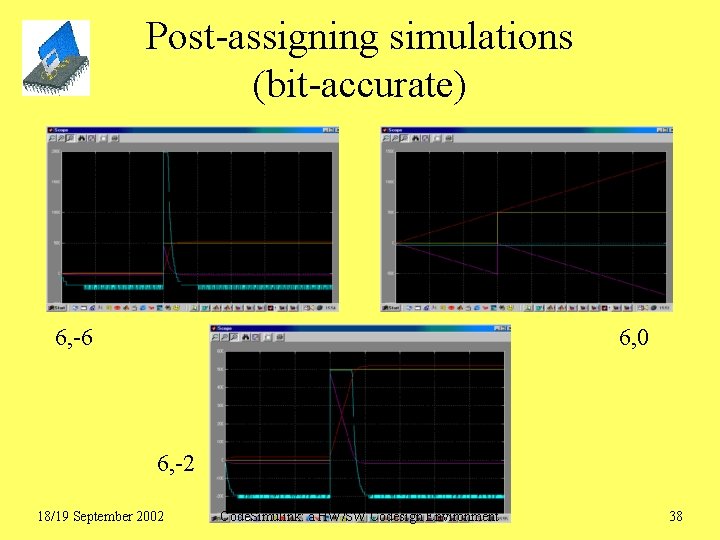

Post-assigning simulations (bit-accurate) 6, -6 6, 0 6, -2 18/19 September 2002 Code. Simulink: a HW/SW Codesign Environment 38

Codesign under Code. Simulink System description/specs. High level languages Functional simulation High level simulator HW/SW partitioning Automatic/driven/manual Fast performance estimation Very quick loop Enough performance? Compilation Programmation HW SW ASIC/FPGA DSP/PC Automatic (System-on-chip) Assembly and testing Enough performance? Often yes, but… Production 18/19 September 2002 Code. Simulink: a HW/SW Codesign Environment 39

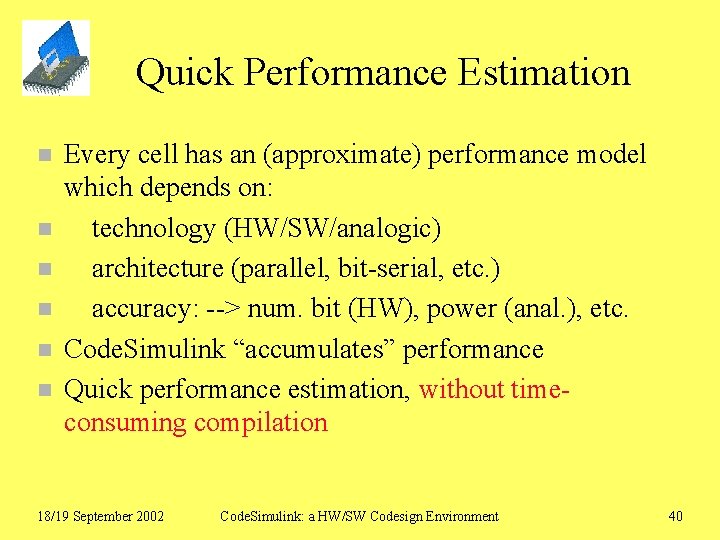

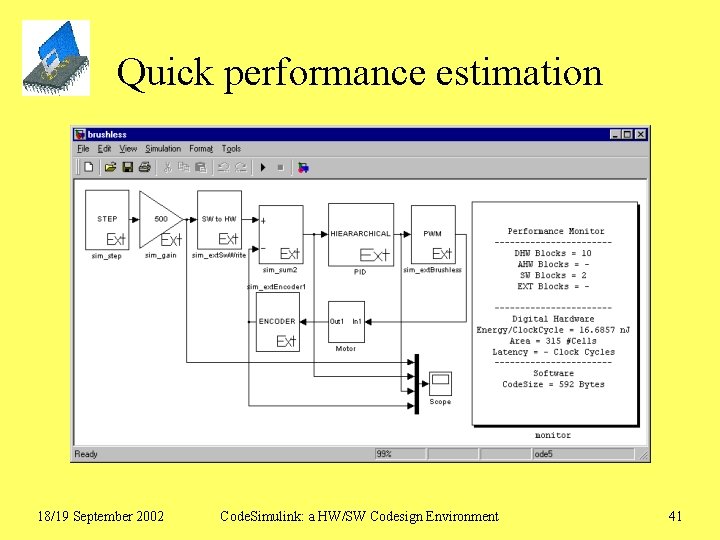

Quick Performance Estimation n n n Every cell has an (approximate) performance model which depends on: technology (HW/SW/analogic) architecture (parallel, bit-serial, etc. ) accuracy: --> num. bit (HW), power (anal. ), etc. Code. Simulink “accumulates” performance Quick performance estimation, without timeconsuming compilation 18/19 September 2002 Code. Simulink: a HW/SW Codesign Environment 40

Quick performance estimation 18/19 September 2002 Code. Simulink: a HW/SW Codesign Environment 41

Quick performance estimation 18/19 September 2002 Code. Simulink: a HW/SW Codesign Environment 42

Performances n n n n Number of cells (FPGA) or area (ASIC) Power dissipation (battery duration. . . ) Latency (computing delay) Max. clock Frequency (not yet…) Max sample frequency Code and data size (RAM size) Accuracy (S/N, bit number), from simulations 18/19 September 2002 Code. Simulink: a HW/SW Codesign Environment 43

Codesign under Code. Simulink System description/specs. High level languages Functional simulation High level simulator HW/SW partitioning Automatic/driven/manual Fast performance estimation Very quick loop Enough performance? Compilation Programmation HW SW ASIC/FPGA DSP/PC Automatic (System-on-chip) Assembly and testing Enough performance? Often yes, but… Production 18/19 September 2002 Code. Simulink: a HW/SW Codesign Environment 44

Code. Simulink compilation n n n Separation of multiple platforms Hierarchy removal (flattening) Separation of SW, digital HW, analog HW blocks Adding interfaces Translation: Code. Simulink (SW) --> C (RTW) Translation: Code. Simulink (digital) --> VHDL Translation: Code. Simulink (analogic) --> EDIF 18/19 September 2002 Code. Simulink: a HW/SW Codesign Environment 45

HW/SW Compilation n n Possibility to edit VHDL/C/EDIF code Compilation: VHDL --> ASIC, FPGA (Altera, Xilinx, others) (Leonardo - Mentor Graphics + proprietary tool) Compilation: C --> executable (ANSI C compiler) Post-compilation performance evaluation 18/19 September 2002 Code. Simulink: a HW/SW Codesign Environment 46

Every cell is made of. . . n n n Simulink symbol Fast functional model for simulations (template) Performance estimation model (SW, HW, …) (template) VHDL, EDIF, C description (template) Parameter editing mask (template) Documentation (template) 18/19 September 2002 Code. Simulink: a HW/SW Codesign Environment 47

Codesign under Code. Simulink System description/specs. High level languages Functional simulation High level simulator HW/SW partitioning Automatic/driven/manual Fast performance estimation Very quick loop Enough performance? Compilation Programmation HW SW ASIC/FPGA DSP/PC Automatic (System-on-chip) Assembly and testing Enough performance? Often yes, but… Production 18/19 September 2002 Code. Simulink: a HW/SW Codesign Environment 48

Platforms n n n SW-only (CPU, microprocessors, PC’s, etc. ) HW-only (ALTERA, XILINX, ASIC, etc. ) HW/SW: – board (CPU+FPGA) – Systems-on-chip (ASIC: core+gates) – Programmable systems-on-chip 18/19 September 2002 Code. Simulink: a HW/SW Codesign Environment 49

A few commercial platforms n n n n SIDSA: HDST 100 board (ARM 7 TDMI + Altera 10 k 100) SIDSA: HDST 200 board (ARM 7 TDMI + Altera 10 k 100) SIDSA: FIPSOC chip (80 C 51 + FPGA) SUNDANCE: HDT 355 board (TMS 320 C 30 + Altera 10 k 100) SUNDANCE: HDT 367 board (ARM + Xilinx Virtex) TRISCEND: chip (80 C 51 + FPGA) TRISCEND: chip (ARM 7 TDMI + FPGA) ALTERA: Excalibur chip (ARM 7 TDMI + FPGA) 18/19 September 2002 Code. Simulink: a HW/SW Codesign Environment 50

Code. Simulink Libraries n n n Basic “Simulink” (+, *, integr. deriv. mux, demux, in, out, filters, f(x), 1/z, sources, scopes, etc. ) Toolboxes (image processing, neuro-fuzzy, flowchart) Application-dependent (under request) 18/19 September 2002 Code. Simulink: a HW/SW Codesign Environment 51

Codesign under Code. Simulink System description/specs. High level languages Functional simulation High level simulator HW/SW partitioning Automatic/driven/manual Fast performance estimation Very quick loop Enough performance? Compilation Programmation HW SW ASIC/FPGA DSP/PC Automatic (System-on-chip) Assembly and testing Enough performance? Often yes, but… Production 18/19 September 2002 Code. Simulink: a HW/SW Codesign Environment 52

Advantages (Code)Simulink 18/19 September 2002 Code. Simulink: a HW/SW Codesign Environment 53

Applications n n n Control, image processing, neuro-fuzzy networks Design of consumer electronic circuits Design of high performance circuits Not suited to design microprocessors Speeding-up Simulink simulations, running on HW (limited resolution) 18/19 September 2002 Code. Simulink: a HW/SW Codesign Environment 54

Project Status (obsolete) n n n Compiler is complete Synchronous parallel library is complete Other libraries are under development New technologies/platforms to be characterized (semi-automatic procedure) We are looking forward to cooperate (e. g. joint development of applications) 18/19 September 2002 Code. Simulink: a HW/SW Codesign Environment 55

Other Simulink-based tools n n There are other commercial HW design tools based on Simulink: – DSP Builder from Altera – System Generator from Xilinx These are mostly HW-only design tools (using Simulink as an HDL language) 18/19 September 2002 Code. Simulink: a HW/SW Codesign Environment 56

Advantages of Code. Simulink n n n Handles both digital and SW and analog and RF and mixed-signal So. C’s Automatically takes care of data exchange and timing (HW/HW, HW/SW, digital/analog) Accurate high-level functional models of digital, analog, RF and mixed-signal interactions High-level performance modeling (power, speed, area, code size, etc. ) Supports FPGA and ASIC and programmable So. C 18/19 September 2002 Code. Simulink: a HW/SW Codesign Environment 57

Advantages of Code. Simulink n n n Natively handles scalars, vectors, matrices Supports multi-platforms, multi-cores (multi-SW, multi-HW, hybrid) Supports Visual Basic / Windows GUI’s (simulations and compilation) Supports bit-parallel, bit-serial, systolic data paths and bundled-data asynchronous design (under developm. ) Interfaces to low-level simulators (Model. Sim, Max. Plus, Quartus, Xilinx, Spice-like) 18/19 September 2002 Code. Simulink: a HW/SW Codesign Environment 58

Limitations of (Code)Simulink n n Data-dominated systems Mostly fixed time sampling strategy (multirate) Library-based (sub-optimal) Models require technology characterization 18/19 September 2002 Code. Simulink: a HW/SW Codesign Environment 59

Commercialization of Code. Simulink n n Free for universities for academic purposes Sundance ltd. is going to commercialize this product at end of May 2003 18/19 September 2002 Code. Simulink: a HW/SW Codesign Environment 60

Part IV Application of Code. Simulink to the design of a Common Rail Test bench 18/19 September 2002 Code. Simulink: a HW/SW Codesign Environment 61

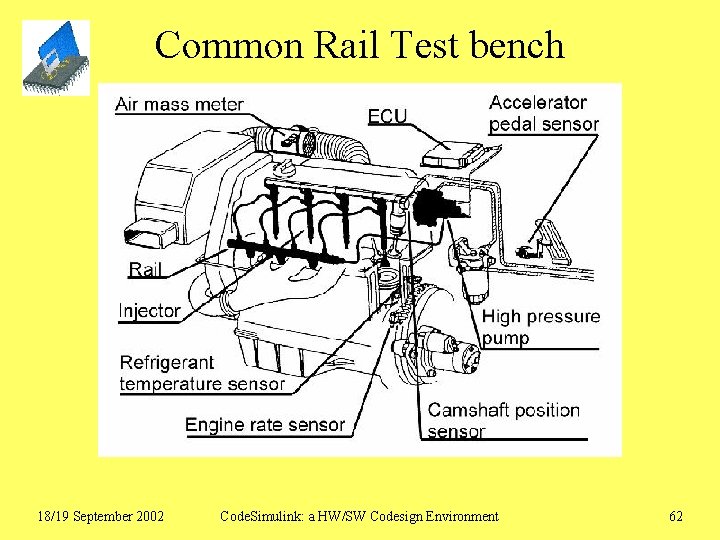

Common Rail Test bench 18/19 September 2002 Code. Simulink: a HW/SW Codesign Environment 62

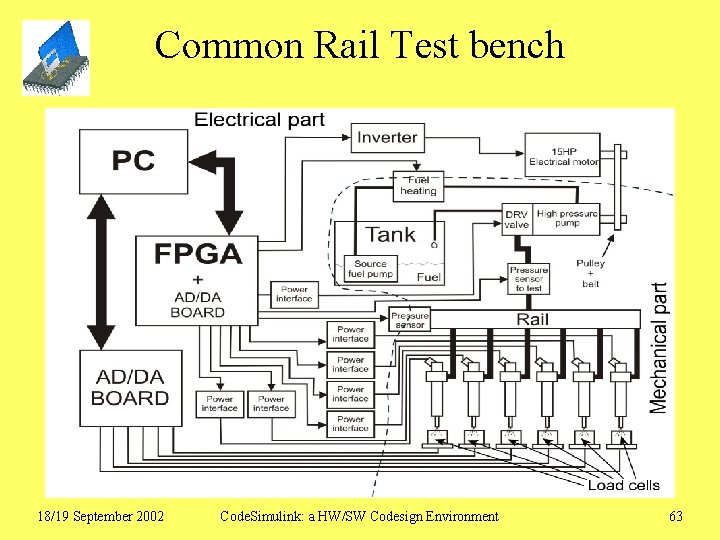

Common Rail Test bench 18/19 September 2002 Code. Simulink: a HW/SW Codesign Environment 63

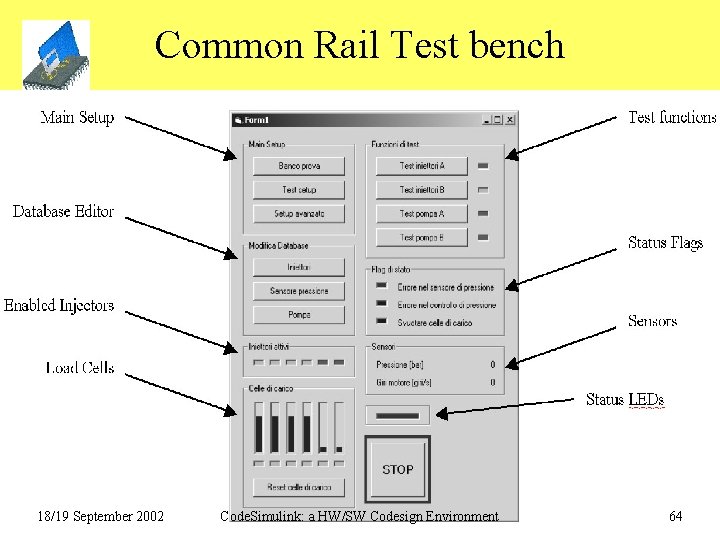

Common Rail Test bench 18/19 September 2002 Code. Simulink: a HW/SW Codesign Environment 64

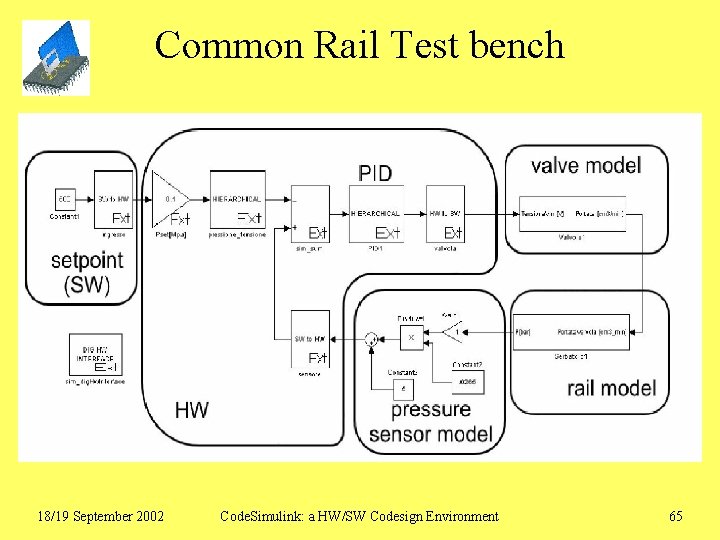

Common Rail Test bench 18/19 September 2002 Code. Simulink: a HW/SW Codesign Environment 65

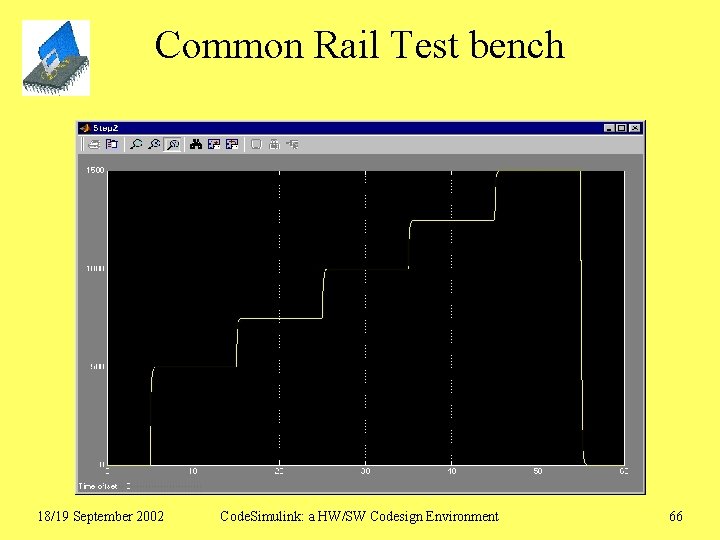

Common Rail Test bench 18/19 September 2002 Code. Simulink: a HW/SW Codesign Environment 66

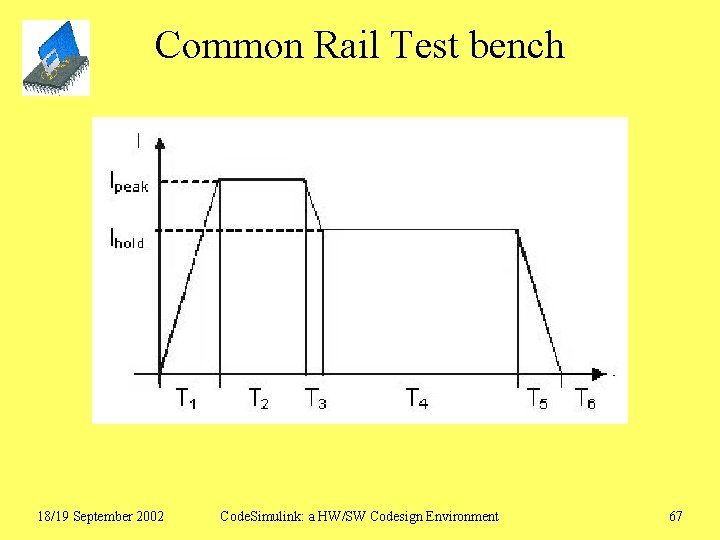

Common Rail Test bench 18/19 September 2002 Code. Simulink: a HW/SW Codesign Environment 67

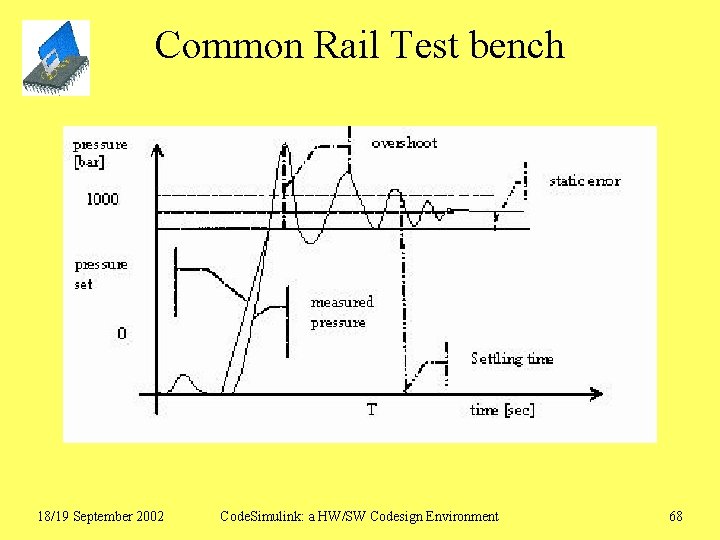

Common Rail Test bench 18/19 September 2002 Code. Simulink: a HW/SW Codesign Environment 68

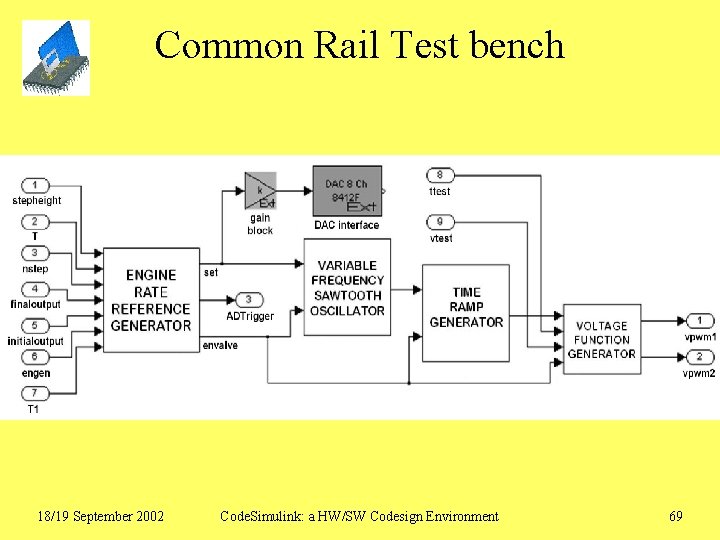

Common Rail Test bench 18/19 September 2002 Code. Simulink: a HW/SW Codesign Environment 69

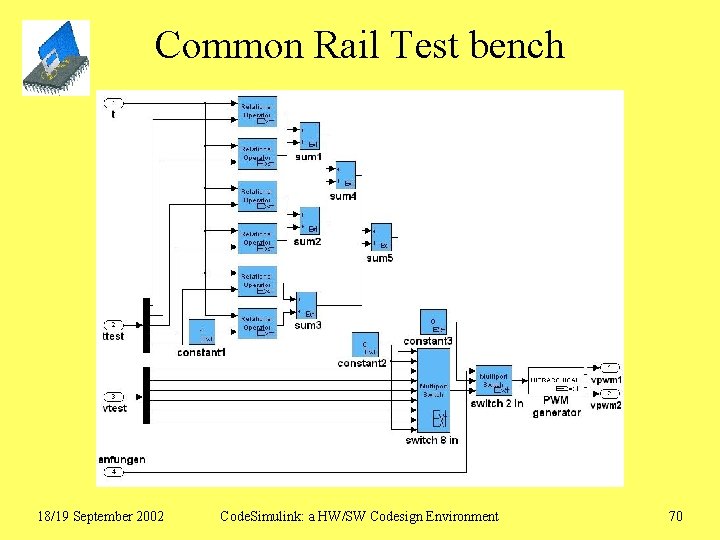

Common Rail Test bench 18/19 September 2002 Code. Simulink: a HW/SW Codesign Environment 70

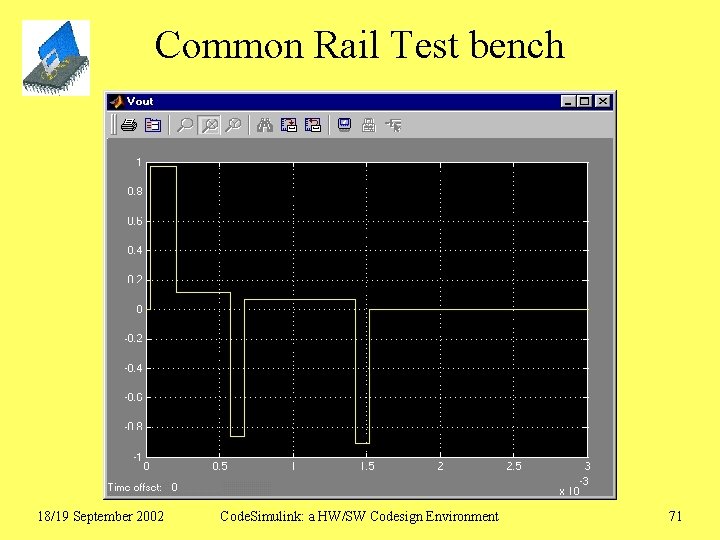

Common Rail Test bench 18/19 September 2002 Code. Simulink: a HW/SW Codesign Environment 71

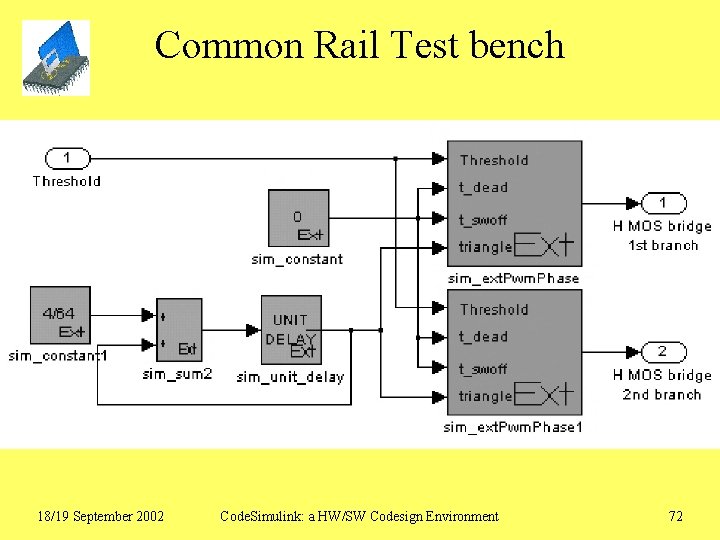

Common Rail Test bench 18/19 September 2002 Code. Simulink: a HW/SW Codesign Environment 72

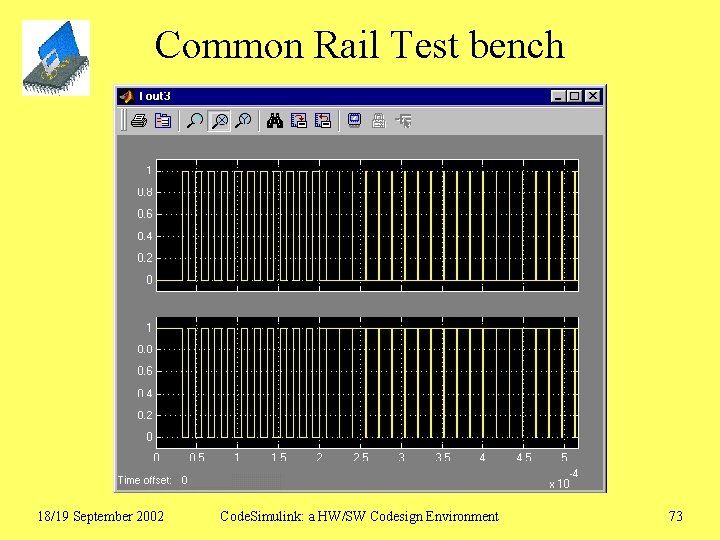

Common Rail Test bench 18/19 September 2002 Code. Simulink: a HW/SW Codesign Environment 73

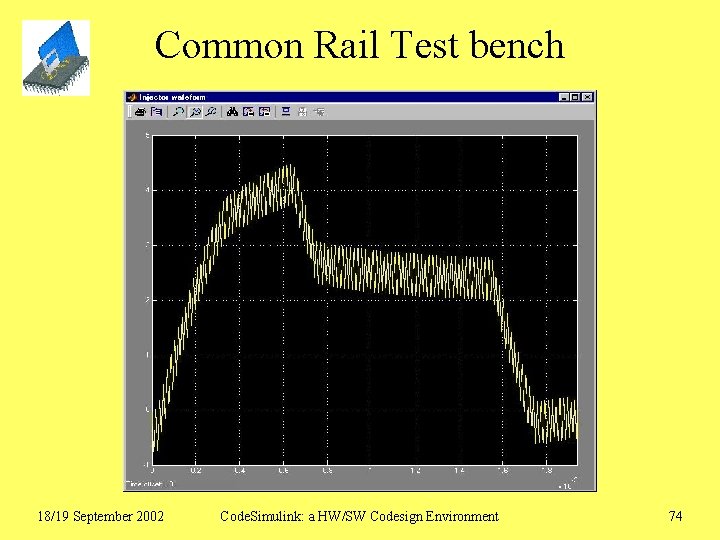

Common Rail Test bench 18/19 September 2002 Code. Simulink: a HW/SW Codesign Environment 74

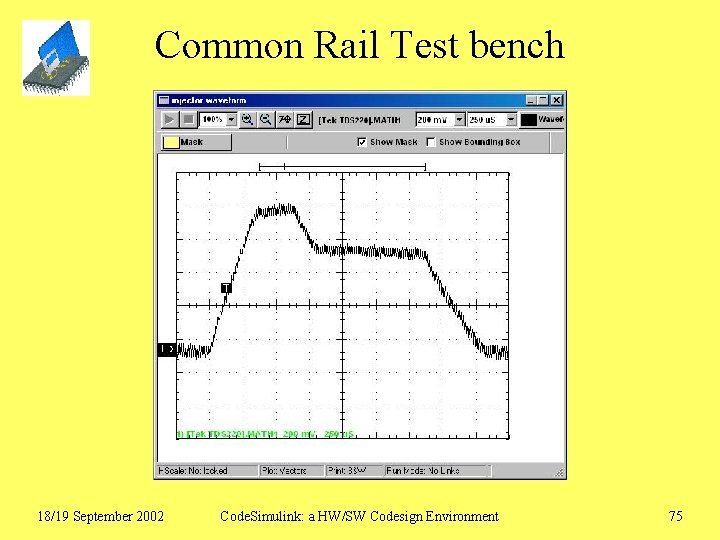

Common Rail Test bench 18/19 September 2002 Code. Simulink: a HW/SW Codesign Environment 75

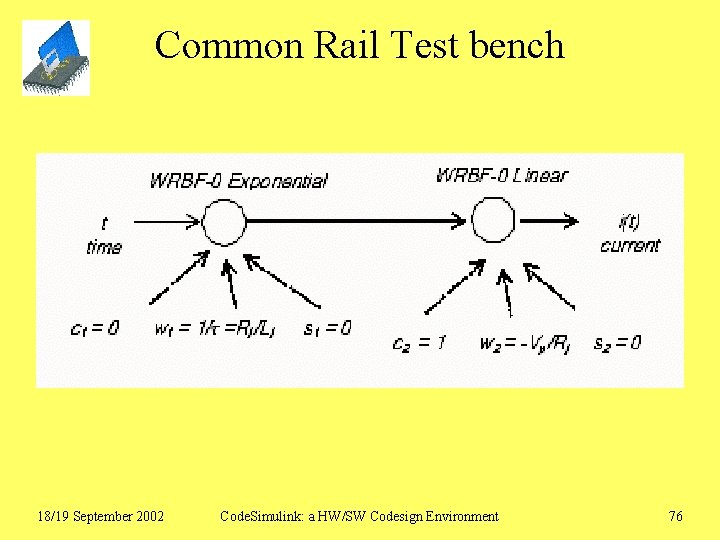

Common Rail Test bench 18/19 September 2002 Code. Simulink: a HW/SW Codesign Environment 76

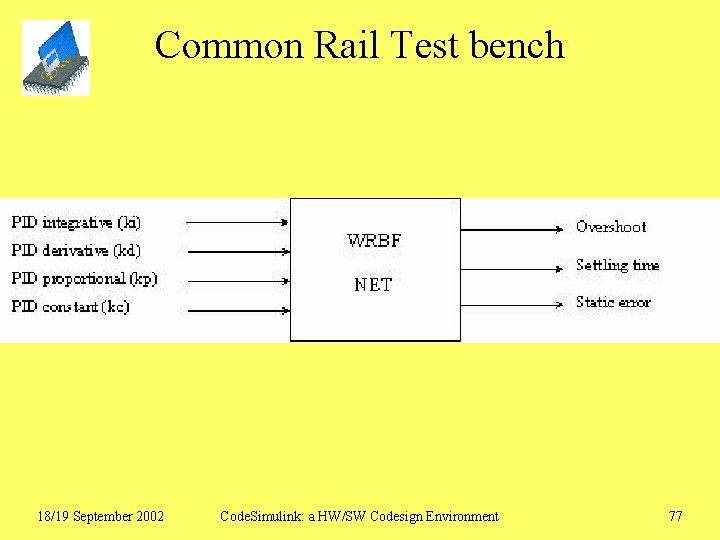

Common Rail Test bench 18/19 September 2002 Code. Simulink: a HW/SW Codesign Environment 77

Part V Code. Simulink HW/SW Codesign tool Internal operation 18/19 September 2002 Code. Simulink: a HW/SW Codesign Environment 78

Index HW/SW Compilation (L. Mari) u Quick Performance Estimation (A. Serra) u HW Performance Models (A. Cerrato) u SW Performance Models (M. Lazarescu) u Numeric optimization (G. Belforte) u HW/SW Platforms (M. Chiaberge) u 18/19 September 2002 Code. Simulink: a HW/SW Codesign Environment 79

- Slides: 79