Virtual Memory Virtual Memory Topics Why virtual memory

- Slides: 17

Virtual Memory

Virtual Memory: Topics Why virtual memory? n Virtual to physical address translation n Page Table n Translation Lookaside Buffer (TLB) n

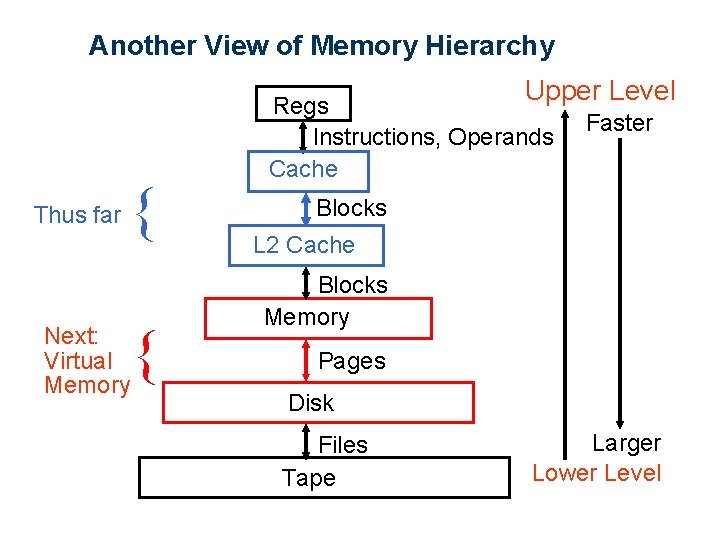

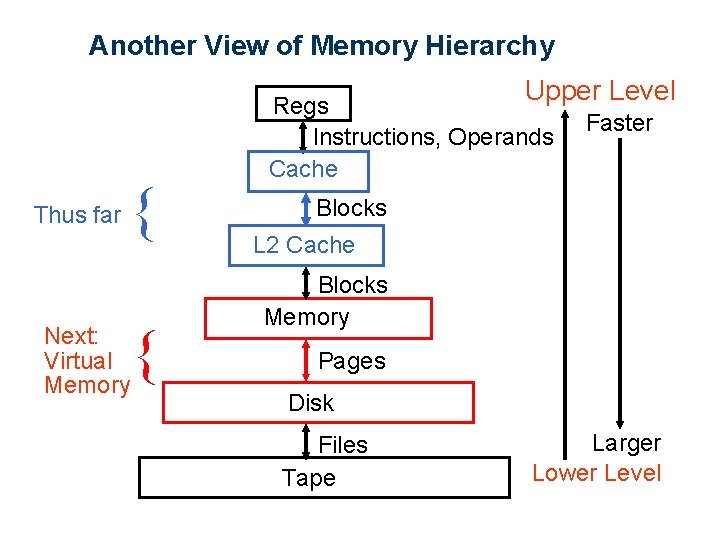

Another View of Memory Hierarchy Upper Level Thus far { Next: Virtual Memory { Regs Instructions, Operands Cache Faster Blocks L 2 Cache Blocks Memory Pages Disk Files Tape Larger Lower Level

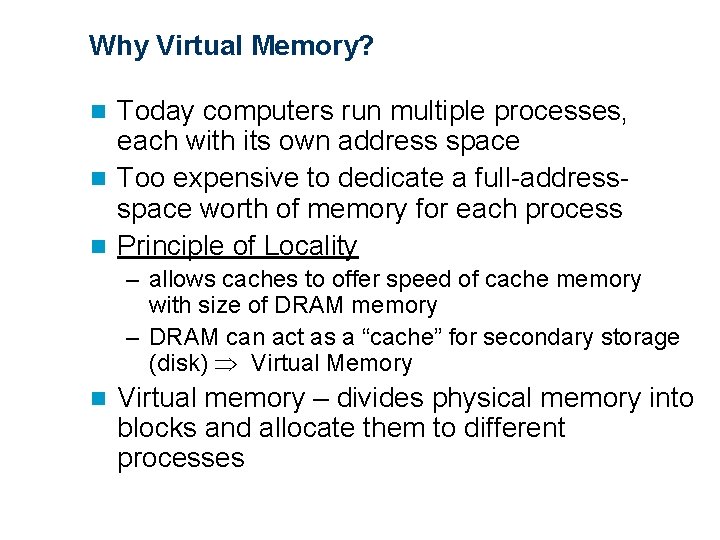

Why Virtual Memory? Today computers run multiple processes, each with its own address space n Too expensive to dedicate a full-addressspace worth of memory for each process n Principle of Locality n – allows caches to offer speed of cache memory with size of DRAM memory – DRAM can act as a “cache” for secondary storage (disk) Virtual Memory n Virtual memory – divides physical memory into blocks and allocate them to different processes

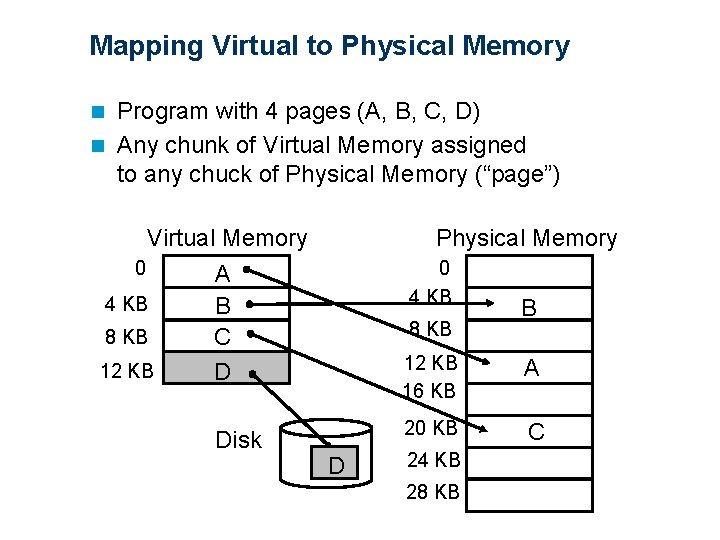

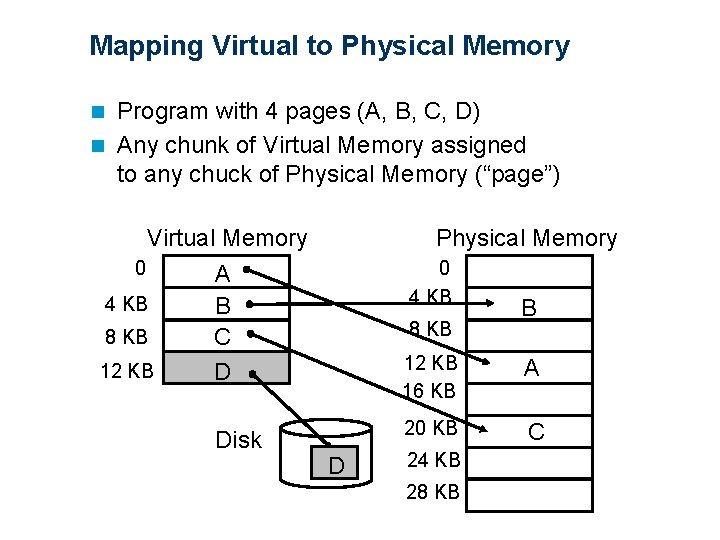

Mapping Virtual to Physical Memory Program with 4 pages (A, B, C, D) n Any chunk of Virtual Memory assigned to any chuck of Physical Memory (“page”) n Virtual Memory 0 4 KB 8 KB 12 KB Physical Memory 0 4 KB A B C D Disk 8 KB D B 12 KB 16 KB A 20 KB C 24 KB 28 KB

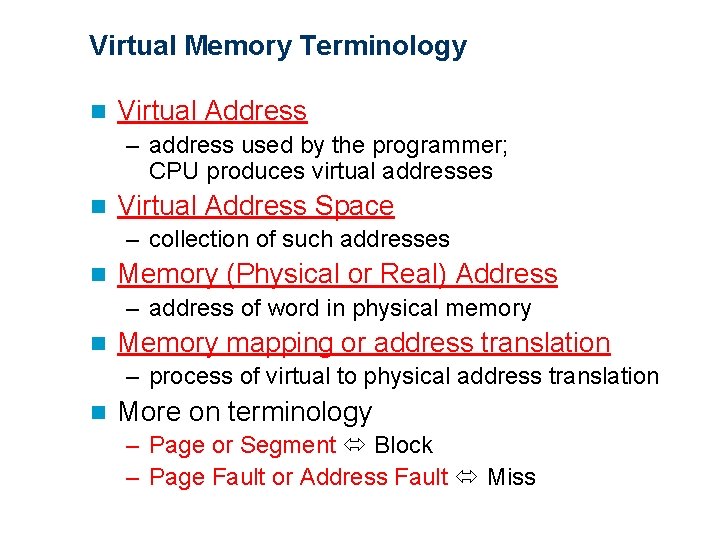

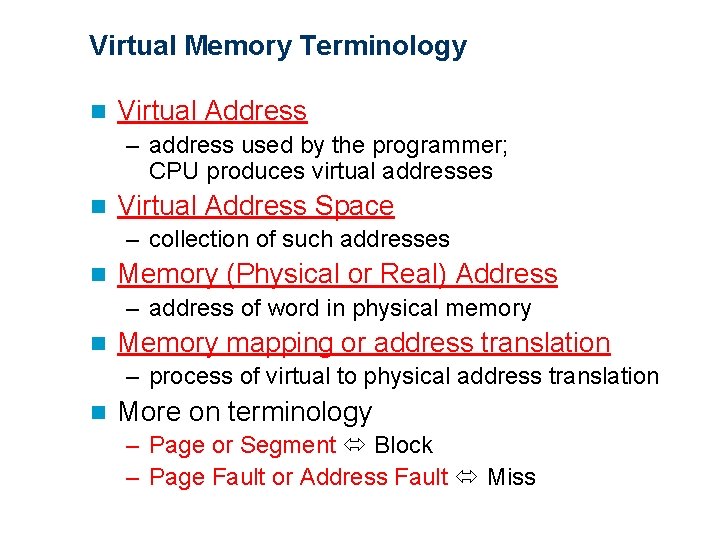

Virtual Memory Terminology n Virtual Address – address used by the programmer; CPU produces virtual addresses n Virtual Address Space – collection of such addresses n Memory (Physical or Real) Address – address of word in physical memory n Memory mapping or address translation – process of virtual to physical address translation n More on terminology – Page or Segment Block – Page Fault or Address Fault Miss

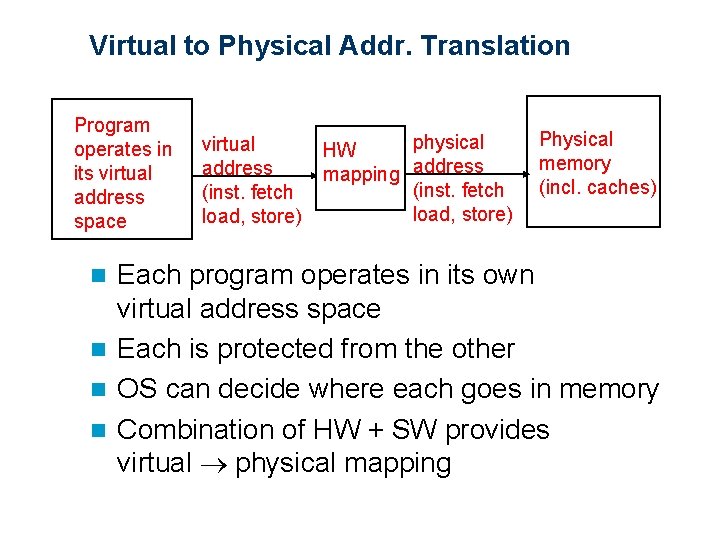

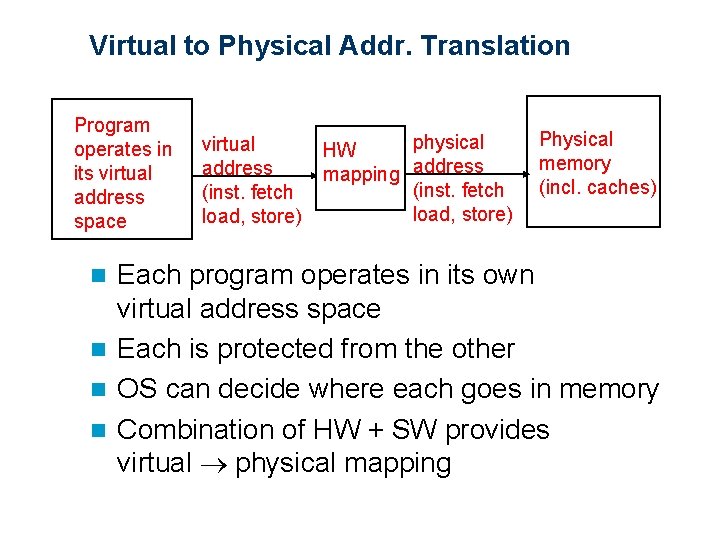

Virtual to Physical Addr. Translation Program operates in its virtual address space virtual address (inst. fetch load, store) physical HW mapping address (inst. fetch load, store) Physical memory (incl. caches) Each program operates in its own virtual address space n Each is protected from the other n OS can decide where each goes in memory n Combination of HW + SW provides virtual physical mapping n

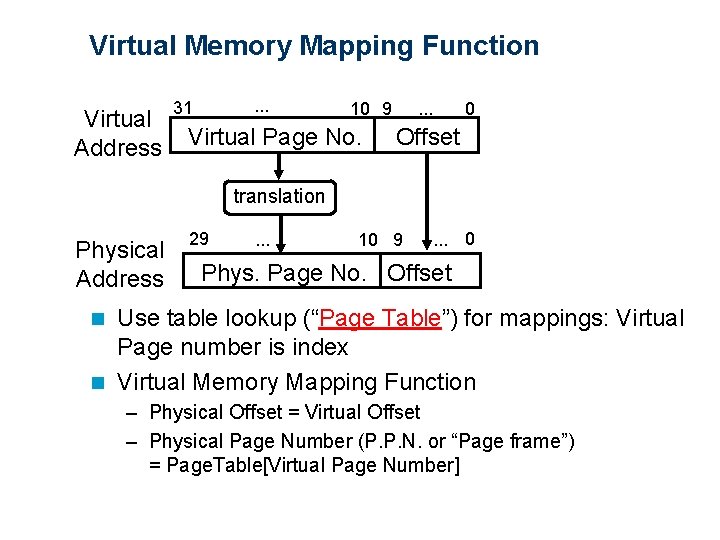

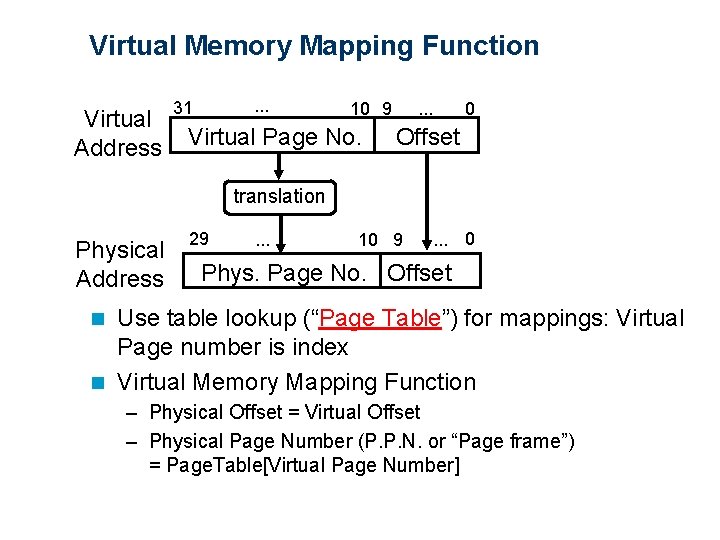

Virtual Memory Mapping Function Virtual Address . . . 31 10 9 Virtual Page No. 0 . . . Offset translation Physical Address 29 . . . 10 9 . . . 0 Phys. Page No. Offset Use table lookup (“Page Table”) for mappings: Virtual Page number is index n Virtual Memory Mapping Function n – Physical Offset = Virtual Offset – Physical Page Number (P. P. N. or “Page frame”) = Page. Table[Virtual Page Number]

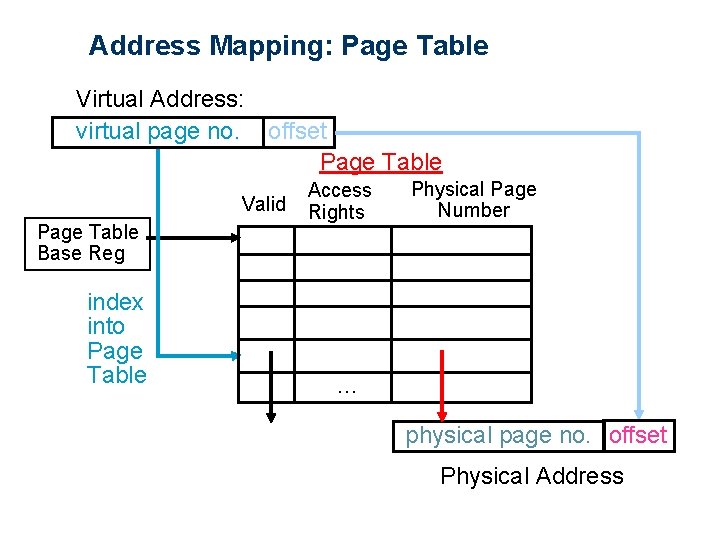

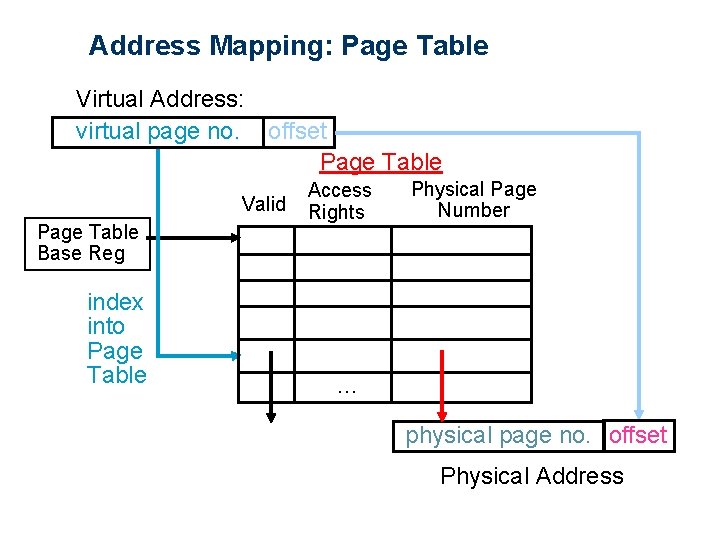

Address Mapping: Page Table Virtual Address: virtual page no. offset Page Table Valid Page Table Base Reg index into Page Table Access Rights Physical Page Number . . . physical page no. offset Physical Address

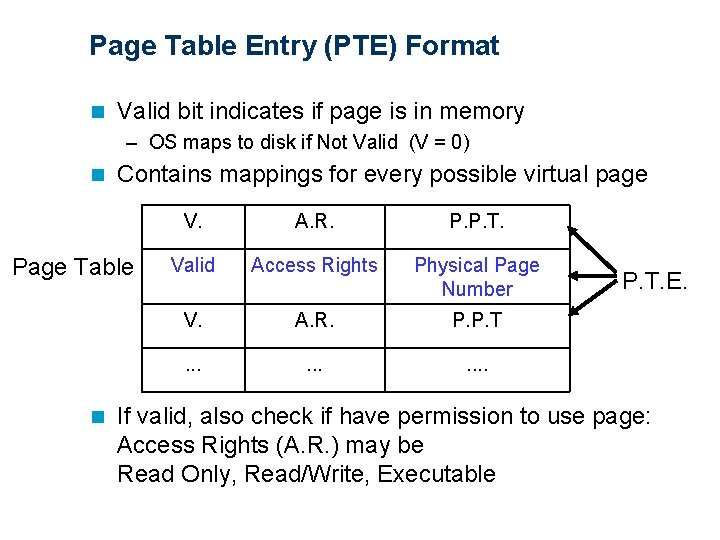

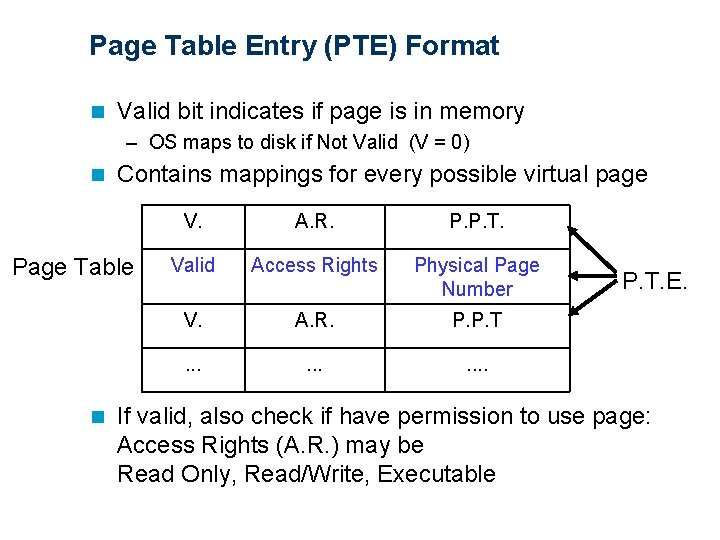

Page Table Entry (PTE) Format n Valid bit indicates if page is in memory – OS maps to disk if Not Valid (V = 0) n Contains mappings for every possible virtual page Page Table n V. A. R. P. P. T. Valid Access Rights Physical Page Number V. A. R. P. P. T . . P. T. E. If valid, also check if have permission to use page: Access Rights (A. R. ) may be Read Only, Read/Write, Executable

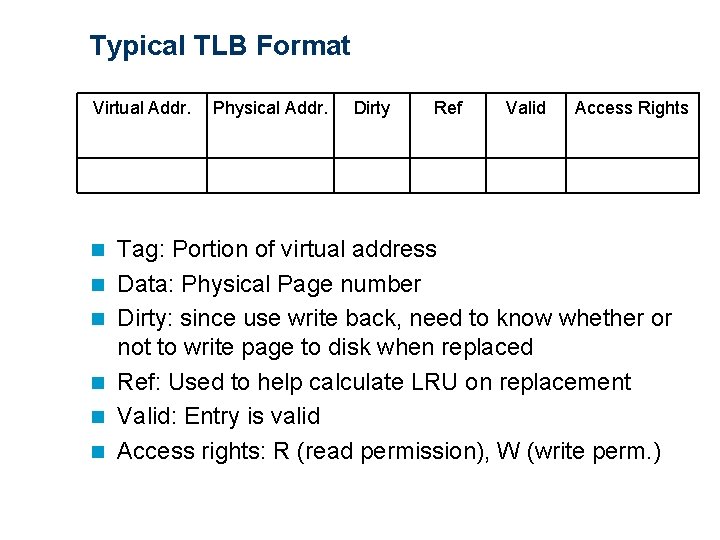

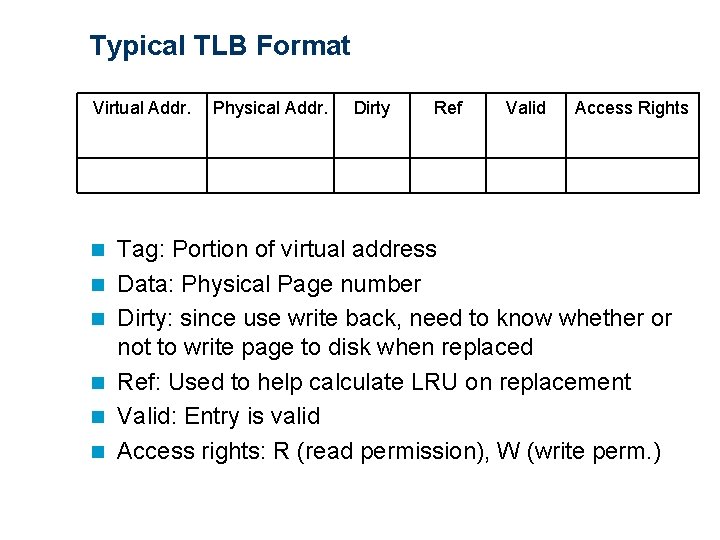

Typical TLB Format Virtual Addr. n n n Physical Addr. Dirty Ref Valid Access Rights Tag: Portion of virtual address Data: Physical Page number Dirty: since use write back, need to know whether or not to write page to disk when replaced Ref: Used to help calculate LRU on replacement Valid: Entry is valid Access rights: R (read permission), W (write perm. )

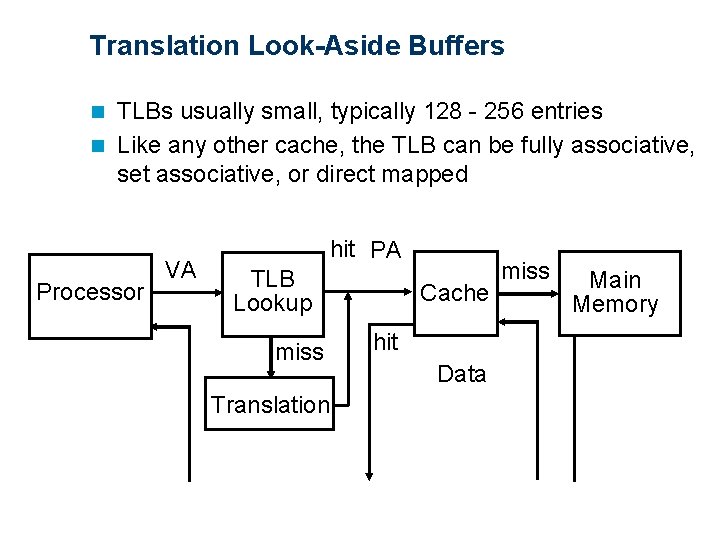

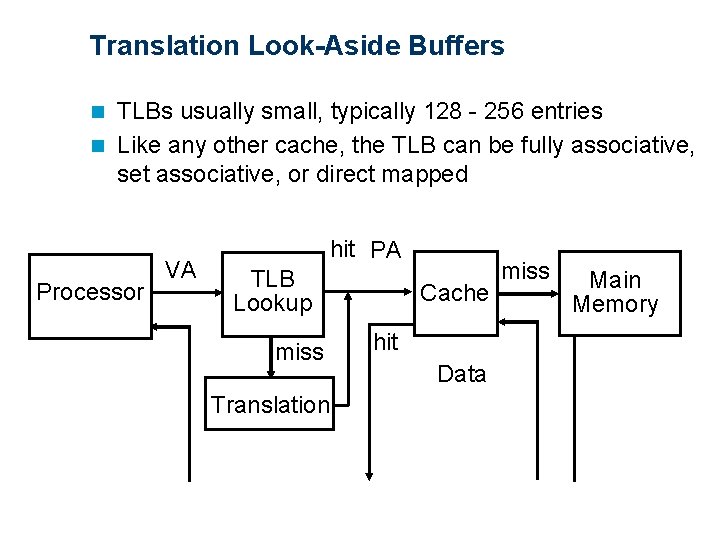

Translation Look-Aside Buffers TLBs usually small, typically 128 - 256 entries n Like any other cache, the TLB can be fully associative, set associative, or direct mapped n Processor VA hit PA TLB Lookup miss Translation Cache hit Data miss Main Memory

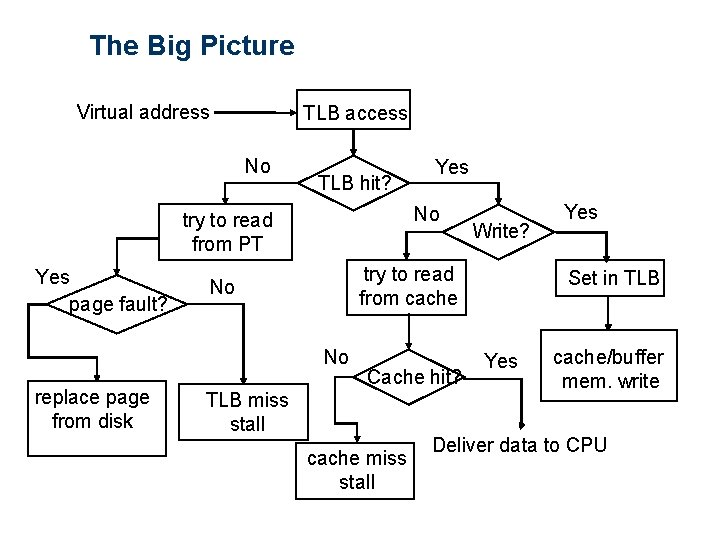

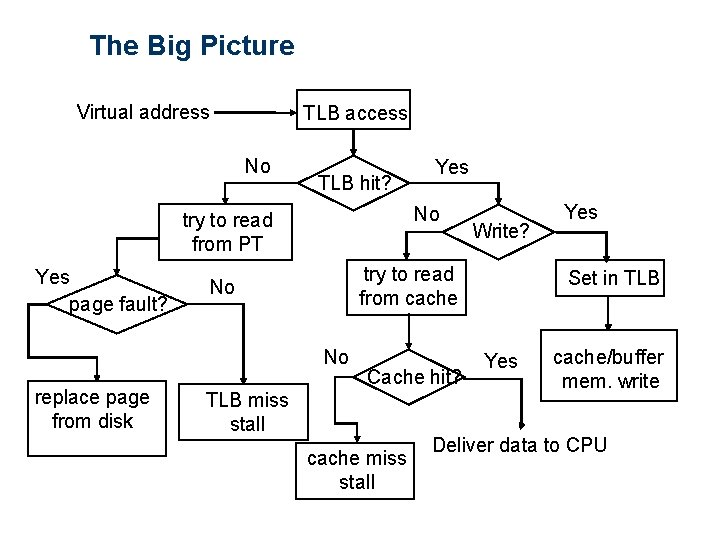

The Big Picture Virtual address TLB access No TLB hit? No try to read from PT Yes page fault? Write? try to read from cache No No replace page from disk Yes Cache hit? TLB miss stall cache miss stall Yes Set in TLB Yes cache/buffer mem. write Deliver data to CPU

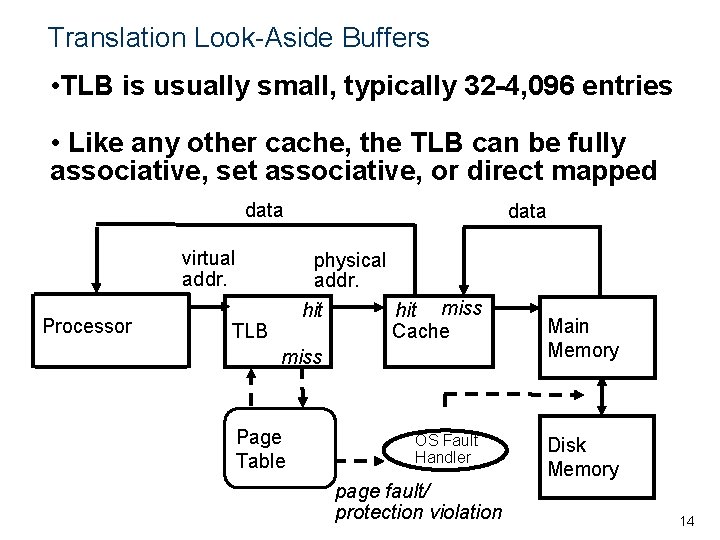

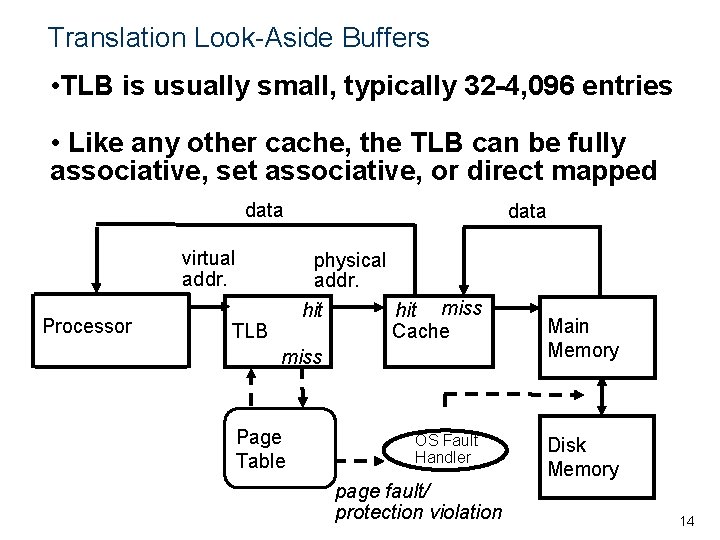

Translation Look-Aside Buffers • TLB is usually small, typically 32 -4, 096 entries • Like any other cache, the TLB can be fully associative, set associative, or direct mapped data virtual addr. Processor physical addr. hit miss TLB Cache miss Main Memory Page Table Disk Memory OS Fault Handler page fault/ protection violation 14

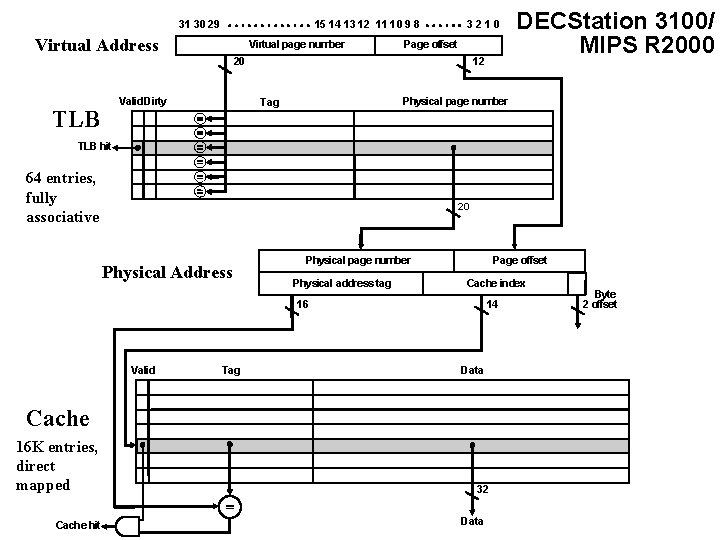

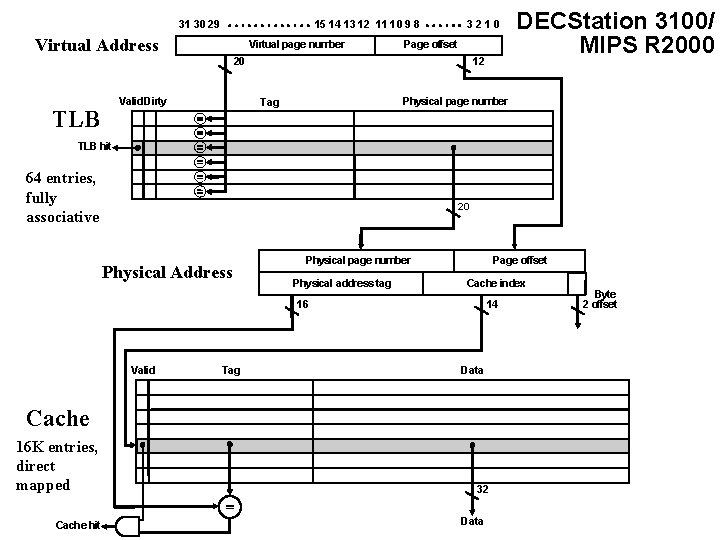

31 30 29 15 14 13 12 11 10 9 8 Virtual Address Virtual page number 3210 Page offset 20 Valid Dirty TLB 12 DECStation 3100/ MIPS R 2000 Physical page number Tag TLB hit 64 entries, fully associative 20 Physical Address Physical page number Physical address tag Page offset Cache index 14 16 Valid Tag Data Cache 16 K entries, direct mapped Cache hit 32 Data Byte 2 offset

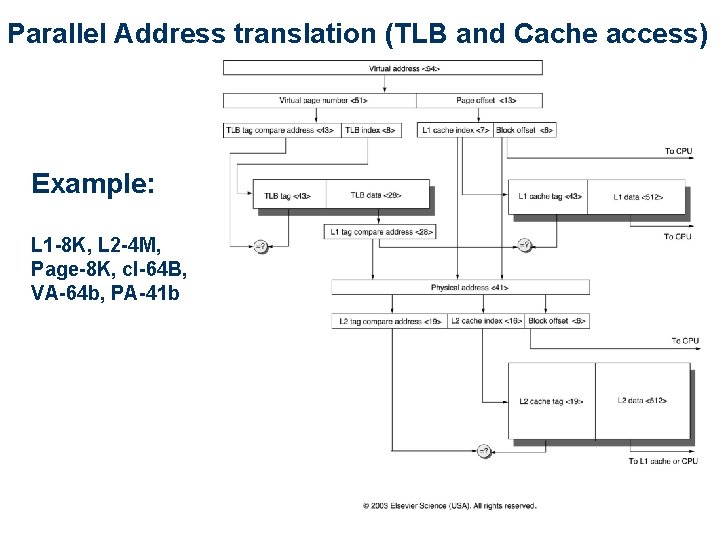

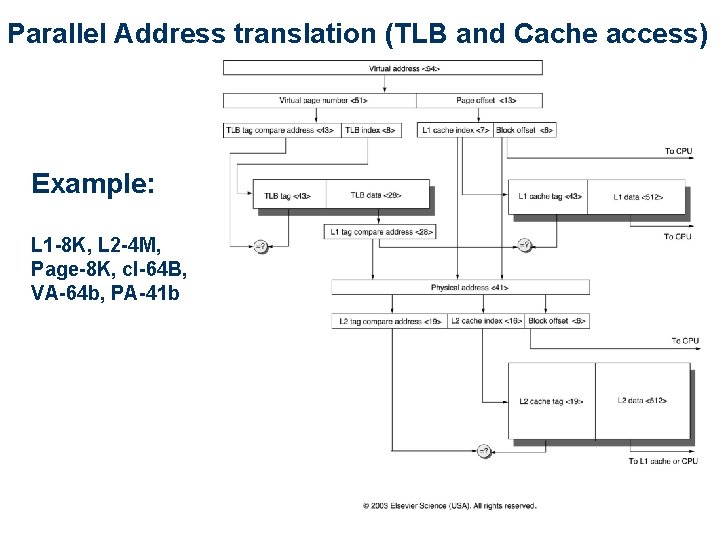

Parallel Address translation (TLB and Cache access) Example: L 1 -8 K, L 2 -4 M, Page-8 K, cl-64 B, VA-64 b, PA-41 b

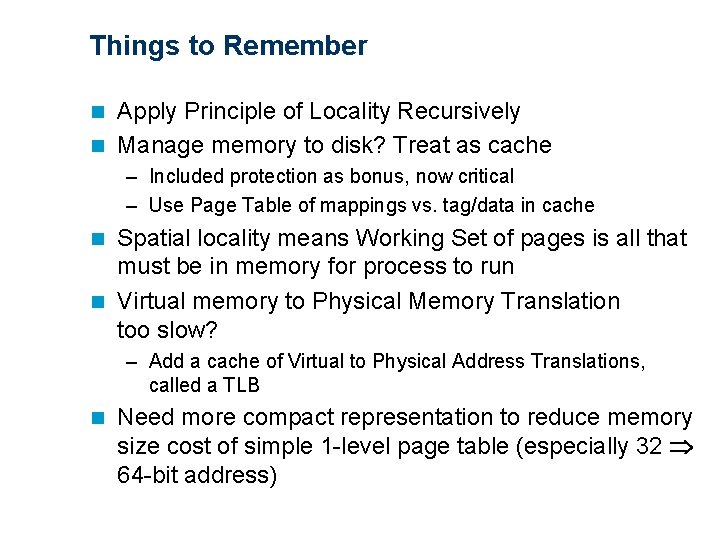

Things to Remember Apply Principle of Locality Recursively n Manage memory to disk? Treat as cache n – Included protection as bonus, now critical – Use Page Table of mappings vs. tag/data in cache Spatial locality means Working Set of pages is all that must be in memory for process to run n Virtual memory to Physical Memory Translation too slow? n – Add a cache of Virtual to Physical Address Translations, called a TLB n Need more compact representation to reduce memory size cost of simple 1 -level page table (especially 32 64 -bit address)