Virtual Memory HABEEB P Virtual Memory 2 Memory

Virtual Memory HABEEB P

Virtual Memory 2 Memory management technique that is implemented using both hardware and software. It maps memory addresses used by a program, called virtual addresses, into physical addresses in computer memory. Address translation hardware in the system, often referred to as a memory management unit or MMU, automatically translates virtual addresses to physical addresses Paging provides a mechanism to implement virtual memory.

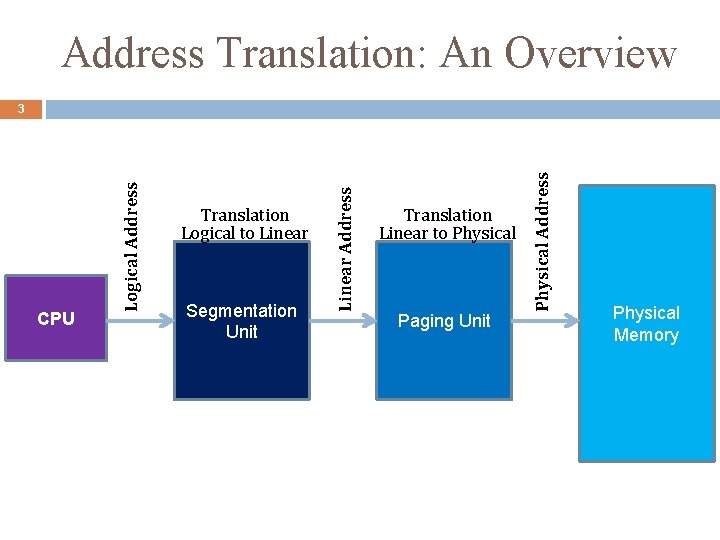

Address Translation: An Overview Segmentation Unit Translation Linear to Physical Paging Unit Physical Address Translation Logical to Linear Address CPU Logical Address 3 Physical Memory

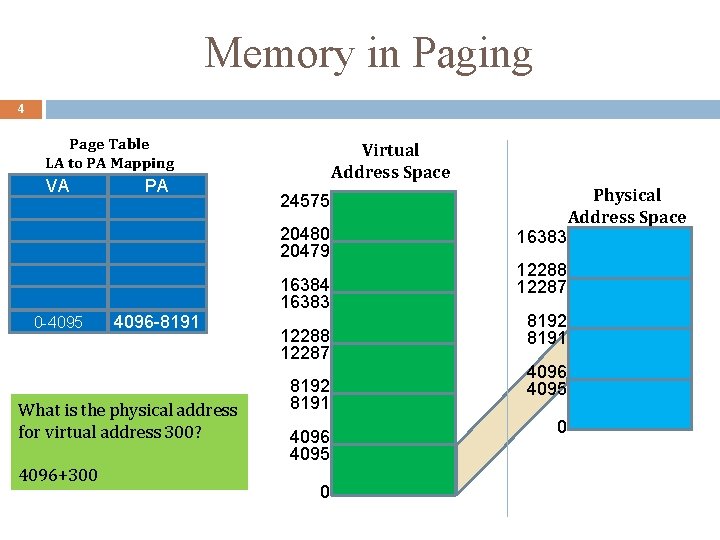

Memory in Paging 4 Page Table LA to PA Mapping VA PA Virtual Address Space 24575 20480 20479 16384 16383 0 -4095 4096 -8191 What is the physical address for virtual address 300? 4096+300 12288 12287 8192 8191 4096 4095 0 16383 12288 12287 8192 8191 4096 4095 0 Physical Address Space

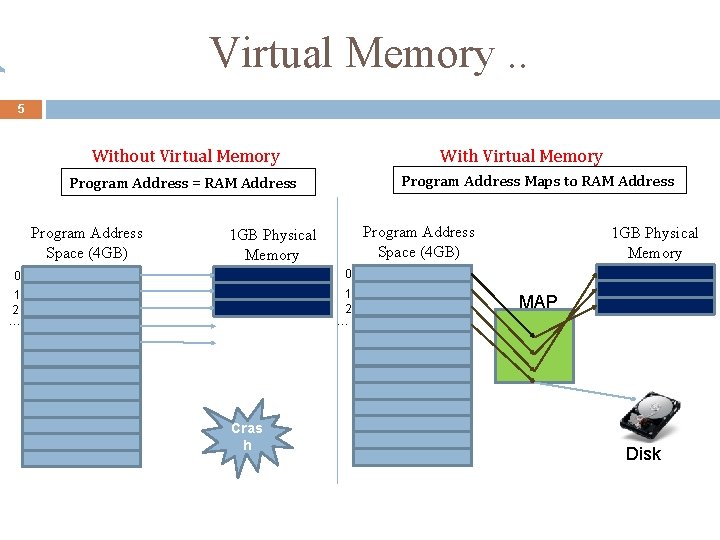

Virtual Memory. . 5 Without Virtual Memory With Virtual Memory Program Address Maps to RAM Address Program Address = RAM Address Program Address Space (4 GB) 1 GB Physical Memory 0 0 1 2 … Cras h 1 GB Physical Memory MAP Disk

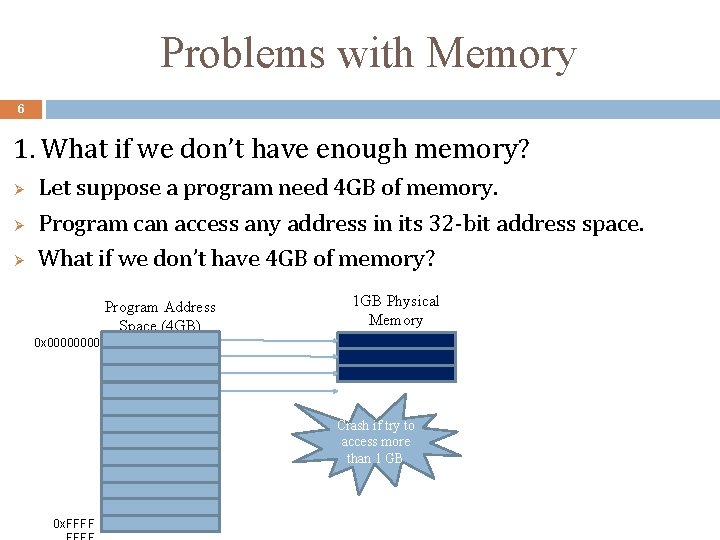

Problems with Memory 6 1. What if we don’t have enough memory? Ø Ø Ø Let suppose a program need 4 GB of memory. Program can access any address in its 32 -bit address space. What if we don’t have 4 GB of memory? Program Address Space (4 GB) 1 GB Physical Memory 0 x 0000 Crash if try to access more than 1 GB 0 x. FFFF

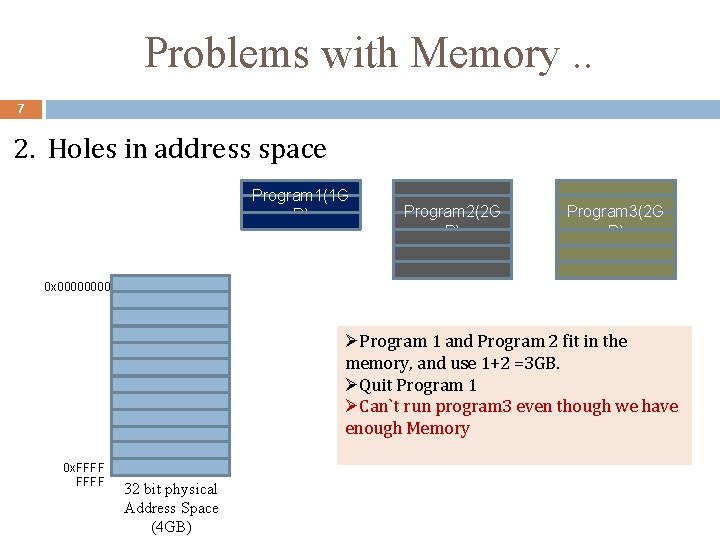

Problems with Memory. . 7 2. Holes in address space Program 1(1 G B) Program 2(2 G B) Program 3(2 G B) 0 x 0000 ØProgram 1 and Program 2 fit in the memory, and use 1+2 =3 GB. ØQuit Program 1 ØCan`t run program 3 even though we have enough Memory 0 x. FFFF 32 bit physical Address Space (4 GB)

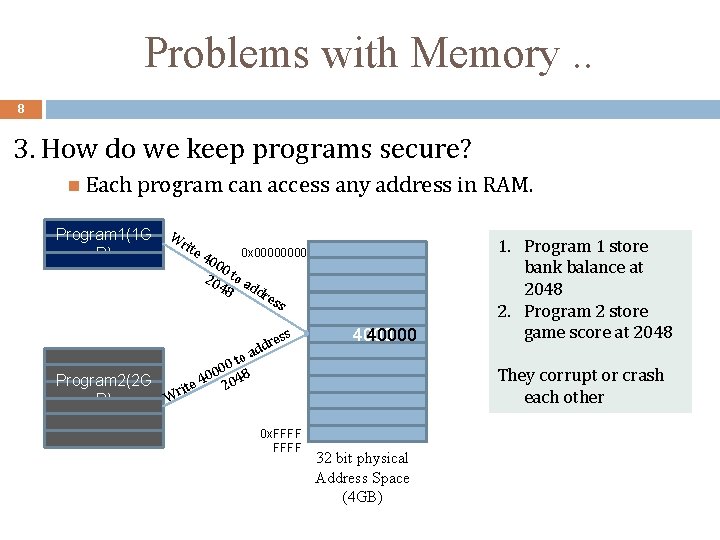

Problems with Memory. . 8 3. How do we keep programs secure? Each program can access any address in RAM. Program 1(1 G B) Wr it e 4 0 x 0000 00 0 20 to a 48 dd res s s res d d a 40000 4000 o 0 t 0 0 40 2048 e t ri 1. Program 1 store bank balance at 2048 2. Program 2 store game score at 2048 They corrupt or crash each other Program 2(2 G W B) 0 x. FFFF 32 bit physical Address Space (4 GB)

Memory Management Overview 9 The memory management facilities of the IA-32 architecture are divided into two parts Segmentation � Segmentation provides a mechanism of isolating individual code, data, and stack modules. � Each program divided into segments. Each segment can have different size. Paging provides a mechanism for implementing a conventional demand-paged, virtual-memory system where sections of a program’s execution environment are mapped into physical memory as needed. � Paging can be used to provide isolation between multiple tasks. �

Memory Management Overview. . 10 When operating in protected mode, some form of segmentation must be used. There is no mode bit to disable segmentation. The use of paging, however, is optional (If CR 0. PG = 0, paging is not used. The logical processor treats all linear addresses as if they were physical addresses. )

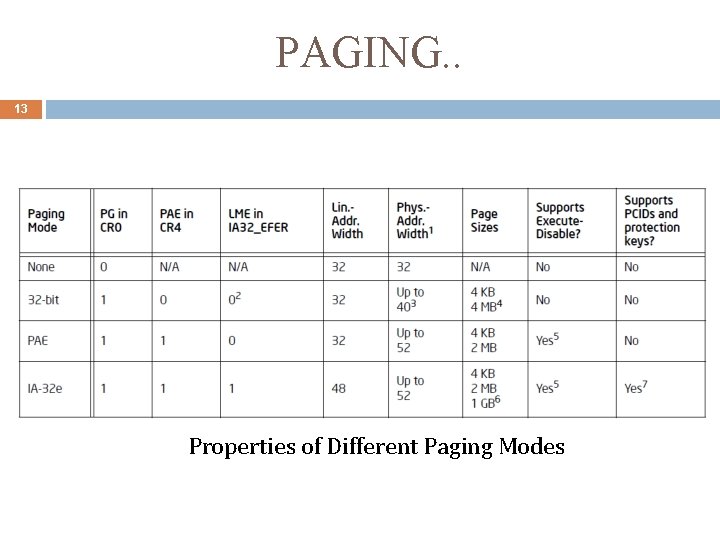

PAGING 11 Intel-64 processors support three different paging modes � 32 -bit paging (CR 0. PG = 1 and CR 4. PAE = 0). � PAE paging (CR 0. PG = 1, CR 4. PAE = 1, and IA 32_EFER. LME = 0). � IA-32 e paging (CR 0. PG = 1, CR 4. PAE =1, and IA 32_EFER. LME= 1)

PAGING. . 12 The three paging modes differ with regard to the following details � Linear-address width. � Physical-address width � Page size � Support for execute-disable access rights.

PAGING. . 13 Properties of Different Paging Modes

PAGING. . 14 Enumeration of Paging Features by CPUID � Software can discover support for different paging features using the CPUID instruction

32 -BIT PAGING 15 Although 40 bits corresponds to 1 TByte, linear addresses are limited to 32 bits; at most 4 GBytes of linear-address space may be accessed at any given time. CR 3 is used to locate the first paging-structure, the page directory.

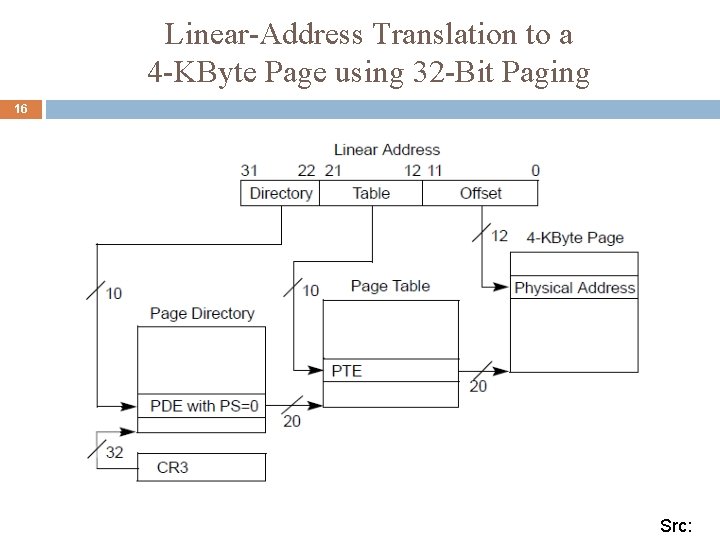

Linear-Address Translation to a 4 -KByte Page using 32 -Bit Paging 16 Src:

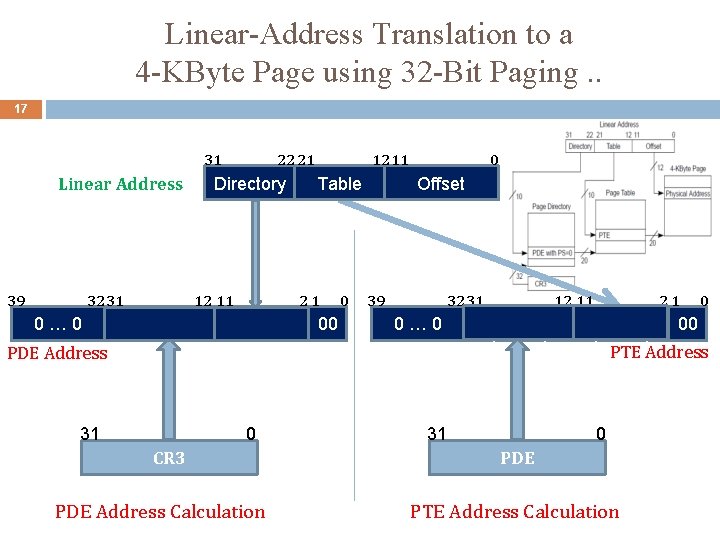

Linear-Address Translation to a 4 -KByte Page using 32 -Bit Paging. . 17 31 Linear Address 39 3231 0… 0 PDE Address CR 3 (31: 12) 31 22 21 Directory 12 11 LA (31: 22) 0 CR 3 PDE Address Calculation 12 11 Table 21 00 0 0 Offset 39 3231 0… 0 PDE (31: 12) 31 12 11 21 0 LA 00 (21: 12) PTE Address 0 PDE PTE Address Calculation

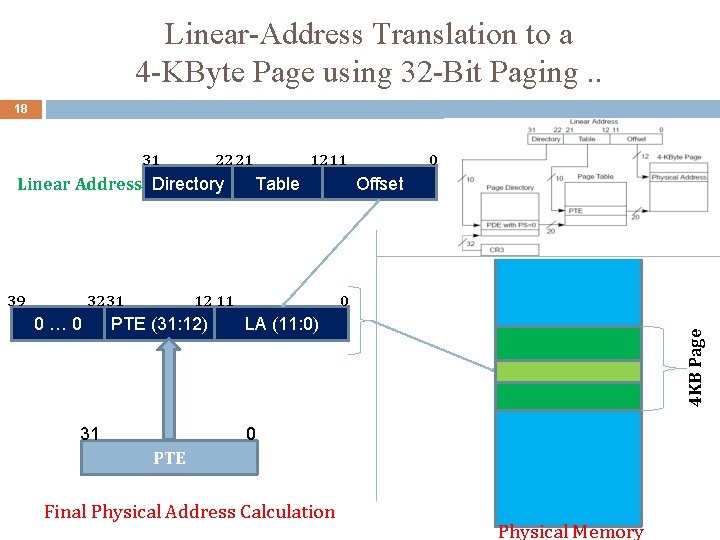

Linear-Address Translation to a 4 -KByte Page using 32 -Bit Paging. . 18 22 21 Linear Address Directory 39 3231 0… 0 12 11 Table 12 11 PTE (31: 12) 31 0 Offset 0 LA (11: 0) 4 KB Page 31 0 PTE Final Physical Address Calculation Physical Memory

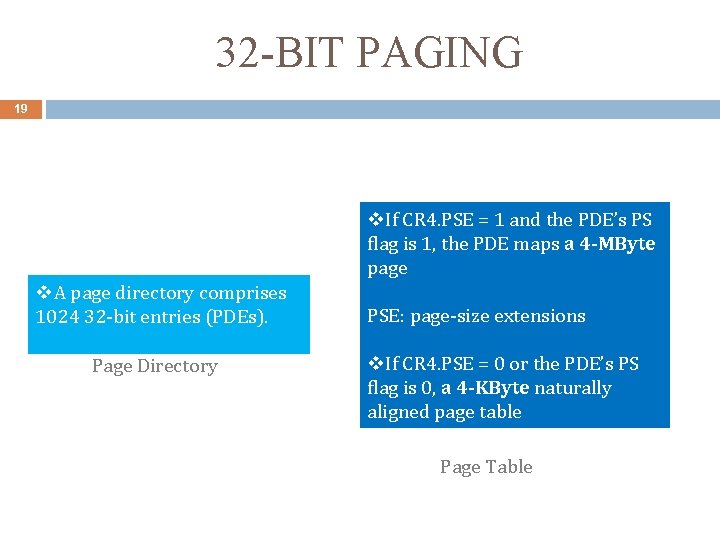

32 -BIT PAGING 19 v. If CR 4. PSE = 1 and the PDE’s PS flag is 1, the PDE maps a 4 -MByte page v. A page directory comprises 1024 32 -bit entries (PDEs). Page Directory PSE: page-size extensions v. If CR 4. PSE = 0 or the PDE’s PS flag is 0, a 4 -KByte naturally aligned page table Page Table

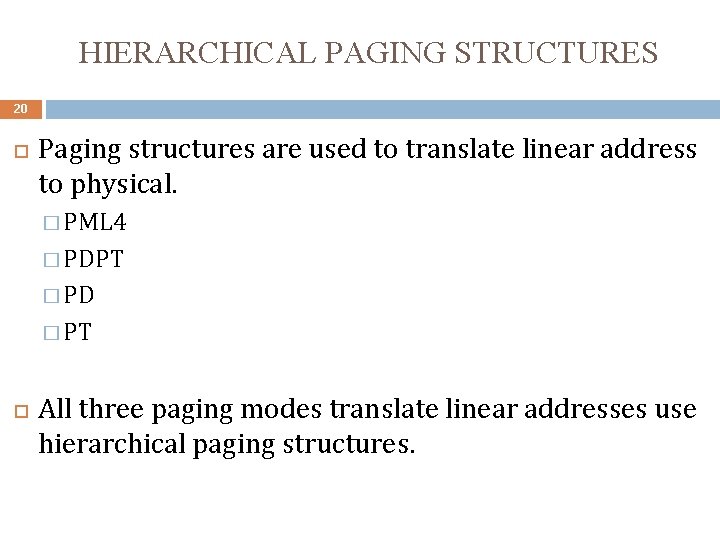

HIERARCHICAL PAGING STRUCTURES 20 Paging structures are used to translate linear address to physical. � PML 4 � PDPT � PD � PT All three paging modes translate linear addresses use hierarchical paging structures.

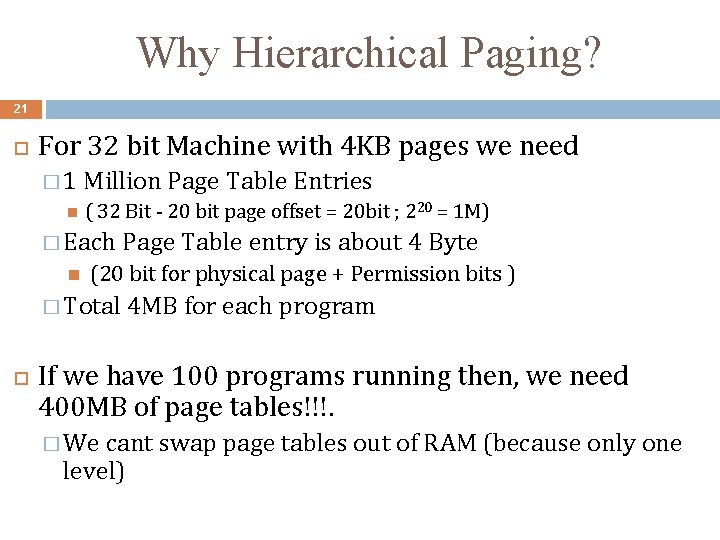

Why Hierarchical Paging? 21 For 32 bit Machine with 4 KB pages we need � 1 Million Page Table Entries ( 32 Bit - 20 bit page offset = 20 bit ; 220 = 1 M) � Each (20 bit for physical page + Permission bits ) � Total Page Table entry is about 4 Byte 4 MB for each program If we have 100 programs running then, we need 400 MB of page tables!!!. � We cant swap page tables out of RAM (because only one level)

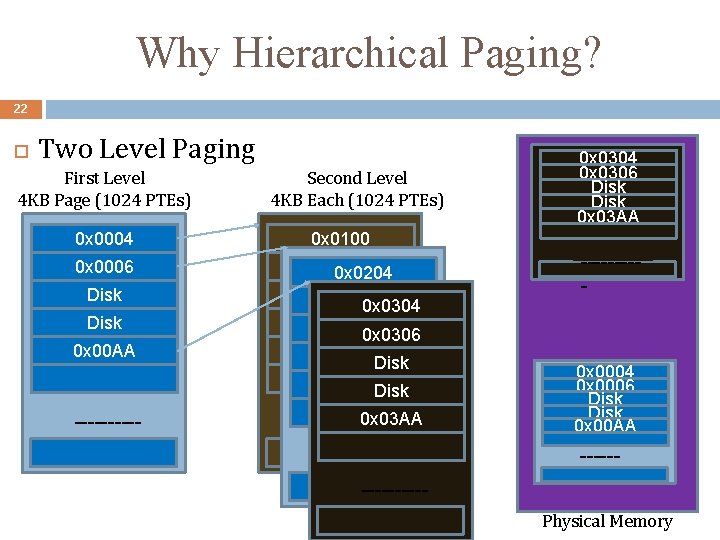

Why Hierarchical Paging? 22 Two Level Paging First Level 4 KB Page (1024 PTEs) Second Level 4 KB Each (1024 PTEs) 0 x 0004 0 x 0100 0 x 0006 0 x 0106 0 x 0204 Disk 0 x 0206 0 x 0304 Disk 0 x 0306 0 x 00 AA Disk Disk 0 x 00 AA ----- 0 x 0304 0 x 0306 Disk 0 x 03 AA ---------- 0 x 0004 0 x 0006 Disk 0 x 00 AA ---------Physical Memory

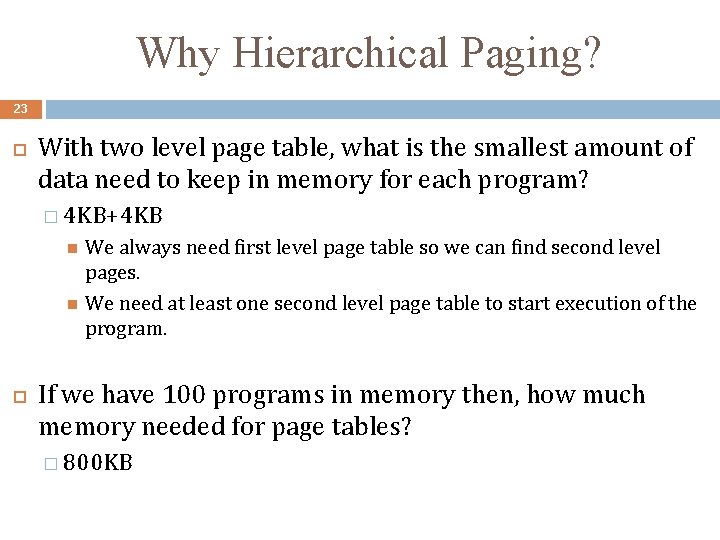

Why Hierarchical Paging? 23 With two level page table, what is the smallest amount of data need to keep in memory for each program? � 4 KB+4 KB We always need first level page table so we can find second level pages. We need at least one second level page table to start execution of the program. If we have 100 programs in memory then, how much memory needed for page tables? � 800 KB

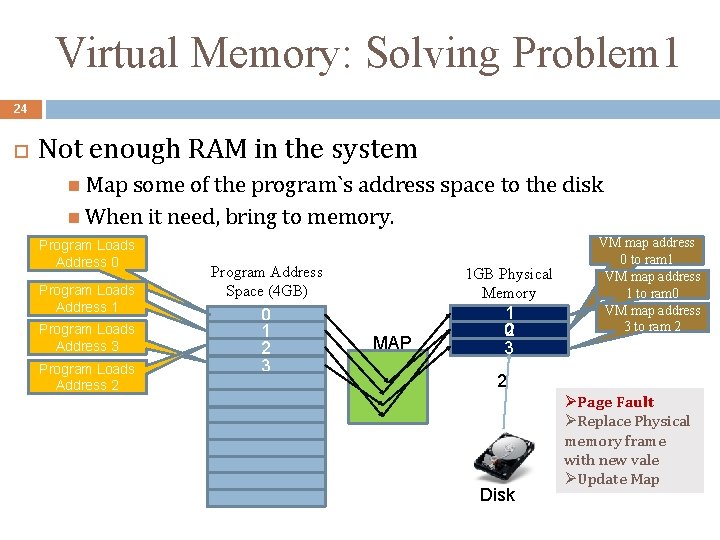

Virtual Memory: Solving Problem 1 24 Not enough RAM in the system Map some of the program`s address space to the disk When it need, bring to memory. Program Loads Address 0 Program Loads Address 1 Program Loads Address 3 Program Loads Address 2 Program Address Space (4 GB) 1 GB Physical Memory 0 1 2 3 1 2 0 3 MAP VM map address 0 to ram 1 VM map address 1 to ram 0 VM map address 3 to ram 2 2 Disk ØPage Fault ØReplace Physical memory frame with new vale ØUpdate Map

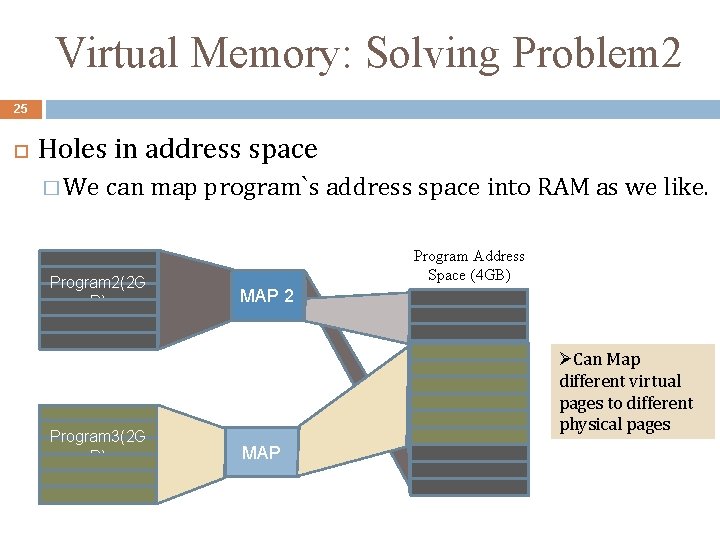

Virtual Memory: Solving Problem 2 25 Holes in address space � We can map program`s address space into RAM as we like. Program 2(2 G B) Program 3(2 G B) Program Address Space (4 GB) MAP 2 ØCan Map different virtual pages to different physical pages MAP

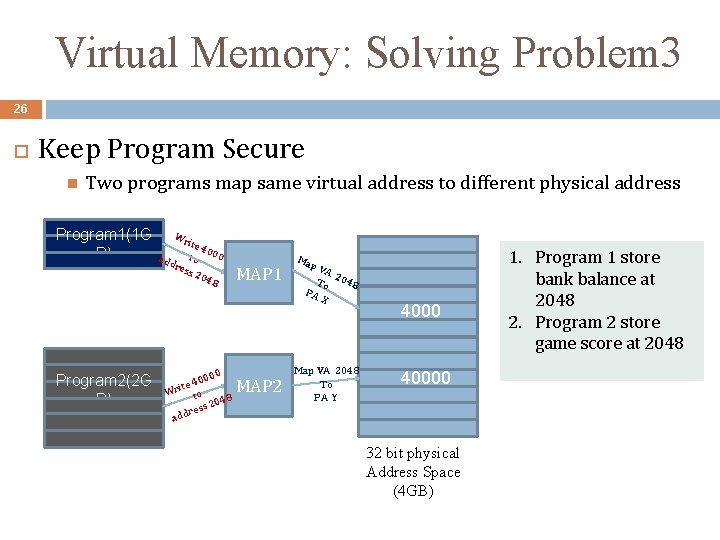

Virtual Memory: Solving Problem 3 26 Keep Program Secure Two programs map same virtual address to different physical address Program 1(1 G B) Program 2(2 G B) Wr ite 40 add to 00 res s 20 48 00 400 e t i Wr to 048 ss 2 e r add MAP 1 MAP 2 Ma p VA 2 To 048 PA X Map VA 2048 To PA Y 40000 32 bit physical Address Space (4 GB) 1. Program 1 store bank balance at 2048 2. Program 2 store game score at 2048

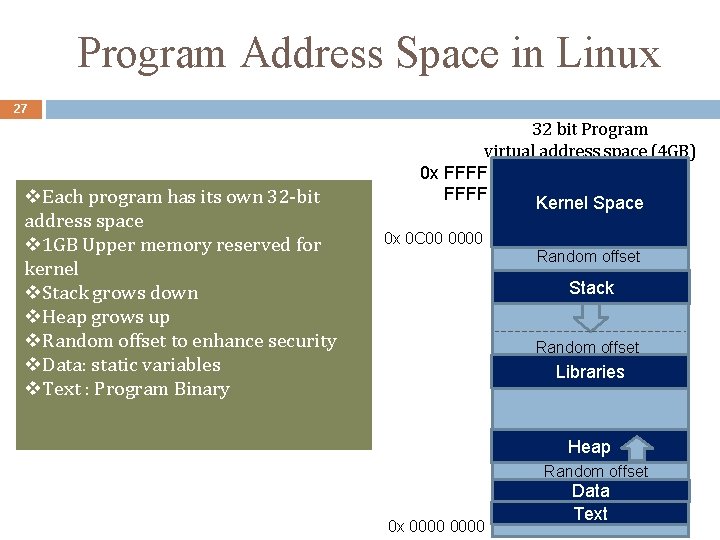

Program Address Space in Linux 27 v. Each program has its own 32 -bit address space v 1 GB Upper memory reserved for kernel v. Stack grows down v. Heap grows up v. Random offset to enhance security v. Data: static variables v. Text : Program Binary 32 bit Program virtual address space (4 GB) 0 x FFFF Kernel Space 0 x 0 C 00 0000 Random offset Stack Random offset Libraries Heap Random offset 0 x 0000 Data Text

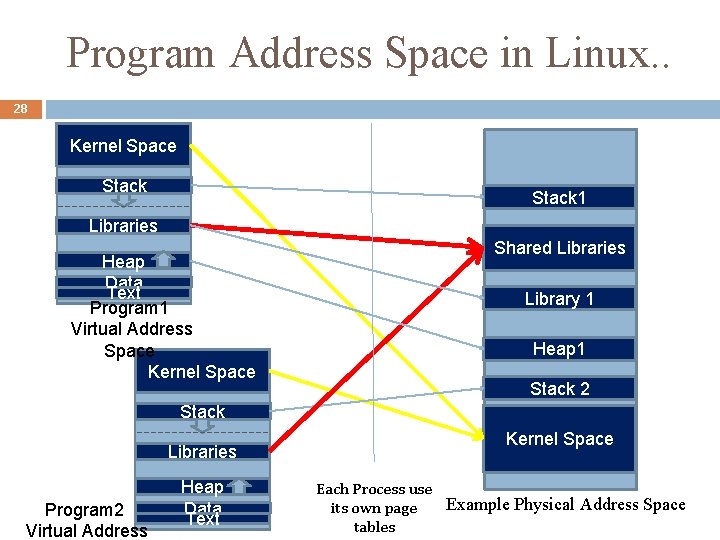

Program Address Space in Linux. . 28 Kernel Space Stack 1 Libraries Heap Data Text Program 1 Virtual Address Space Kernel Space Shared Libraries Library 1 Heap 1 Stack 2 Stack Libraries Program 2 Virtual Address Heap Data Text Kernel Space Each Process use Example Physical Address Space its own page tables

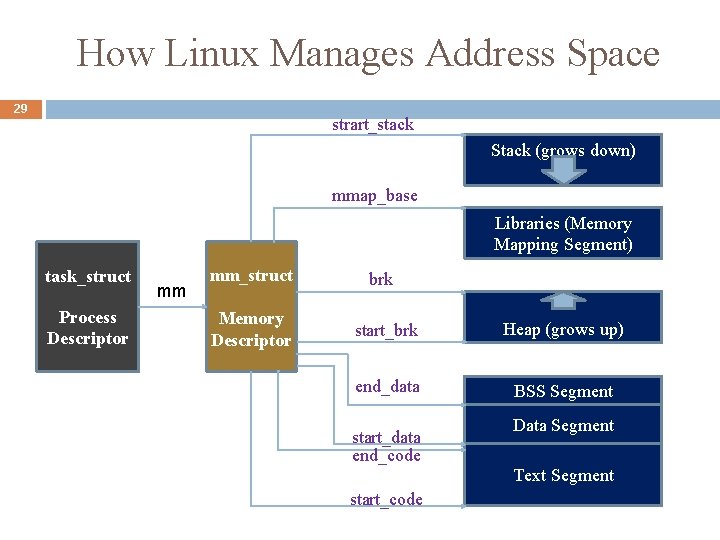

How Linux Manages Address Space 29 strart_stack Stack (grows down) mmap_base Libraries (Memory Mapping Segment) task_struct Process Descriptor mm mm_struct Memory Descriptor brk start_brk Heap (grows up) end_data BSS Segment start_data end_code Data Segment Text Segment start_code

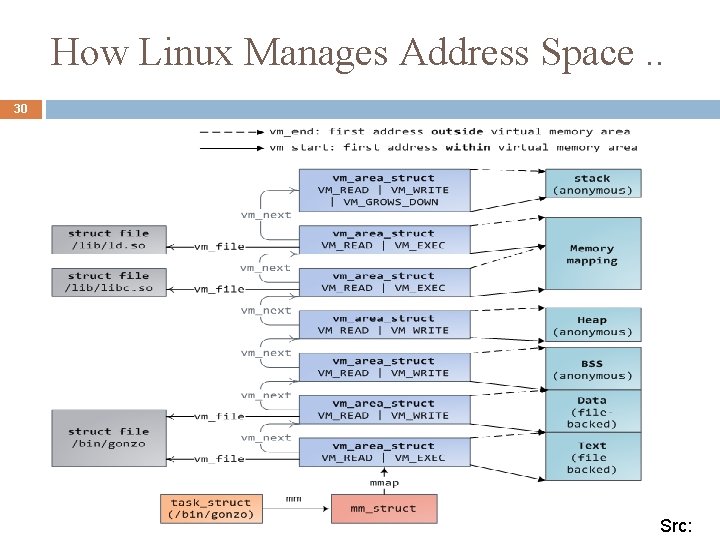

How Linux Manages Address Space. . 30 Src:

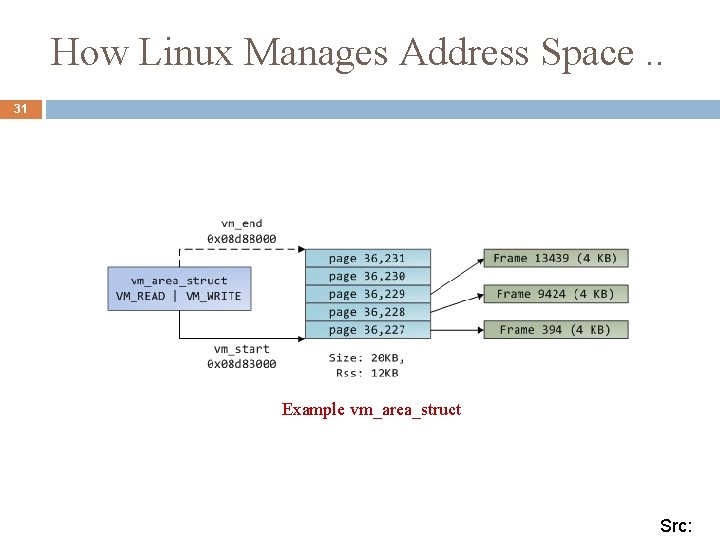

How Linux Manages Address Space. . 31 Example vm_area_struct Src:

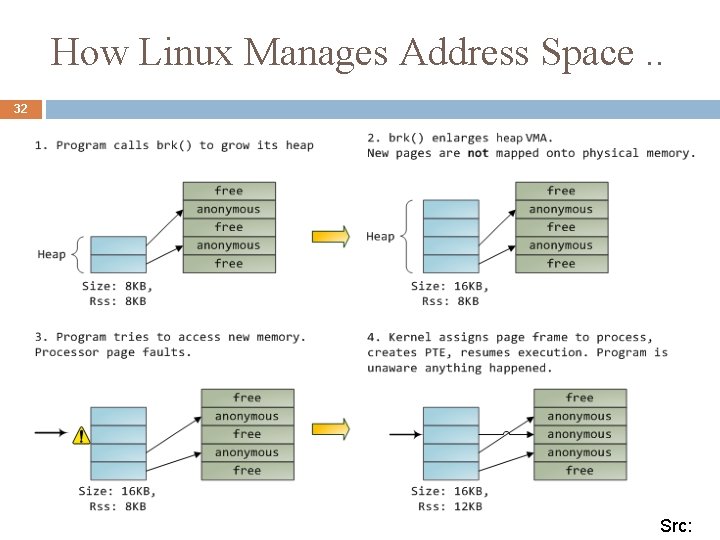

How Linux Manages Address Space. . 32 Src:

PAGE-FAULT EXCEPTIONS 33 Accesses using linear addresses may cause page-fault exceptions. An access to a linear address may cause a page-fault exception for either of two reasons: � There is no translation for the linear address � There is a translation for the linear address, but its access rights do not permit the access. In Linux do_page_fault() function is responsible for the handling of page fault.

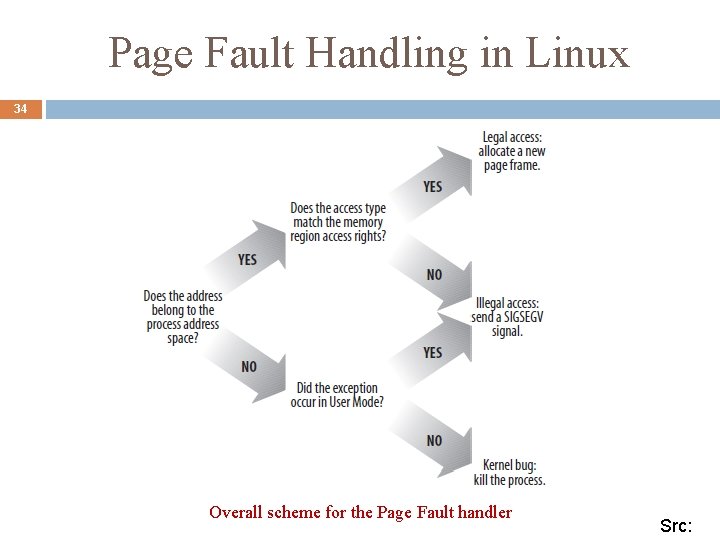

Page Fault Handling in Linux 34 Overall scheme for the Page Fault handler Src:

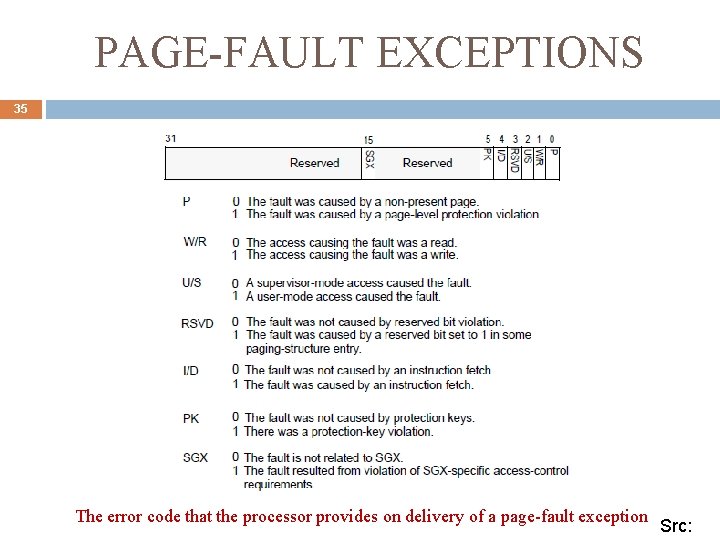

PAGE-FAULT EXCEPTIONS 35 The error code that the processor provides on delivery of a page-fault exception Src:

![References 36 [1]. Intel 64 -ia-32 -architectures-software-developermanual-325462 [2]. Understanding the LINUX KERNEL , Third References 36 [1]. Intel 64 -ia-32 -architectures-software-developermanual-325462 [2]. Understanding the LINUX KERNEL , Third](http://slidetodoc.com/presentation_image_h/ec97cc56b88cbe4d116f6830ad170ea5/image-36.jpg)

References 36 [1]. Intel 64 -ia-32 -architectures-software-developermanual-325462 [2]. Understanding the LINUX KERNEL , Third edition, Daniel P. Bovet and Marco Cesati [3]. http: //duartes. org/gustavo/blog [4]. You. Tube video : Virtual Memory by David Black. Schaffer

THANK YOU 37

- Slides: 37