Using the USART Configuration and Programming CE2810 Dr

- Slides: 10

Using the USART Configuration and Programming CE-2810 Dr. Mark L. Hornick 1

Configuring the USART Several I/O registers are used to: Control the configuration of the USART 1. l l Baud rate (bits/s) Parity (even/odd/none) Number of data bits (4 -9) Framing ( 1 or 2 stop bits) Represent the status of a recent transmission or reception 2. l l Frame errors Data overrun errors Tx complete Rx complete CS-280 Dr. Mark L. Hornick 2

Lots of I/O registers make configuring the USART a bit complicated: UCSRA – USART Control/Status Register A Mainly status flags UCSRB – USART Control/Status Register B Flags for enabling transmitting, receiving, interrupts UCSRC – USART Control/Status Register C Mode selection UBRRH, UBRRL– USART Baud Rate Registers (16 bit combined) Baud rate selection UDR– USART Data Register Does two things at once: l l Contains data to be transmitted, or Data that is received CE-2810 Dr. Mark L. Hornick Full documentation on the USART can be found (around p 146) of the Atmega 32. pdf reference manual 3

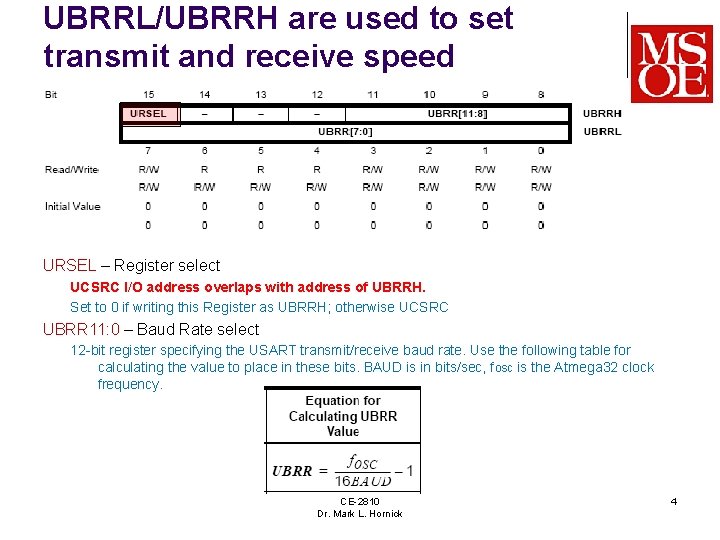

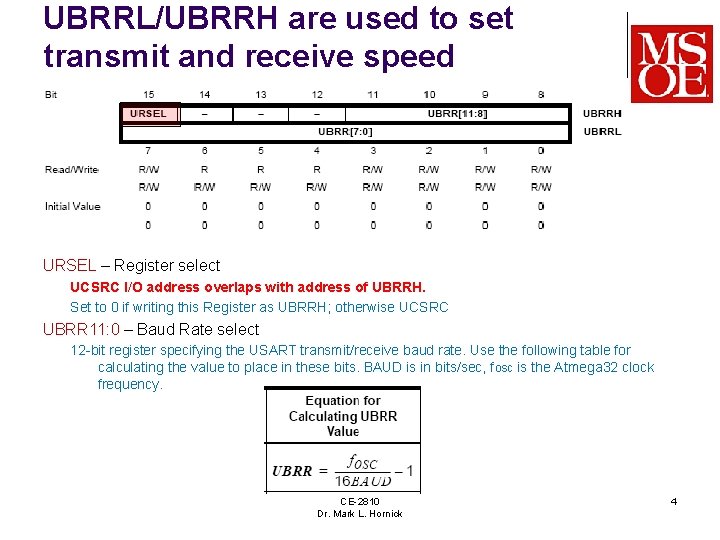

UBRRL/UBRRH are used to set transmit and receive speed URSEL – Register select UCSRC I/O address overlaps with address of UBRRH. Set to 0 if writing this Register as UBRRH; otherwise UCSRC UBRR 11: 0 – Baud Rate select 12 -bit register specifying the USART transmit/receive baud rate. Use the following table for calculating the value to place in these bits. BAUD is in bits/sec, fosc is the Atmega 32 clock frequency. CE-2810 Dr. Mark L. Hornick 4

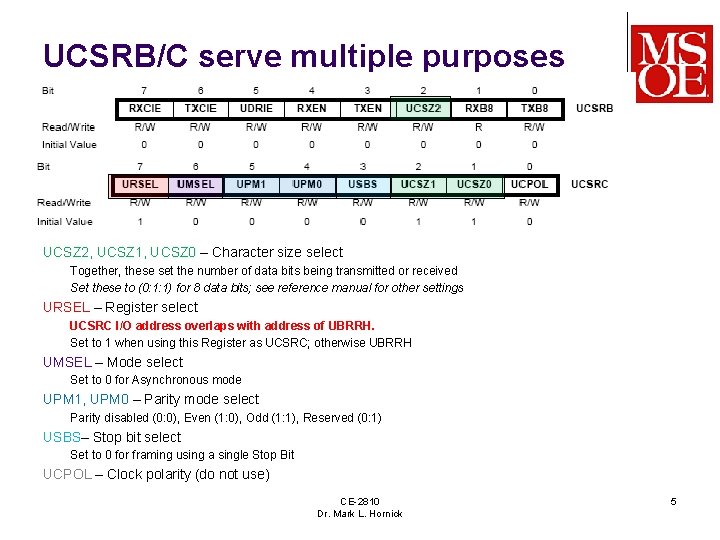

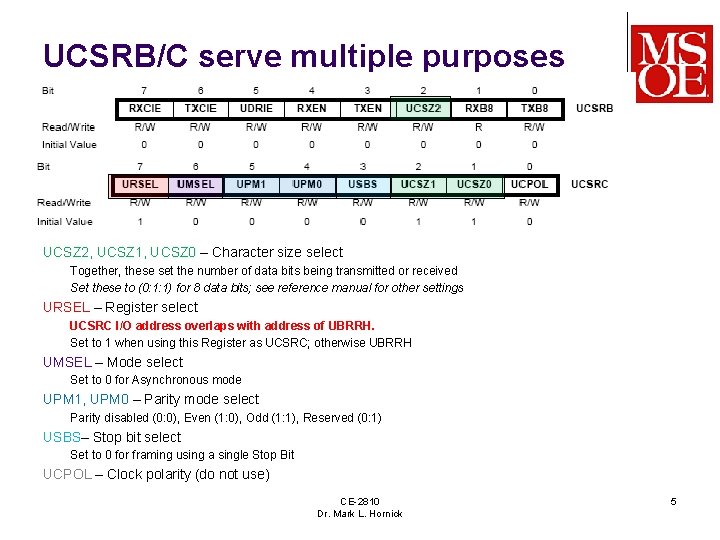

UCSRB/C serve multiple purposes UCSZ 2, UCSZ 1, UCSZ 0 – Character size select Together, these set the number of data bits being transmitted or received Set these to (0: 1: 1) for 8 data bits; see reference manual for other settings URSEL – Register select UCSRC I/O address overlaps with address of UBRRH. Set to 1 when using this Register as UCSRC; otherwise UBRRH UMSEL – Mode select Set to 0 for Asynchronous mode UPM 1, UPM 0 – Parity mode select Parity disabled (0: 0), Even (1: 0), Odd (1: 1), Reserved (0: 1) USBS– Stop bit select Set to 0 for framing using a single Stop Bit UCPOL – Clock polarity (do not use) CE-2810 Dr. Mark L. Hornick 5

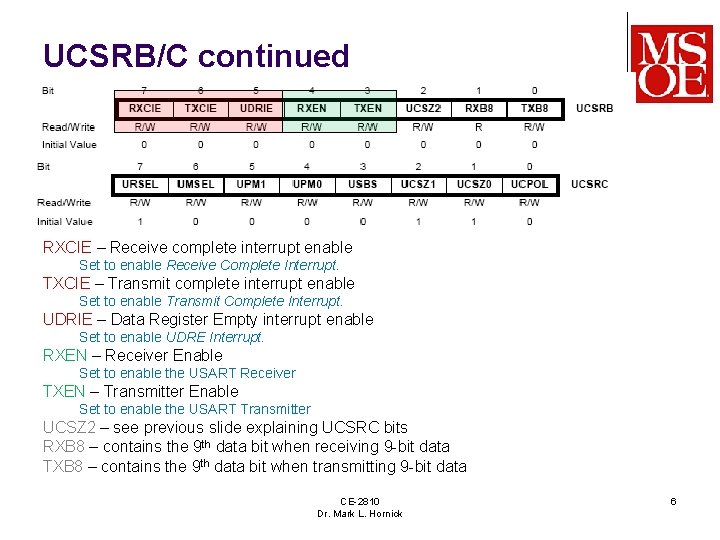

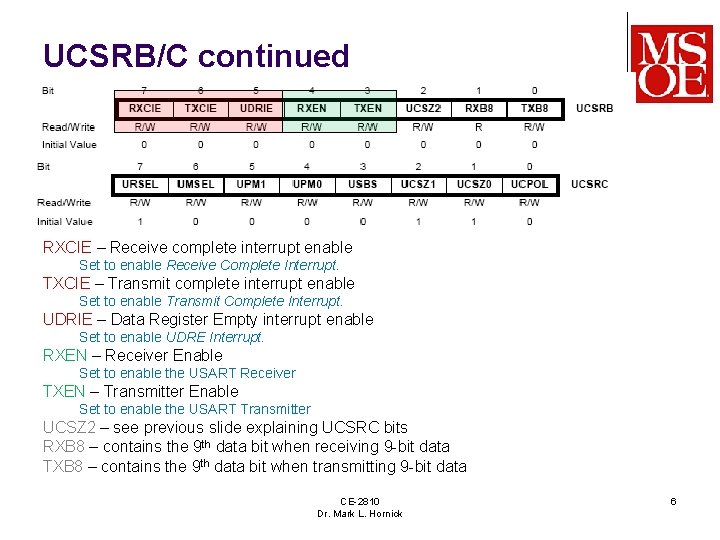

UCSRB/C continued RXCIE – Receive complete interrupt enable Set to enable Receive Complete Interrupt. TXCIE – Transmit complete interrupt enable Set to enable Transmit Complete Interrupt. UDRIE – Data Register Empty interrupt enable Set to enable UDRE Interrupt. RXEN – Receiver Enable Set to enable the USART Receiver TXEN – Transmitter Enable Set to enable the USART Transmitter UCSZ 2 – see previous slide explaining UCSRC bits RXB 8 – contains the 9 th data bit when receiving 9 -bit data TXB 8 – contains the 9 th data bit when transmitting 9 -bit data CE-2810 Dr. Mark L. Hornick 6

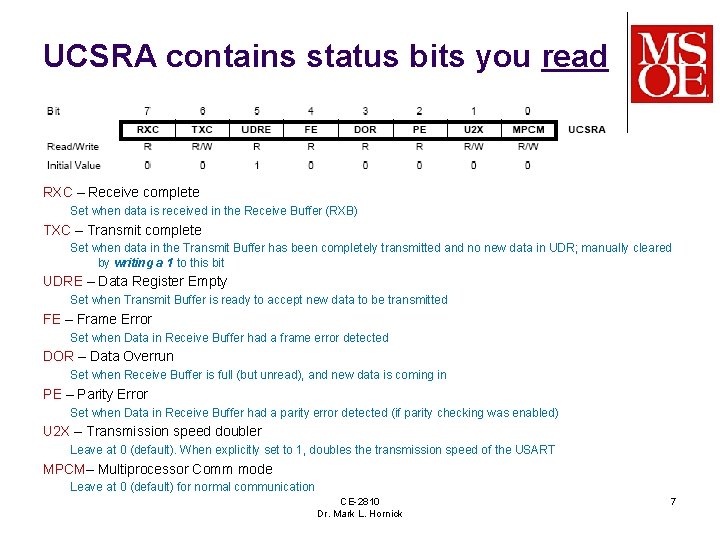

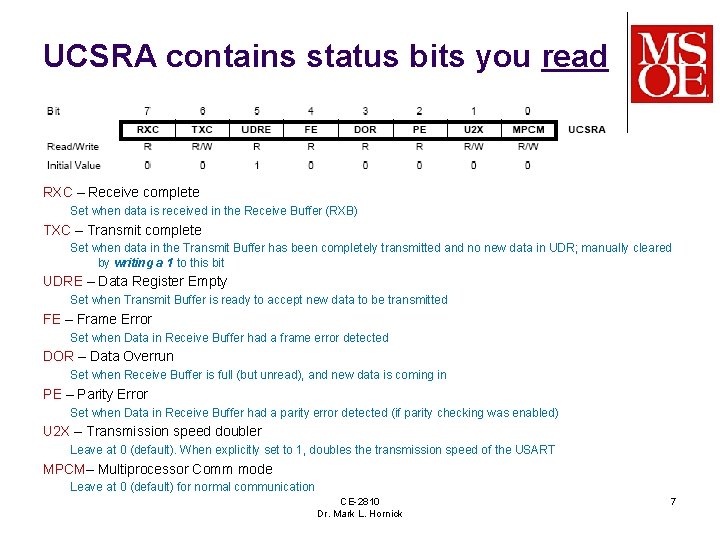

UCSRA contains status bits you read RXC – Receive complete Set when data is received in the Receive Buffer (RXB) TXC – Transmit complete Set when data in the Transmit Buffer has been completely transmitted and no new data in UDR; manually cleared by writing a 1 to this bit UDRE – Data Register Empty Set when Transmit Buffer is ready to accept new data to be transmitted FE – Frame Error Set when Data in Receive Buffer had a frame error detected DOR – Data Overrun Set when Receive Buffer is full (but unread), and new data is coming in PE – Parity Error Set when Data in Receive Buffer had a parity error detected (if parity checking was enabled) U 2 X – Transmission speed doubler Leave at 0 (default). When explicitly set to 1, doubles the transmission speed of the USART MPCM– Multiprocessor Comm mode Leave at 0 (default) for normal communication CE-2810 Dr. Mark L. Hornick 7

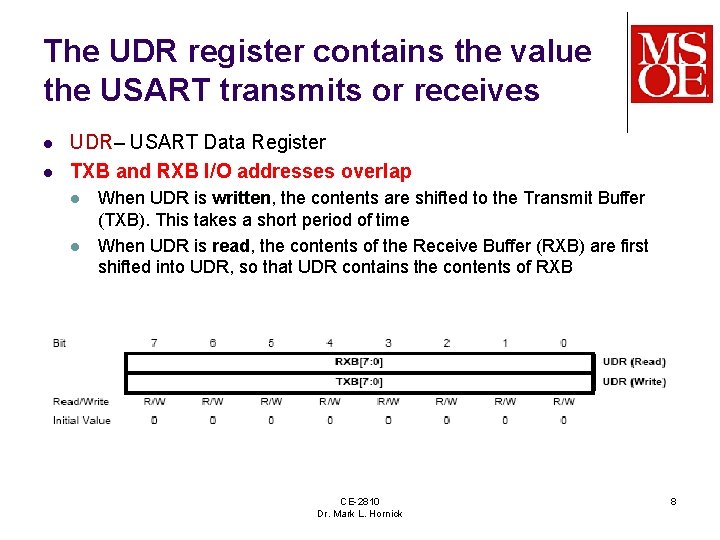

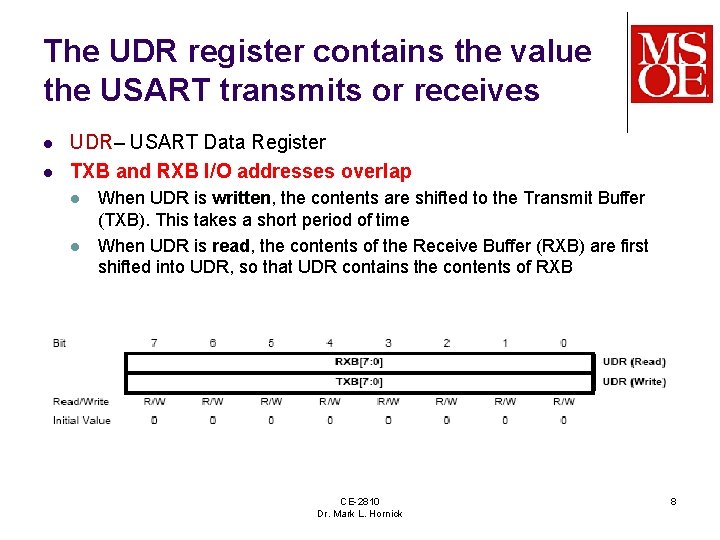

The UDR register contains the value the USART transmits or receives l l UDR– USART Data Register TXB and RXB I/O addresses overlap l l When UDR is written, the contents are shifted to the Transmit Buffer (TXB). This takes a short period of time When UDR is read, the contents of the Receive Buffer (RXB) are first shifted into UDR, so that UDR contains the contents of RXB CE-2810 Dr. Mark L. Hornick 8

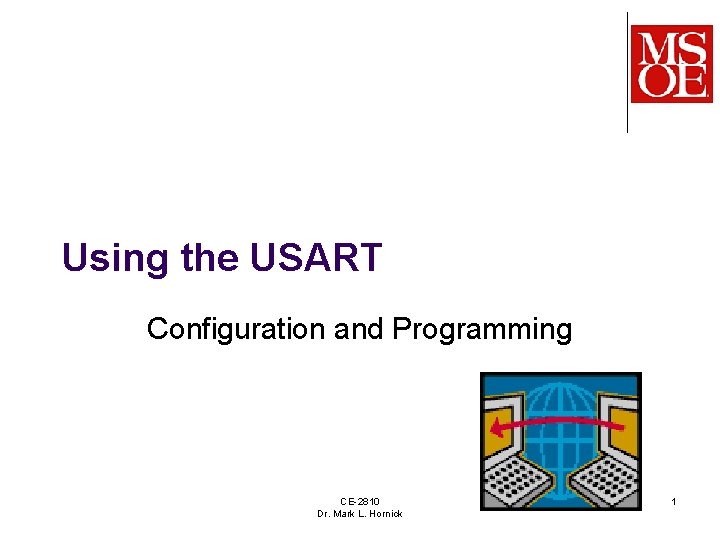

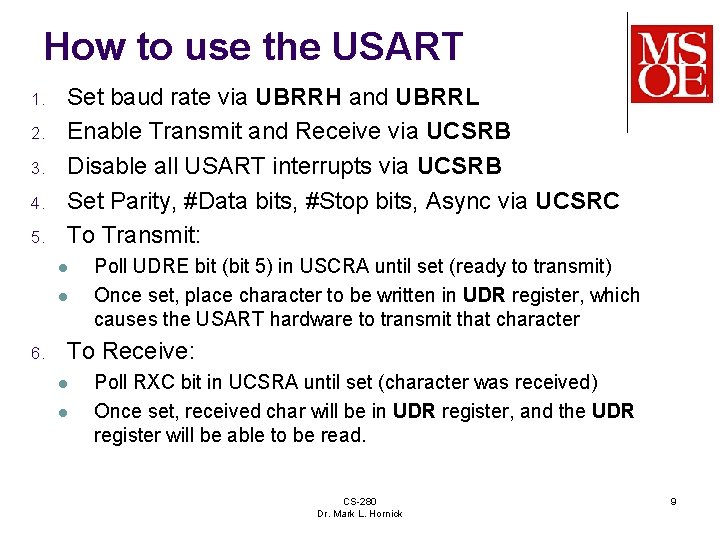

How to use the USART 1. 2. 3. 4. 5. Set baud rate via UBRRH and UBRRL Enable Transmit and Receive via UCSRB Disable all USART interrupts via UCSRB Set Parity, #Data bits, #Stop bits, Async via UCSRC To Transmit: l l 6. Poll UDRE bit (bit 5) in USCRA until set (ready to transmit) Once set, place character to be written in UDR register, which causes the USART hardware to transmit that character To Receive: l l Poll RXC bit in UCSRA until set (character was received) Once set, received char will be in UDR register, and the UDR register will be able to be read. CS-280 Dr. Mark L. Hornick 9

The USART can receive while it is transmitting But the TXB and RXB buffers can each hold only one character l So you must keep polling RXC to avoid dropping received characters l And you must poll UDRE before sending another character to ensure that TXC has been emptied CS-280 Dr. Mark L. Hornick 10