Ultra low power PLL design and noise analysis

- Slides: 14

Ultra low power PLL design and noise analysis EE 241 Prof. Borivoje Nikolic Peter Chen, Mingcui Zhou EE 241 Term Project - Spring 2004

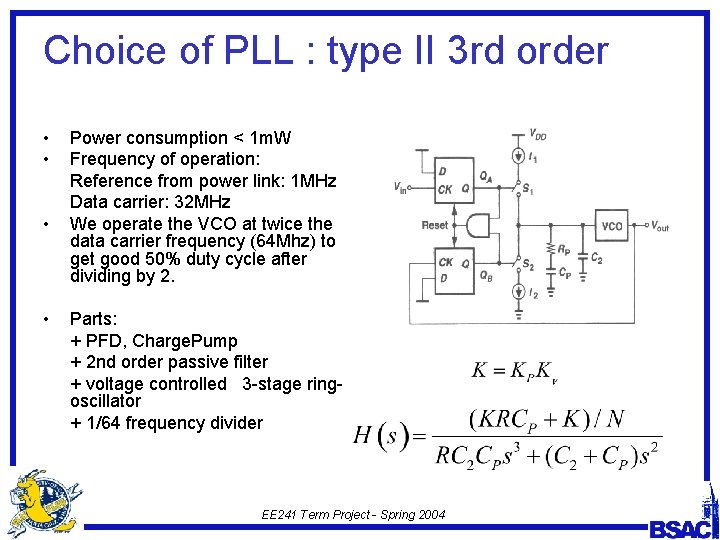

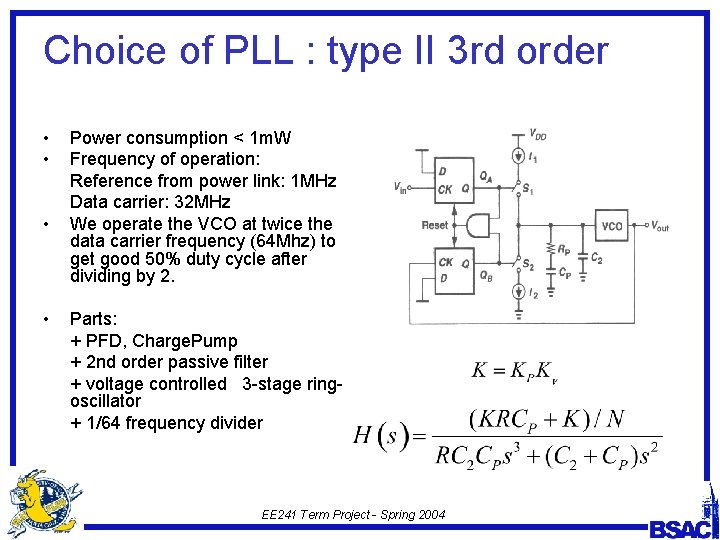

Choice of PLL : type II 3 rd order • • Power consumption < 1 m. W Frequency of operation: Reference from power link: 1 MHz Data carrier: 32 MHz We operate the VCO at twice the data carrier frequency (64 Mhz) to get good 50% duty cycle after dividing by 2. Parts: + PFD, Charge. Pump + 2 nd order passive filter + voltage controlled 3 -stage ringoscillator + 1/64 frequency divider EE 241 Term Project - Spring 2004

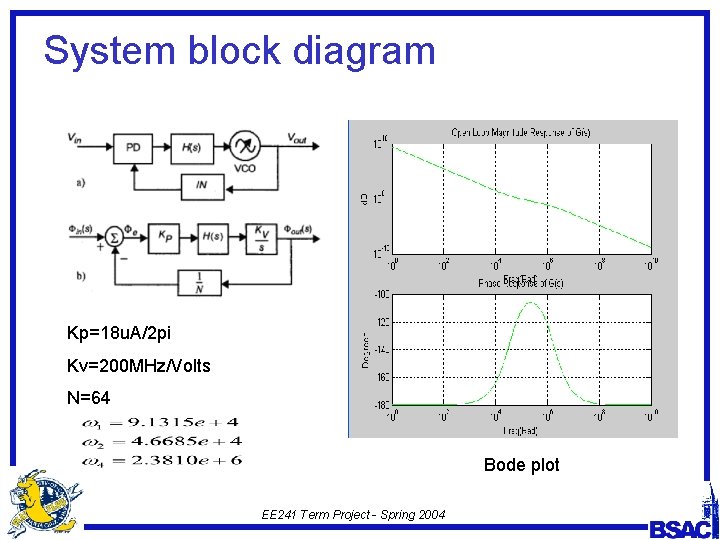

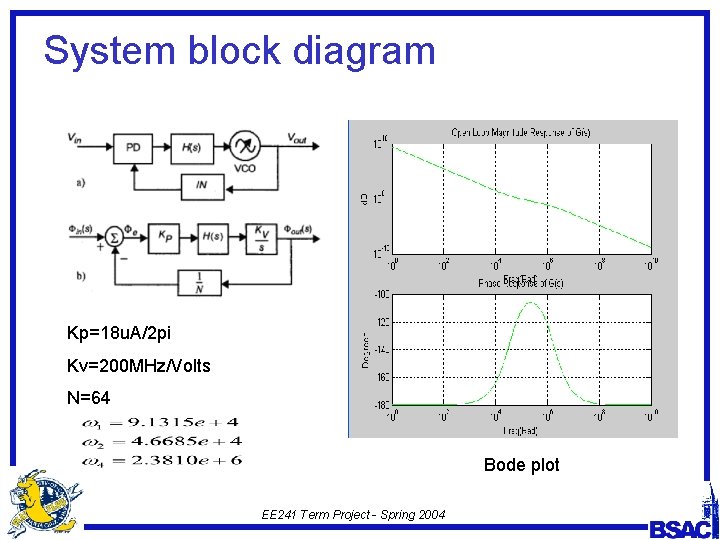

System block diagram Kp=18 u. A/2 pi Kv=200 MHz/Volts N=64 Bode plot EE 241 Term Project - Spring 2004

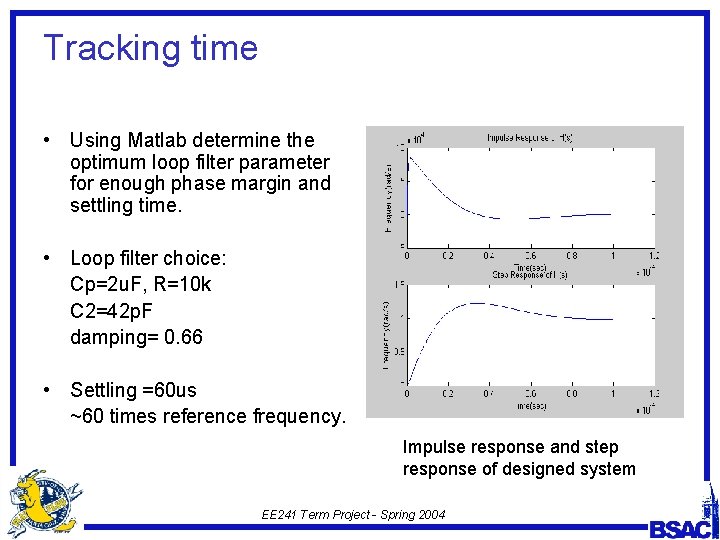

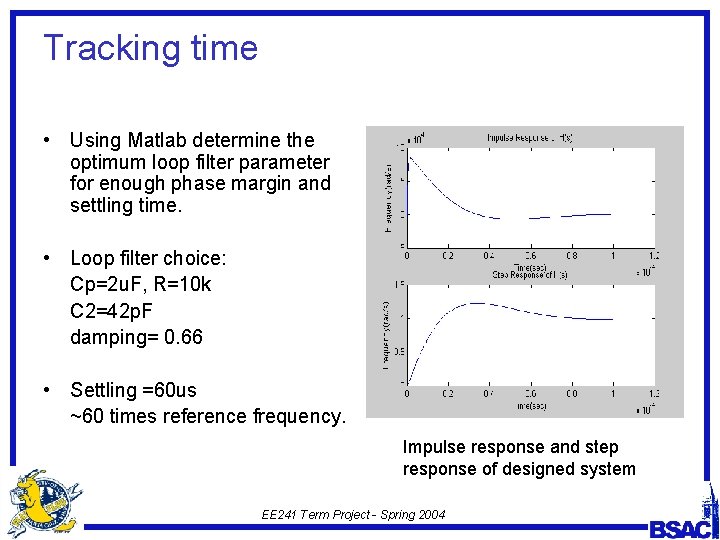

Tracking time • Using Matlab determine the optimum loop filter parameter for enough phase margin and settling time. • Loop filter choice: Cp=2 u. F, R=10 k C 2=42 p. F damping= 0. 66 • Settling =60 us ~60 times reference frequency. Impulse response and step response of designed system EE 241 Term Project - Spring 2004

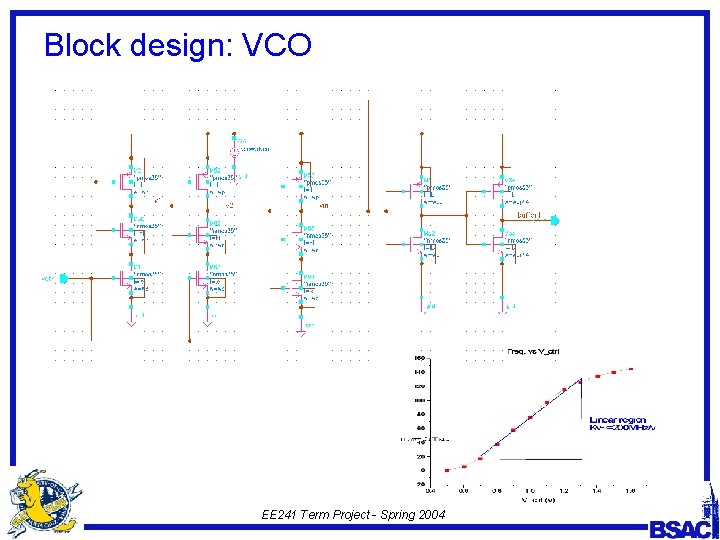

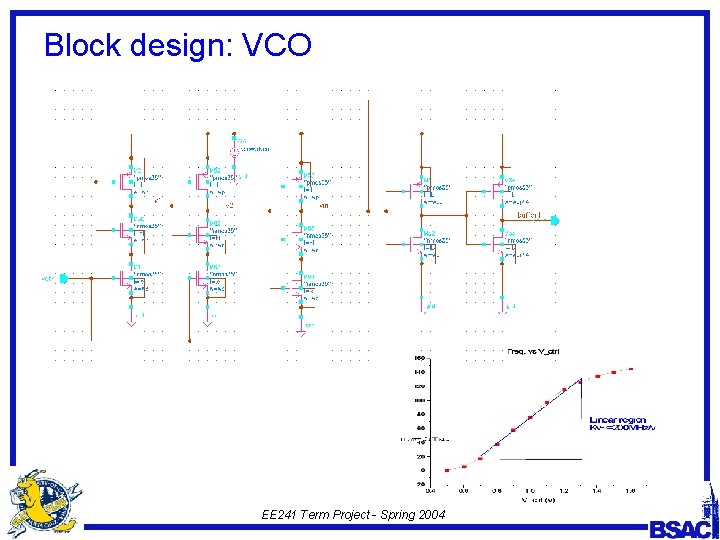

Block design: VCO EE 241 Term Project - Spring 2004

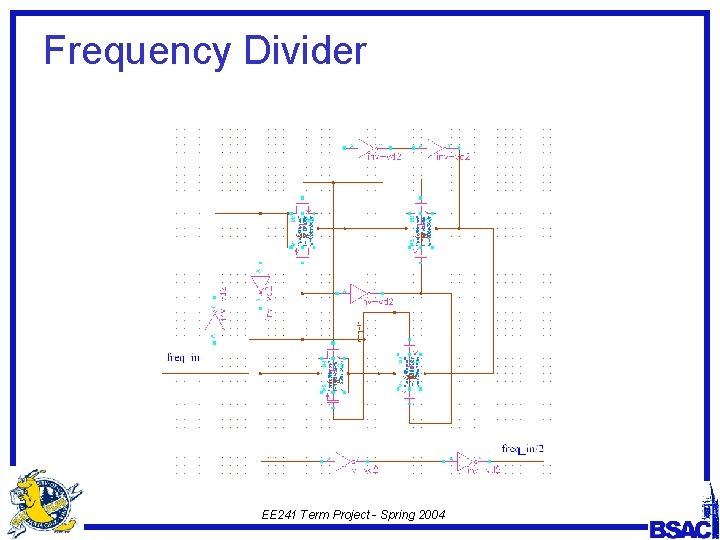

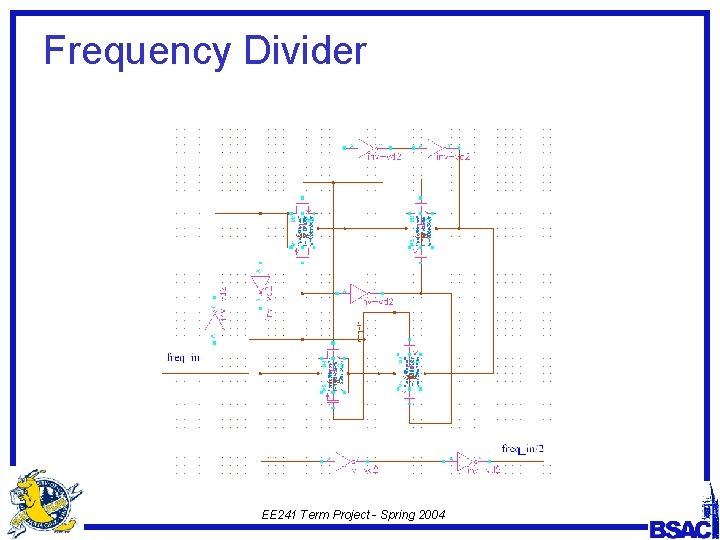

Frequency Divider EE 241 Term Project - Spring 2004

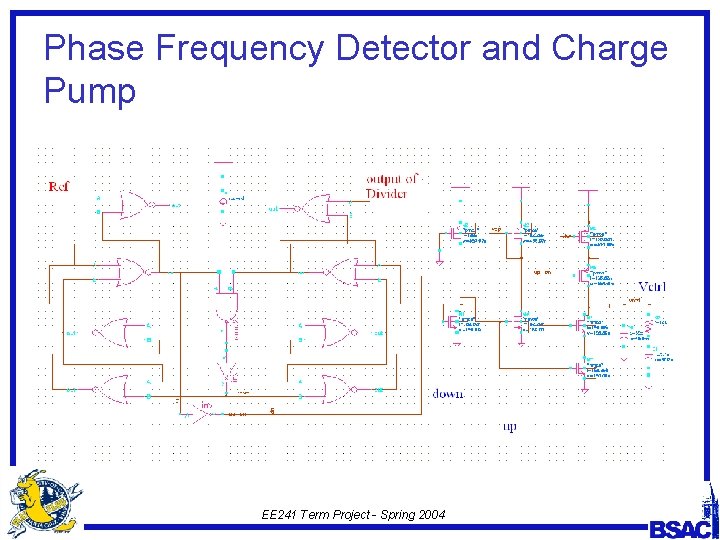

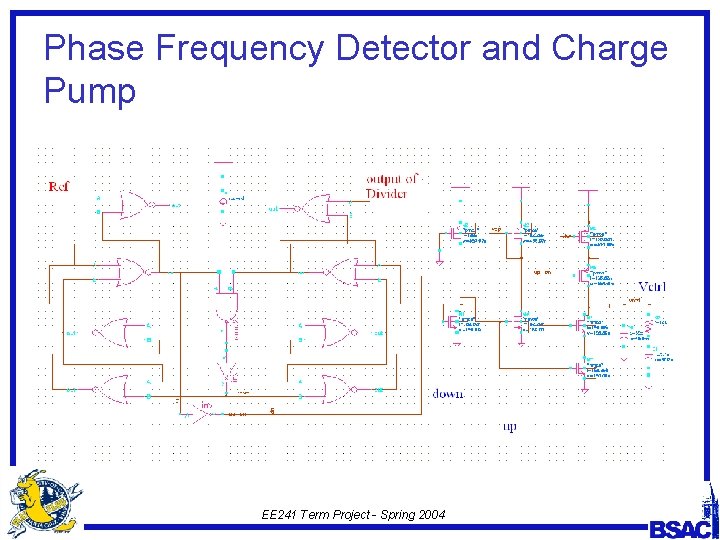

Phase Frequency Detector and Charge Pump EE 241 Term Project - Spring 2004

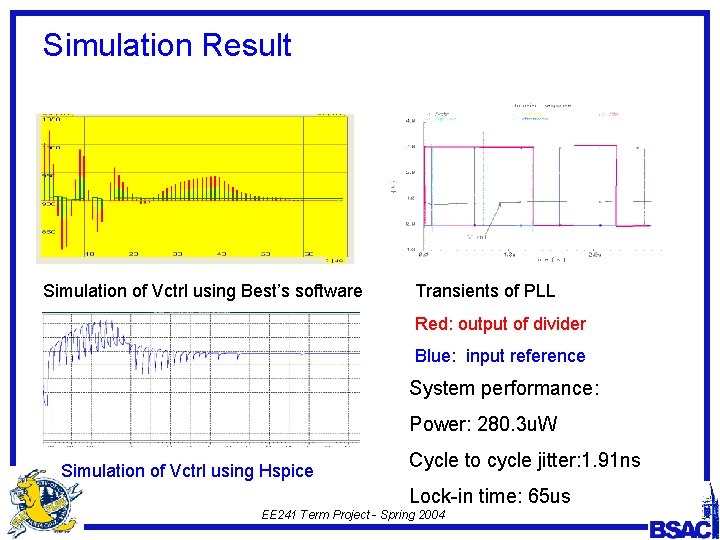

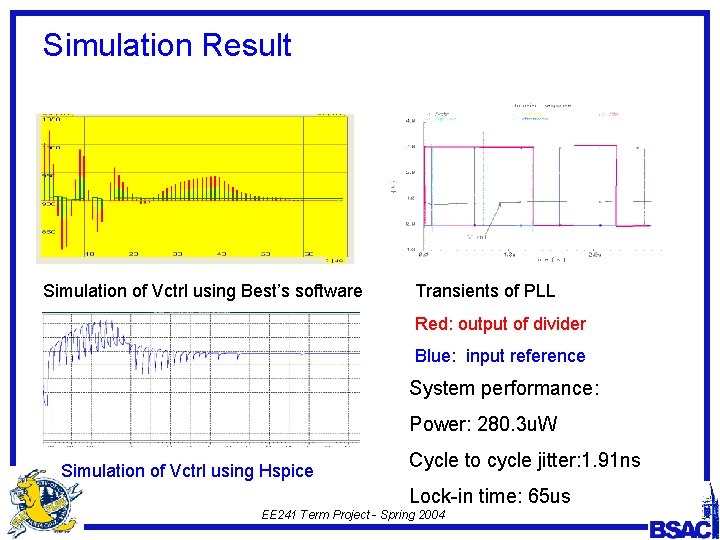

Simulation Result Simulation of Vctrl using Best’s software Transients of PLL Red: output of divider Blue: input reference System performance: Power: 280. 3 u. W Simulation of Vctrl using Hspice Cycle to cycle jitter: 1. 91 ns Lock-in time: 65 us EE 241 Term Project - Spring 2004

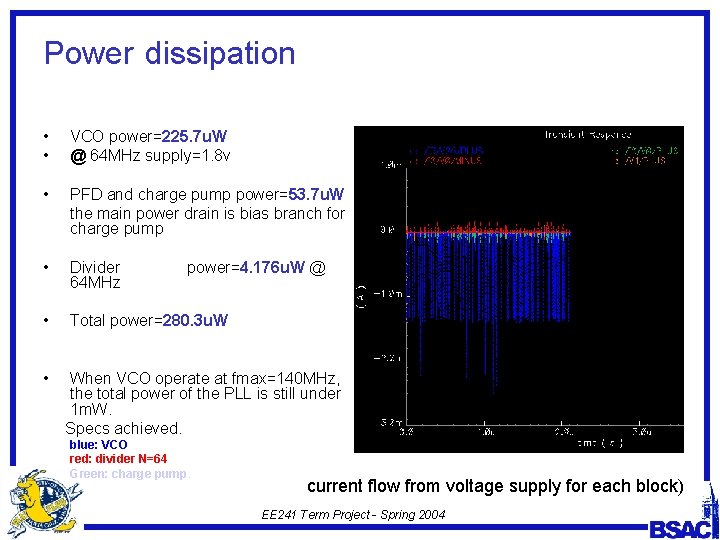

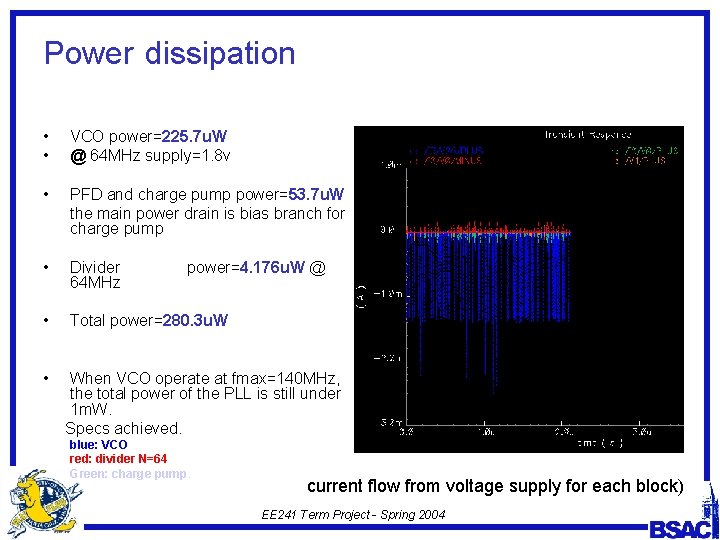

Power dissipation • • VCO power=225. 7 u. W @ 64 MHz supply=1. 8 v • PFD and charge pump power=53. 7 u. W the main power drain is bias branch for charge pump • Divider 64 MHz • Total power=280. 3 u. W • power=4. 176 u. W @ When VCO operate at fmax=140 MHz, the total power of the PLL is still under 1 m. W. Specs achieved. blue: VCO red: divider N=64 Green: charge pump. current flow from voltage supply for each block) EE 241 Term Project - Spring 2004

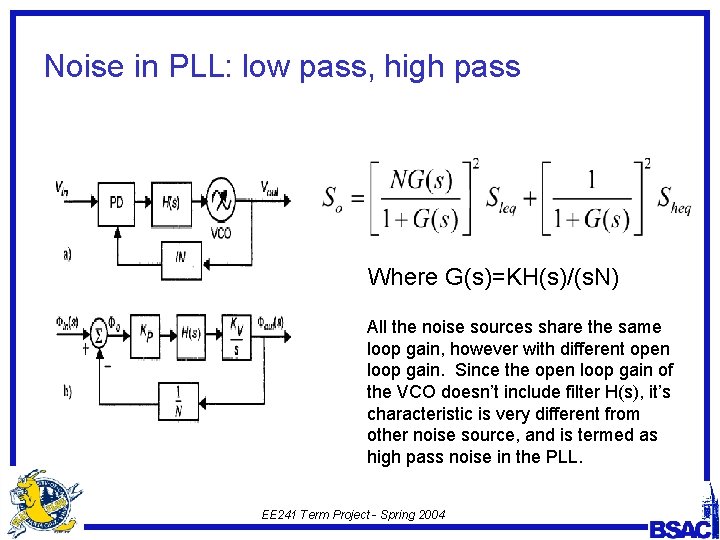

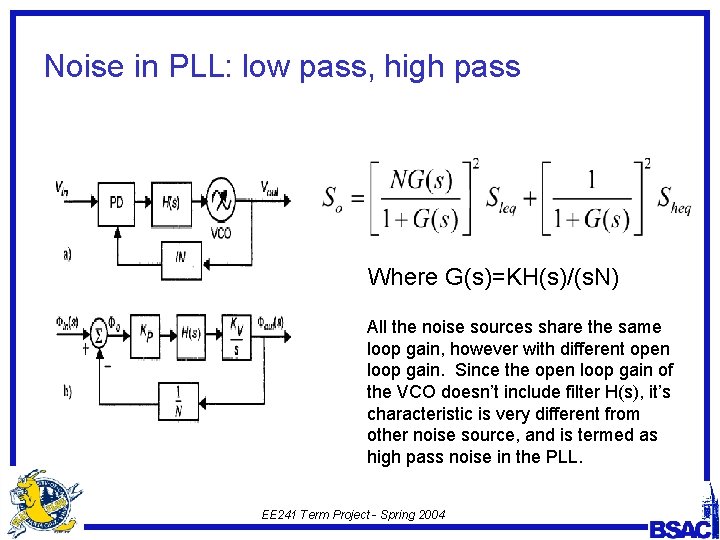

Noise in PLL: low pass, high pass Where G(s)=KH(s)/(s. N) All the noise sources share the same loop gain, however with different open loop gain. Since the open loop gain of the VCO doesn’t include filter H(s), it’s characteristic is very different from other noise source, and is termed as high pass noise in the PLL. EE 241 Term Project - Spring 2004

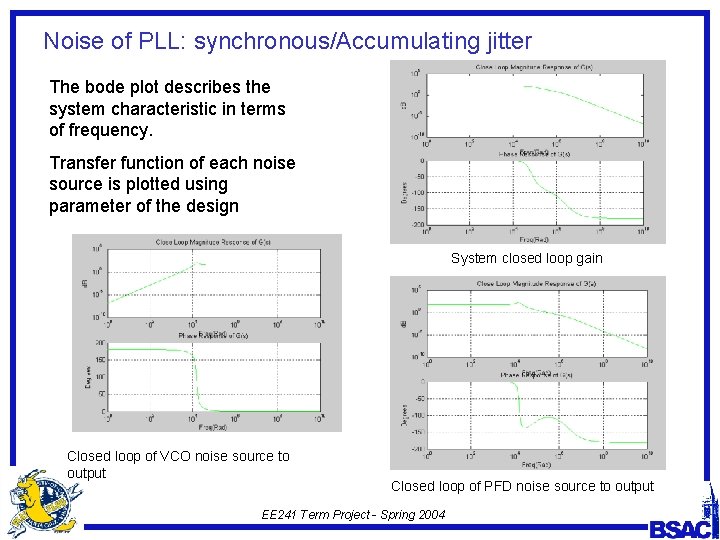

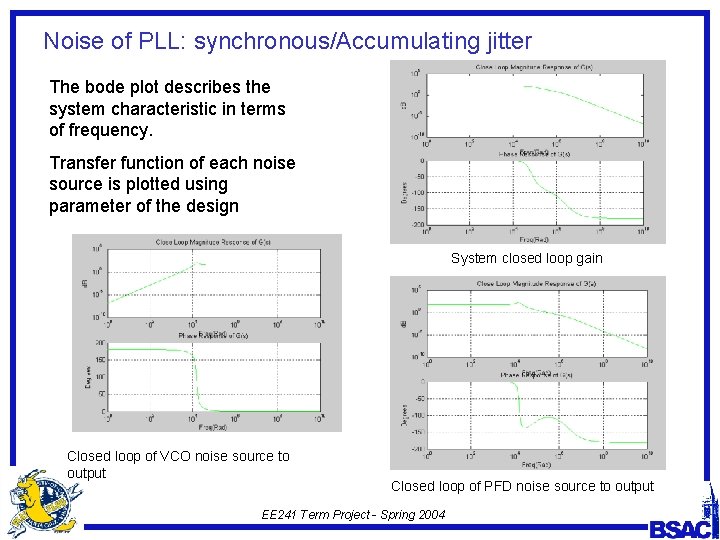

Noise of PLL: synchronous/Accumulating jitter The bode plot describes the system characteristic in terms of frequency. Transfer function of each noise source is plotted using parameter of the design System closed loop gain Closed loop of VCO noise source to output Closed loop of PFD noise source to output EE 241 Term Project - Spring 2004

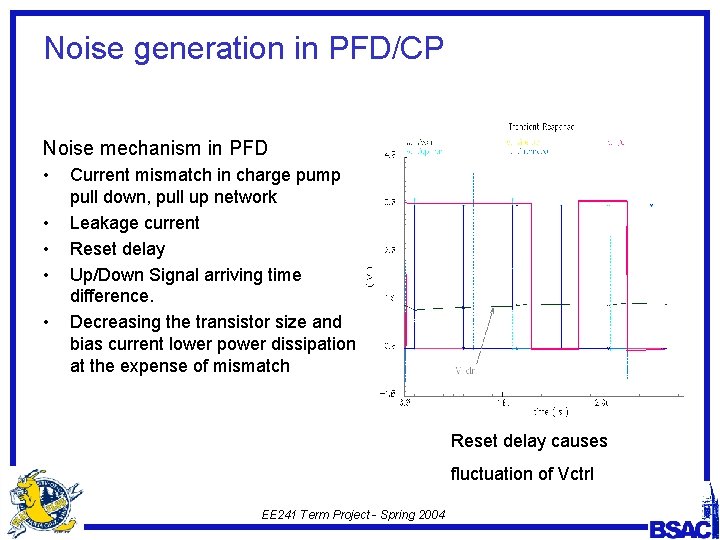

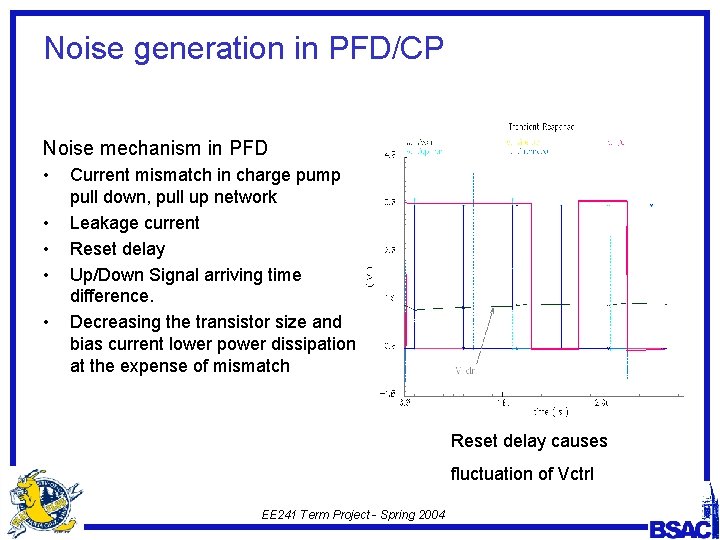

Noise generation in PFD/CP Noise mechanism in PFD • • • Current mismatch in charge pump pull down, pull up network Leakage current Reset delay Up/Down Signal arriving time difference. Decreasing the transistor size and bias current lower power dissipation at the expense of mismatch Reset delay causes fluctuation of Vctrl EE 241 Term Project - Spring 2004

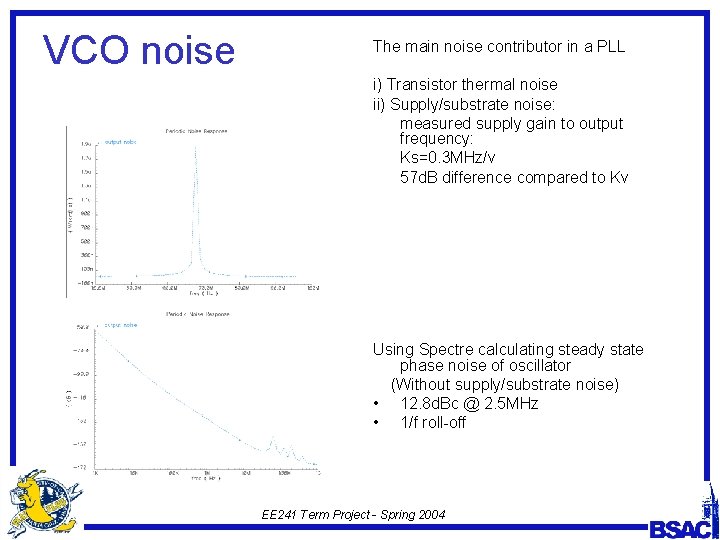

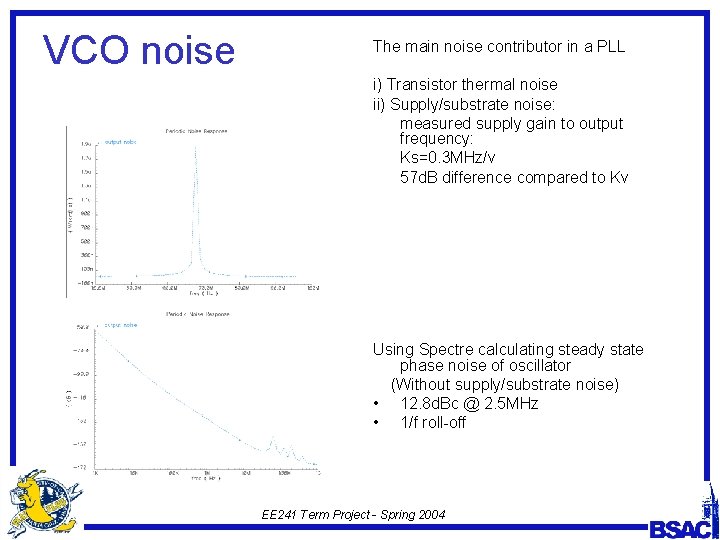

VCO noise The main noise contributor in a PLL i) Transistor thermal noise ii) Supply/substrate noise: measured supply gain to output frequency: Ks=0. 3 MHz/v 57 d. B difference compared to Kv Using Spectre calculating steady state phase noise of oscillator (Without supply/substrate noise) • 12. 8 d. Bc @ 2. 5 MHz • 1/f roll-off EE 241 Term Project - Spring 2004

Conclusions • Don’t even think about all-digital PLL (ADPLL) if you want very low-power operation • A novel low-power and low noise VCO design would be very attractive (e. g. MEMS? ) EE 241 Term Project - Spring 2004