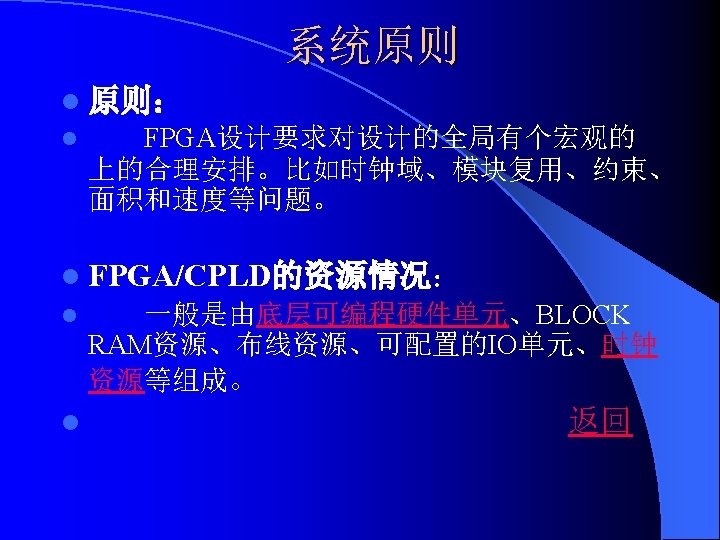

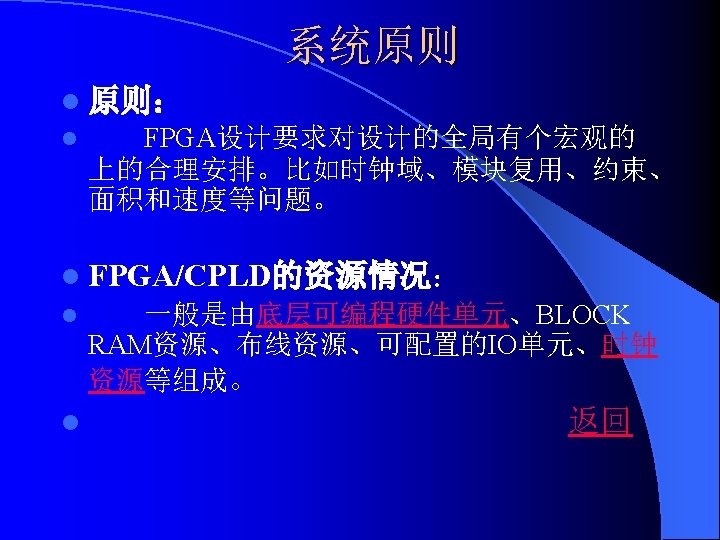

FPGA Loop PLL l DelayLocked Loop DLL l

- Slides: 24

FPGA设计

时钟资源 Loop, PLL) l 延迟锁定环(Delay-Locked Loop, DLL) l 锁相环(Phase-Locked l 返回

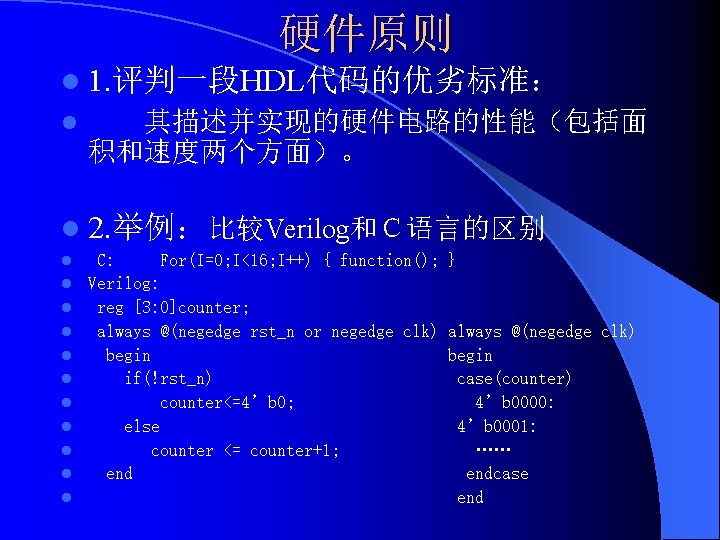

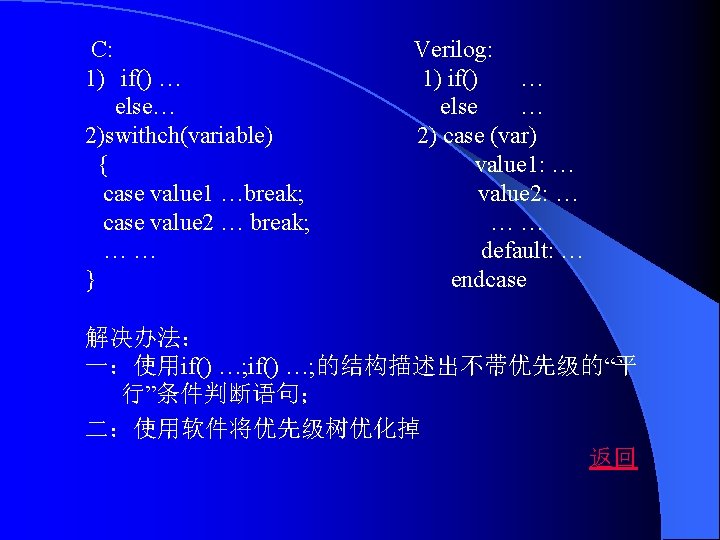

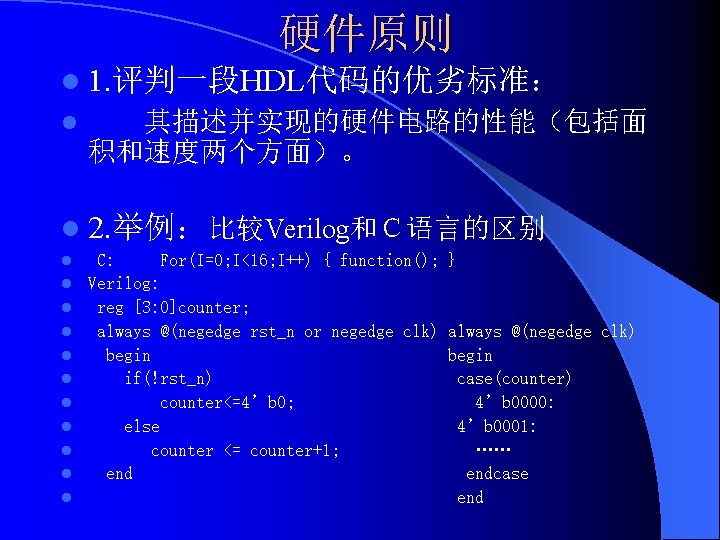

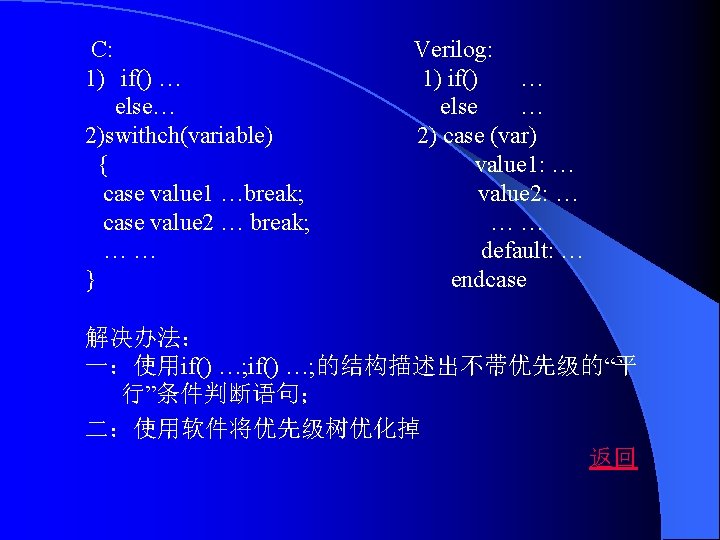

硬件原则 l 1. 评判一段HDL代码的优劣标准: l 其描述并实现的硬件电路的性能(包括面 积和速度两个方面)。 l 2. 举例:比较Verilog和C语言的区别 l l l C: For(I=0; I<16; I++) { function(); Verilog: reg [3: 0]counter; always @(negedge rst_n or negedge clk) begin if(!rst_n) counter<=4’b 0; else counter <= counter+1; end } always @(negedge clk) begin case(counter) 4’b 0000: 4’b 0001: …… endcase end

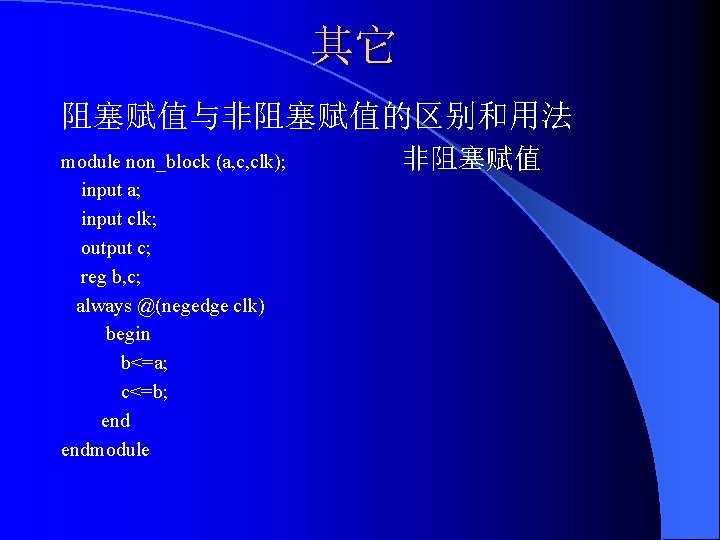

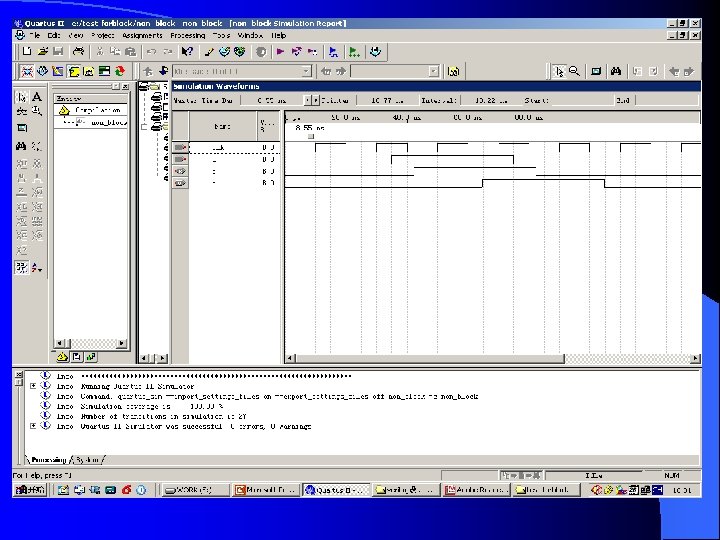

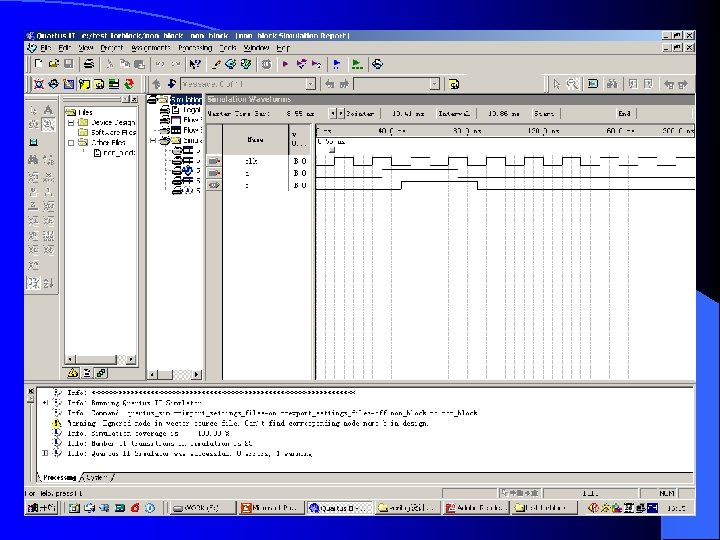

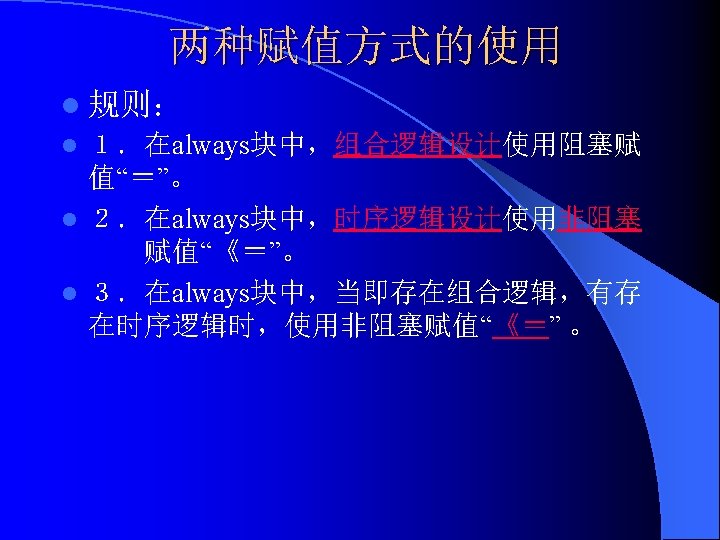

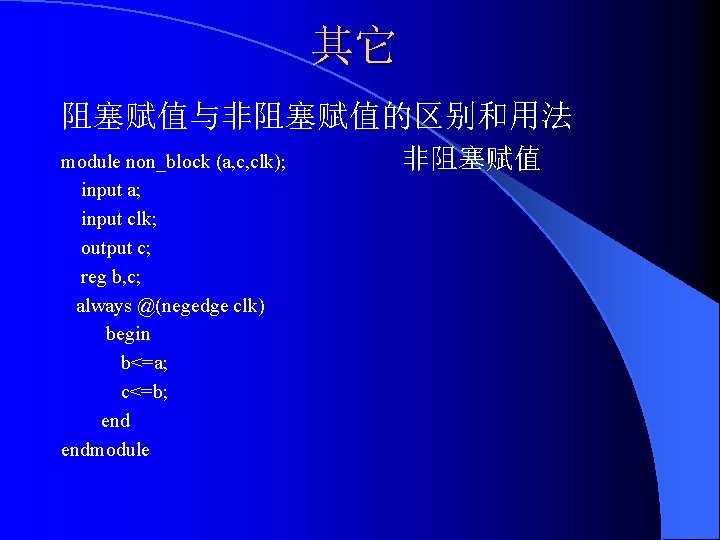

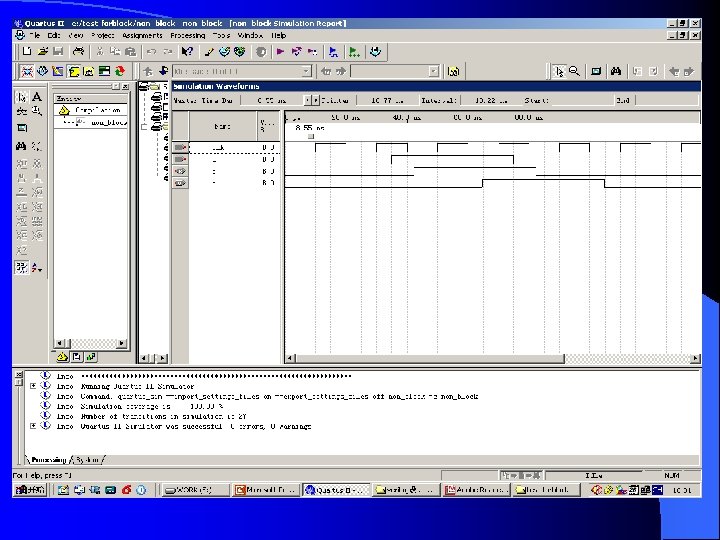

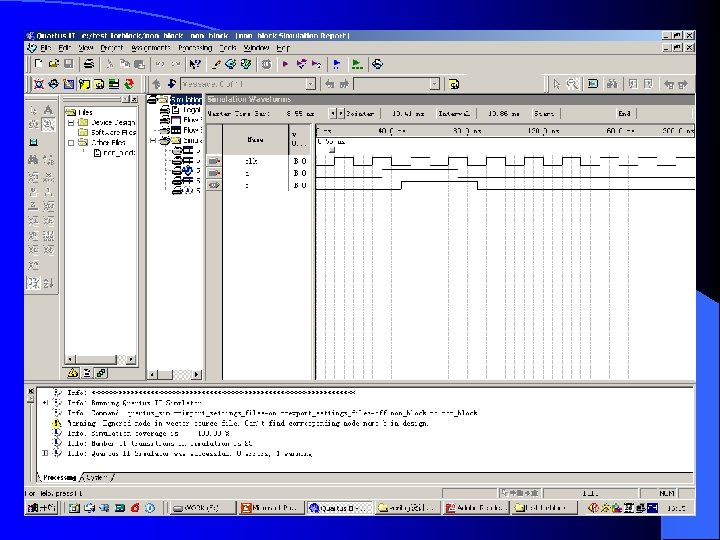

其它 阻塞赋值与非阻塞赋值的区别和用法 module non_block (a, c, clk); input a; input clk; output c; reg b, c; always @(negedge clk) begin b<=a; c<=b; endmodule 非阻塞赋值

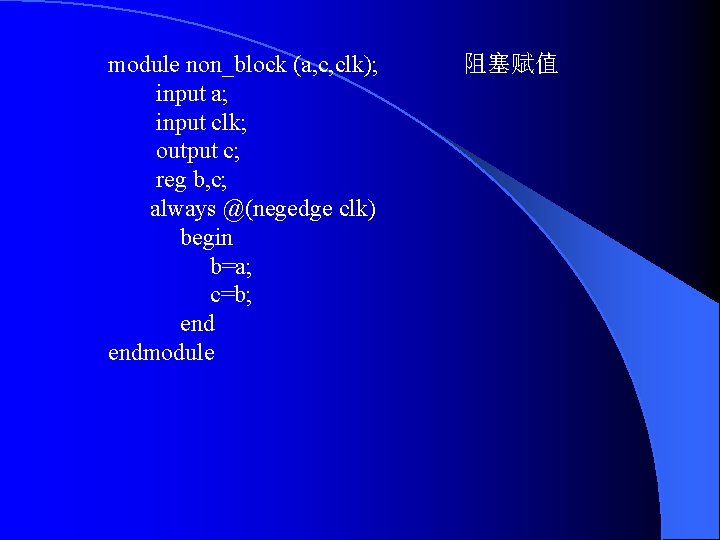

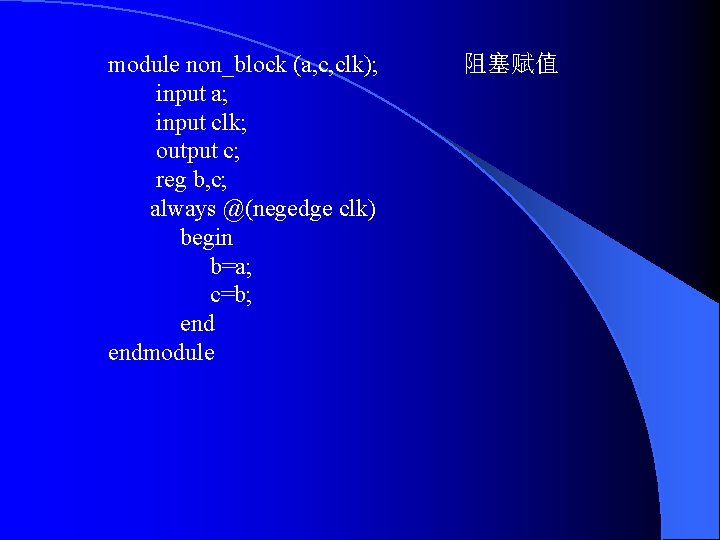

module non_block (a, c, clk); input a; input clk; output c; reg b, c; always @(negedge clk) begin b=a; c=b; endmodule 阻塞赋值

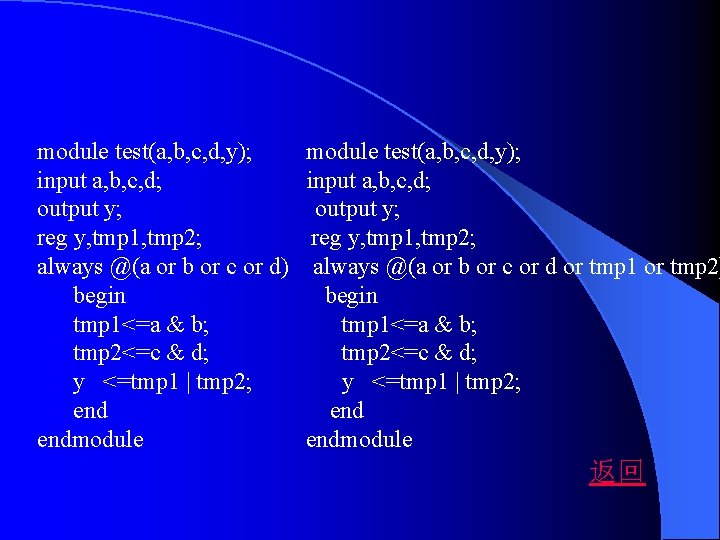

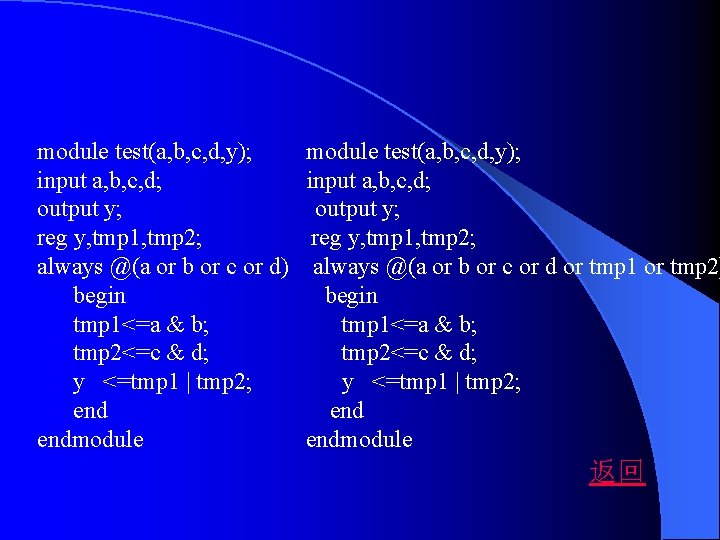

module test(a, b, c, d, y); input a, b, c, d; output y; output y; reg y, tmp 1, tmp 2; always @(a or b or c or d) always @(a or b or c or d or tmp 1 or tmp 2) begin tmp 1<=a & b; tmp 2<=c & d; y <=tmp 1 | tmp 2; end endmodule 返回

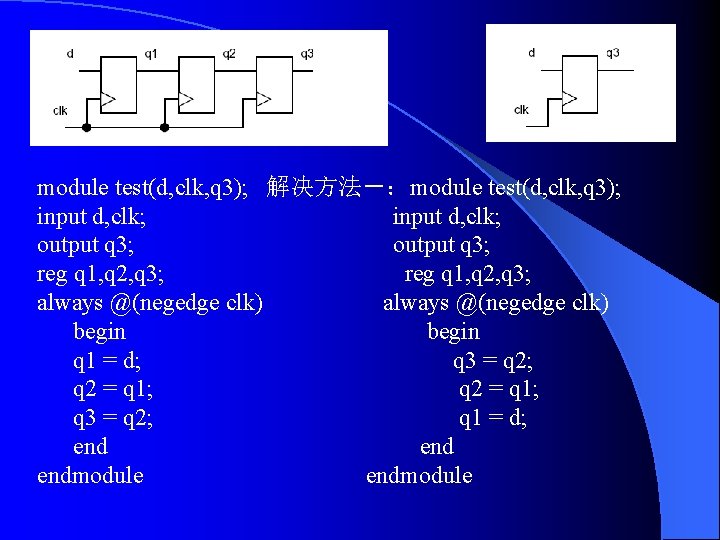

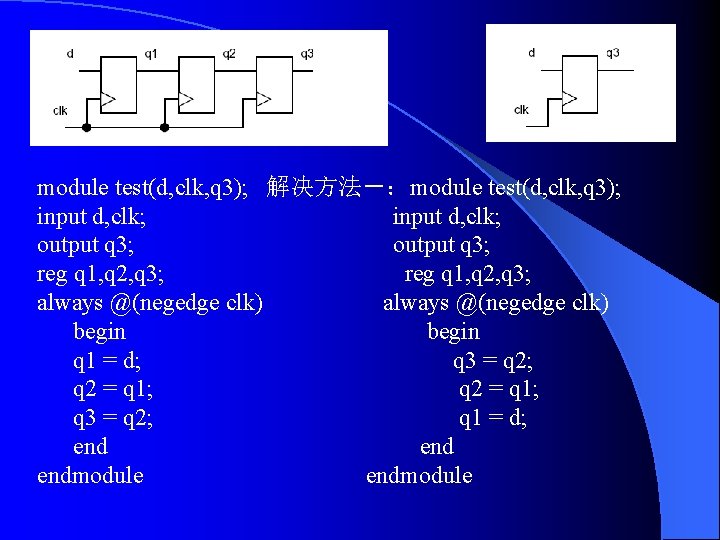

module test(d, clk, q 3); 解决方法-:module test(d, clk, q 3); input d, clk; input d, clk; output q 3; output q 3; reg q 1, q 2, q 3; reg q 1, q 2, q 3; always @(negedge clk) always @(negedge clk) begin begin q 1 = d; q 3 = q 2; q 2 = q 1; q 2 = q 1; q 3 = q 2; q 1 = d; end endmodule endmodule

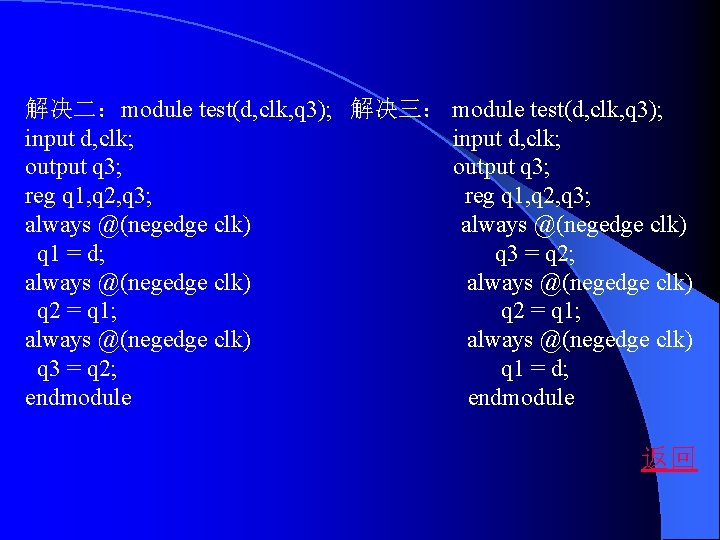

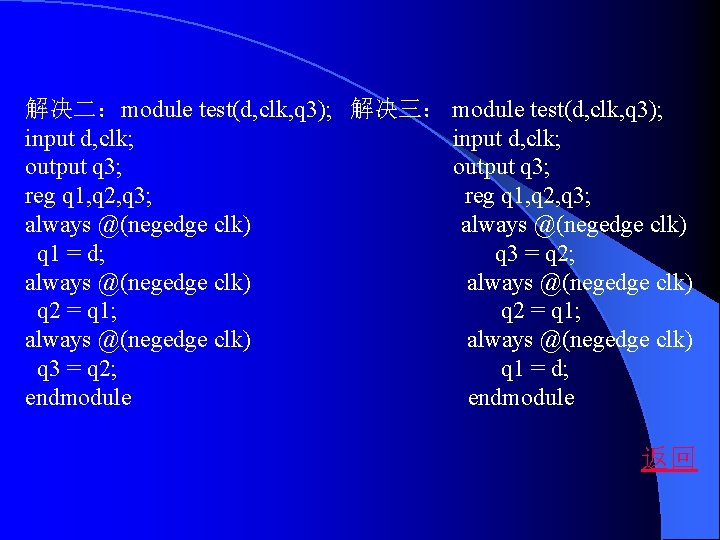

解决二:module test(d, clk, q 3); 解决三: module test(d, clk, q 3); input d, clk; input d, clk; output q 3; output q 3; reg q 1, q 2, q 3; reg q 1, q 2, q 3; always @(negedge clk) always @(negedge clk) q 1 = d; q 3 = q 2; always @(negedge clk) always @(negedge clk) q 2 = q 1; q 2 = q 1; always @(negedge clk) always @(negedge clk) q 3 = q 2; q 1 = d; endmodule 返回

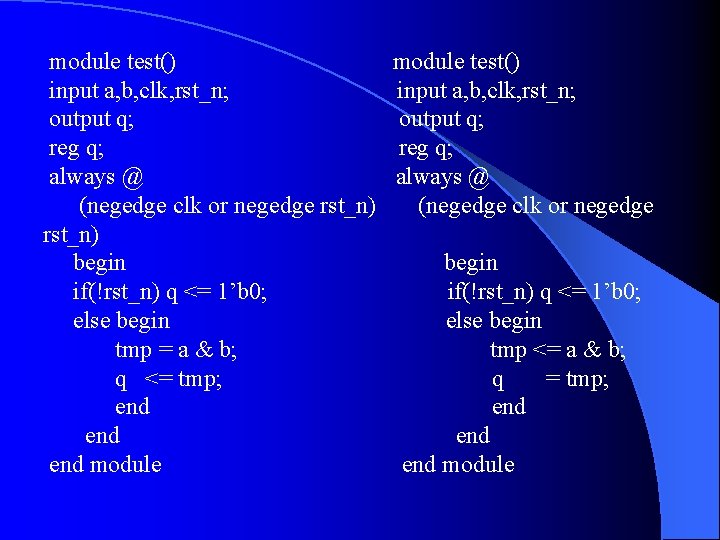

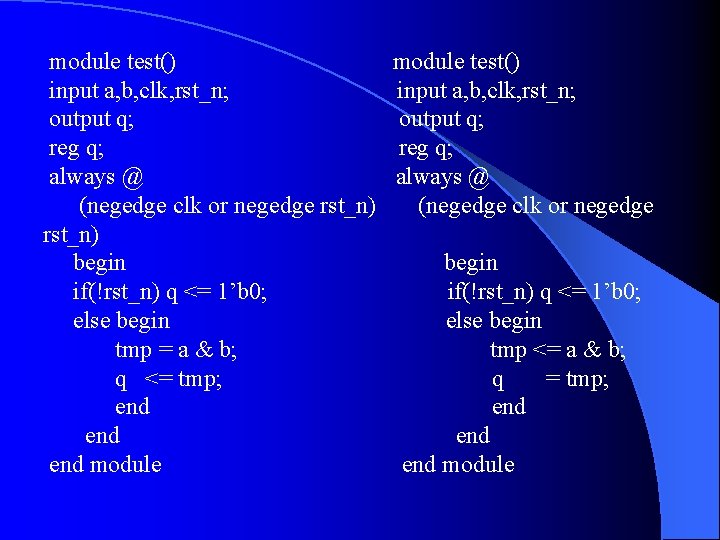

module test() input a, b, clk, rst_n; output q; reg q; always @ (negedge clk or negedge rst_n) begin if(!rst_n) q <= 1’b 0; else begin tmp = a & b; q <= tmp; end end module test() input a, b, clk, rst_n; output q; reg q; always @ (negedge clk or negedge begin if(!rst_n) q <= 1’b 0; else begin tmp <= a & b; q = tmp; end end module