Test System Architecture for AOCS Testing S SudhakarGroup

- Slides: 32

Test System Architecture for AOCS Testing S Sudhakar-Group Head, CDEG, ISAC/ISRO Email: sudhakar@isac. gov. in FSW-2015 John Hopkins Applied Physics Lab, Maryland, USA October 2015

Agenda Test System Architecture for AOCS Testing • Introduction • AOCS Test Requirements • Architecture • Design of Various Features • Summary October 2015 2

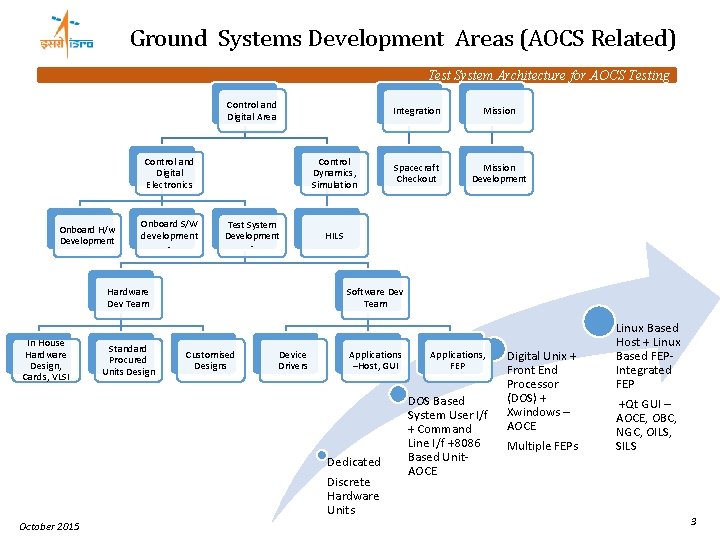

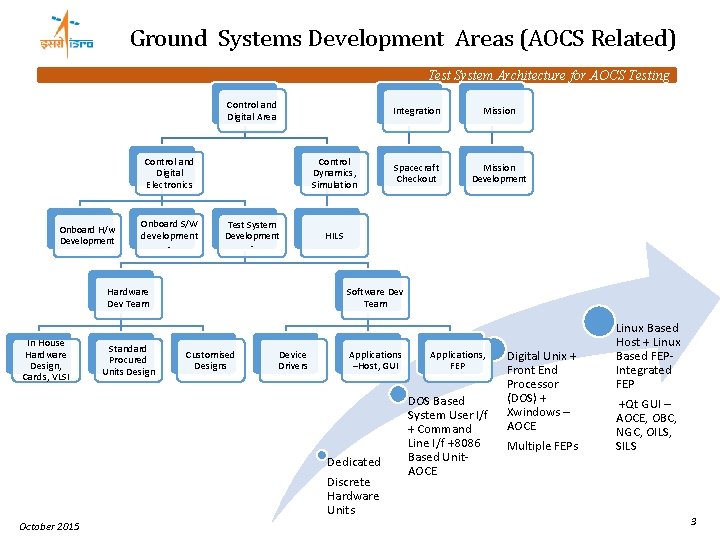

Ground Systems Development Areas (AOCS Related) Test System Architecture for AOCS Testing Control and Digital Area Control and Digital Electronics Onboard H/w Development Onboard S/W development - Control Dynamics, Simulation Test System Development - Hardware Dev Team In House Hardware Design, Cards, VLSI Standard Procured Units Design Mission Spacecraft Checkout Mission Development HILS Software Dev Team Customised Designs Device Drivers Applications –Host, GUI Dedicated Discrete Hardware Units October 2015 Integration Applications, FEP DOS Based System User I/f + Command Line I/f +8086 Based Unit. AOCE Digital Unix + Front End Processor (DOS) + Xwindows – AOCE Multiple FEPs Linux Based Host + Linux Based FEPIntegrated FEP +Qt GUI – AOCE, OBC, NGC, OILS, SILS 3

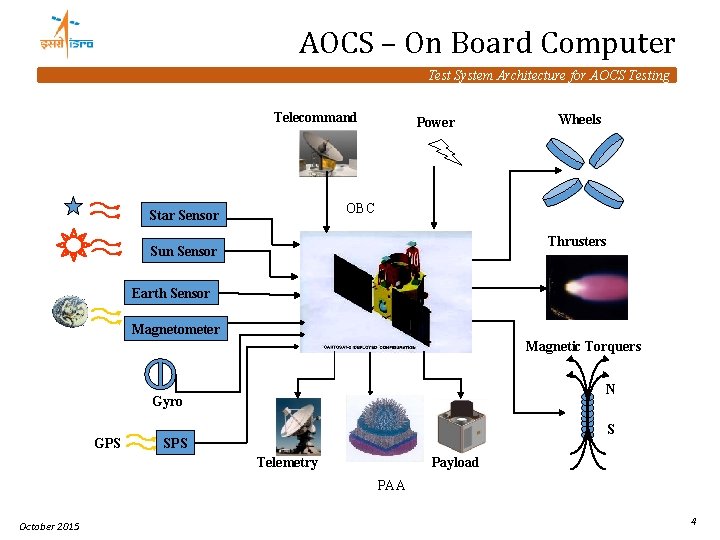

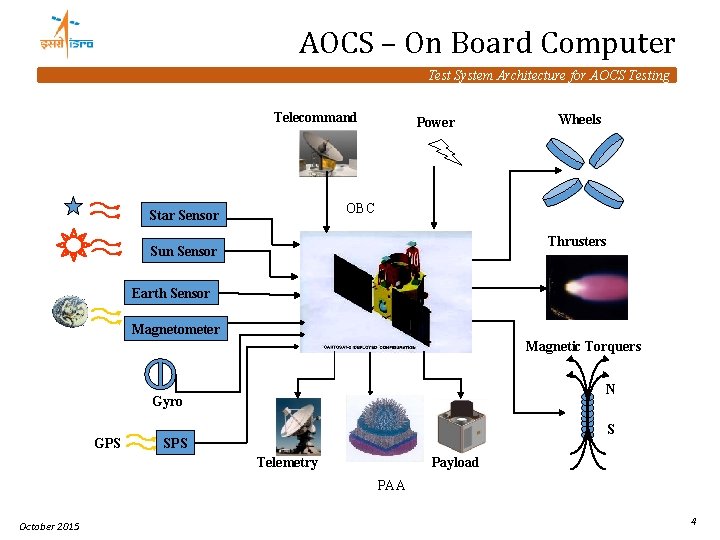

AOCS – On Board Computer Test System Architecture for AOCS Testing Telecommand Power Wheels OBC Star Sensor Thrusters Sun Sensor Earth Sensor Magnetometer Magnetic Torquers N Gyro GPS S SPS Payload Telemetry PAA October 2015 4

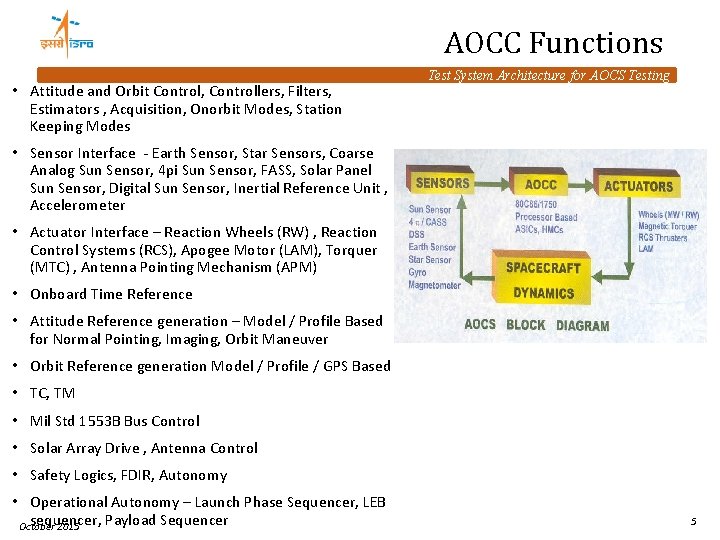

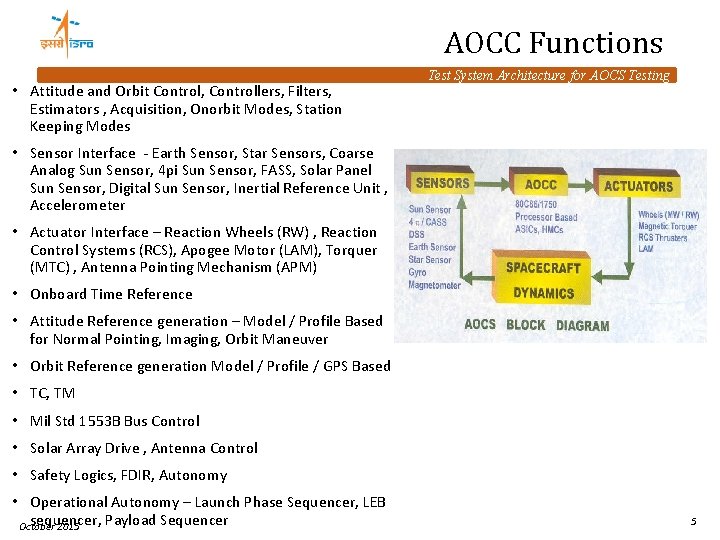

AOCC Functions • Attitude and Orbit Control, Controllers, Filters, Estimators , Acquisition, Onorbit Modes, Station Keeping Modes Test System Architecture for AOCS Testing • Sensor Interface - Earth Sensor, Star Sensors, Coarse Analog Sun Sensor, 4 pi Sun Sensor, FASS, Solar Panel Sun Sensor, Digital Sun Sensor, Inertial Reference Unit , Accelerometer • Actuator Interface – Reaction Wheels (RW) , Reaction Control Systems (RCS), Apogee Motor (LAM), Torquer (MTC) , Antenna Pointing Mechanism (APM) • Onboard Time Reference • Attitude Reference generation – Model / Profile Based for Normal Pointing, Imaging, Orbit Maneuver • Orbit Reference generation Model / Profile / GPS Based • TC, TM • Mil Std 1553 B Bus Control • Solar Array Drive , Antenna Control • Safety Logics, FDIR, Autonomy • Operational Autonomy – Launch Phase Sequencer, LEB sequencer, Payload Sequencer October 2015 5

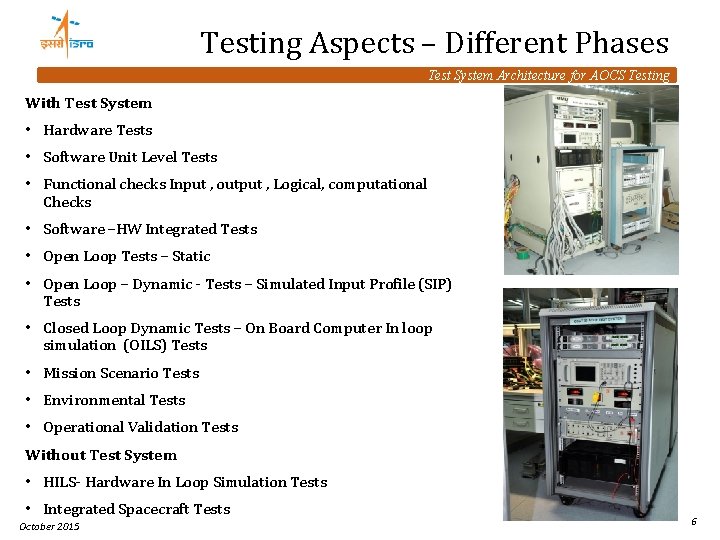

Testing Aspects – Different Phases Test System Architecture for AOCS Testing With Test System • Hardware Tests • Software Unit Level Tests • Functional checks Input , output , Logical, computational Checks • Software –HW Integrated Tests • Open Loop Tests – Static • Open Loop – Dynamic - Tests – Simulated Input Profile (SIP) Tests • Closed Loop Dynamic Tests – On Board Computer In loop simulation (OILS) Tests • Mission Scenario Tests • Environmental Tests • Operational Validation Tests Without Test System • HILS- Hardware In Loop Simulation Tests • Integrated Spacecraft Tests October 2015 6

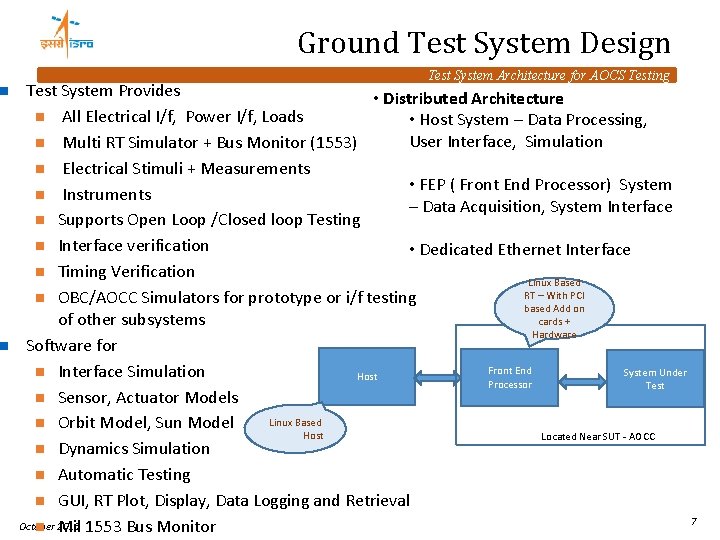

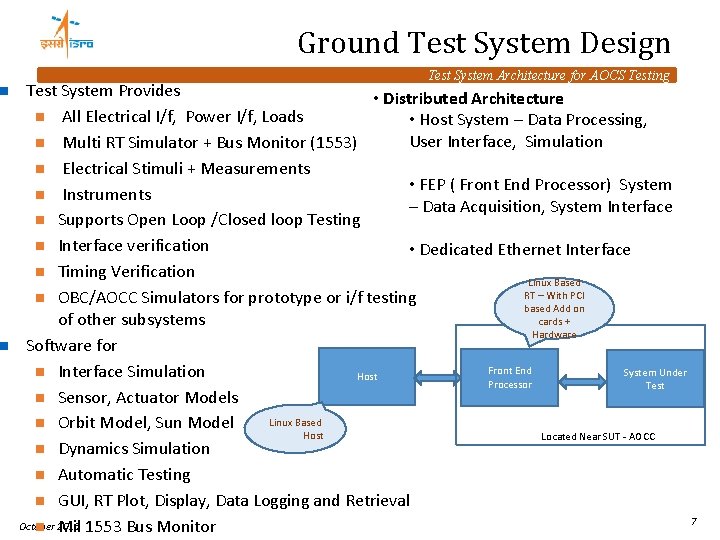

n n Ground Test System Design Test System Architecture for AOCS Testing Test System Provides • Distributed Architecture n All Electrical I/f, Power I/f, Loads • Host System – Data Processing, User Interface, Simulation n Multi RT Simulator + Bus Monitor (1553) n Electrical Stimuli + Measurements • FEP ( Front End Processor) System n Instruments – Data Acquisition, System Interface n Supports Open Loop /Closed loop Testing n Interface verification • Dedicated Ethernet Interface n Timing Verification Linux Based RT – With PCI n OBC/AOCC Simulators for prototype or i/f testing based Add on of other subsystems cards + Hardware Software for Front End System Under n Interface Simulation Host Processor Test n Sensor, Actuator Models Linux Based n Orbit Model, Sun Model Host Located Near SUT - AOCC n Dynamics Simulation n Automatic Testing n GUI, RT Plot, Display, Data Logging and Retrieval 7 October n 2015 Mil 1553 Bus Monitor

Ground Test System Elements Test System Architecture for AOCS Testing October 2015 8

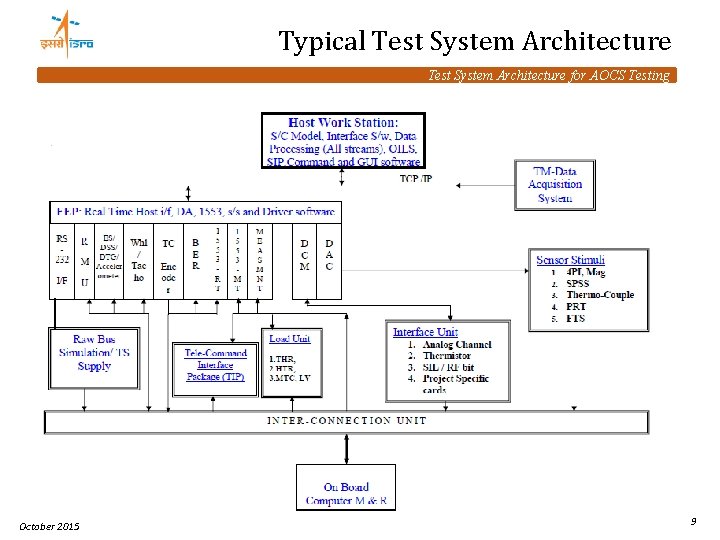

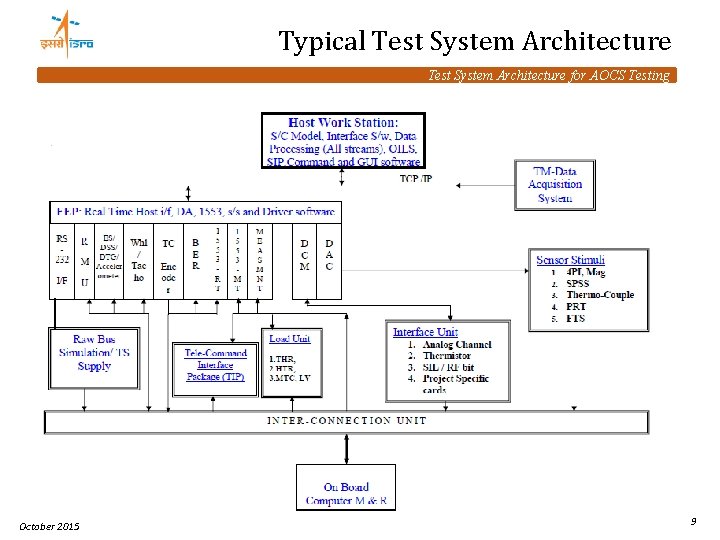

Typical Test System Architecture for AOCS Testing October 2015 9

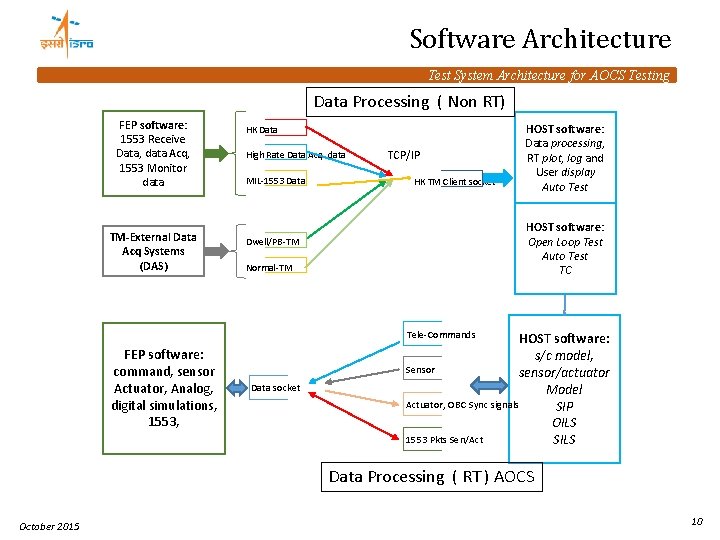

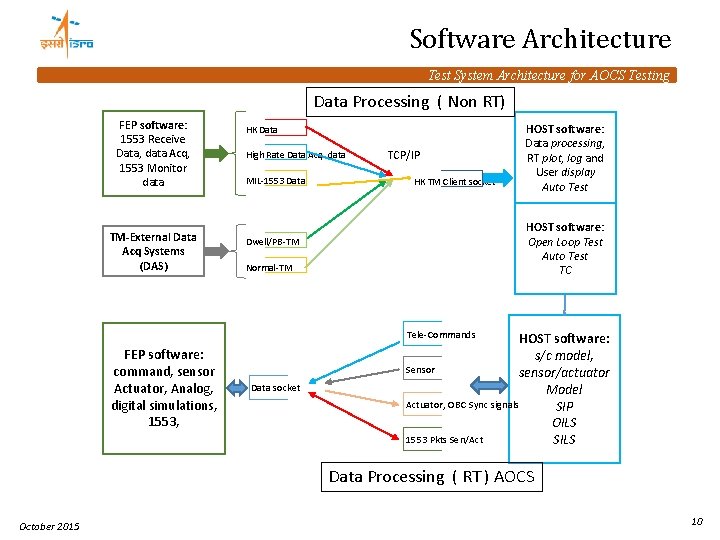

Software Architecture Test System Architecture for AOCS Testing Data Processing ( Non RT) FEP software: 1553 Receive Data, data Acq, 1553 Monitor data TM-External Data Acq Systems (DAS) HK Data High Rate Data Acq data MIL-1553 Data TCP/IP HK TM Client socket HOST software: Data processing, RT plot, log and User display Auto Test HOST software: Open Loop Test Auto Test TC Dwell/PB-TM Normal-TM Tele-Commands FEP software: command, sensor Actuator, Analog, digital simulations, 1553, Data socket HOST software: s/c model, Sensor sensor/actuator Model Actuator, OBC Sync signals SIP OILS 1553 Pkts Sen/Act SILS Data Processing ( RT ) AOCS October 2015 10

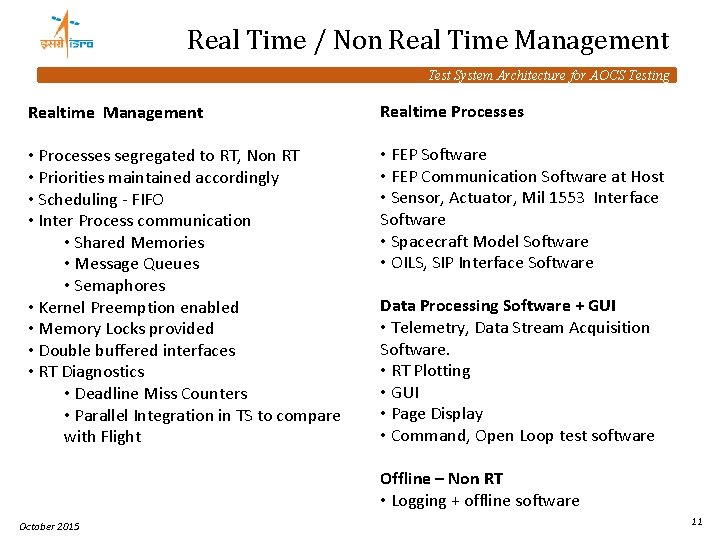

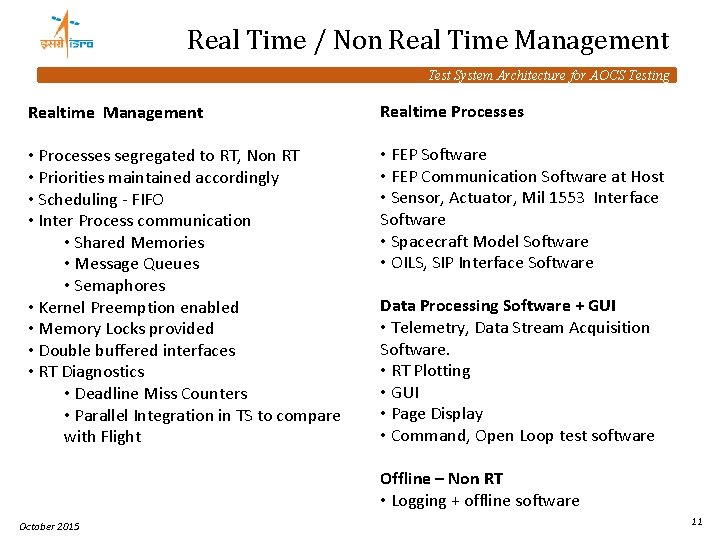

Real Time / Non Real Time Management Test System Architecture for AOCS Testing Realtime Management Realtime Processes • Processes segregated to RT, Non RT • Priorities maintained accordingly • Scheduling - FIFO • Inter Process communication • Shared Memories • Message Queues • Semaphores • Kernel Preemption enabled • Memory Locks provided • Double buffered interfaces • RT Diagnostics • Deadline Miss Counters • Parallel Integration in TS to compare with Flight • FEP Software • FEP Communication Software at Host • Sensor, Actuator, Mil 1553 Interface Software • Spacecraft Model Software • OILS, SIP Interface Software Data Processing Software + GUI • Telemetry, Data Stream Acquisition Software. • RT Plotting • GUI • Page Display • Command, Open Loop test software Offline – Non RT • Logging + offline software October 2015 11

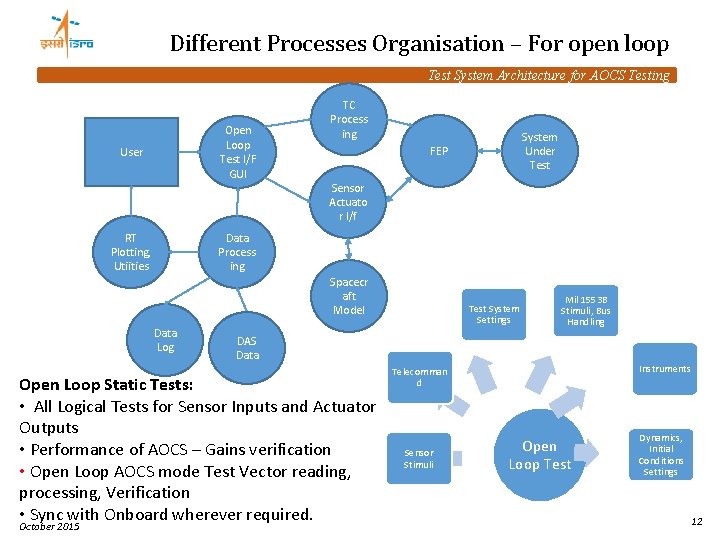

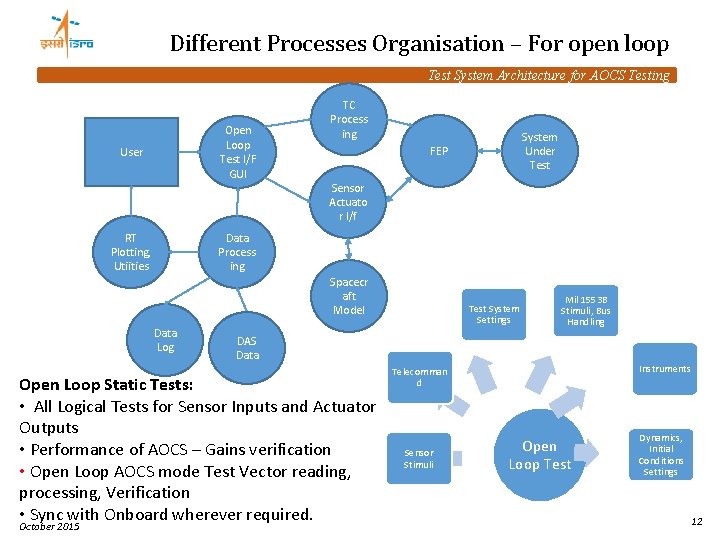

Different Processes Organisation – For open loop Test System Architecture for AOCS Testing Open Loop Test I/F GUI User RT Plotting, Utiities TC Process ing Sensor Actuato r I/f Data Process ing Spacecr aft Model Data Log Test System Settings Mil 1553 B Stimuli, Bus Handling DAS Data Open Loop Static Tests: • All Logical Tests for Sensor Inputs and Actuator Outputs • Performance of AOCS – Gains verification • Open Loop AOCS mode Test Vector reading, processing, Verification • Sync with Onboard wherever required. October 2015 System Under Test FEP Instruments Telecomman d Sensor Stimuli Open Loop Test Dynamics, Initial Conditions Settings 12

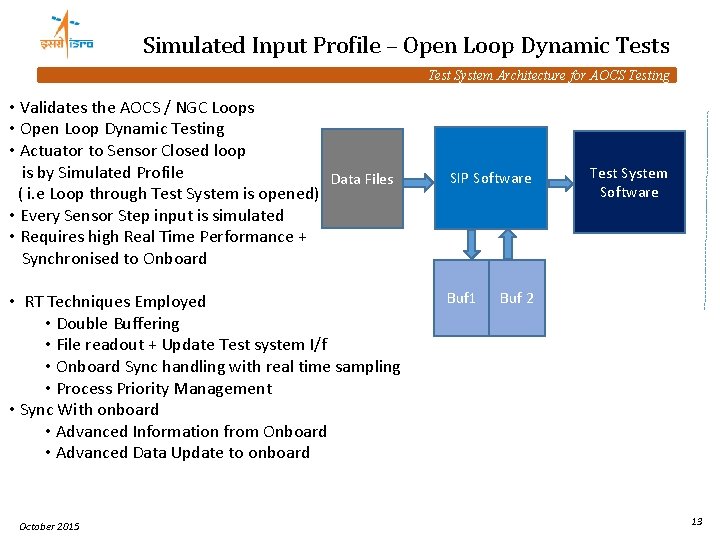

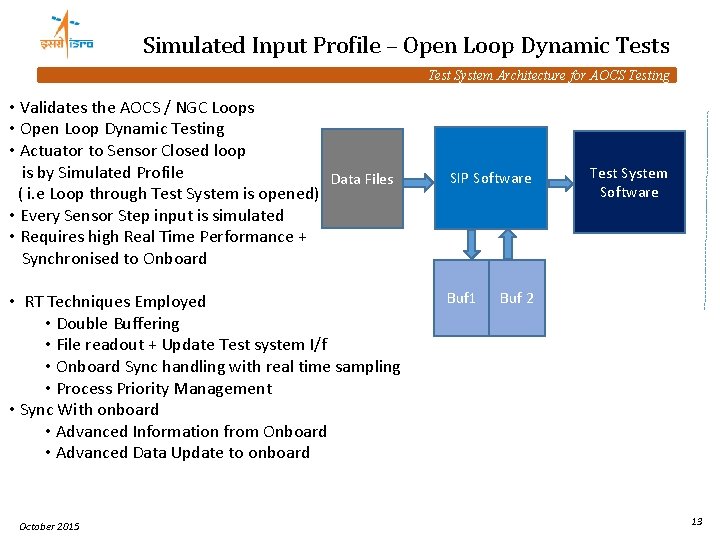

Simulated Input Profile – Open Loop Dynamic Tests Test System Architecture for AOCS Testing • Validates the AOCS / NGC Loops • Open Loop Dynamic Testing • Actuator to Sensor Closed loop is by Simulated Profile Data Files ( i. e Loop through Test System is opened) • Every Sensor Step input is simulated • Requires high Real Time Performance + Synchronised to Onboard • RT Techniques Employed • Double Buffering • File readout + Update Test system I/f • Onboard Sync handling with real time sampling • Process Priority Management • Sync With onboard • Advanced Information from Onboard • Advanced Data Update to onboard October 2015 SIP Software Buf 1 Test System Software Buf 2 13

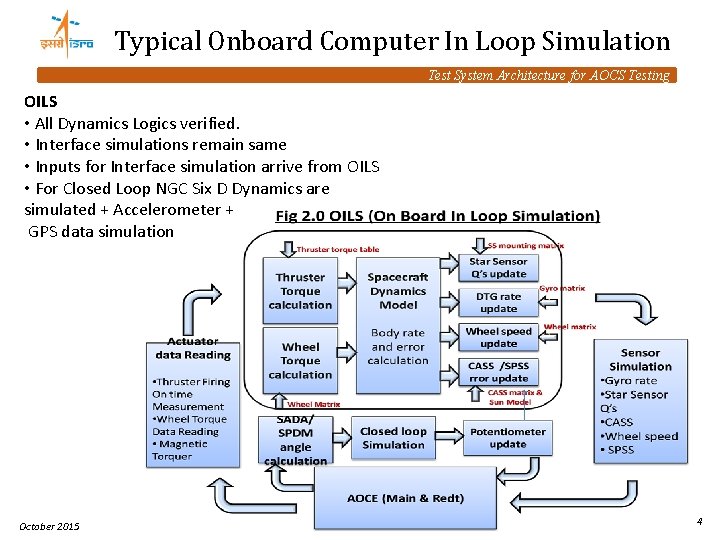

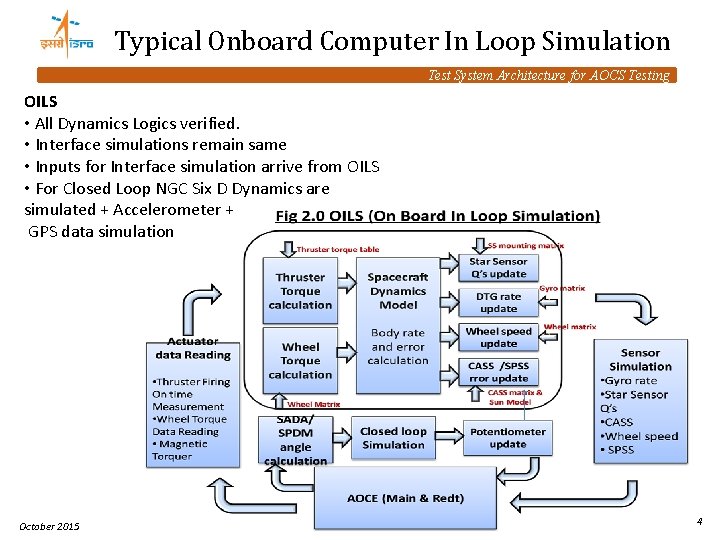

Typical Onboard Computer In Loop Simulation Test System Architecture for AOCS Testing OILS • All Dynamics Logics verified. • Interface simulations remain same • Inputs for Interface simulation arrive from OILS • For Closed Loop NGC Six D Dynamics are simulated + Accelerometer + GPS data simulation October 2015 14

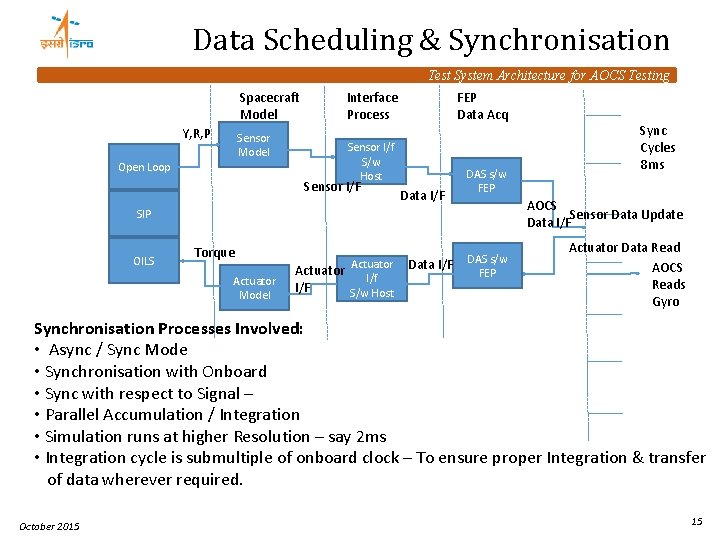

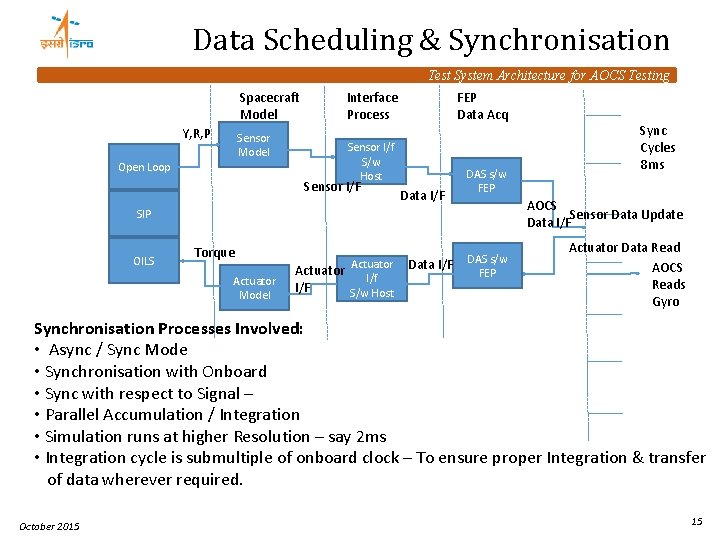

Data Scheduling & Synchronisation Test System Architecture for AOCS Testing Spacecraft Model Y, R, P Sensor Model Open Loop Interface Process FEP Data Acq Sensor I/f S/w Host Sensor I/F Data I/F DAS s/w FEP AOCS Sensor Data Update Data I/F SIP OILS Torque Actuator Model Actuator I/f I/F S/w Host Data I/F Sync Cycles 8 ms DAS s/w FEP Actuator Data Read AOCS Reads Gyro Synchronisation Processes Involved: • Async / Sync Mode • Synchronisation with Onboard • Sync with respect to Signal – • Parallel Accumulation / Integration • Simulation runs at higher Resolution – say 2 ms • Integration cycle is submultiple of onboard clock – To ensure proper Integration & transfer of data wherever required. October 2015 15

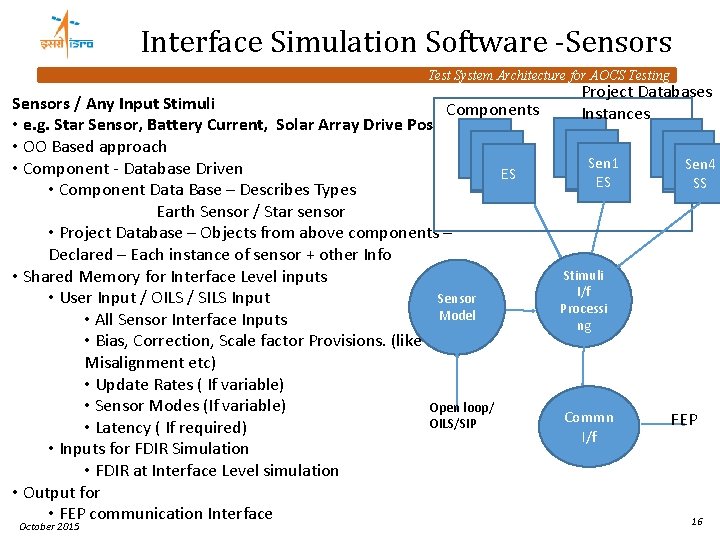

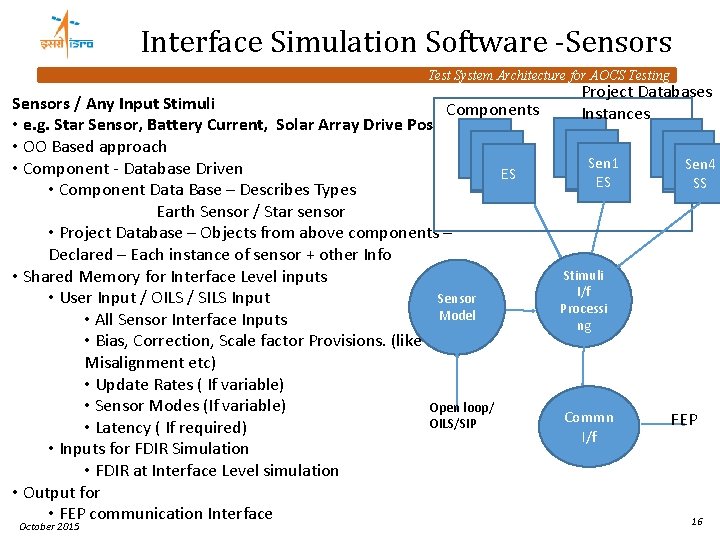

Interface Simulation Software -Sensors Test System Architecture for AOCS Testing Sensors / Any Input Stimuli Components • e. g. Star Sensor, Battery Current, Solar Array Drive Pos • OO Based approach • Component - Database Driven ES • Component Data Base – Describes Types Earth Sensor / Star sensor • Project Database – Objects from above components – Declared – Each instance of sensor + other Info • Shared Memory for Interface Level inputs • User Input / OILS / SILS Input Sensor Model • All Sensor Interface Inputs • Bias, Correction, Scale factor Provisions. (like Drift, Misalignment etc) • Update Rates ( If variable) • Sensor Modes (If variable) Open loop/ OILS/SIP • Latency ( If required) • Inputs for FDIR Simulation • FDIR at Interface Level simulation • Output for • FEP communication Interface October 2015 Project Databases Instances Sen 1 ES Sen 4 SS Stimuli I/f Processi ng Commn I/f FEP 16

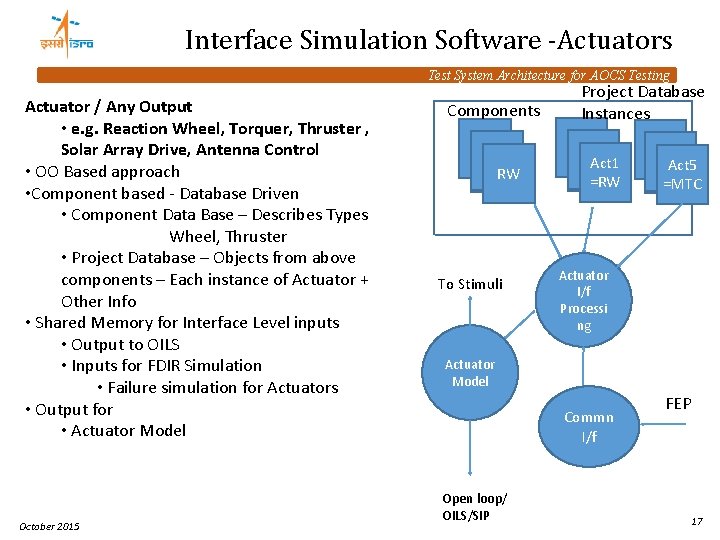

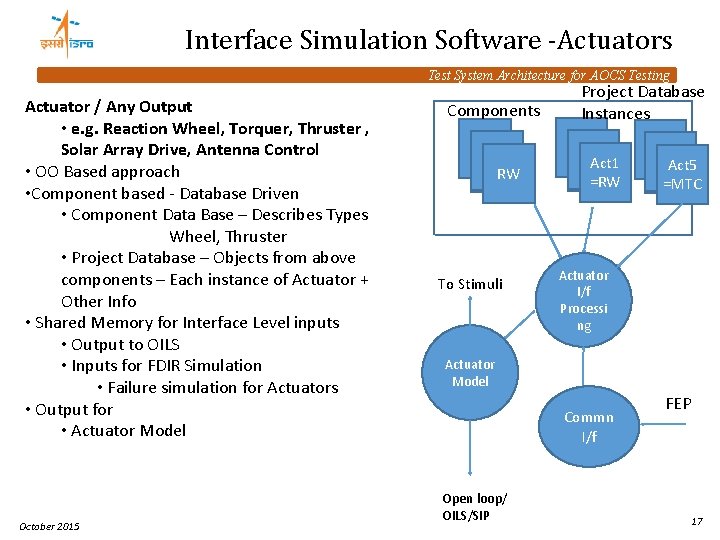

Interface Simulation Software -Actuators Test System Architecture for AOCS Testing Actuator / Any Output • e. g. Reaction Wheel, Torquer, Thruster , Solar Array Drive, Antenna Control • OO Based approach • Component based - Database Driven • Component Data Base – Describes Types Wheel, Thruster • Project Database – Objects from above components – Each instance of Actuator + Other Info • Shared Memory for Interface Level inputs • Output to OILS • Inputs for FDIR Simulation • Failure simulation for Actuators • Output for • Actuator Model October 2015 Components RW To Stimuli Project Database Instances Act 1 =RW Act 5 =MTC Actuator I/f Processi ng Actuator Model Commn I/f Open loop/ OILS/SIP FEP 17

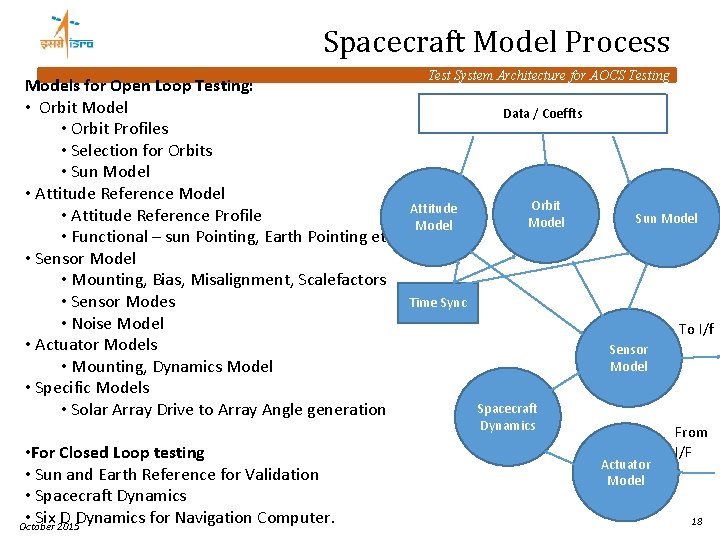

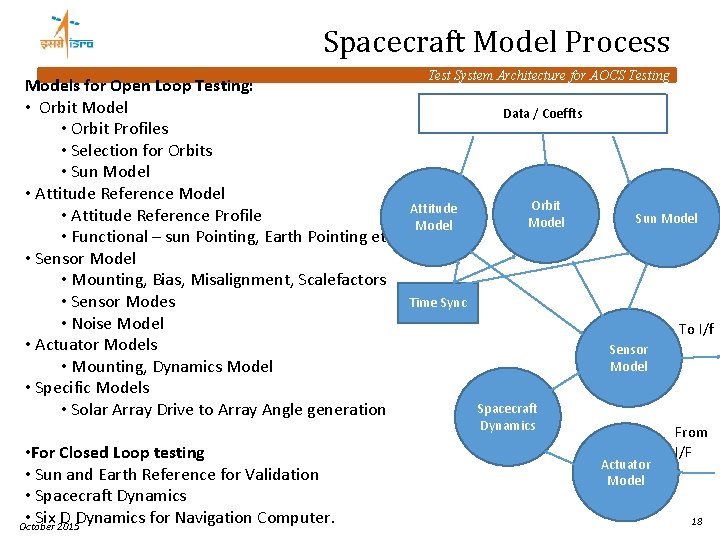

Spacecraft Model Process Models for Open Loop Testing: • Orbit Model • Orbit Profiles • Selection for Orbits • Sun Model • Attitude Reference Profile • Functional – sun Pointing, Earth Pointing etc • Sensor Model • Mounting, Bias, Misalignment, Scalefactors • Sensor Modes • Noise Model • Actuator Models • Mounting, Dynamics Model • Specific Models • Solar Array Drive to Array Angle generation • For Closed Loop testing • Sun and Earth Reference for Validation • Spacecraft Dynamics • Six D Dynamics for Navigation Computer. October 2015 Test System Architecture for AOCS Testing Data / Coeffts Attitude Model Orbit Model Sun Model Time Sync To I/f Sensor Model Spacecraft Dynamics Actuator Model From I/F 18

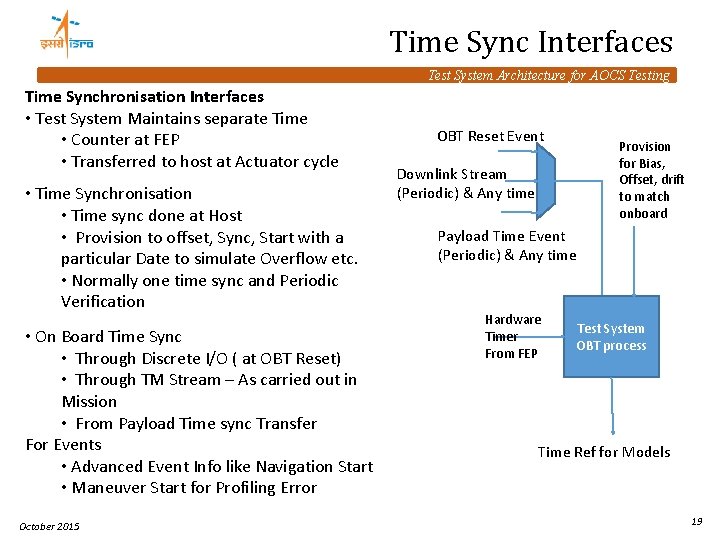

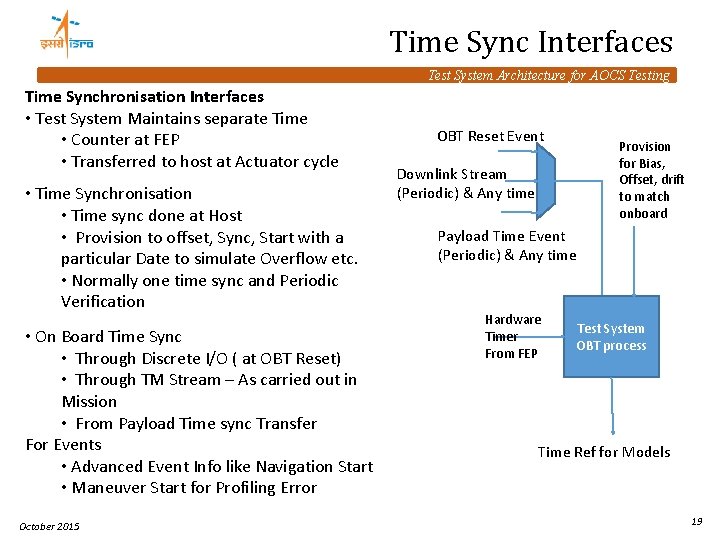

Time Sync Interfaces Test System Architecture for AOCS Testing Time Synchronisation Interfaces • Test System Maintains separate Time • Counter at FEP • Transferred to host at Actuator cycle • Time Synchronisation • Time sync done at Host • Provision to offset, Sync, Start with a particular Date to simulate Overflow etc. • Normally one time sync and Periodic Verification • On Board Time Sync • Through Discrete I/O ( at OBT Reset) • Through TM Stream – As carried out in Mission • From Payload Time sync Transfer For Events • Advanced Event Info like Navigation Start • Maneuver Start for Profiling Error October 2015 OBT Reset Event Provision for Bias, Offset, drift to match onboard Downlink Stream (Periodic) & Any time Payload Time Event (Periodic) & Any time Hardware Timer From FEP Test System OBT process Time Ref for Models 19

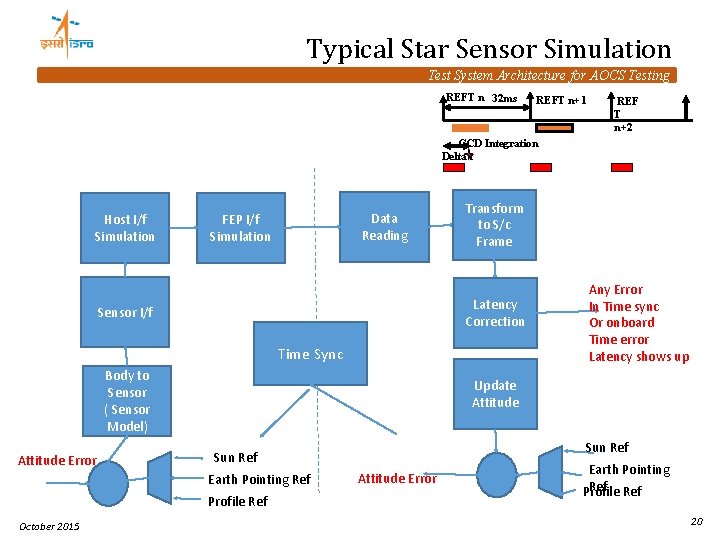

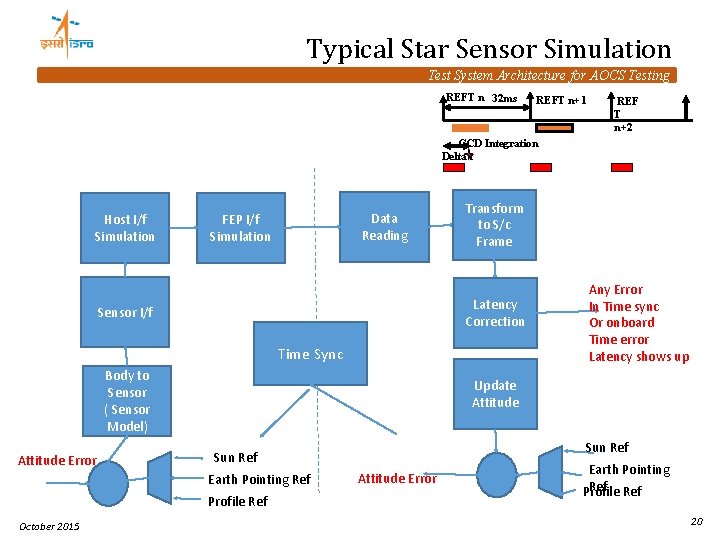

Typical Star Sensor Simulation Test System Architecture for AOCS Testing REFT n 32 ms REFT n+1 REF T n+2 CCD Integration Delta t Host I/f Simulation Data Reading FEP I/f Simulation Transform to S/c Frame Latency Correction Sensor I/f Time Sync Body to Sensor ( Sensor Model) Attitude Error Update Attitude Sun Ref Earth Pointing Ref Profile Ref October 2015 Any Error In Time sync Or onboard Time error Latency shows up Attitude Error Earth Pointing Ref Profile 20

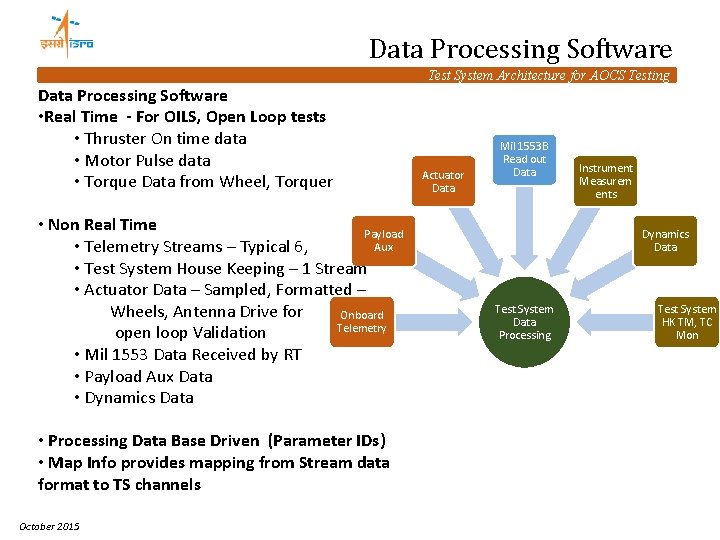

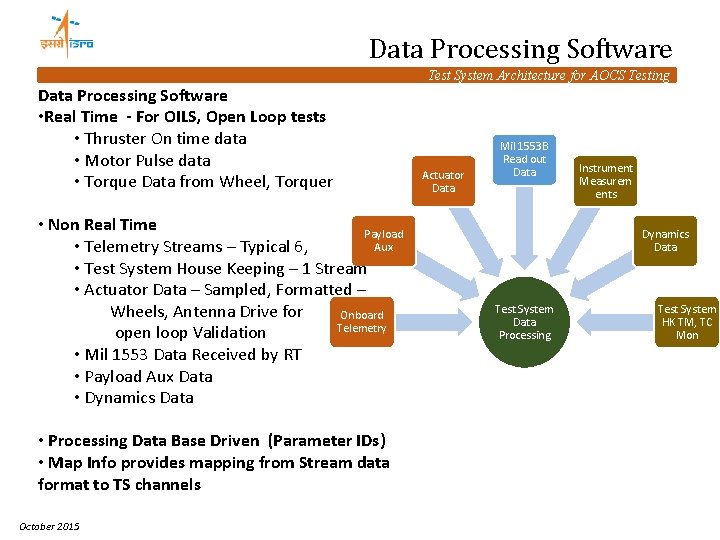

Data Processing Software Test System Architecture for AOCS Testing Data Processing Software • Real Time - For OILS, Open Loop tests • Thruster On time data • Motor Pulse data • Torque Data from Wheel, Torquer • Non Real Time Payload Aux • Telemetry Streams – Typical 6, • Test System House Keeping – 1 Stream • Actuator Data – Sampled, Formatted – Wheels, Antenna Drive for Onboard Telemetry open loop Validation • Mil 1553 Data Received by RT • Payload Aux Data • Dynamics Data • Processing Data Base Driven (Parameter IDs) • Map Info provides mapping from Stream data format to TS channels October 2015 Actuator Data Mil 1553 B Read out Data Instrument Measurem ents Dynamics Data Test System Data Processing Test System HK TM, TC Mon

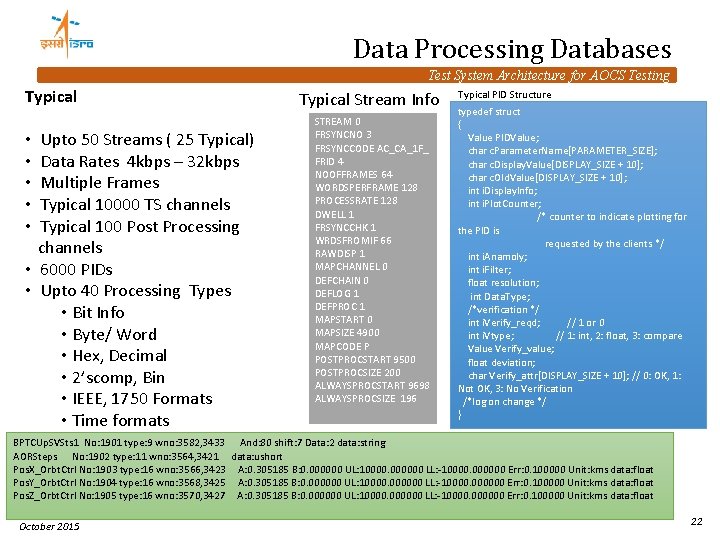

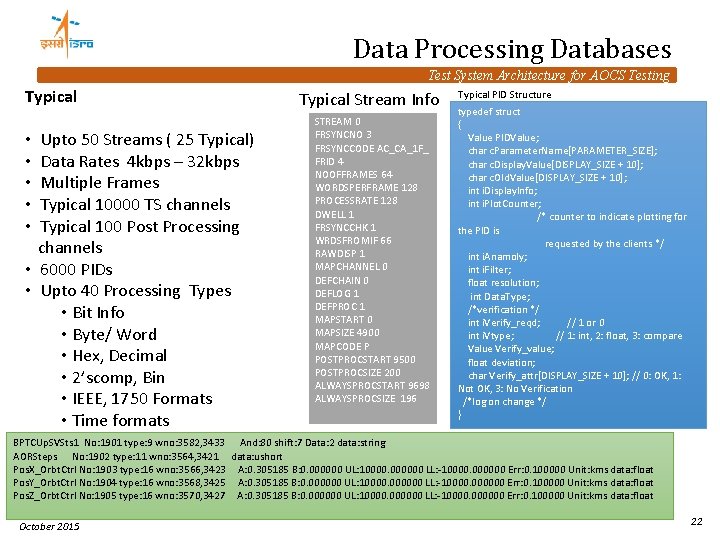

Data Processing Databases Test System Architecture for AOCS Testing Typical Upto 50 Streams ( 25 Typical) Data Rates 4 kbps – 32 kbps Multiple Frames Typical 10000 TS channels Typical 100 Post Processing channels • 6000 PIDs • Upto 40 Processing Types • Bit Info • Byte/ Word • Hex, Decimal • 2’scomp, Bin • IEEE, 1750 Formats • Time formats • • • Typical Stream Info STREAM 0 FRSYNCNO 3 FRSYNCCODE AC_CA_1 F_ FRID 4 NOOFFRAMES 64 WORDSPERFRAME 128 PROCESSRATE 128 DWELL 1 FRSYNCCHK 1 WRDSFROMIF 66 RAWDISP 1 MAPCHANNEL 0 DEFCHAIN 0 DEFLOG 1 DEFPROC 1 MAPSTART 0 MAPSIZE 4900 MAPCODE P POSTPROCSTART 9500 POSTPROCSIZE 200 ALWAYSPROCSTART 9698 ALWAYSPROCSIZE 196 Typical PID Structure typedef struct { Value PIDValue; char c. Parameter. Name[PARAMETER_SIZE]; char c. Display. Value[DISPLAY_SIZE + 10]; char c. Old. Value[DISPLAY_SIZE + 10]; int i. Display. Info; int i. Plot. Counter; /* counter to indicate plotting for the PID is requested by the clients */ int i. Anamoly; int i. Filter; float resolution; int Data. Type; /*verification */ int i. Verify_reqd; // 1 or 0 int i. Vtype; // 1: int, 2: float, 3: compare Value Verify_value; float deviation; char Verify_attr[DISPLAY_SIZE + 10]; // 0: OK, 1: Not OK, 3: No Verification /*log on change */ } BPTCUp. SVSts 1 No: 1901 type: 9 wno: 3582, 3433 And: 80 shift: 7 Data: 2 data: string AORSteps No: 1902 type: 11 wno: 3564, 3421 data: ushort Pos. X_Orbt. Ctrl No: 1903 type: 16 wno: 3566, 3423 A: 0. 305185 B: 0. 000000 UL: 1000000 LL: -1000000 Err: 0. 100000 Unit: kms data: float Pos. Y_Orbt. Ctrl No: 1904 type: 16 wno: 3568, 3425 A: 0. 305185 B: 0. 000000 UL: 1000000 LL: -1000000 Err: 0. 100000 Unit: kms data: float Pos. Z_Orbt. Ctrl No: 1905 type: 16 wno: 3570, 3427 A: 0. 305185 B: 0. 000000 UL: 1000000 LL: -1000000 Err: 0. 100000 Unit: kms data: float October 2015 22

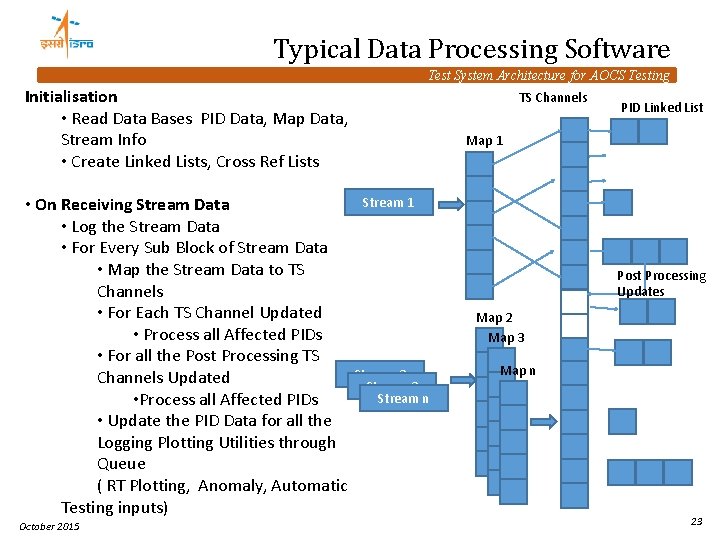

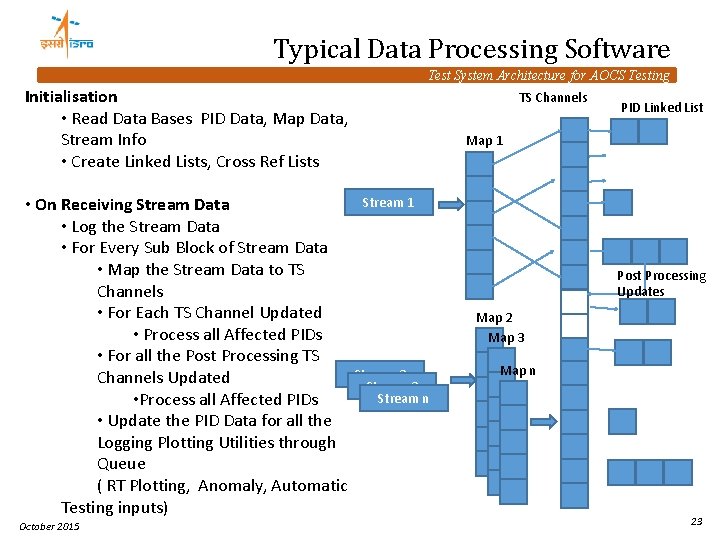

Typical Data Processing Software Test System Architecture for AOCS Testing Initialisation • Read Data Bases PID Data, Map Data, Stream Info • Create Linked Lists, Cross Ref Lists • On Receiving Stream Data • Log the Stream Data • For Every Sub Block of Stream Data • Map the Stream Data to TS Channels • For Each TS Channel Updated • Process all Affected PIDs • For all the Post Processing TS Channels Updated • Process all Affected PIDs • Update the PID Data for all the Logging Plotting Utilities through Queue ( RT Plotting, Anomaly, Automatic Testing inputs) October 2015 TS Channels PID Linked List Map 1 Stream 1 Post Processing Updates Map 2 Map 3 Stream 2 Stream 3 Stream n Map n 23

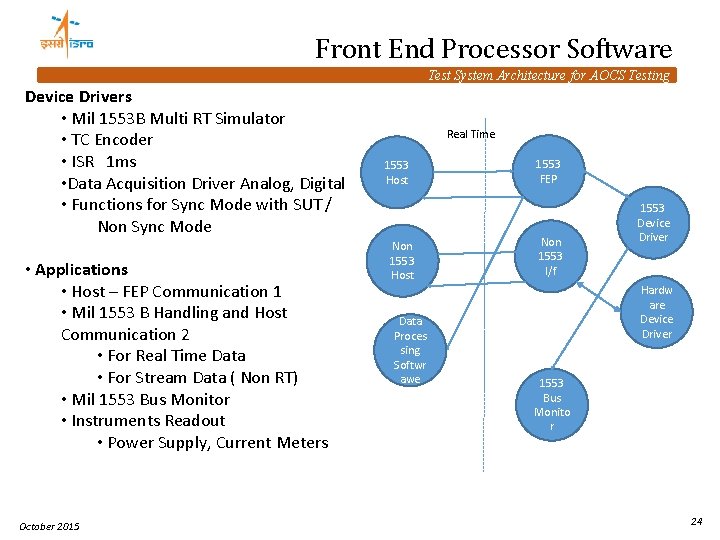

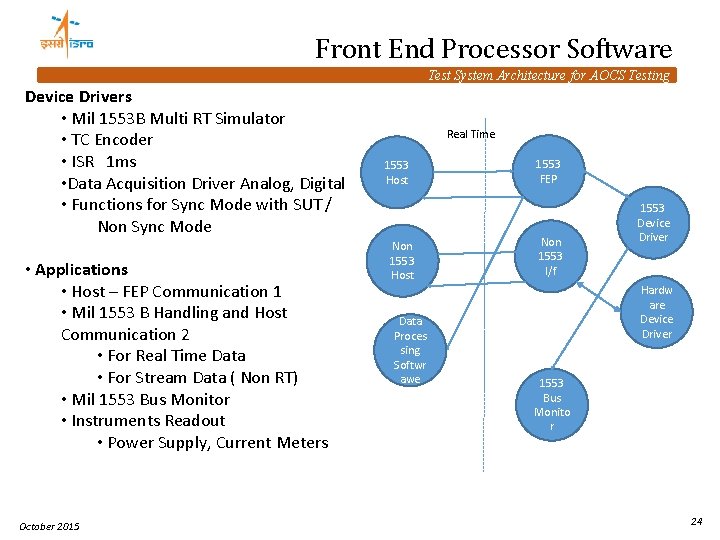

Front End Processor Software Test System Architecture for AOCS Testing Device Drivers • Mil 1553 B Multi RT Simulator • TC Encoder • ISR 1 ms • Data Acquisition Driver Analog, Digital • Functions for Sync Mode with SUT / Non Sync Mode • Applications • Host – FEP Communication 1 • Mil 1553 B Handling and Host Communication 2 • For Real Time Data • For Stream Data ( Non RT) • Mil 1553 Bus Monitor • Instruments Readout • Power Supply, Current Meters October 2015 Real Time 1553 Host Non 1553 Host Data Proces sing Softwr awe 1553 FEP Non 1553 I/f 1553 Device Driver Hardw are Device Driver 1553 Bus Monito r 24

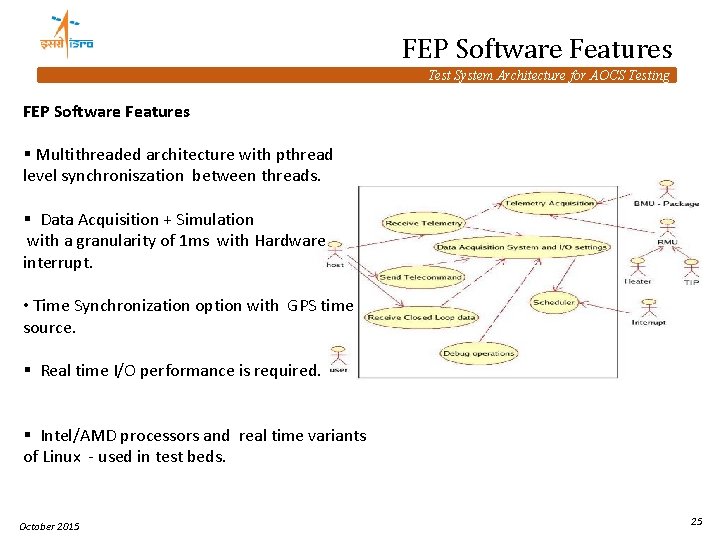

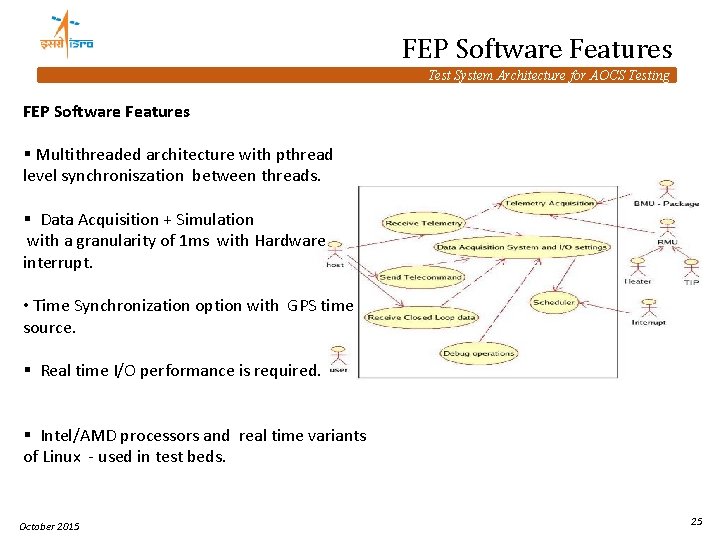

FEP Software Features Test System Architecture for AOCS Testing FEP Software Features § Multithreaded architecture with pthread level synchroniszation between threads. § Data Acquisition + Simulation with a granularity of 1 ms with Hardware interrupt. • Time Synchronization option with GPS time source. § Real time I/O performance is required. § Intel/AMD processors and real time variants of Linux - used in test beds. October 2015 25

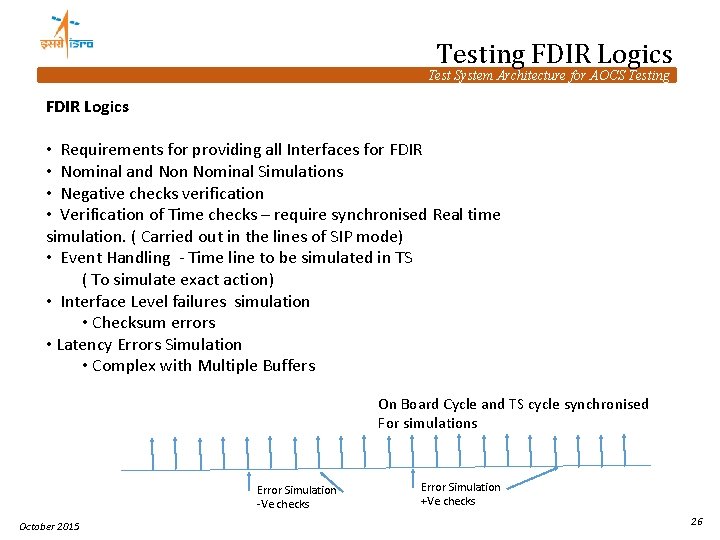

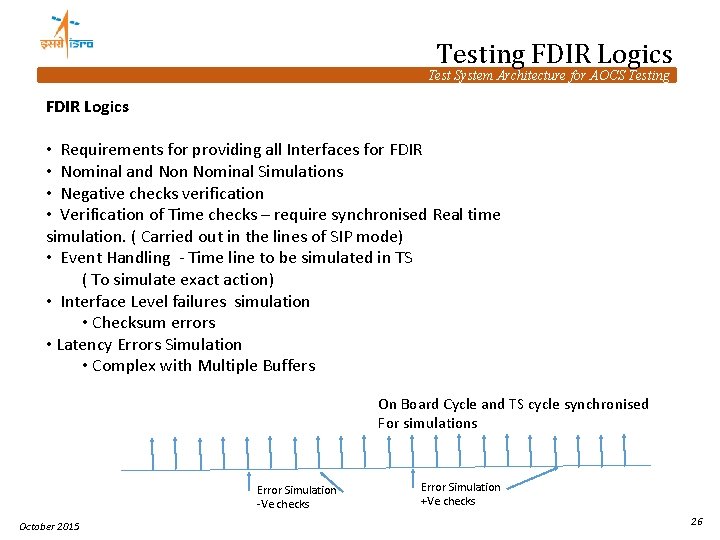

Testing FDIR Logics Test System Architecture for AOCS Testing FDIR Logics • Requirements for providing all Interfaces for FDIR • Nominal and Non Nominal Simulations • Negative checks verification • Verification of Time checks – require synchronised Real time simulation. ( Carried out in the lines of SIP mode) • Event Handling - Time line to be simulated in TS ( To simulate exact action) • Interface Level failures simulation • Checksum errors • Latency Errors Simulation • Complex with Multiple Buffers On Board Cycle and TS cycle synchronised For simulations Error Simulation -Ve checks October 2015 Error Simulation +Ve checks 26

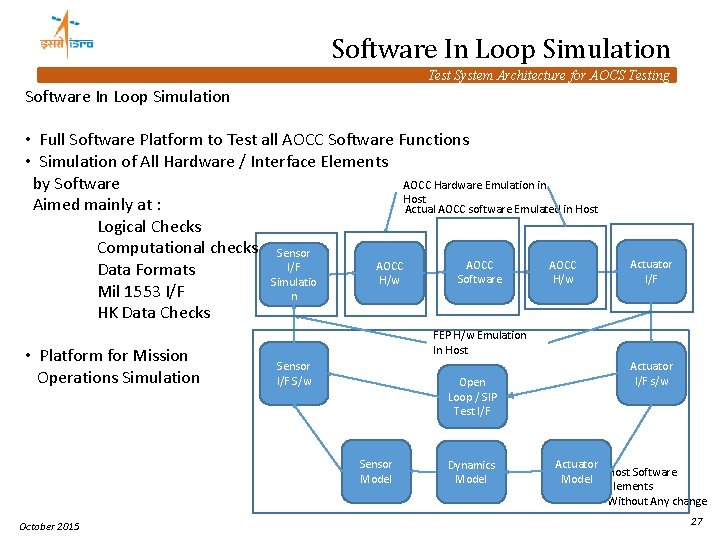

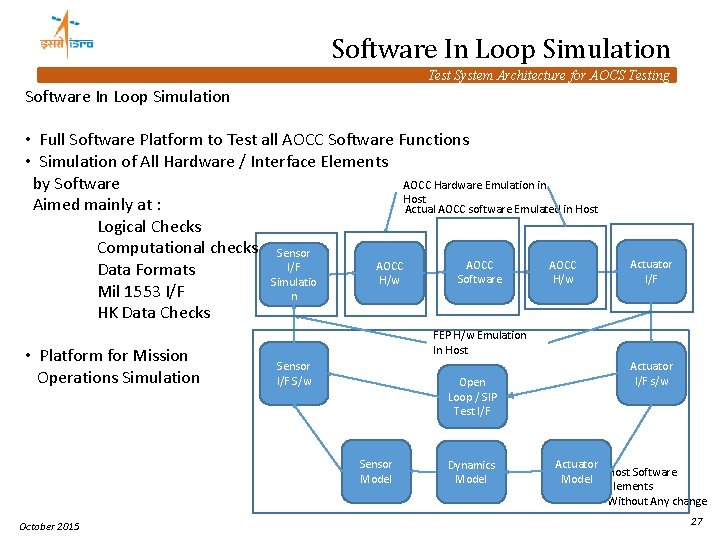

Software In Loop Simulation Test System Architecture for AOCS Testing Software In Loop Simulation • Full Software Platform to Test all AOCC Software Functions • Simulation of All Hardware / Interface Elements by Software AOCC Hardware Emulation in Host Aimed mainly at : Actual AOCC software Emulated in Host Logical Checks Computational checks Sensor AOCC I/F Data Formats Software H/w Simulatio Mil 1553 I/F n HK Data Checks • Platform for Mission Operations Simulation FEP H/w Emulation In Host Sensor I/F S/w Open Loop / SIP Test I/F Sensor Model October 2015 Actuator I/F Dynamics Model Actuator I/F s/w Actuator Host Software Model Elements Without Any change 27

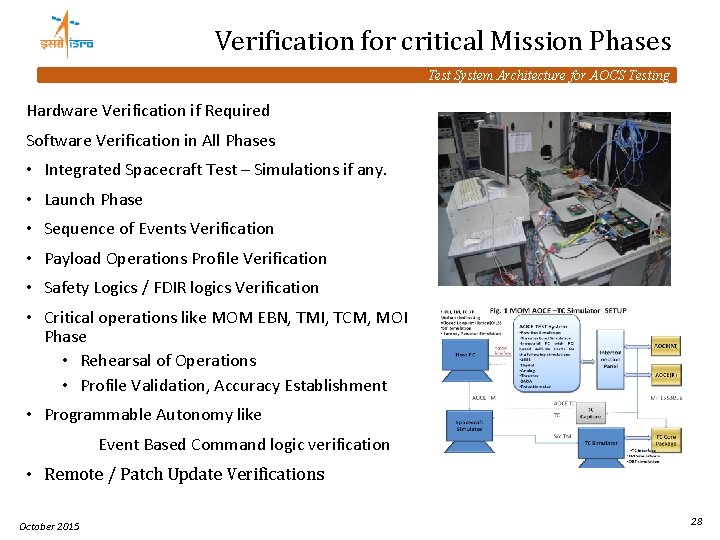

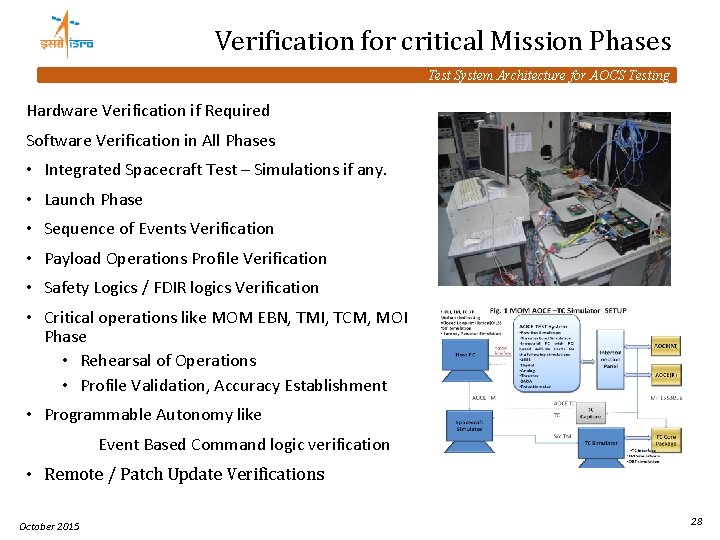

Verification for critical Mission Phases Test System Architecture for AOCS Testing Hardware Verification if Required Software Verification in All Phases • Integrated Spacecraft Test – Simulations if any. • Launch Phase • Sequence of Events Verification • Payload Operations Profile Verification • Safety Logics / FDIR logics Verification • Critical operations like MOM EBN, TMI, TCM, MOI Phase • Rehearsal of Operations • Profile Validation, Accuracy Establishment • Programmable Autonomy like Event Based Command logic verification • Remote / Patch Update Verifications October 2015 28

Other Features Test System Architecture for AOCS Testing Test System Features • Page Display • Real Time Plotting • Inter Message Queues between RT Plot and Data Processing Software • Data Logging • Real Time Commanding, Delay Simulation • Off Line Data Processing Other Test Systems • BC Simulators ( OBC Simulators) • Test System for Motor Drive • Same as RT Data Processing – Data received Electronics ( Antenna Control, Payload from File Platform Control) • Automatic Testing • Testing of Open Loop Test Vectors • Automatic Verification OK/Not OK • Auto Test Language with Script Files with various Features. October 2015 29

Major causes of Error in Testing / Simulation Test System Architecture for AOCS Testing Test Level • Simulation Assumptions / Actual Information not available • Time Synchronisation Errors • Scenario / Sequence Coverage • Accuracy, Precision, Sampling Simulation Errors • Test coverage is not complete/insufficient test cases • Actuator I/f clearance with Diagnostic TM rather than actual actuator output. • Insufficient Test – especially less critical ones like TM • Independent Tests – Interrelated effects missing • Test Limitations Solutions § Proper ICDs § Mission Scenario Tests § Operational Validation § Identification of simulation limitations and addressing alternate methods of validation § Analysis, Review and Process Implementation § Test case generation from requirements /Test Review Boards/Test procedure review/ Automation of testing / Test Results Review § Observations tracking and guidelines/check list generations • Simulation Errors October 2015 30

Summary & Future Enhancements. Test System Architecture for AOCS Testing • The Distributed Test System Architecture has been used extensively for AOCS, Integrated OBC, NGC applications • With little modifications, same frame work is being used for HILS. • Continuous improvements in terms of Automation, Simulations, Data Presentations, Validations are being done. • Increased real time performance, Inclusion of Flexibility dynamics for Closed loop simulation & higher models - the requirements for AOCS are being continuously improved / added. • Software In Loop simulation – being developed for Testing, Operational requirements. Hardware Modelling is also being attempted. • Standard Auto Test Languages, Databases are to be explored. • Miniaturisation in Hardware is being attempted. October 2015 31

Test System Architecture for AOCS Testing Acknowledgements are Due to • Dr. A S Kiran Kumar, Chairman ISRO • Dr. M Annadurai, Director ISAC • Mr. Subramanya Udupa, DD, CDA, ISAC • Colleagues and Team members of Control and Digital Electronics Group, Sincere thanks to • Dr. Allen D Unell, Chairman FSW-2015 • Mr. Subodh Harmalkar, FSW-2015, APL sudhakar@isac. gov. in October 2015