Paging and Virtual Memory Operating Systems Spring 2004

- Slides: 35

Paging and Virtual Memory Operating Systems Spring 2004 OS Spring ‘ 04

The memory of a program § Source-code is compiled into linkable object modules Memory addresses given as relative offsets Libraries contain object modules § Object modules are linked together into a loadable module Leave unresolved references to dynamic libraries § Loadable modules are loaded into memory and execute in a process The OS + hardware map from logical address space to physical memory OS Spring ‘ 04

Physical to logical address mapping § Every memory access is handled by the memory management unit (MMU) Example: C = A+B w four memory accesses (why? ) § Simple scheme: Physical addr = base register + logical addr § Logical addressing allows Multiple programs to co-exist in memory Use overlays to increase the available address space beyond physical limitation Use shared libraries and dynamic library loading OS Spring ‘ 04

Swapping § Use secondary storage to store running processes Swap-out: suspend a process, copy its memory from main memory to disk Swap-in: copy a stored process from disk to main memory and resume running state § Logical addressing: allow swapping back to a different location in memory § Caution: DMA and asynchronous I/O to swapped processes must take care OS Spring ‘ 04

Memory management: Review § Fixed partitioning, dynamic partitioning § Problems Internal/external fragmentation A process can be loaded only if a contiguous memory chunk is available to accommodate the process Process size is limited by the main memory size § Advantage: simplicity OS Spring ‘ 04

Paging § Process memory is divided into fixed size chunks of the same size, called pages § Pages are mapped onto frames in the main memory § Process pages can be scattered all over the main memory § No external fragmentation OS Spring ‘ 04

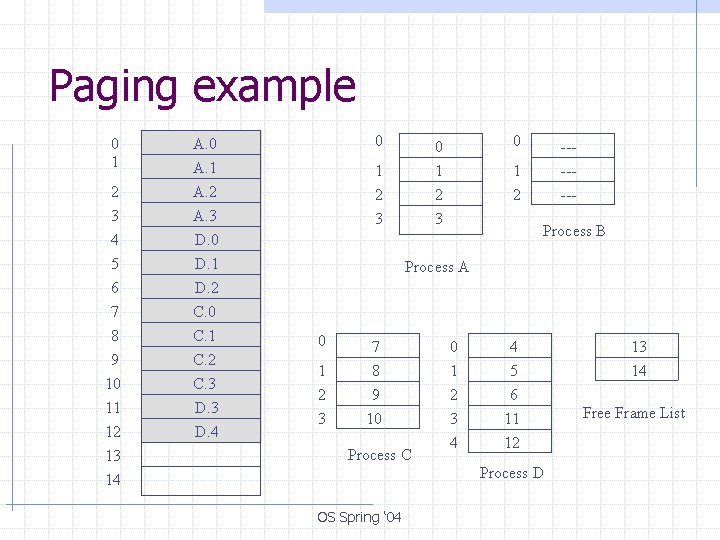

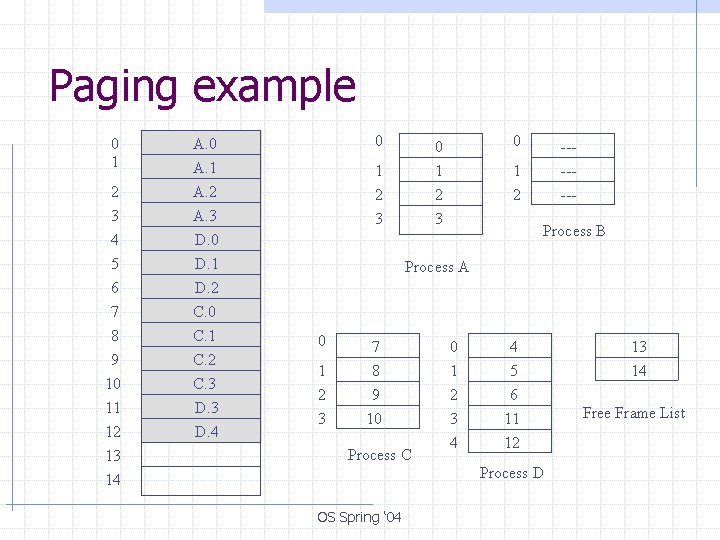

Paging example 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 0 A. 1 A. 2 A. 3 D. 0 D. 1 D. 2 C. 0 C. 1 C. 2 C. 3 D. 4 0 0 1 2 3 ------- 1 2 Process B Process A 0 1 2 3 7 8 9 10 Process C 0 1 2 3 4 4 5 6 11 12 Process D OS Spring ‘ 04 13 14 Free Frame List

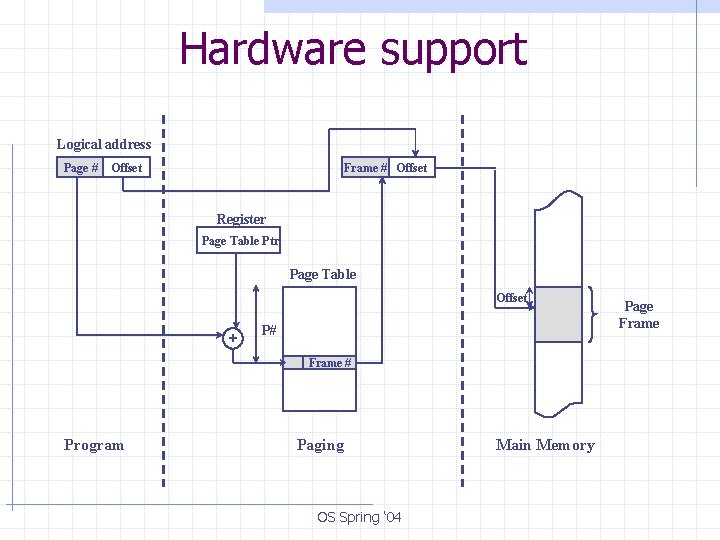

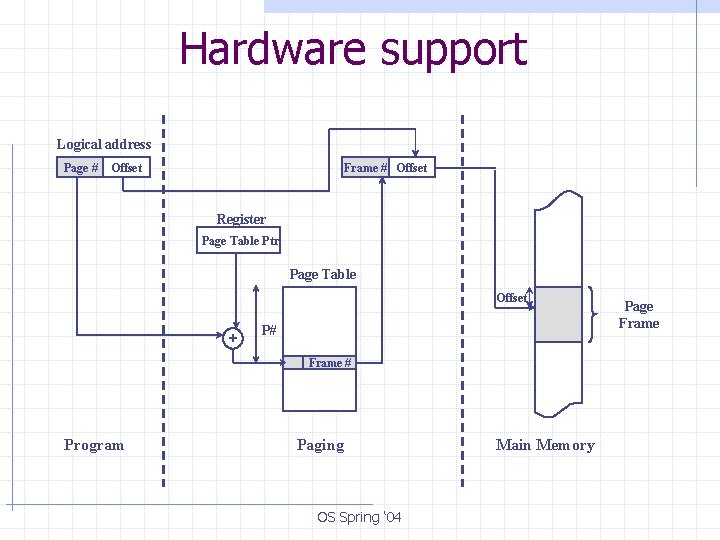

Paging support § Page table maintains mapping of process pages onto frames § Hardware support is needed to support translation of relative addresses within a program (logical addresses) into the memory addresses OS Spring ‘ 04

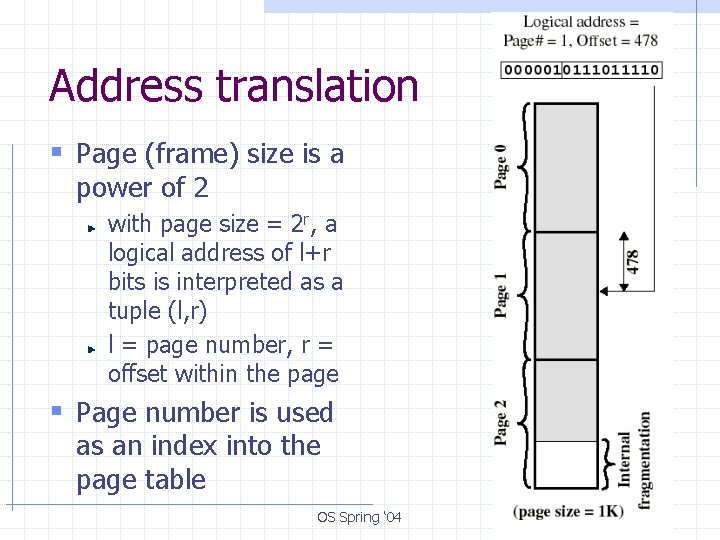

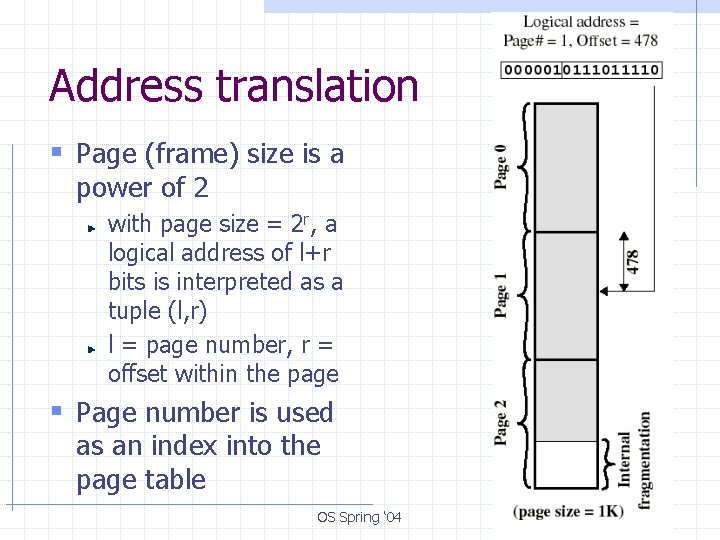

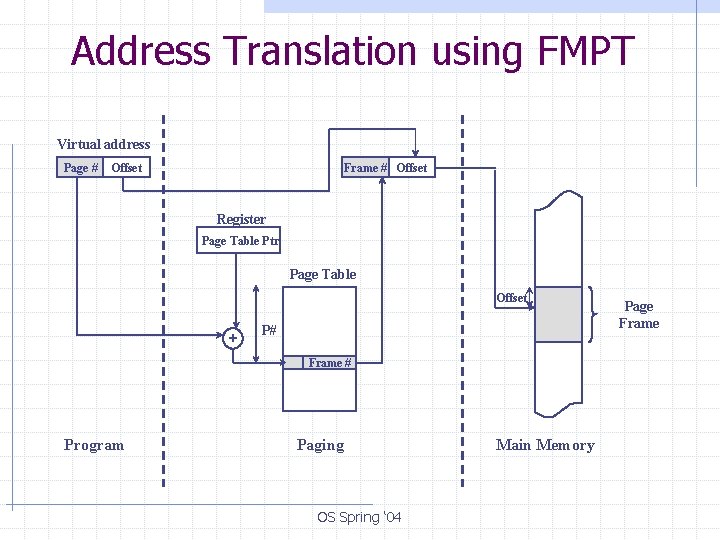

Address translation § Page (frame) size is a power of 2 with page size = 2 r, a logical address of l+r bits is interpreted as a tuple (l, r) l = page number, r = offset within the page § Page number is used as an index into the page table OS Spring ‘ 04

Hardware support Logical address Page # Offset Frame # Offset Register Page Table Ptr Page Table Offset + P# Frame # Program Paging OS Spring ‘ 04 Main Memory Page Frame

Virtual Memory § Paging makes virtual memory possible Logical to physical address mapping is dynamic => It is not necessary that all of the process pages be in main memory during execution OS Spring ‘ 04

Benefits § More processes may be maintained in the main memory Better system utilization and throughput § The process size is not restricted by the physical memory size: the process memory is virtual But what is the limit anyway? § Less disk I/O to swap/load programs OS Spring ‘ 04

How does this work? § CPU can execute a process as long as some portion of its address space is mapped onto the physical memory E. g. , next instruction and data addresses are mapped § Once a reference to an unmapped page is generated (page fault): Page fault interrupt transfers control to the OS handler OS Spring ‘ 04

Page Fault Handler § Put the process into blocking state § Program disk controller to read the page from disk into the memory § Later on: I/O interrupt signals completion § Resume the process OS Spring ‘ 04

Why is this practical? § Observation: Program branching and data access patterns are not random § Principle of locality: program and data references tend to cluster => Only a fraction of the process virtual address space need to be resident to allow the process to execute for sufficiently long OS Spring ‘ 04

Virtual memory implementation § Efficient run-time address translation Hardware support, control data structures § Fetch policy Demand paging: page is brought into the memory only when page-fault occurs Pre-paging: pages are brought in advance § Page replacement policy Which page to evict when a page fault occurs? OS Spring ‘ 04

Thrashing § A condition when the system is engaged in moving pages back and forth between memory and disk most of the time § Bad page replacement policy may result in thrashing § Programs with non-local behavior OS Spring ‘ 04

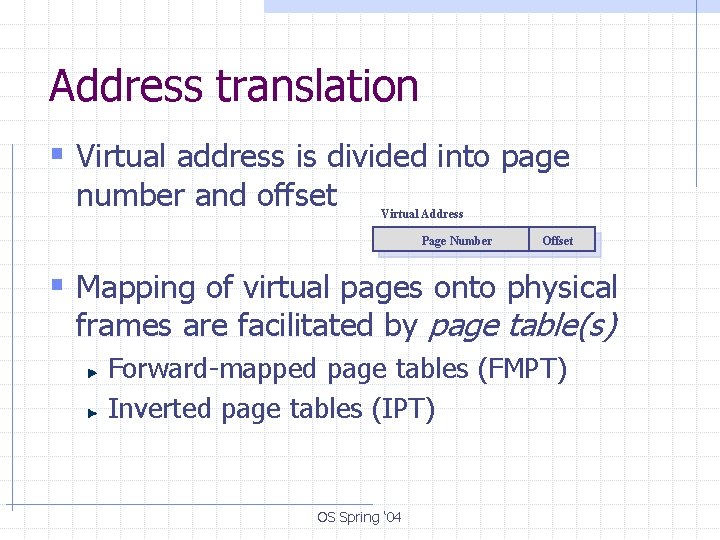

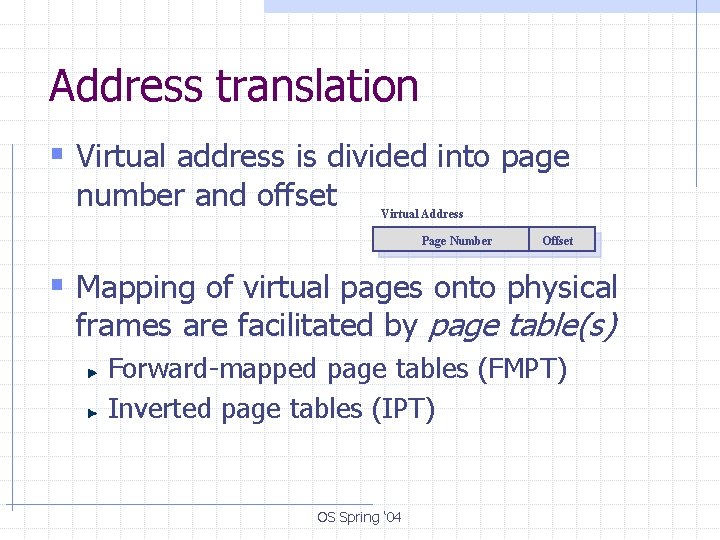

Address translation § Virtual address is divided into page number and offset Virtual Address Page Number Offset § Mapping of virtual pages onto physical frames are facilitated by page table(s) Forward-mapped page tables (FMPT) Inverted page tables (IPT) OS Spring ‘ 04

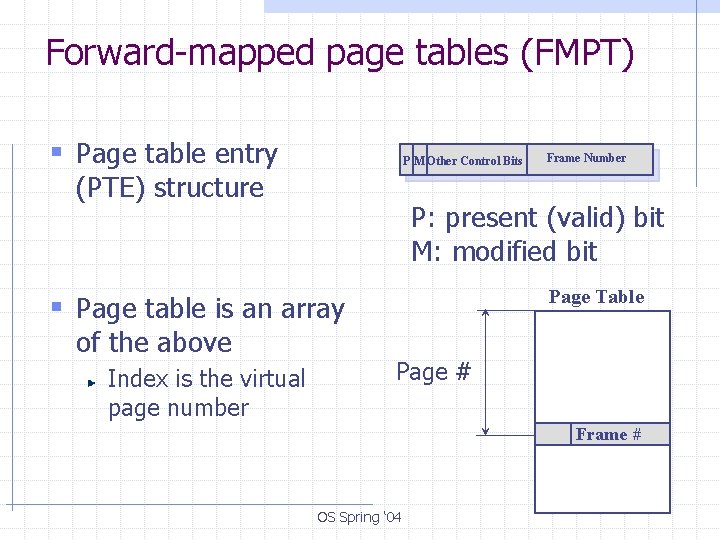

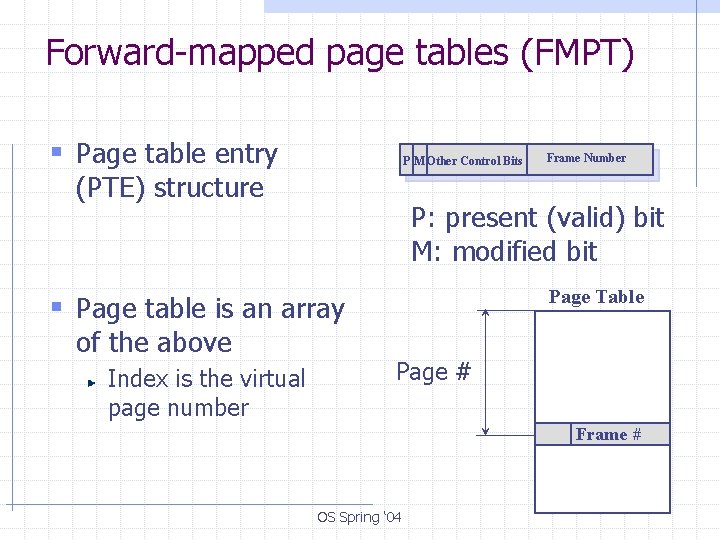

Forward-mapped page tables (FMPT) § Page table entry P M Other Control Bits (PTE) structure P: present (valid) bit M: modified bit Page Table § Page table is an array of the above Index is the virtual page number Frame Number Page # Frame # OS Spring ‘ 04

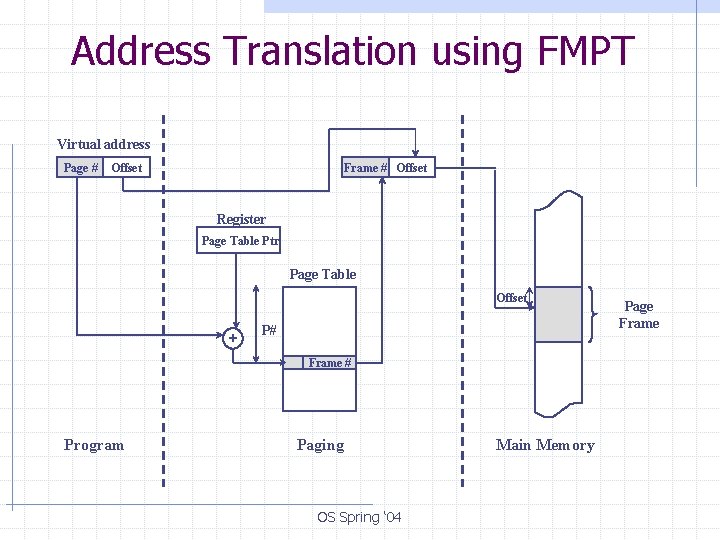

Address Translation using FMPT Virtual address Page # Offset Frame # Offset Register Page Table Ptr Page Table Offset + P# Frame # Program Paging OS Spring ‘ 04 Main Memory Page Frame

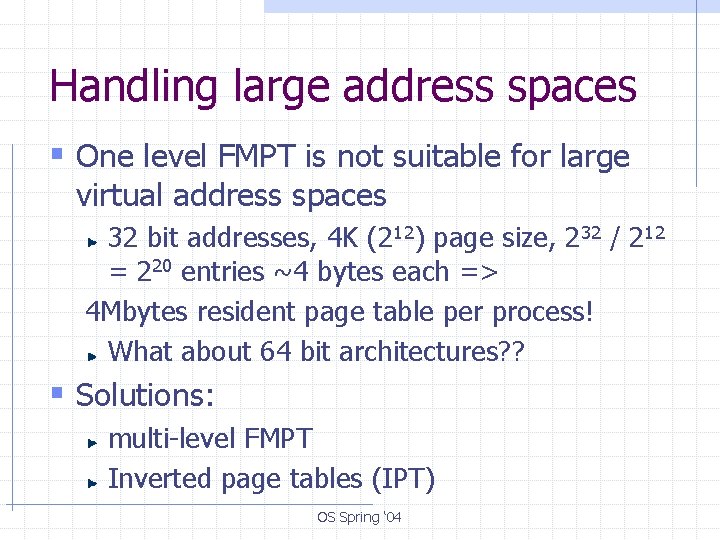

Handling large address spaces § One level FMPT is not suitable for large virtual address spaces 32 bit addresses, 4 K (212) page size, 232 / 212 = 220 entries ~4 bytes each => 4 Mbytes resident page table per process! What about 64 bit architectures? ? § Solutions: multi-level FMPT Inverted page tables (IPT) OS Spring ‘ 04

Multilevel FMPT § Use bits of the virtual address to index a hierarchy of page tables § The leaf is a regular PTE § Only the root is required to stay resident in main memory Other portions of the hierarchy are subject to paging as regular process pages OS Spring ‘ 04

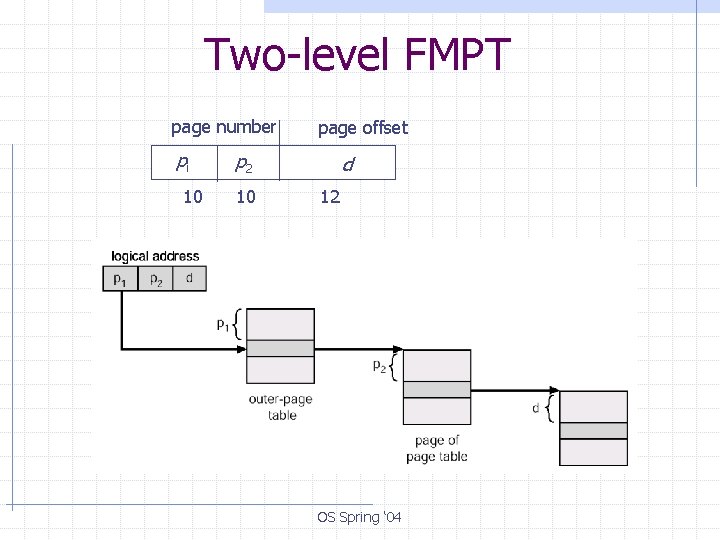

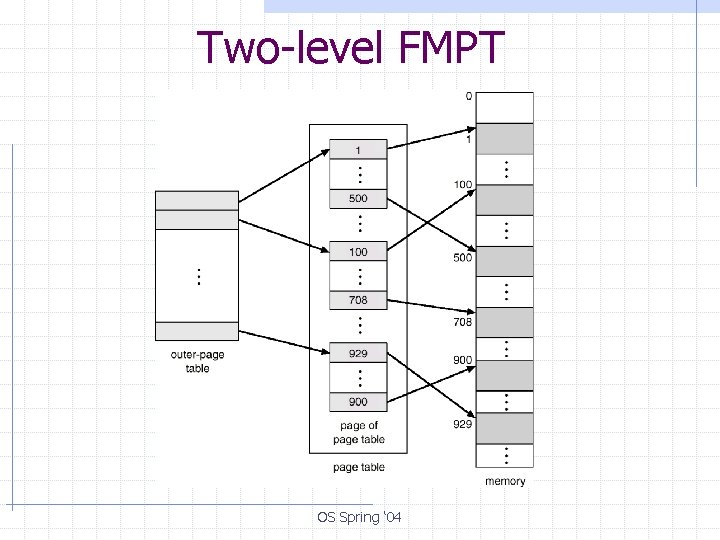

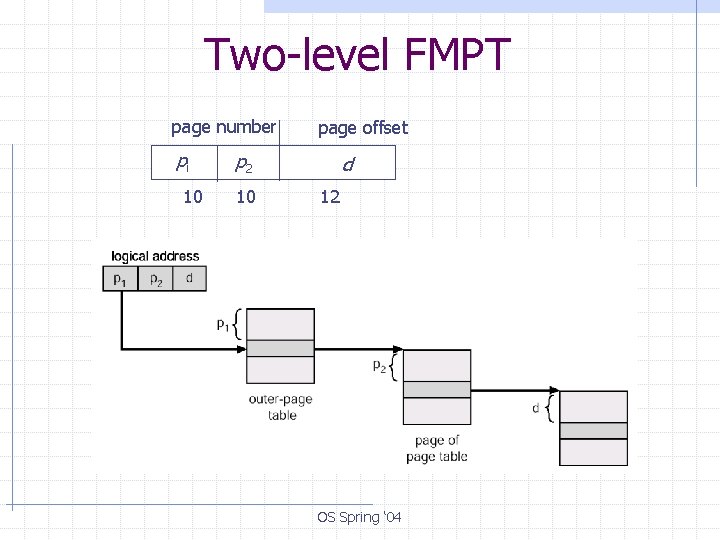

Two-level FMPT page number pi 10 page offset p 2 10 d 12 OS Spring ‘ 04

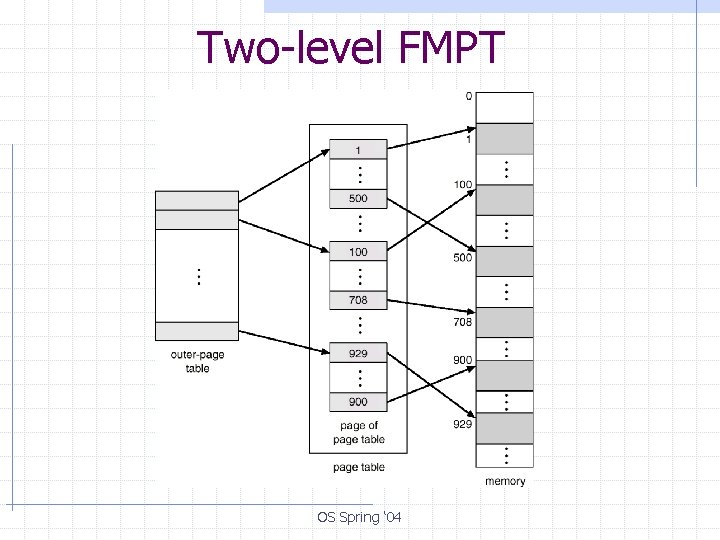

Two-level FMPT OS Spring ‘ 04

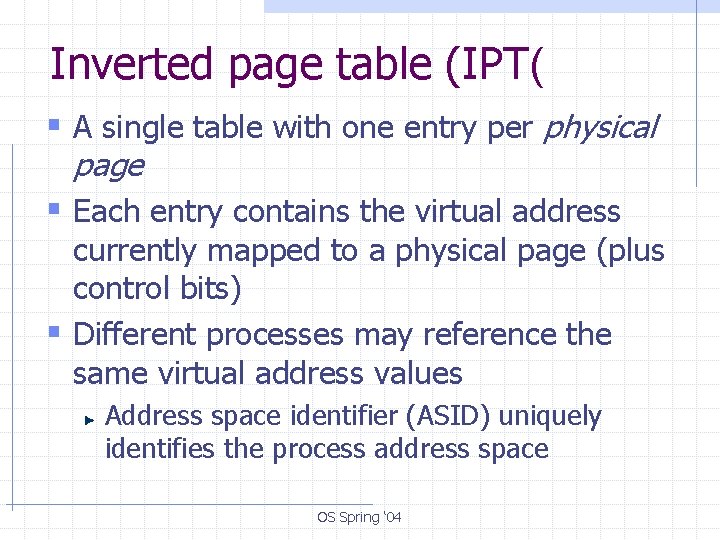

Inverted page table (IPT( § A single table with one entry per physical page § Each entry contains the virtual address currently mapped to a physical page (plus control bits) § Different processes may reference the same virtual address values Address space identifier (ASID) uniquely identifies the process address space OS Spring ‘ 04

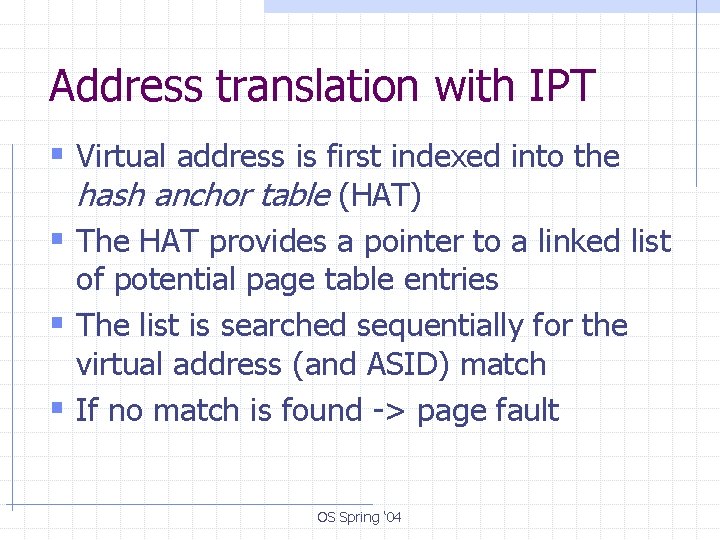

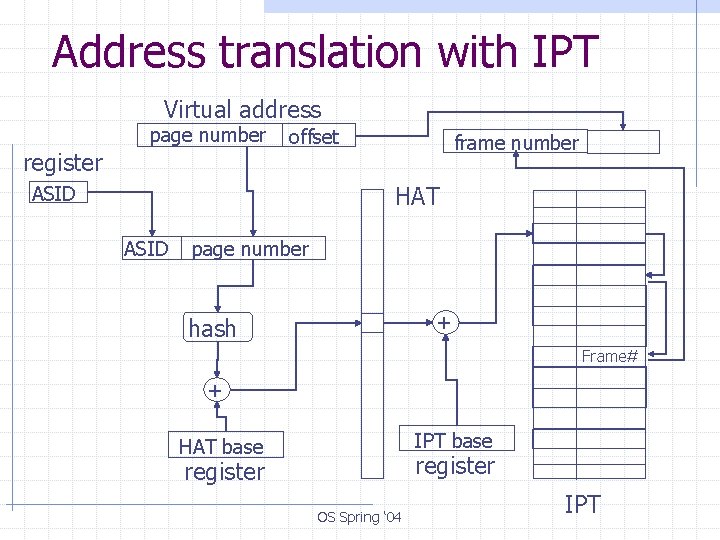

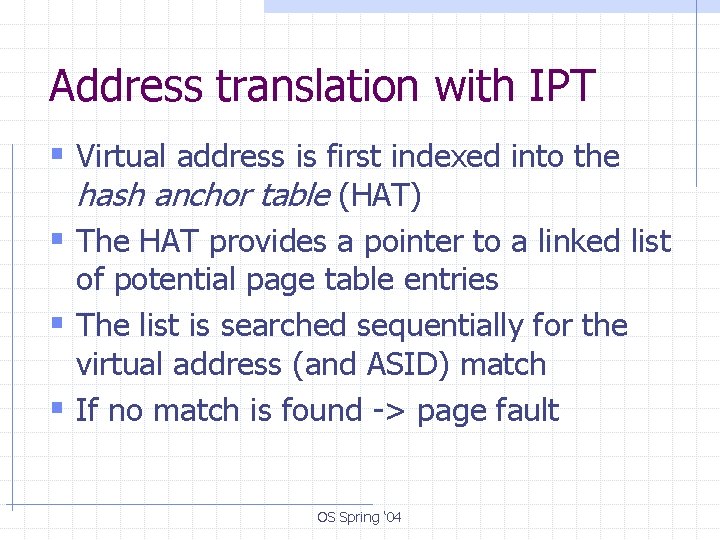

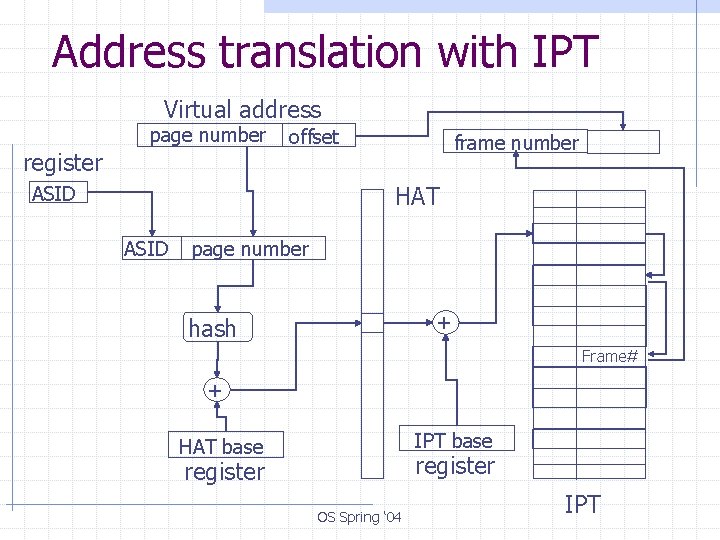

Address translation with IPT § Virtual address is first indexed into the hash anchor table (HAT) § The HAT provides a pointer to a linked list of potential page table entries § The list is searched sequentially for the virtual address (and ASID) match § If no match is found -> page fault OS Spring ‘ 04

Address translation with IPT Virtual address page number register offset frame number HAT ASID page number + hash Frame# + IPT base HAT base register OS Spring ‘ 04 IPT

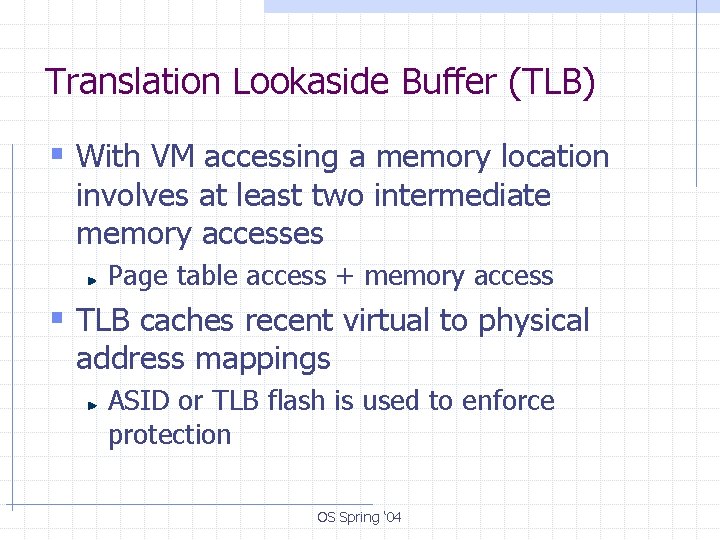

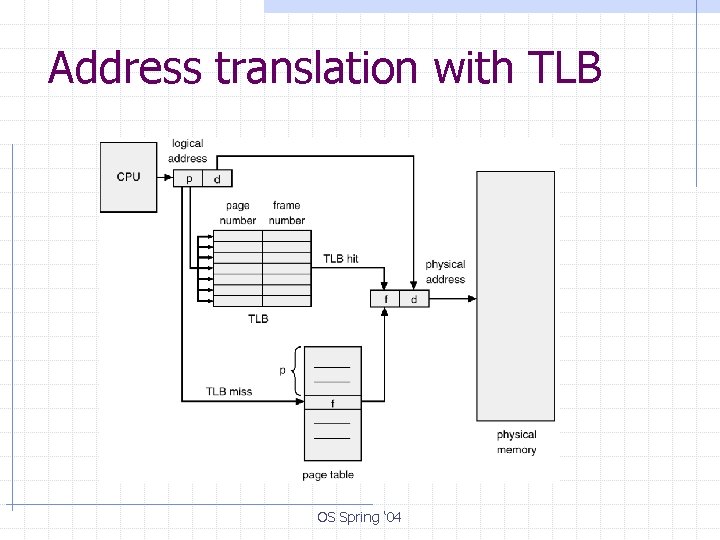

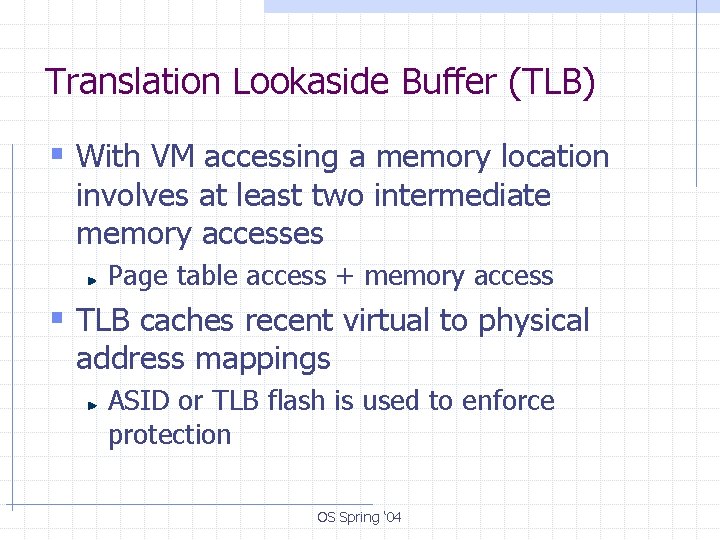

Translation Lookaside Buffer (TLB) § With VM accessing a memory location involves at least two intermediate memory accesses Page table access + memory access § TLB caches recent virtual to physical address mappings ASID or TLB flash is used to enforce protection OS Spring ‘ 04

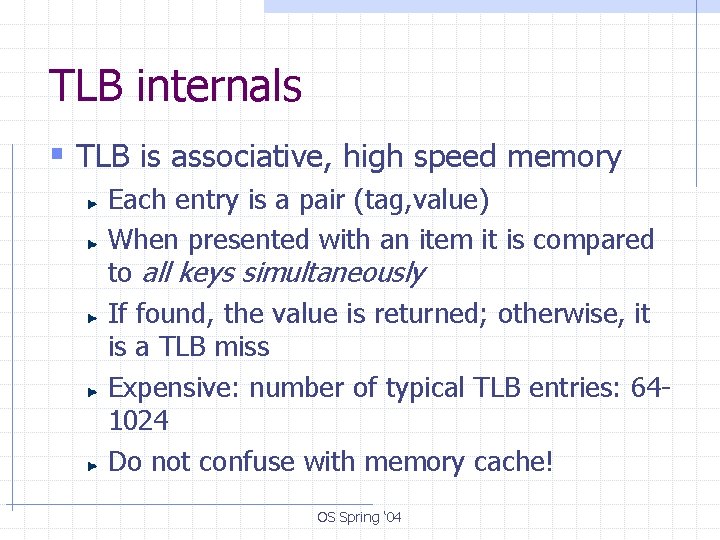

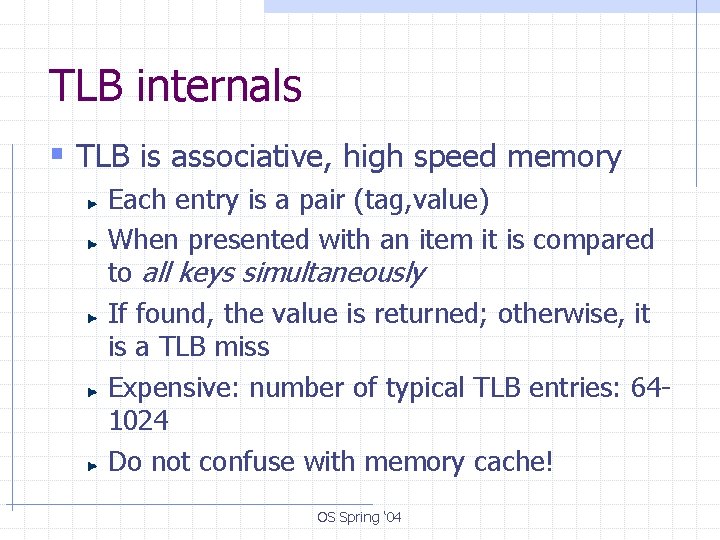

TLB internals § TLB is associative, high speed memory Each entry is a pair (tag, value) When presented with an item it is compared to all keys simultaneously If found, the value is returned; otherwise, it is a TLB miss Expensive: number of typical TLB entries: 641024 Do not confuse with memory cache! OS Spring ‘ 04

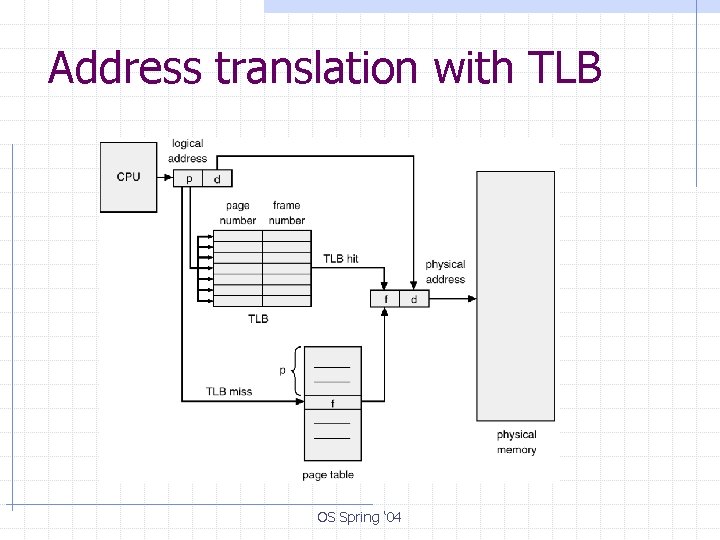

Address translation with TLB OS Spring ‘ 04

Bits in the PTE: Present (valid( § Present (valid) bit Indicates whether the page is assigned to frame or not A reference to an invalid page generates page fault which is handled by the operating system OS Spring ‘ 04

Bits in PTE: modified, used § Modified (dirty) bit Indicates whether the page has been modified Unmodified pages need not be written back to the disk when evicted § Used bit Indicates whether the page has been accessed recently Used by the page replacement algorithm OS Spring ‘ 04

Bits in PTE § Access permissions bit indicates whether the page is read-only or read-write § UNIX copy-on-write bit Set whether more than one process shares a page If one of the processes writes into the page, a separate copy must first be made for all other processes sharing the page Useful for optimizing fork() OS Spring ‘ 04

Protection with VM § Preventing processes from accessing other process pages § Simple with FMPT Load the process page table base address into a register upon context switch § ASID with IPT OS Spring ‘ 04

Page size considerations § Small page size better approximates locality large page tables inefficient disk transfer § Large page size internal fragmentation § Most modern architectures support a number of different page sizes w a configurable system parameter OS Spring ‘ 04