Nzev projektu slo materilu Pedmt Ronk Tematick celek

- Slides: 14

Název projektu: Číslo materiálu: Předmět: Ročník: Tematický celek: Moderní výuka s využitím ICT CZ. 1. 07/1. 5. 00/34. 0734 VY_2_INOVACE_CT-3 -06 -1 Bc Číslicová technika 3. Sekvenční obvody Klopný obvod MASTER-SLAVE Autor: Ing. Pavel Bachura Datum tvorby: 10. 12. 2012

Obsah tematického celku 1) Klopný obvod MASTER-SLAVE - úvod 2) Klopný obvod RST - opakování 3) Klopný obvod RST – shrnutí 4) Klopný obvod MASTER-SLAVE

Klíčová slova • • • Sekvenční obvod Klopný obvod RST Klopný obvod MASTER-SLAVE Statický vstup T Dynamický vstup T Paměťový stav

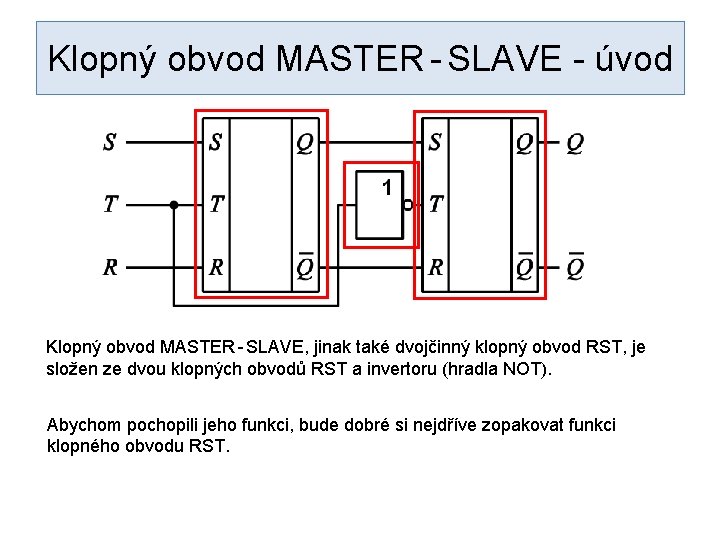

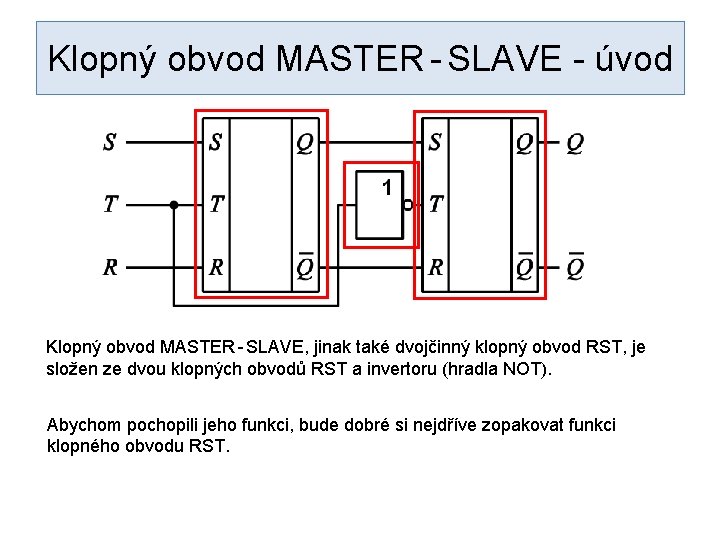

Klopný obvod MASTER - SLAVE - úvod Klopný obvod MASTER - SLAVE, jinak také dvojčinný klopný obvod RST, je složen ze dvou klopných obvodů RST a invertoru (hradla NOT). Abychom pochopili jeho funkci, bude dobré si nejdříve zopakovat funkci klopného obvodu RST.

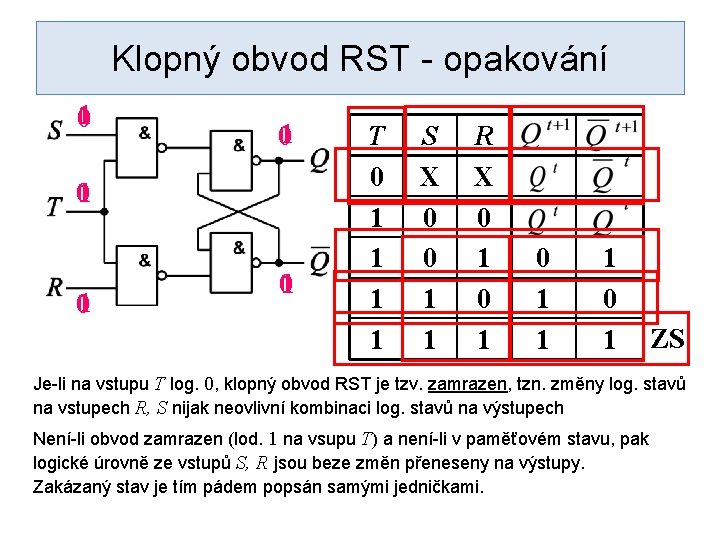

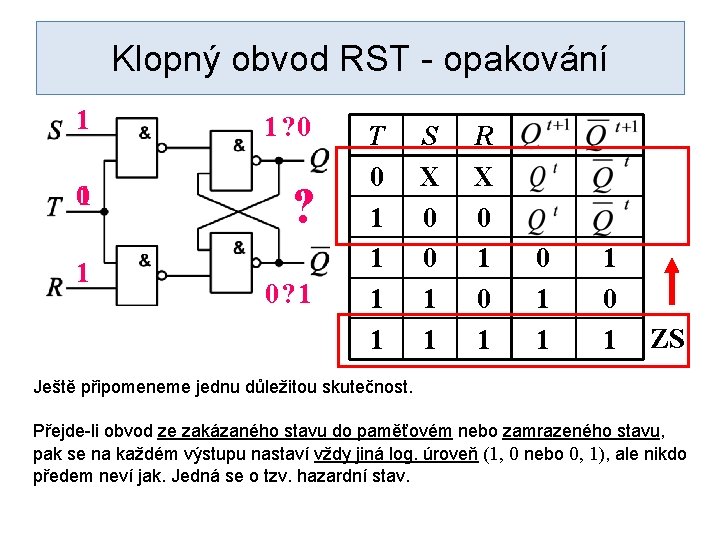

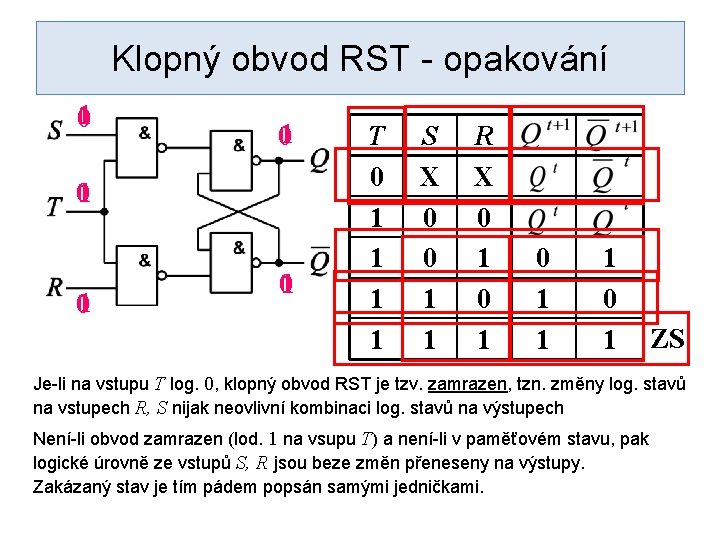

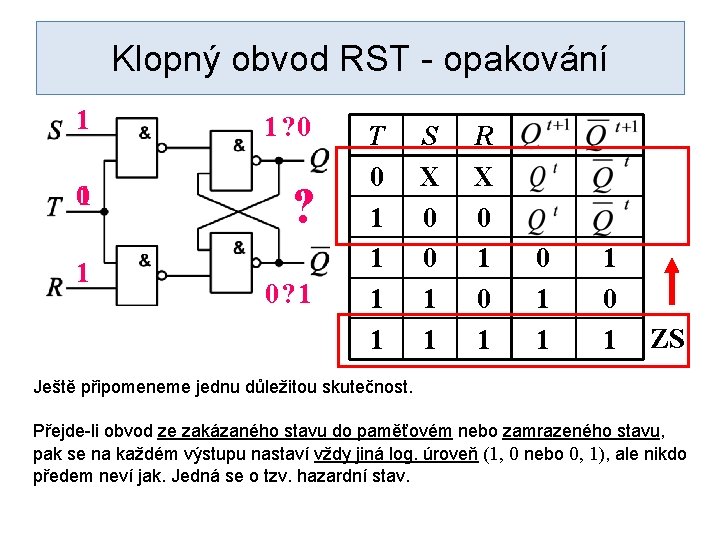

Klopný obvod RST - opakování 01 01 01 T 0 1 1 S X 0 0 1 1 R X 0 1 0 1 1 1 0 1 ZS Je-li na vstupu T log. 0, klopný obvod RST je tzv. zamrazen, tzn. změny log. stavů na vstupech R, S nijak neovlivní kombinaci log. stavů na výstupech Není-li obvod zamrazen (lod. 1 na vsupu T) a není-li v paměťovém stavu, pak logické úrovně ze vstupů S, R jsou beze změn přeneseny na výstupy. Zakázaný stav je tím pádem popsán samými jedničkami.

Klopný obvod RST - opakování 1 1? 0 01 ? 1 0? 1 T 0 1 1 S X 0 0 1 1 R X 0 1 0 1 1 1 0 1 ZS Ještě připomeneme jednu důležitou skutečnost. Přejde-li obvod ze zakázaného stavu do paměťovém nebo zamrazeného stavu, pak se na každém výstupu nastaví vždy jiná log. úroveň (1, 0 nebo 0, 1), ale nikdo předem neví jak. Jedná se o tzv. hazardní stav.

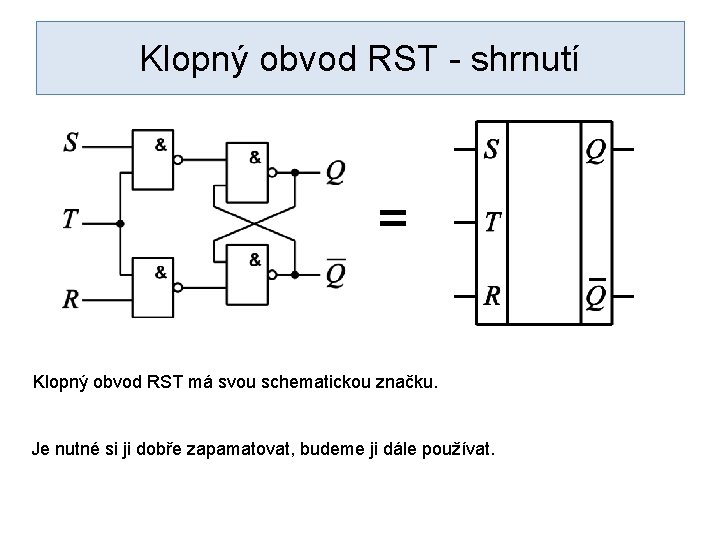

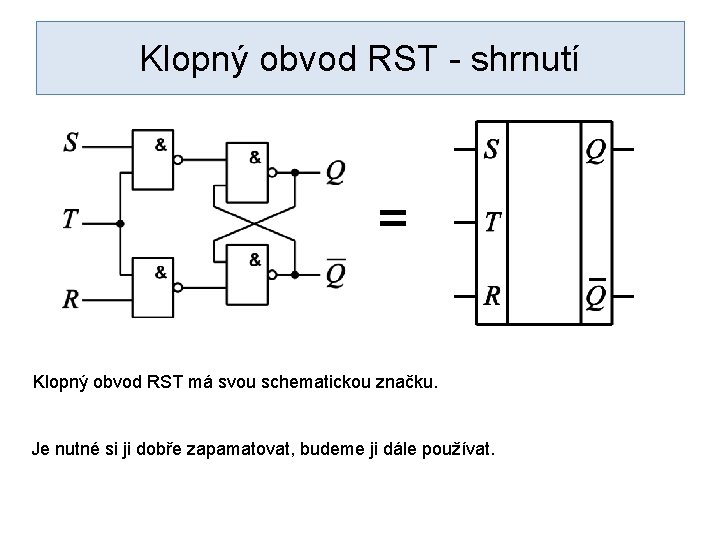

Klopný obvod RST - shrnutí = Klopný obvod RST má svou schematickou značku. Je nutné si ji dobře zapamatovat, budeme ji dále používat.

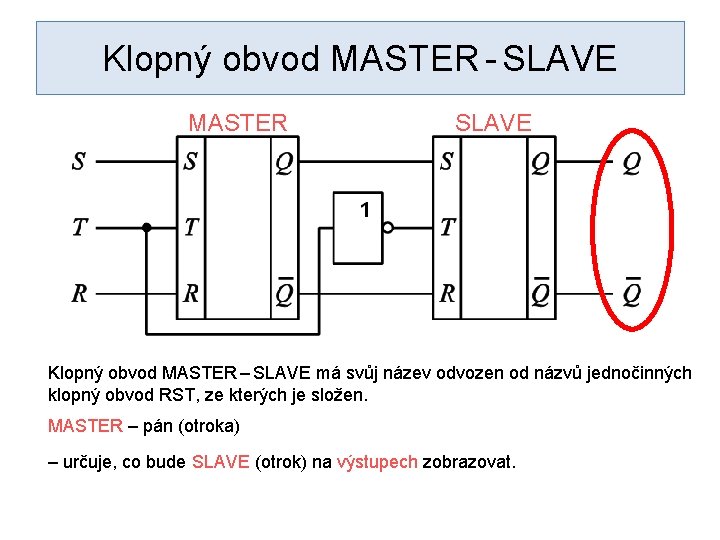

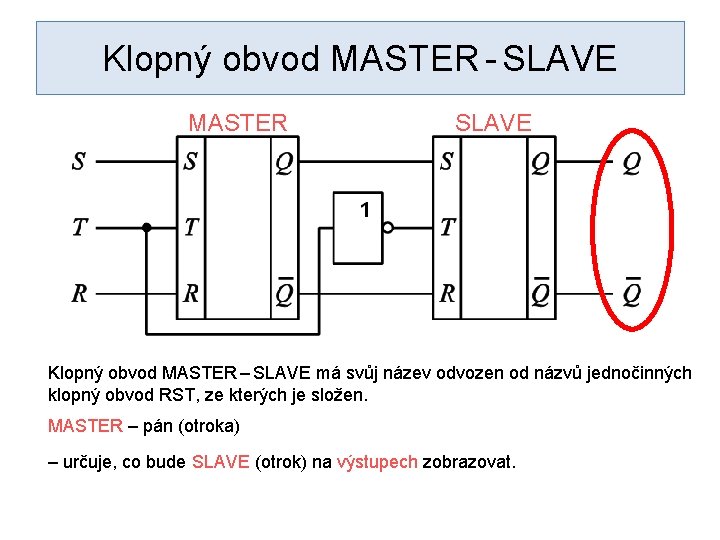

Klopný obvod MASTER - SLAVE MASTER SLAVE Klopný obvod MASTER – SLAVE má svůj název odvozen od názvů jednočinných klopný obvod RST, ze kterých je složen. MASTER – pán (otroka) – určuje, co bude SLAVE (otrok) na výstupech zobrazovat.

Klopný obvod MASTER - SLAVE 1 1 0 MASTER R O Z M R A Z E N 1 ▲ 0 VNITŘNÍ PAMĚŤ ▼ 0 SLAVE Z A M R A Z E N 1? 0 0? 1 Funkci klopného obvodu MASTER – SLAVE budeme zkoumat vždy ze stejného výchozího stavu - logická 1 na vstupu T => MASTER je rozmrazen a SLAVE logická 0 na vstupu T (za invertorem) zamrazen. Na vstup S přivedeme např. log. 1 a na vstup R log. 0. Tyto logické stavy se ihned přenesou na výstupy rozmrazeného klopného obvodu MASTER, tedy do tzv. „vnitřní paměti“ klopného obvodu MASTER – SLAVE. Dál se ale přes zamrazený SLAVE nedostanou, na výstupech tedy budou nějaké rozdílné logické stavy zapamatované z předchozího stavu klopného obvodu.

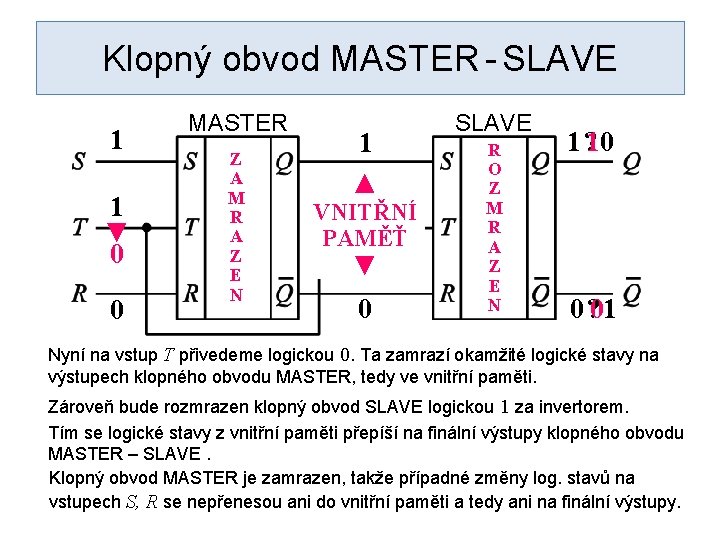

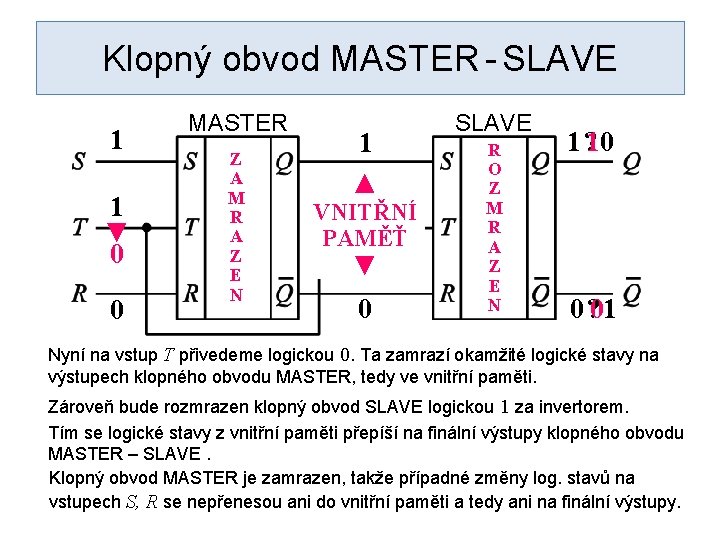

Klopný obvod MASTER - SLAVE 1 1 ▼ 0 0 MASTER Z A M R A Z E N 1 ▲ 0 VNITŘNÍ ▼ PAMĚŤ ▼ 1 0 SLAVE R O Z M R A Z E N 1 ? 10 0 ? 01 Nyní na vstup T přivedeme logickou 0. Ta zamrazí okamžité logické stavy na výstupech klopného obvodu MASTER, tedy ve vnitřní paměti. Zároveň bude rozmrazen klopný obvod SLAVE logickou 1 za invertorem. Tím se logické stavy z vnitřní paměti přepíší na finální výstupy klopného obvodu MASTER – SLAVE. Klopný obvod MASTER je zamrazen, takže případné změny log. stavů na vstupech S, R se nepřenesou ani do vnitřní paměti a tedy ani na finální výstupy.

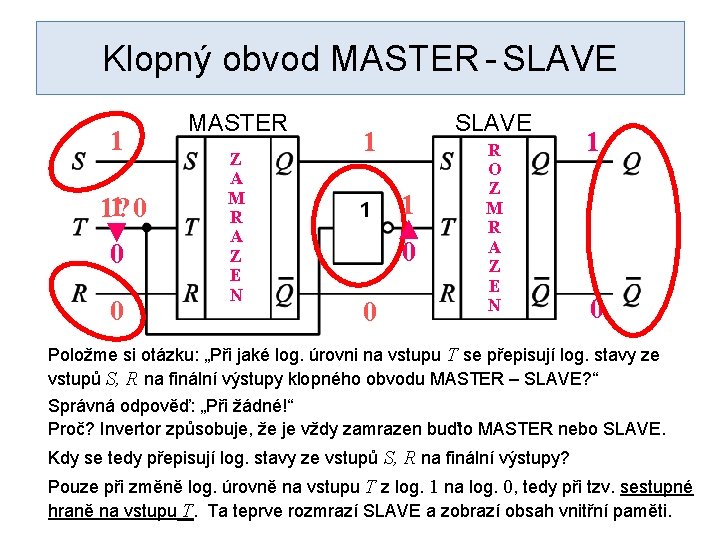

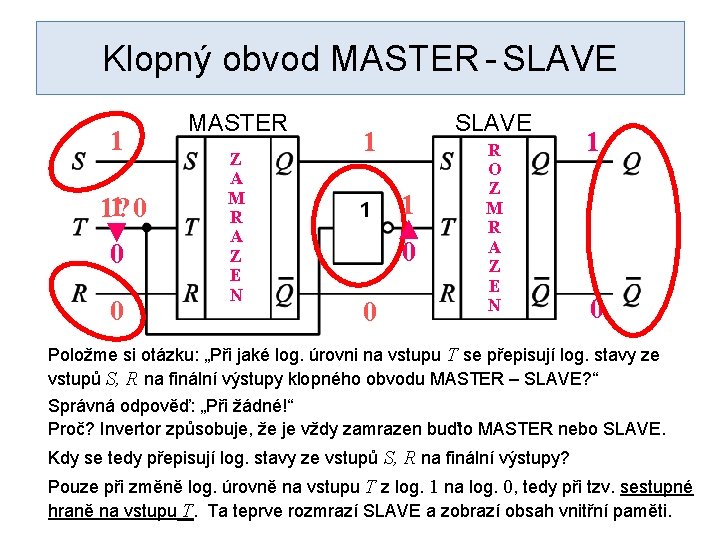

Klopný obvod MASTER - SLAVE 1 11? 0 ▼ 0 0 MASTER Z A M R A Z E N SLAVE 1 1 ▲ 0 0 R O Z M R A Z E N 1 0 Položme si otázku: „Při jaké log. úrovni na vstupu T se přepisují log. stavy ze vstupů S, R na finální výstupy klopného obvodu MASTER – SLAVE? “ Správná odpověď: „Při žádné!“ Proč? Invertor způsobuje, že je vždy zamrazen buďto MASTER nebo SLAVE. Kdy se tedy přepisují log. stavy ze vstupů S, R na finální výstupy? Pouze při změně log. úrovně na vstupu T z log. 1 na log. 0, tedy při tzv. sestupné hraně na vstupu T. Ta teprve rozmrazí SLAVE a zobrazí obsah vnitřní paměti.

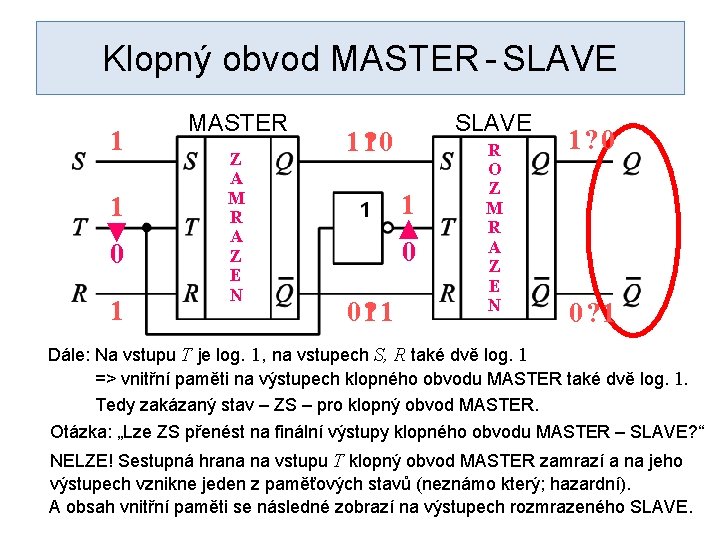

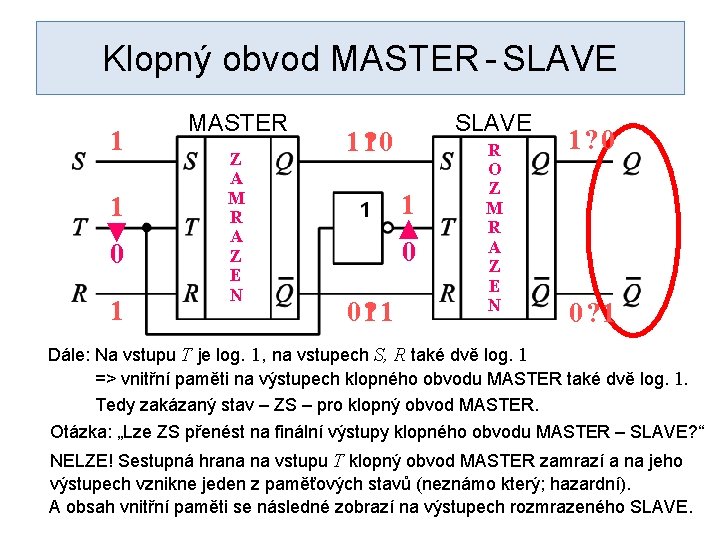

Klopný obvod MASTER - SLAVE 1 1 ▼ 0 1 MASTER Z A M R A Z E N SLAVE 1 ? 1 0 1 ▲ 0 0 ? 1 1 R O Z M R A Z E N 1? 0 0? 1 Dále: Na vstupu T je log. 1, na vstupech S, R také dvě log. 1 => vnitřní paměti na výstupech klopného obvodu MASTER také dvě log. 1. Tedy zakázaný stav – ZS – pro klopný obvod MASTER. Otázka: „Lze ZS přenést na finální výstupy klopného obvodu MASTER – SLAVE? “ NELZE! Sestupná hrana na vstupu T klopný obvod MASTER zamrazí a na jeho výstupech vznikne jeden z paměťových stavů (neznámo který; hazardní). A obsah vnitřní paměti se následné zobrazí na výstupech rozmrazeného SLAVE.

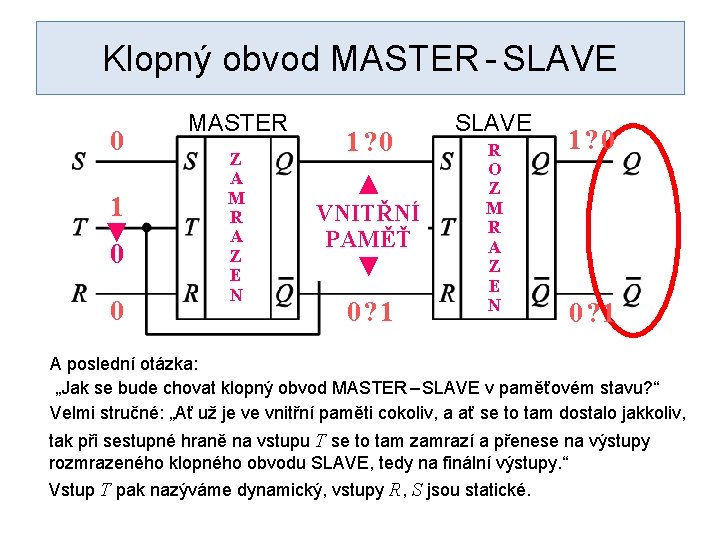

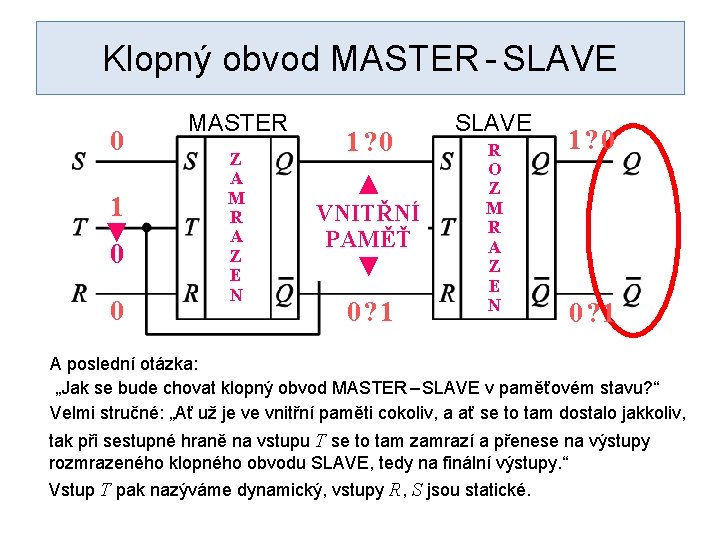

Klopný obvod MASTER - SLAVE 0 1 ▼ 0 0 MASTER Z A M R A Z E N SLAVE 1? 0 ▲ 1 VNITŘNÍ ▲ PAMĚŤ ▼ 0? 1 0 R O Z M R A Z E N 1? 0 0? 1 A poslední otázka: „Jak se bude chovat klopný obvod MASTER – SLAVE v paměťovém stavu? “ Velmi stručné: „Ať už je ve vnitřní paměti cokoliv, a ať se to tam dostalo jakkoliv, tak při sestupné hraně na vstupu T se to tam zamrazí a přenese na výstupy rozmrazeného klopného obvodu SLAVE, tedy na finální výstupy. “ Vstup T pak nazýváme dynamický, vstupy R, S jsou statické.

Použitá literatura 1. Antošová, M. , Davídek V. : Číslicová technika. Nakl. KOPP, 2009.