Muon TrackFinder Trigger Darin Acosta University of Florida

- Slides: 18

Muon Track-Finder Trigger Darin Acosta University of Florida June, 2002 US CMS DOE/NSF Review: June 2002, Darin Acosta, University of Florida 1

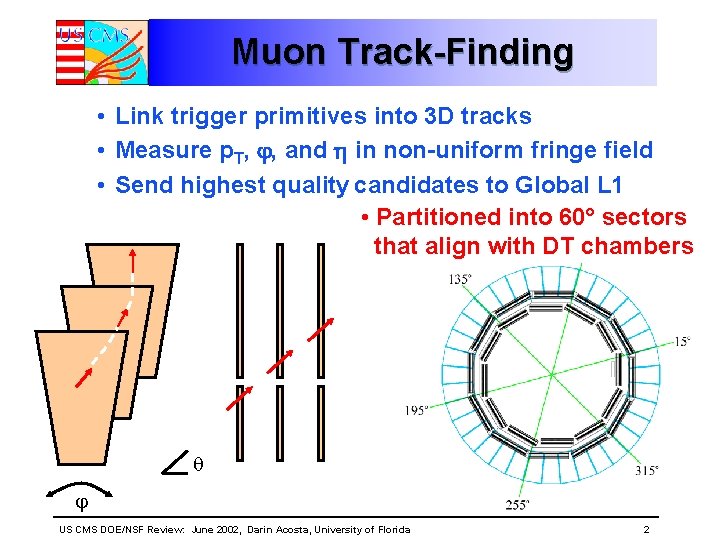

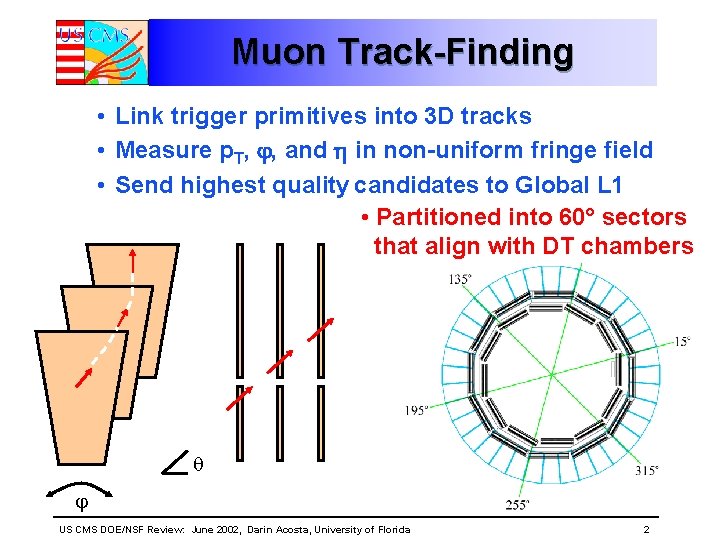

Muon Track-Finding • Link trigger primitives into 3 D tracks • Measure p. T, , and in non-uniform fringe field • Send highest quality candidates to Global L 1 • Partitioned into 60° sectors that align with DT chambers US CMS DOE/NSF Review: June 2002, Darin Acosta, University of Florida 2

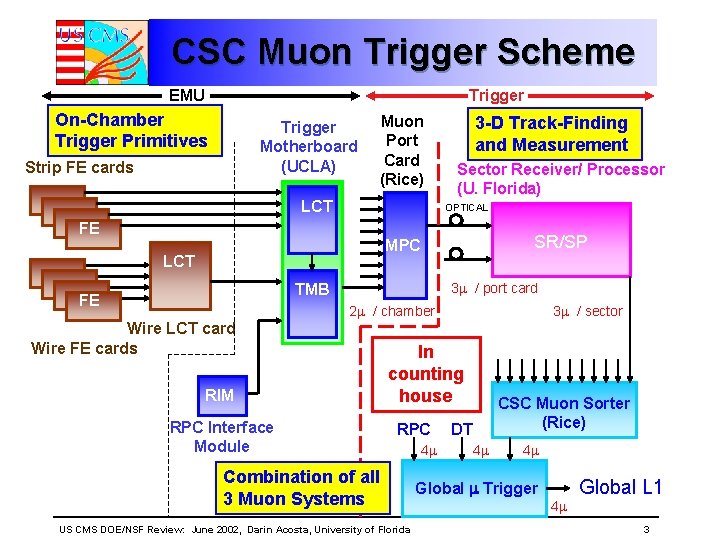

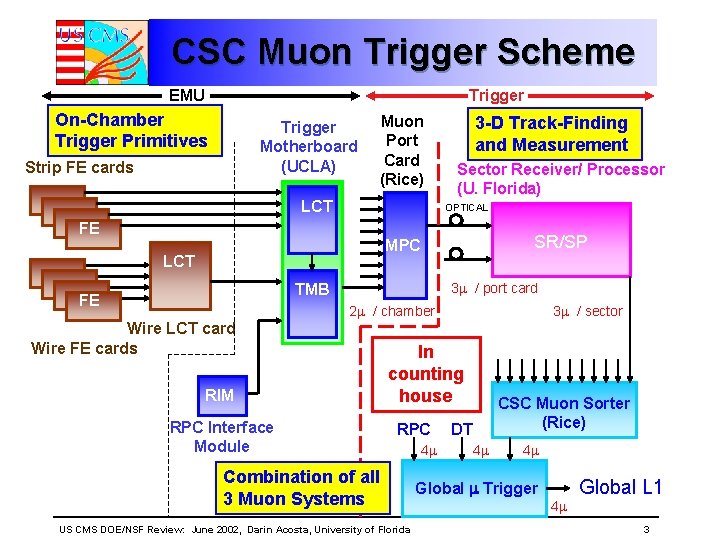

CSC Muon Trigger Scheme EMU Trigger On-Chamber Trigger Primitives Trigger Motherboard (UCLA) Strip FE cards Muon Port Card (Rice) LCT 3 -D Track-Finding and Measurement Sector Receiver/ Processor (U. Florida) OPTICAL FE SR/SP MPC LCT 3 / port card TMB FE SP 2 / chamber Wire LCT card Wire FE cards RIM RPC Interface Module 3 / sector In counting house RPC Combination of all 3 Muon Systems US CMS DOE/NSF Review: June 2002, Darin Acosta, University of Florida 4 CSC Muon Sorter (Rice) DT 4 4 Global Trigger 4 Global L 1 3

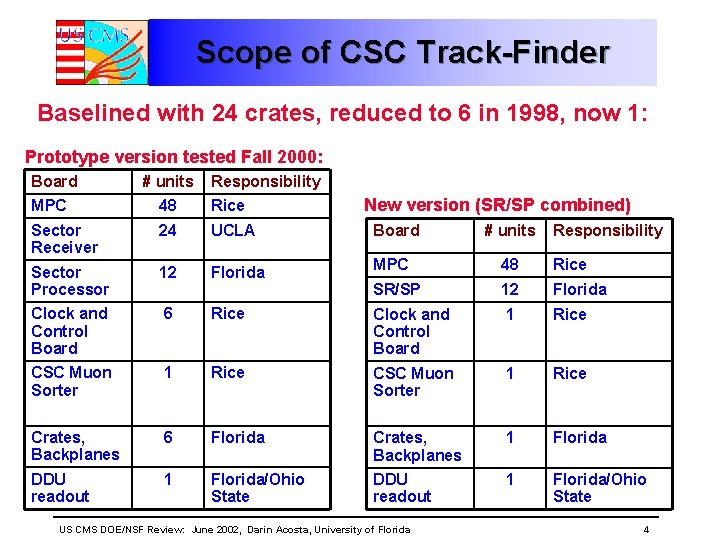

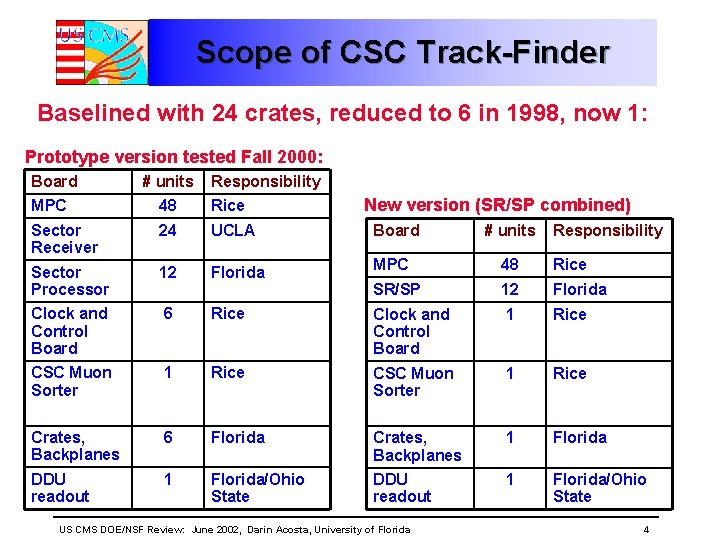

Scope of CSC Track-Finder Baselined with 24 crates, reduced to 6 in 1998, now 1: Prototype version tested Fall 2000: Board # units Responsibility New version (SR/SP combined) MPC 48 Rice Sector Receiver 24 UCLA Board Sector Processor 12 Florida MPC 48 Rice SR/SP 12 Florida Clock and Control Board 6 Rice Clock and Control Board 1 Rice CSC Muon Sorter 1 Rice Crates, Backplanes 6 Florida Crates, Backplanes 1 Florida DDU readout 1 Florida/Ohio State US CMS DOE/NSF Review: June 2002, Darin Acosta, University of Florida # units Responsibility 4

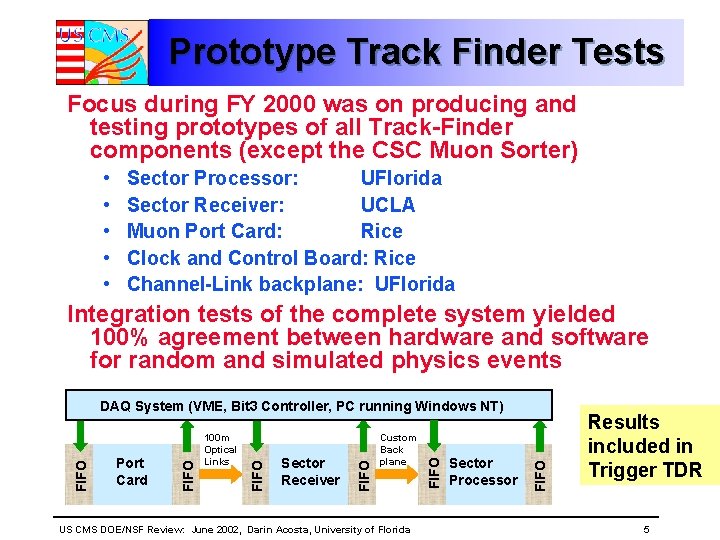

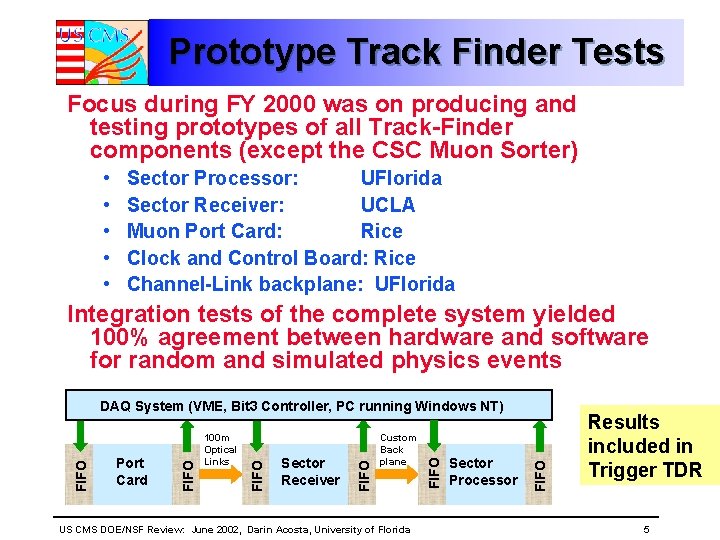

Prototype Track Finder Tests Focus during FY 2000 was on producing and testing prototypes of all Track-Finder components (except the CSC Muon Sorter) • • • Sector Processor: UFlorida Sector Receiver: UCLA Muon Port Card: Rice Clock and Control Board: Rice Channel-Link backplane: UFlorida Integration tests of the complete system yielded 100% agreement between hardware and software for random and simulated physics events US CMS DOE/NSF Review: June 2002, Darin Acosta, University of Florida Sector Processor FIFO Custom Back plane FIFO Sector Receiver FIFO 100 m Optical Links FIFO Port Card FIFO DAQ System (VME, Bit 3 Controller, PC running Windows NT) Results included in Trigger TDR 5

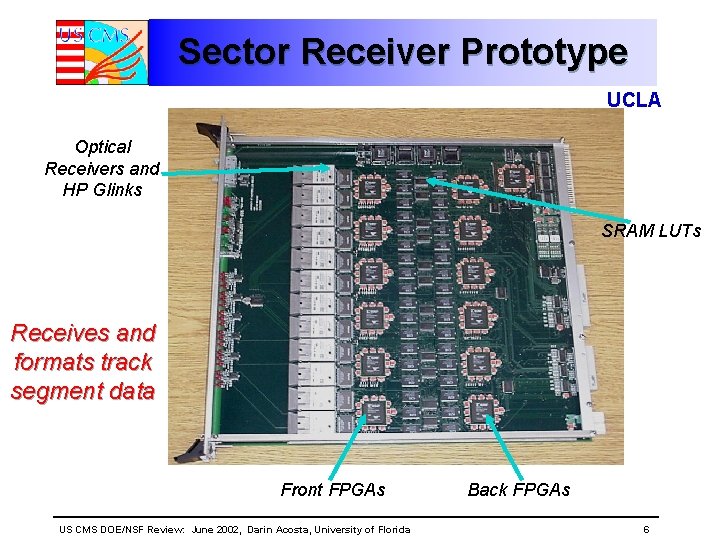

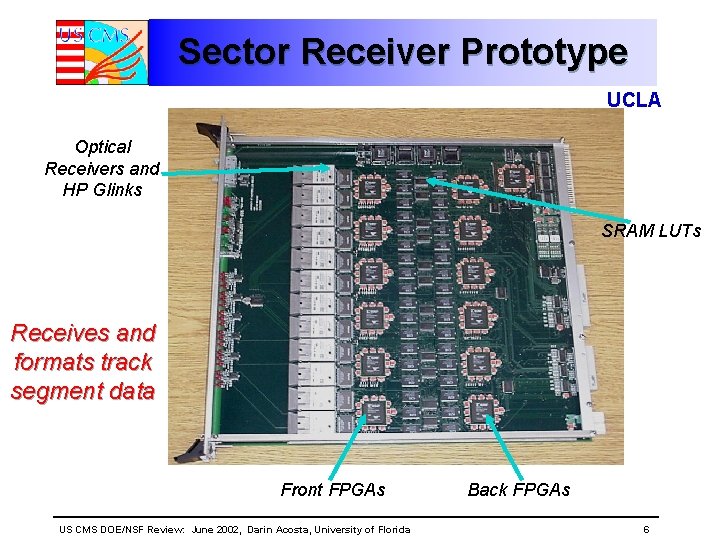

Sector Receiver Prototype UCLA Optical Receivers and HP Glinks SRAM LUTs Receives and formats track segment data Front FPGAs US CMS DOE/NSF Review: June 2002, Darin Acosta, University of Florida Back FPGAs 6

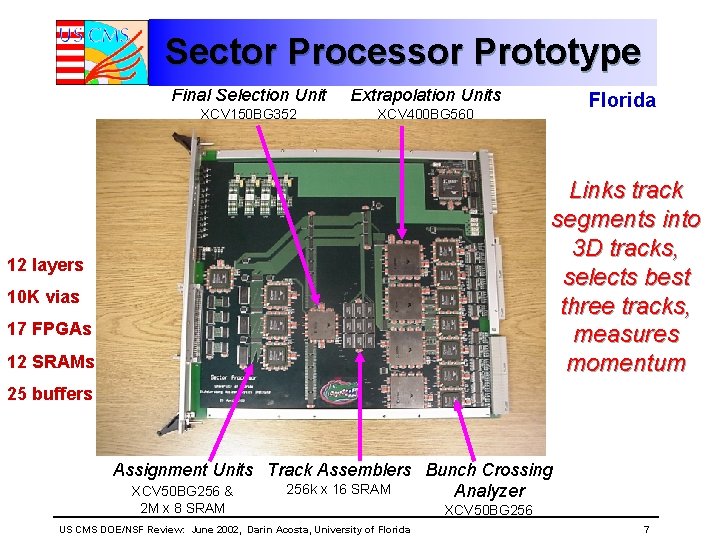

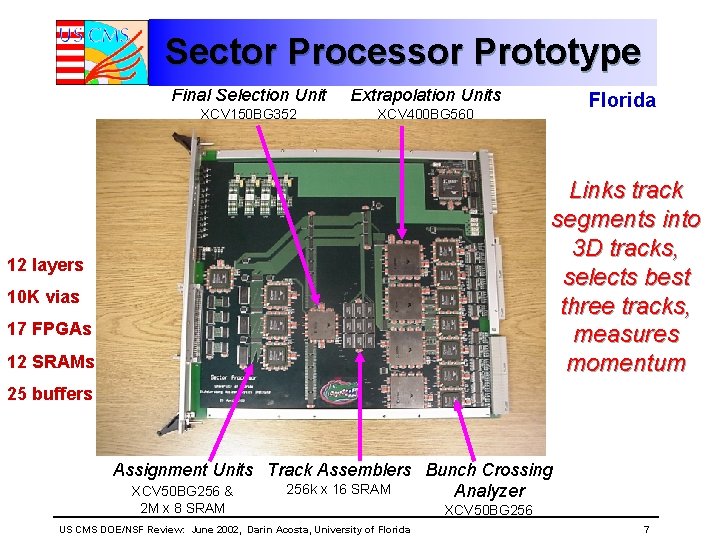

Sector Processor Prototype Final Selection Unit Extrapolation Units XCV 150 BG 352 XCV 400 BG 560 Florida Links track segments into 3 D tracks, selects best three tracks, measures momentum 12 layers 10 K vias 17 FPGAs 12 SRAMs 25 buffers Assignment Units Track Assemblers Bunch Crossing 256 k x 16 SRAM XCV 50 BG 256 & Analyzer 2 M x 8 SRAM US CMS DOE/NSF Review: June 2002, Darin Acosta, University of Florida XCV 50 BG 256 7

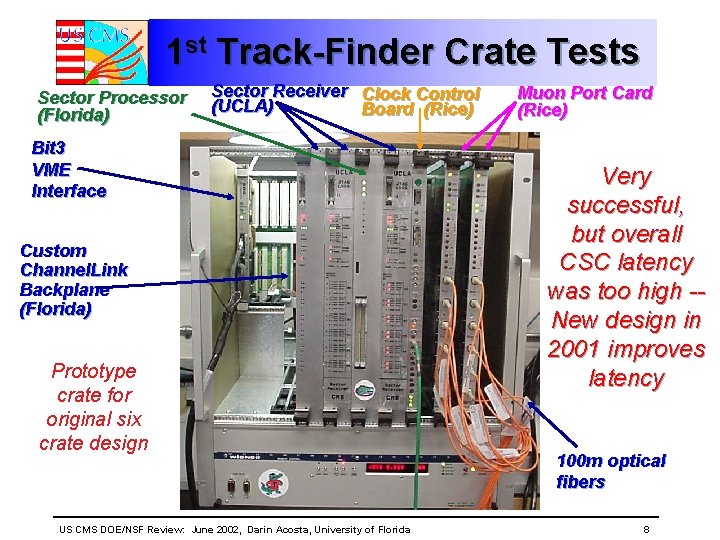

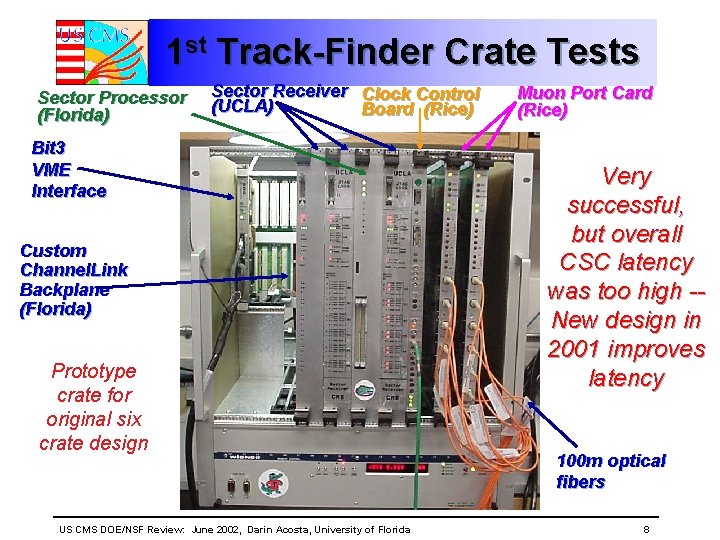

1 st Track-Finder Crate Tests Sector Processor (Florida) Sector Receiver Clock Control (UCLA) Board (Rice) Bit 3 VME Interface Custom Channel. Link Backplane (Florida) Prototype crate for original six crate design US CMS DOE/NSF Review: June 2002, Darin Acosta, University of Florida Muon Port Card (Rice) Very successful, but overall CSC latency was too high -New design in 2001 improves latency 100 m optical fibers 8

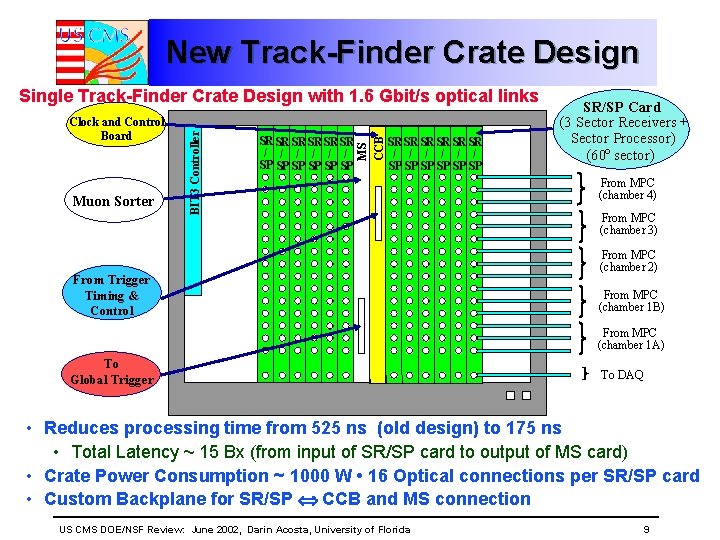

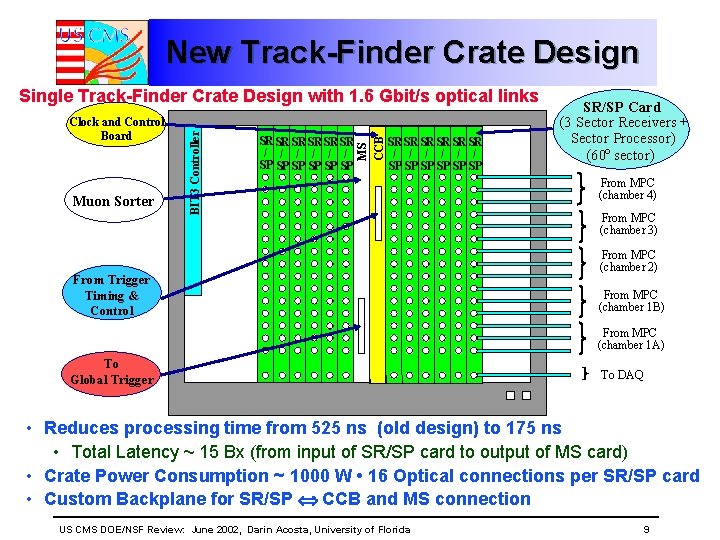

New Track-Finder Crate Design Muon Sorter SR SR SR / / / SP SP SP MS CCB Clock and Control Board BIT 3 Controller Single Track-Finder Crate Design with 1. 6 Gbit/s optical links SR SR SR / / / SP SP SP From Trigger Timing & Control SR/SP Card (3 Sector Receivers + Sector Processor) (60° sector) From MPC (chamber 4) From MPC (chamber 3) From MPC (chamber 2) From MPC (chamber 1 B) From MPC (chamber 1 A) To Global Trigger To DAQ • Reduces processing time from 525 ns (old design) to 175 ns • Total Latency ~ 15 Bx (from input of SR/SP card to output of MS card) • Crate Power Consumption ~ 1000 W • 16 Optical connections per SR/SP card • Custom Backplane for SR/SP CCB and MS connection US CMS DOE/NSF Review: June 2002, Darin Acosta, University of Florida 9

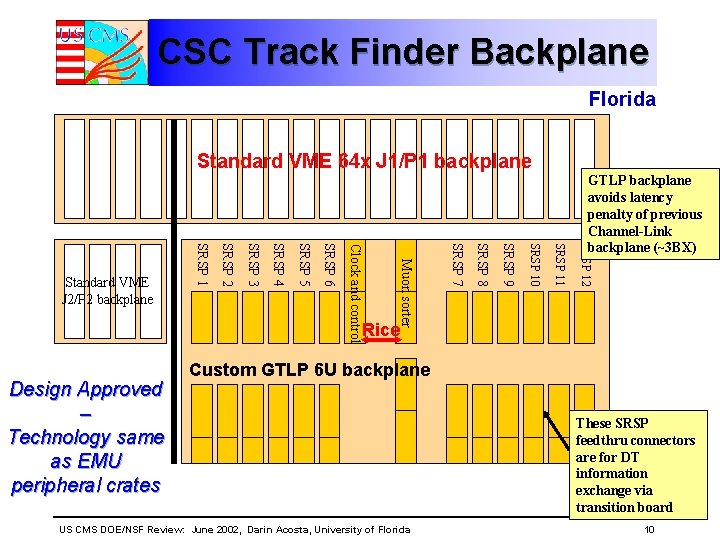

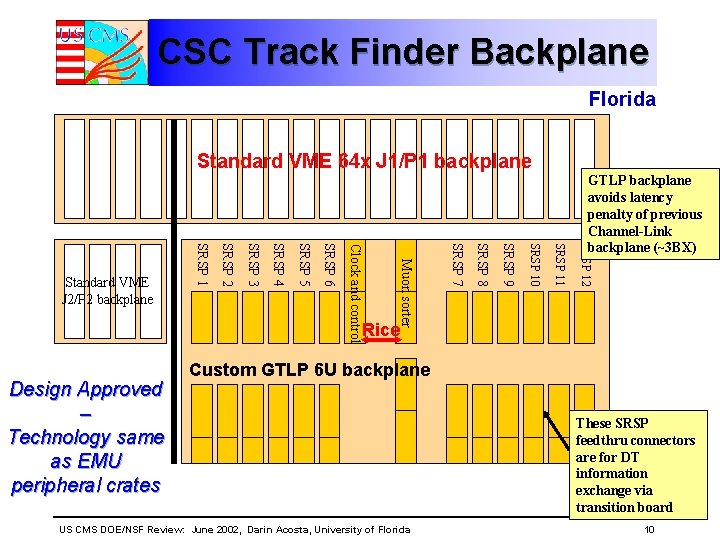

CSC Track Finder Backplane Florida Standard VME 64 x J 1/P 1 backplane SRSP 12 SRSP 11 SRSP 10 SRSP 9 SRSP 8 SRSP 7 Muon sorter Clock and control SRSP 6 SRSP 5 SRSP 4 SRSP 3 SRSP 2 SRSP 1 Standard VME J 2/P 2 backplane GTLP backplane avoids latency penalty of previous Channel-Link backplane (~3 BX) Rice Design Approved – Technology same as EMU peripheral crates Custom GTLP 6 U backplane US CMS DOE/NSF Review: June 2002, Darin Acosta, University of Florida These SRSP feedthru connectors are for DT information exchange via transition board 10

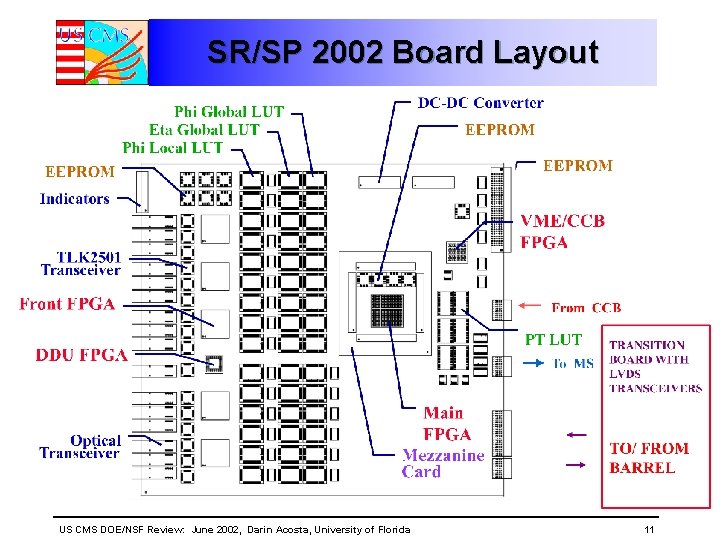

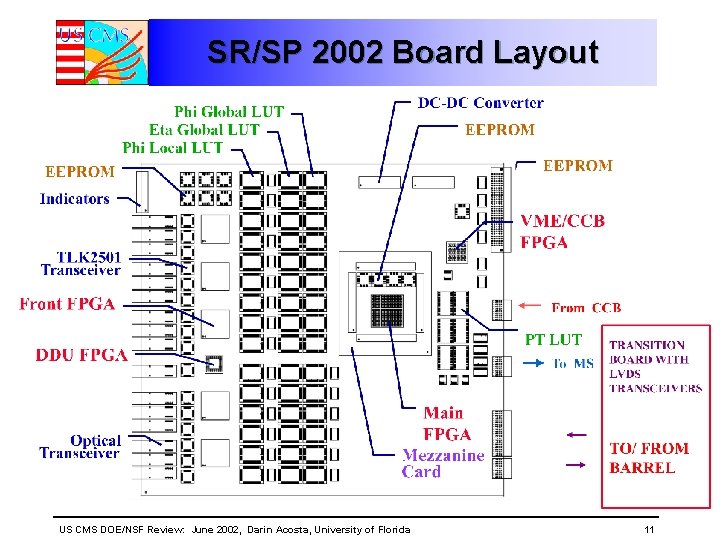

SR/SP 2002 Board Layout US CMS DOE/NSF Review: June 2002, Darin Acosta, University of Florida 11

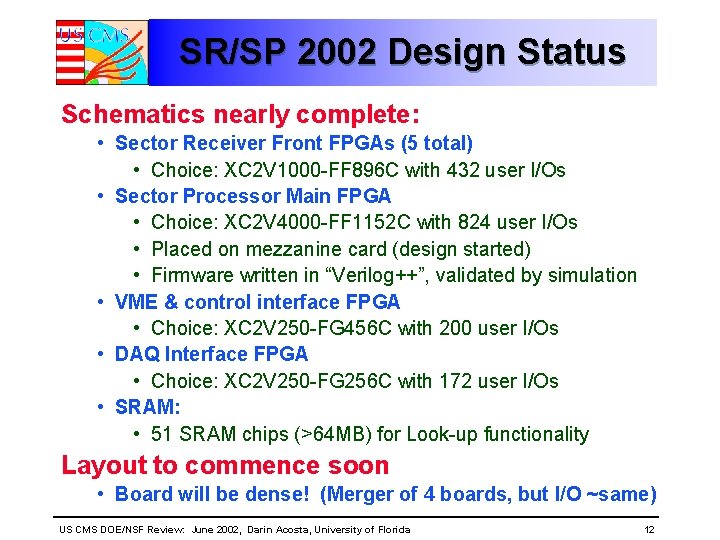

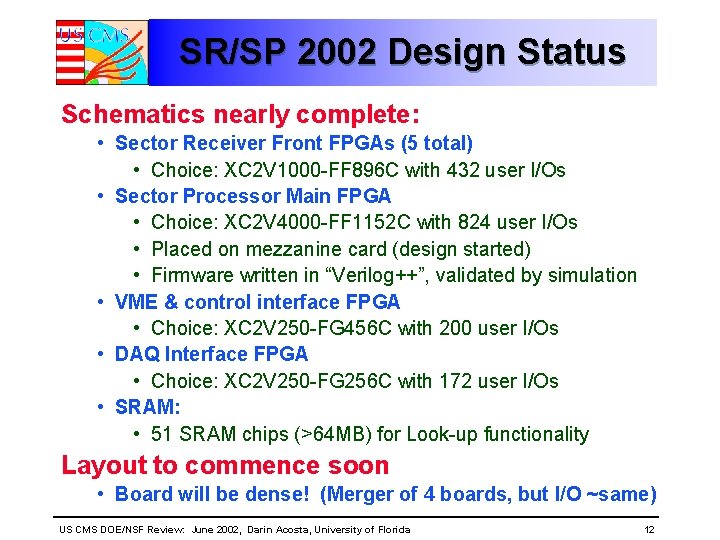

SR/SP 2002 Design Status Schematics nearly complete: • Sector Receiver Front FPGAs (5 total) • Choice: XC 2 V 1000 -FF 896 C with 432 user I/Os • Sector Processor Main FPGA • Choice: XC 2 V 4000 -FF 1152 C with 824 user I/Os • Placed on mezzanine card (design started) • Firmware written in “Verilog++”, validated by simulation • VME & control interface FPGA • Choice: XC 2 V 250 -FG 456 C with 200 user I/Os • DAQ Interface FPGA • Choice: XC 2 V 250 -FG 256 C with 172 user I/Os • SRAM: • 51 SRAM chips (>64 MB) for Look-up functionality Layout to commence soon • Board will be dense! (Merger of 4 boards, but I/O ~same) US CMS DOE/NSF Review: June 2002, Darin Acosta, University of Florida 12

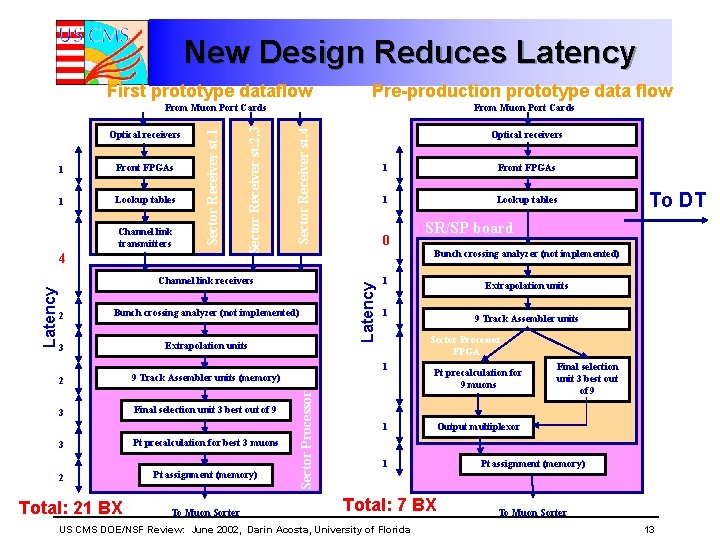

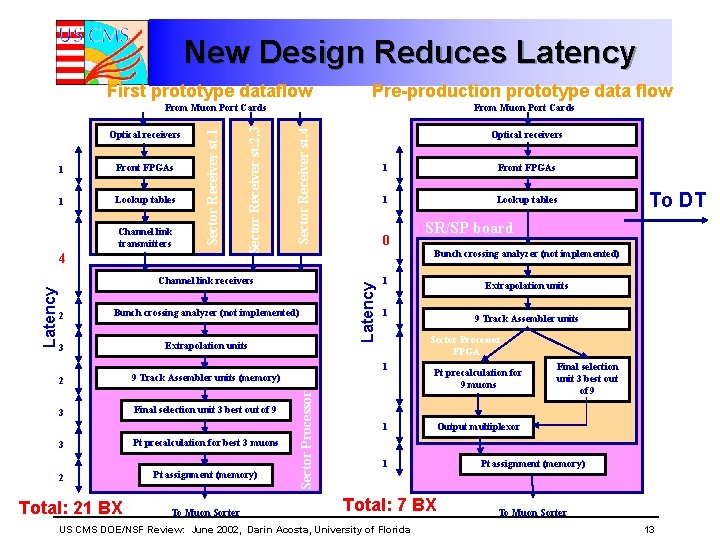

New Design Reduces Latency First prototype dataflow Pre-production prototype data flow 1 Lookup tables Channel link transmitters 4 Bunch crossing analyzer (not implemented) 3 Extrapolation units 2 9 Track Assembler units (memory) 3 Final selection unit 3 best out of 9 2 Pt assignment (memory) Total: 21 BX To Muon Sorter Front FPGAs 1 Lookup tables 0 To DT SR/SP board 1 Extrapolation units 1 9 Track Assembler units Sector Processor FPGA 1 Sector Processor Latency 2 Pt precalculation for best 3 muons 1 Bunch crossing analyzer (not implemented) Channel link receivers 3 Optical receivers Latency Front FPGAs From Muon Port Cards Sector Receiver st. 4 1 Sector Receiver st. 2, 3 Optical receivers Sector Receiver st. 1 From Muon Port Cards 1 Pt precalculation for 9 muons Output multiplexor 1 Total: 7 BX US CMS DOE/NSF Review: June 2002, Darin Acosta, University of Florida Final selection unit 3 best out of 9 Pt assignment (memory) To Muon Sorter 13

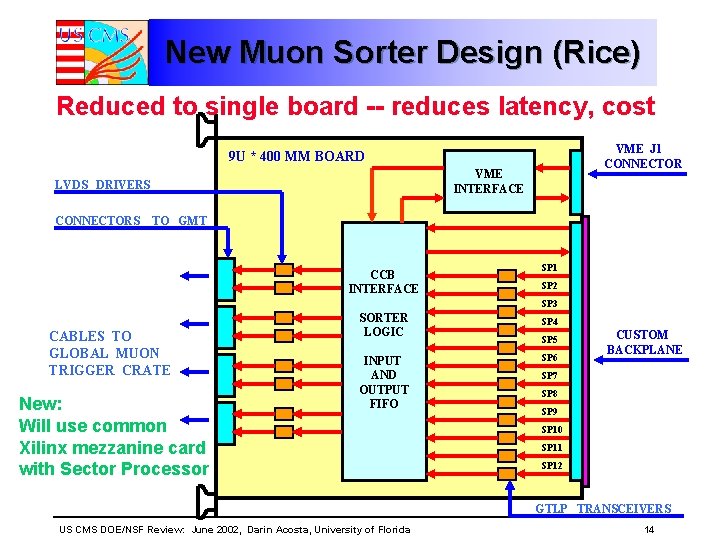

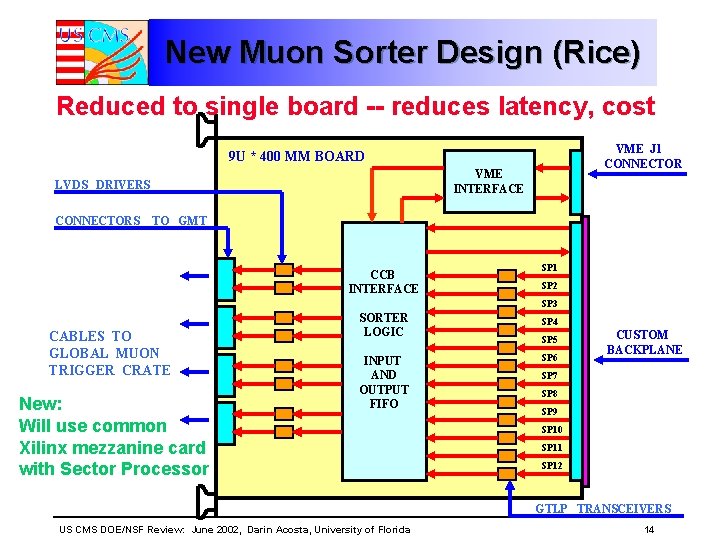

New Muon Sorter Design (Rice) Reduced to single board -- reduces latency, cost VME J 1 CONNECTOR 9 U * 400 MM BOARD VME INTERFACE LVDS DRIVERS CONNECTORS TO GMT CCB INTERFACE SP 1 SP 2 SP 3 CABLES TO GLOBAL MUON TRIGGER CRATE New: Will use common Xilinx mezzanine card with Sector Processor SORTER LOGIC INPUT AND OUTPUT FIFO SP 4 SP 5 SP 6 CUSTOM BACKPLANE SP 7 SP 8 SP 9 SP 10 SP 11 SP 12 GTLP TRANSCEIVERS US CMS DOE/NSF Review: June 2002, Darin Acosta, University of Florida 14

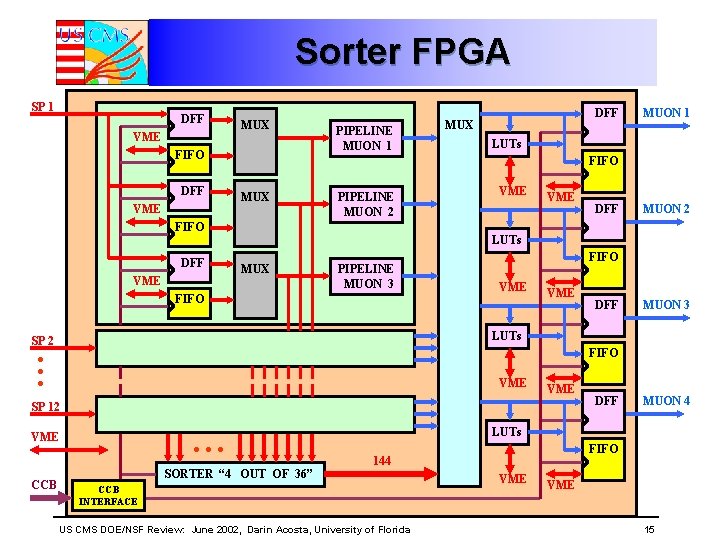

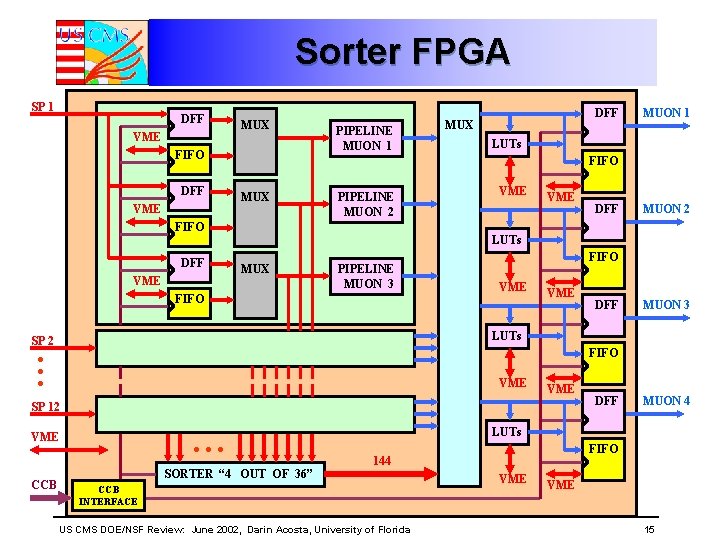

Sorter FPGA SP 1 DFF VME MUX FIFO DFF VME PIPELINE MUON 1 VME MUX PIPELINE MUON 2 LUTs VME DFF MUON 2 LUTs MUX PIPELINE MUON 3 FIFO VME DFF MUON 3 LUTs . . . SP 2 FIFO VME SP 12 . . . VME CCB MUON 1 FIFO DFF MUX SORTER “ 4 OUT OF 36” DFF MUON 4 LUTs FIFO 144 CCB INTERFACE US CMS DOE/NSF Review: June 2002, Darin Acosta, University of Florida VME 15

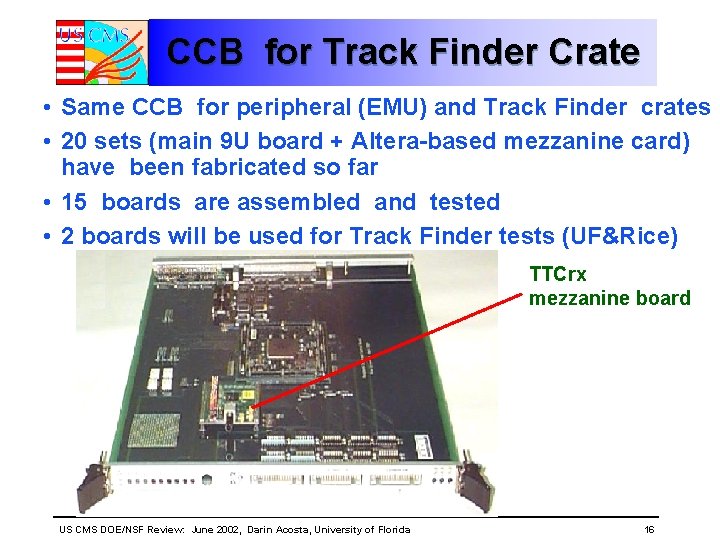

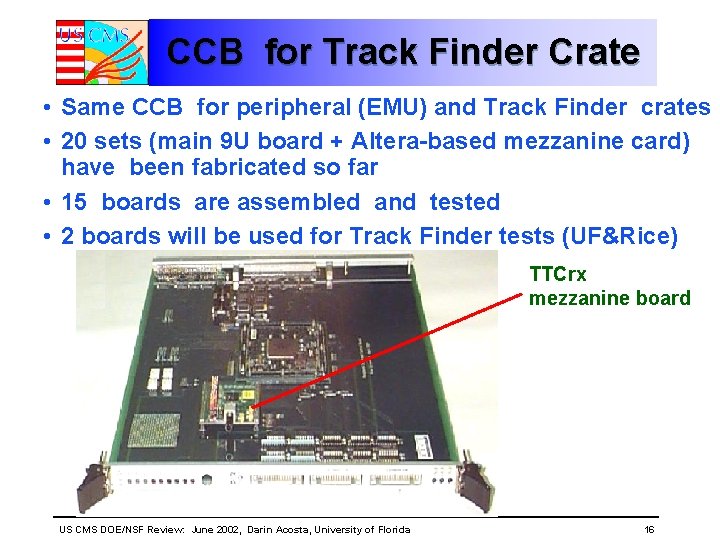

CCB for Track Finder Crate • Same CCB for peripheral (EMU) and Track Finder crates • 20 sets (main 9 U board + Altera-based mezzanine card) have been fabricated so far • 15 boards are assembled and tested • 2 boards will be used for Track Finder tests (UF&Rice) TTCrx mezzanine board US CMS DOE/NSF Review: June 2002, Darin Acosta, University of Florida 16

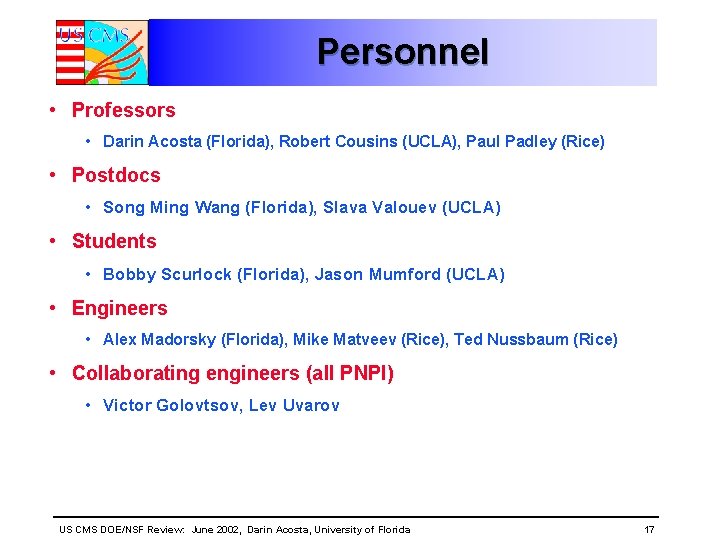

Personnel • Professors • Darin Acosta (Florida), Robert Cousins (UCLA), Paul Padley (Rice) • Postdocs • Song Ming Wang (Florida), Slava Valouev (UCLA) • Students • Bobby Scurlock (Florida), Jason Mumford (UCLA) • Engineers • Alex Madorsky (Florida), Mike Matveev (Rice), Ted Nussbaum (Rice) • Collaborating engineers (all PNPI) • Victor Golovtsov, Lev Uvarov US CMS DOE/NSF Review: June 2002, Darin Acosta, University of Florida 17

Conclusions • First Track Finder system prototyped successfully in Fall 2000 • Exact match to CMS OO simulation package • Second generation pre-production prototype is well underway with significant improvements • Present and future activities • 2001: R&D on optical links, FPGA logic, memory look-ups, backplane technology, and DAQ readout • 2002: build the 2 nd generation prototype • 2003: test with multiple CSC chambers, cosmic rays and/or structured beam, tweaks for final design (if necessary) • 2004: full production • 2005: installation • No trouble expected: all-digital system with off-the-shelf components, well-defined internal and external interfaces, and a stable and capable engineering team US CMS DOE/NSF Review: June 2002, Darin Acosta, University of Florida 18