Status of the CSC TrackFinder Darin Acosta University

- Slides: 13

Status of the CSC Track-Finder Darin Acosta University of Florida n n

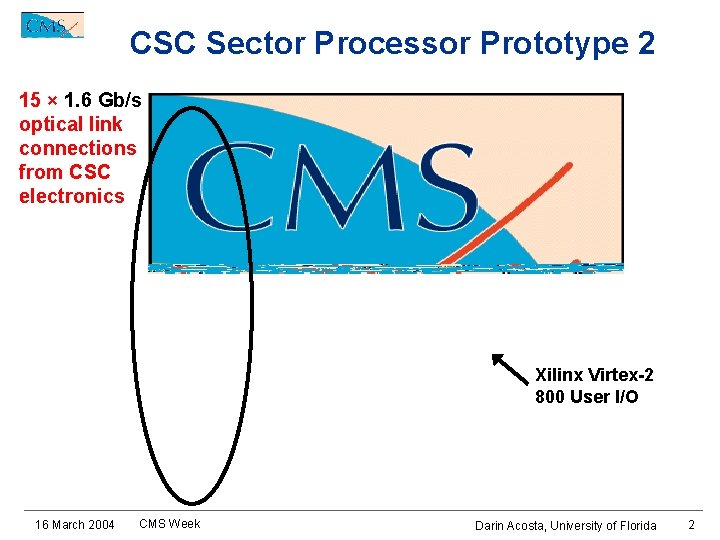

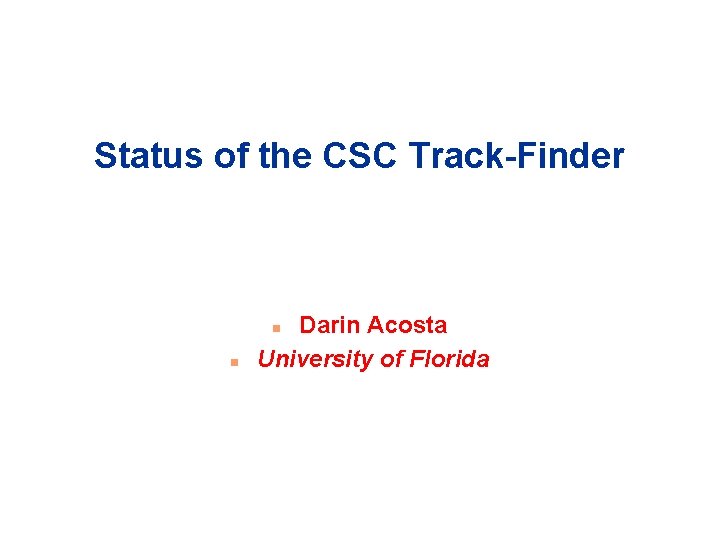

CSC Sector Processor Prototype 2 15 × 1. 6 Gb/s optical link connections from CSC electronics Xilinx Virtex-2 800 User I/O 16 March 2004 CMS Week Darin Acosta, University of Florida 2

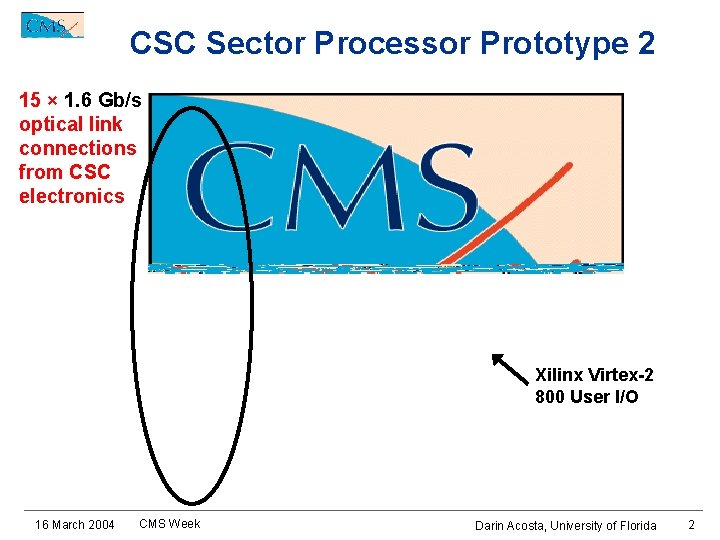

Test Status n n Basically all functionality has been successfully tested Optical links: u n LUT Tests: u n Validated loading and read-back of all 45 SR LUTs and 3 PT LUTs using random numbers and simulated muon LUT files SP Track-Finding Logic Tests: u u n Demonstrated to work error-free during Sept’ 03 beam test with home-built PLL+VCXO and with latest QPLL (TTCRq) Downloaded random data and simulated muon data into 512 BX input FIFO, read-back and compare output FIFO No discrepancies in 1. 2 M random events No discrepancies in 13 K single muon events, or 4 K triple muon events (3 single muons piled up) Verilog model also “installed” into ORCA Complete functionality test u Input FIFO LUTs Track-Finding output FIFO 16 March 2004 CMS Week Darin Acosta, University of Florida 3

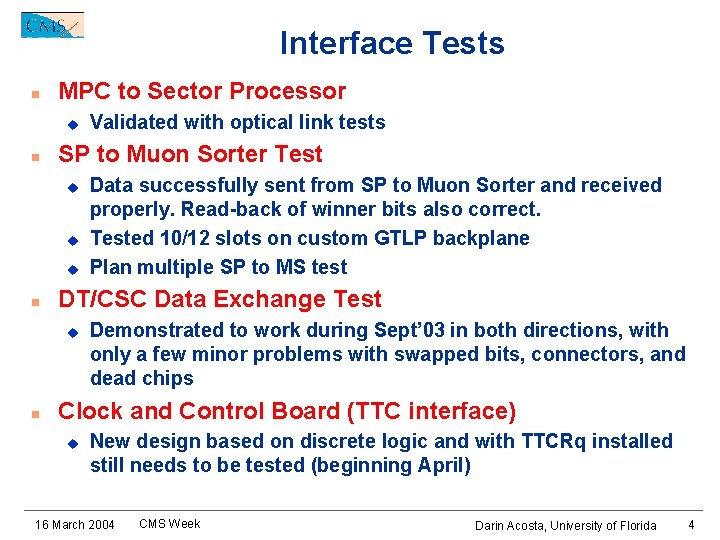

Interface Tests n MPC to Sector Processor u n SP to Muon Sorter Test u u u n Data successfully sent from SP to Muon Sorter and received properly. Read-back of winner bits also correct. Tested 10/12 slots on custom GTLP backplane Plan multiple SP to MS test DT/CSC Data Exchange Test u n Validated with optical link tests Demonstrated to work during Sept’ 03 in both directions, with only a few minor problems with swapped bits, connectors, and dead chips Clock and Control Board (TTC interface) u New design based on discrete logic and with TTCRq installed still needs to be tested (beginning April) 16 March 2004 CMS Week Darin Acosta, University of Florida 4

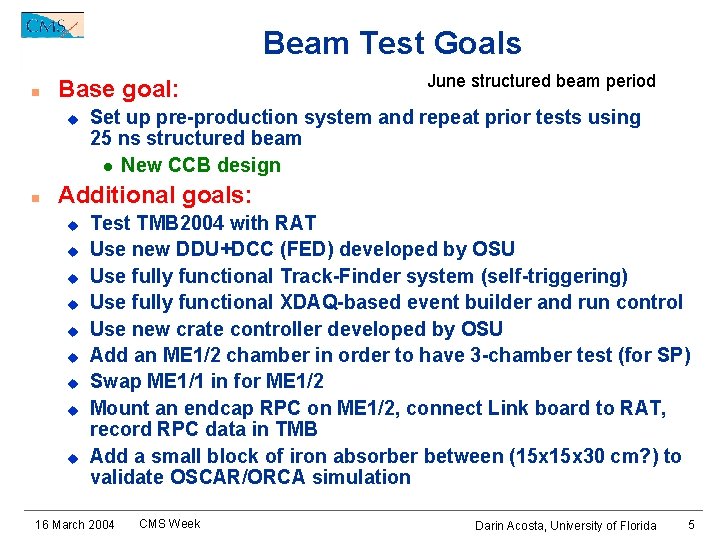

Beam Test Goals n Base goal: u n June structured beam period Set up pre-production system and repeat prior tests using 25 ns structured beam l New CCB design Additional goals: u u u u u Test TMB 2004 with RAT Use new DDU+DCC (FED) developed by OSU Use fully functional Track-Finder system (self-triggering) Use fully functional XDAQ-based event builder and run control Use new crate controller developed by OSU Add an ME 1/2 chamber in order to have 3 -chamber test (for SP) Swap ME 1/1 in for ME 1/2 Mount an endcap RPC on ME 1/2, connect Link board to RAT, record RPC data in TMB Add a small block of iron absorber between (15 x 30 cm? ) to validate OSCAR/ORCA simulation 16 March 2004 CMS Week Darin Acosta, University of Florida 5

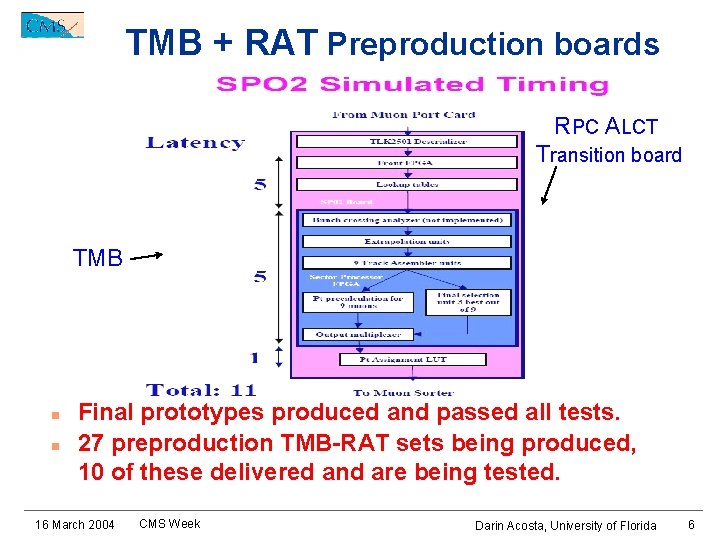

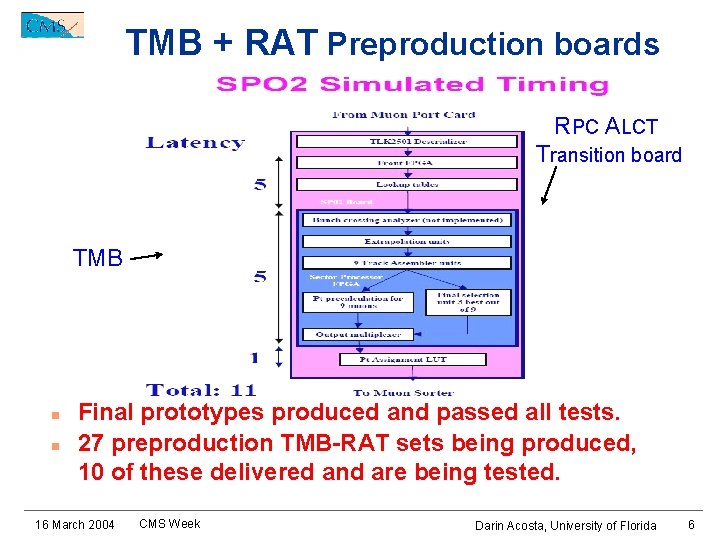

TMB + RAT Preproduction boards RPC ALCT Transition board TMB n n Final prototypes produced and passed all tests. 27 preproduction TMB-RAT sets being produced, 10 of these delivered and are being tested. 16 March 2004 CMS Week Darin Acosta, University of Florida 6

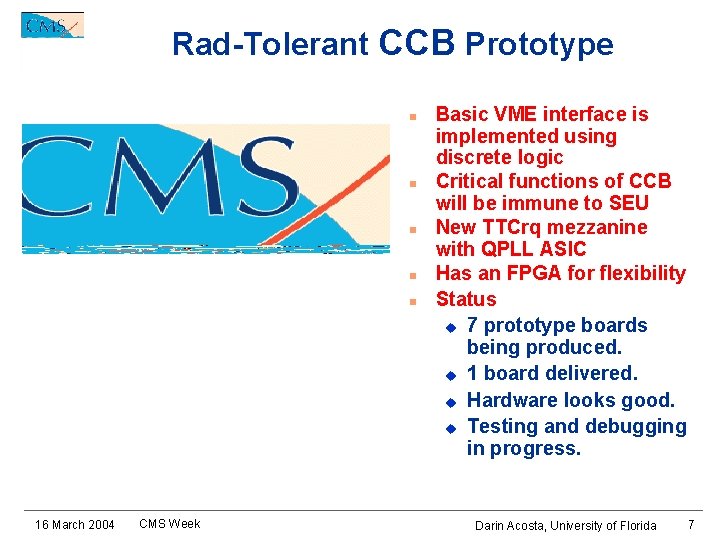

Rad-Tolerant CCB Prototype n n n 16 March 2004 CMS Week Basic VME interface is implemented using discrete logic Critical functions of CCB will be immune to SEU New TTCrq mezzanine with QPLL ASIC Has an FPGA for flexibility Status u 7 prototype boards being produced. u 1 board delivered. u Hardware looks good. u Testing and debugging in progress. Darin Acosta, University of Florida 7

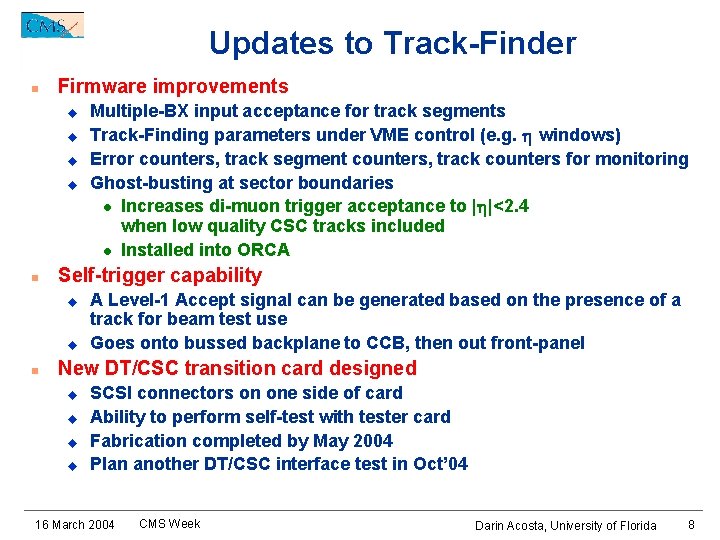

Updates to Track-Finder n Firmware improvements u u n Self-trigger capability u u n Multiple-BX input acceptance for track segments Track-Finding parameters under VME control (e. g. windows) Error counters, track segment counters, track counters for monitoring Ghost-busting at sector boundaries l Increases di-muon trigger acceptance to | |<2. 4 when low quality CSC tracks included l Installed into ORCA A Level-1 Accept signal can be generated based on the presence of a track for beam test use Goes onto bussed backplane to CCB, then out front-panel New DT/CSC transition card designed u u SCSI connectors on one side of card Ability to perform self-test with tester card Fabrication completed by May 2004 Plan another DT/CSC interface test in Oct’ 04 16 March 2004 CMS Week Darin Acosta, University of Florida 8

New DT/CSC Transition Board Layout 16 March 2004 CMS Week Darin Acosta, University of Florida 9

CSC Track-Finding Latency 11 25 ns, or 275 ns 16 March 2004 CMS Week Darin Acosta, University of Florida 10

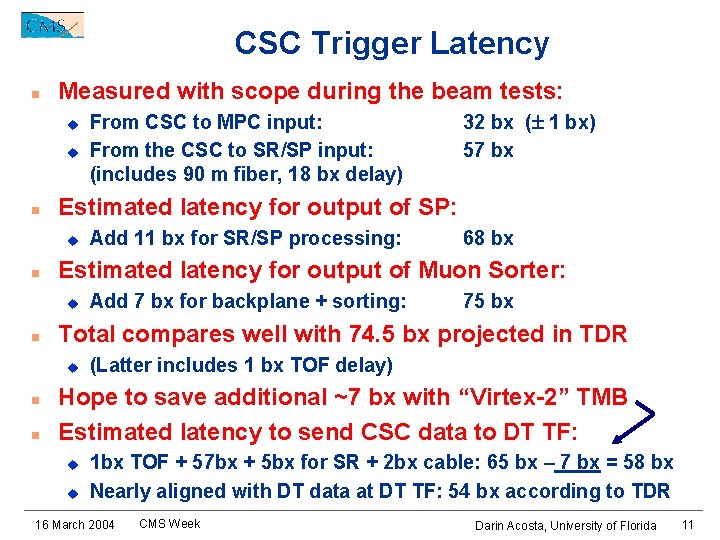

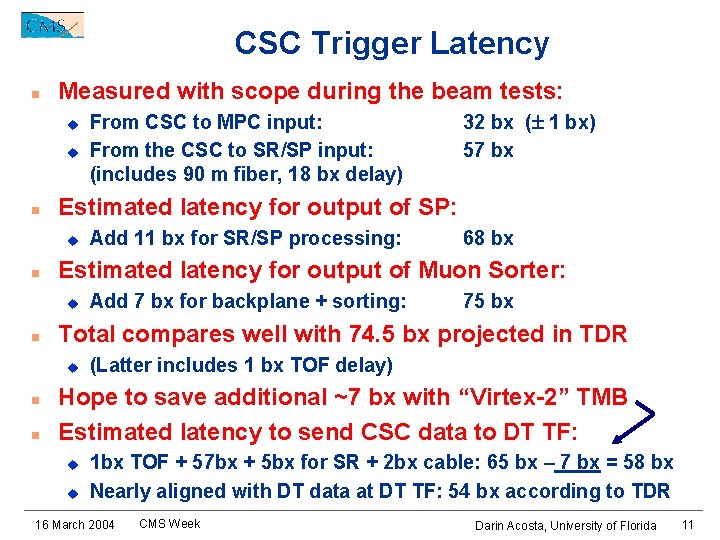

CSC Trigger Latency n Measured with scope during the beam tests: u u n n 68 bx Add 7 bx for backplane + sorting: 75 bx Total compares well with 74. 5 bx projected in TDR u n Add 11 bx for SR/SP processing: Estimated latency for output of Muon Sorter: u n 32 bx ( 1 bx) 57 bx Estimated latency for output of SP: u n From CSC to MPC input: From the CSC to SR/SP input: (includes 90 m fiber, 18 bx delay) (Latter includes 1 bx TOF delay) Hope to save additional ~7 bx with “Virtex-2” TMB Estimated latency to send CSC data to DT TF: u u 1 bx TOF + 57 bx + 5 bx for SR + 2 bx cable: 65 bx – 7 bx = 58 bx Nearly aligned with DT data at DT TF: 54 bx according to TDR 16 March 2004 CMS Week Darin Acosta, University of Florida 11

CSC Track-Finder Rack Layout 16 March 2004 CMS Week Darin Acosta, University of Florida 12

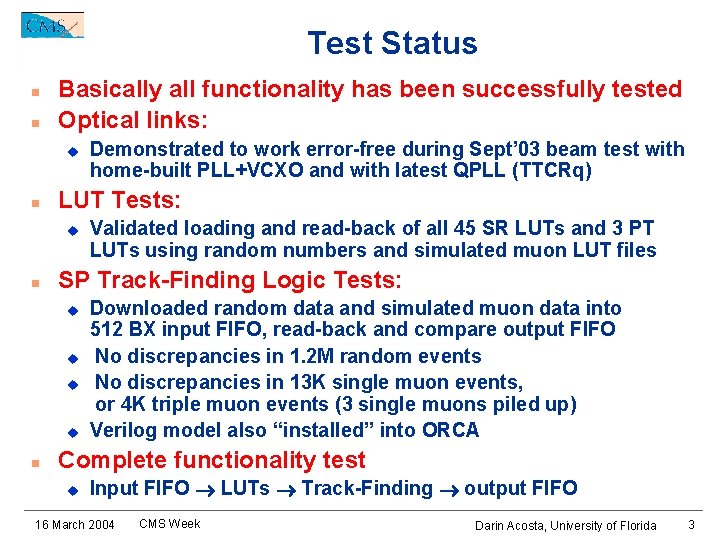

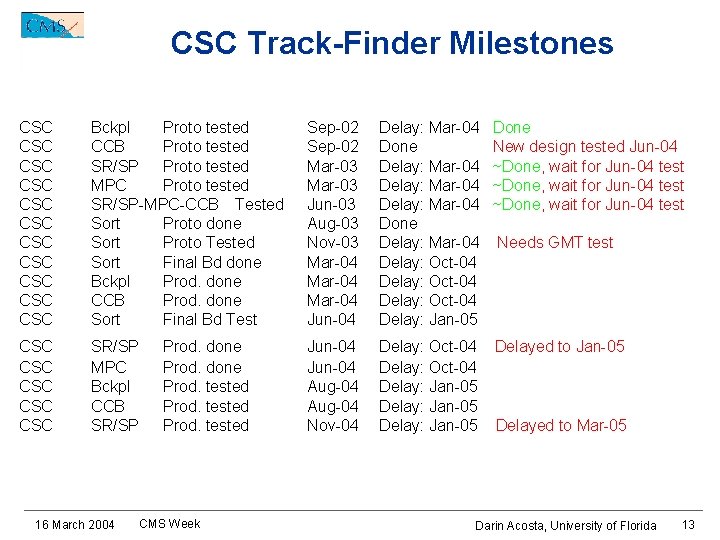

CSC Track-Finder Milestones CSC CSC CSC Bckpl Proto tested CCB Proto tested SR/SP Proto tested MPC Proto tested SR/SP-MPC-CCB Tested Sort Proto done Sort Proto Tested Sort Final Bd done Bckpl Prod. done CCB Prod. done Sort Final Bd Test Sep-02 Mar-03 Jun-03 Aug-03 Nov-03 Mar-04 Jun-04 Delay: Mar-04 Done Delay: Mar-04 Delay: Oct-04 Delay: Jan-05 Done New design tested Jun-04 ~Done, wait for Jun-04 test CSC CSC CSC SR/SP MPC Bckpl CCB SR/SP Jun-04 Aug-04 Nov-04 Delay: Oct-04 Delay: Jan-05 Delayed to Jan-05 16 March 2004 Prod. done Prod. tested CMS Week Needs GMT test Delayed to Mar-05 Darin Acosta, University of Florida 13