Magic An IndustrialStrength Logic Optimization Technology Mapping and

- Slides: 24

Magic An Industrial-Strength Logic Optimization, Technology Mapping, and Formal Verification System Alan Mishchenko UC Berkeley 1

Overview Motivation Ø Big picture Ø Problem representation Ø Algorithms Ø l l Sequential synthesis Combinational synthesis with choices Technology mapping Minimum-perturbation retiming Experimental results Ø Future work Ø 2

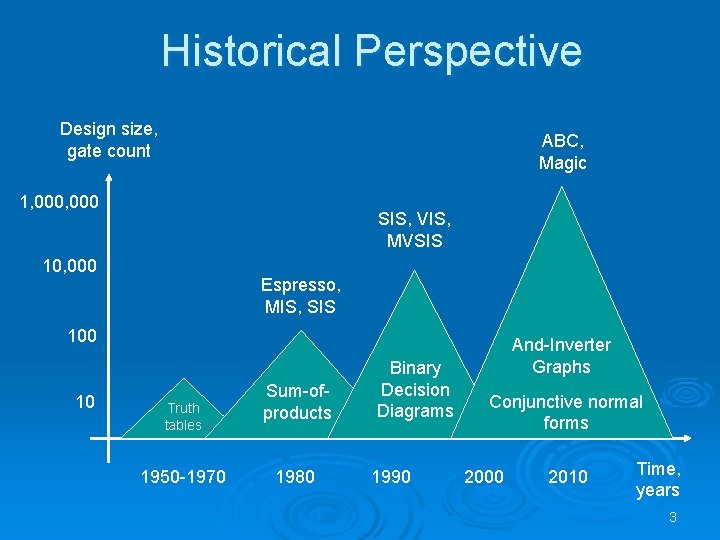

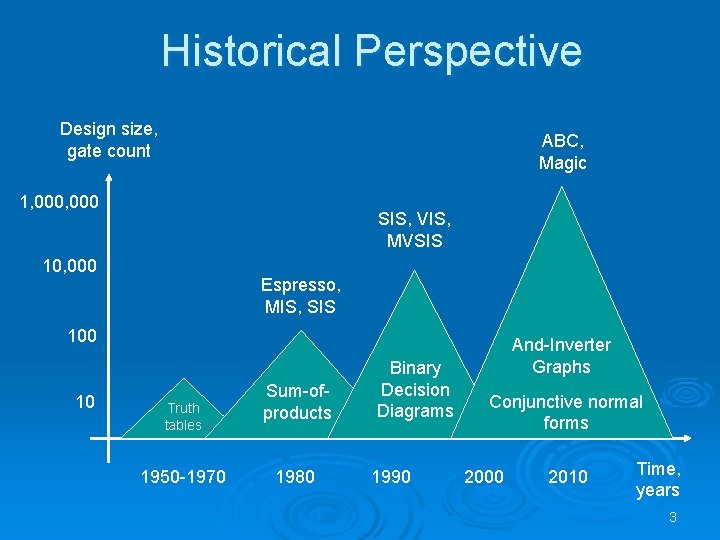

Historical Perspective Design size, gate count ABC, Magic 1, 000 SIS, VIS, MVSIS 10, 000 Espresso, MIS, SIS 100 10 Truth tables 1950 -1970 Sum-ofproducts 1980 Binary Decision Diagrams 1990 And-Inverter Graphs Conjunctive normal forms 2000 2010 Time, years 3

Motivation Ø ABC is a public-domain system for logic synthesis and formal verification under development at Berkeley since 2005 l Ø The baseline version of ABC is not applicable to industrial designs because it does not support l l Ø A successor of Espresso, MIS, SIS, VIS, MVSIS Complex flops Multiple clock domains Special objects (adders, RAMs, DSPs, etc) Standard-cell libraries A fresh start, called Magic, was taken in Fall 2009 l l l Includes new design database that supports these Integrates application packages for better memory/runtime Achieves better scalability 4

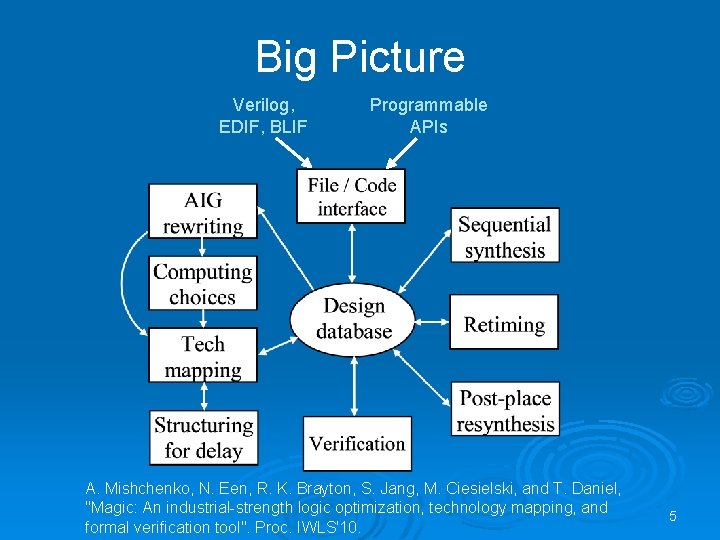

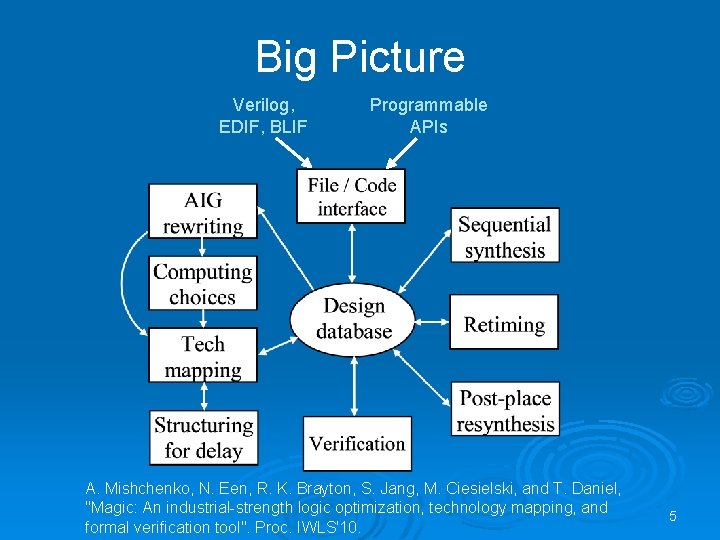

Big Picture Verilog, EDIF, BLIF Programmable APIs A. Mishchenko, N. Een, R. K. Brayton, S. Jang, M. Ciesielski, and T. Daniel, "Magic: An industrial-strength logic optimization, technology mapping, and formal verification tool". Proc. IWLS'10. 5

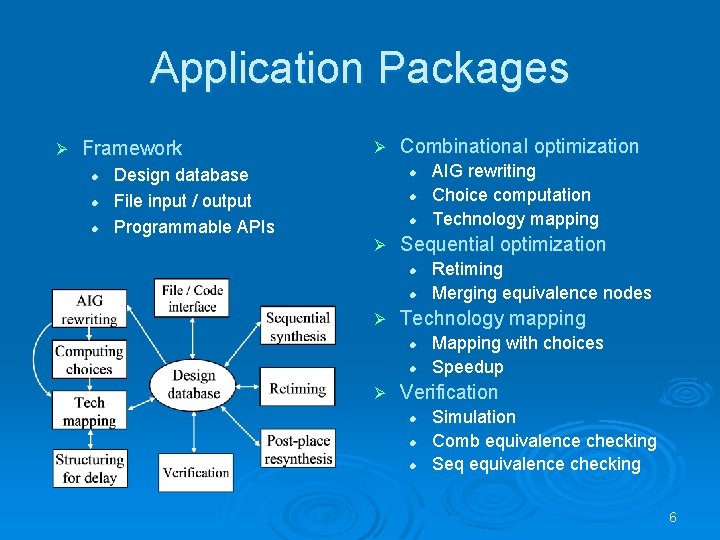

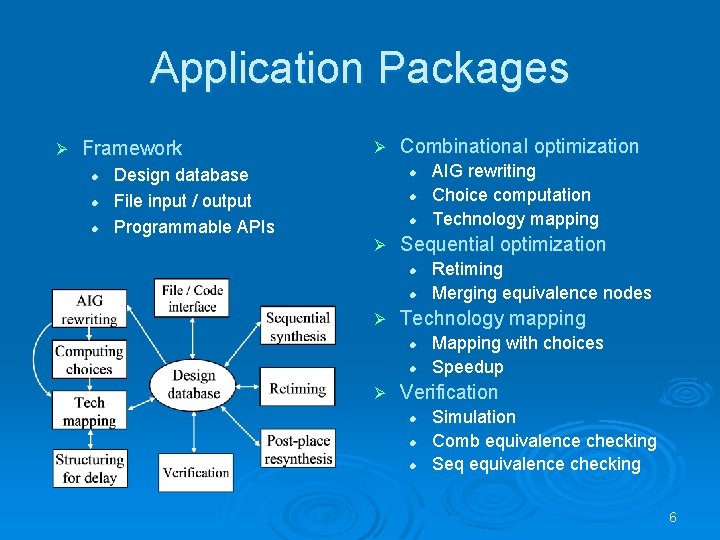

Application Packages Ø Framework l l l Design database File input / output Programmable APIs Ø Combinational optimization l l l Ø Sequential optimization l l Ø Retiming Merging equivalence nodes Technology mapping l l Ø AIG rewriting Choice computation Technology mapping Mapping with choices Speedup Verification l l l Simulation Comb equivalence checking Seq equivalence checking 6

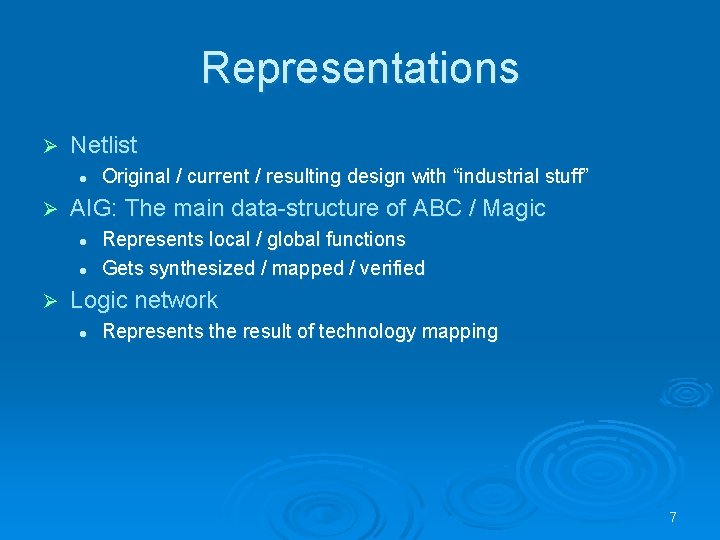

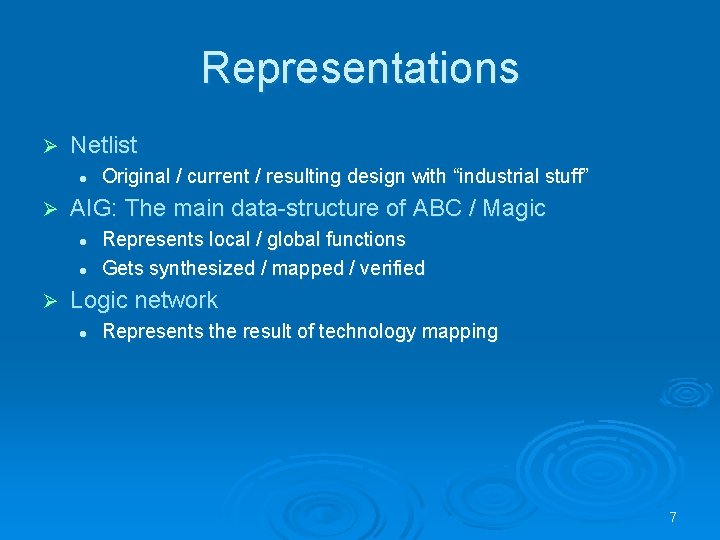

Representations Ø Netlist l Ø AIG: The main data-structure of ABC / Magic l l Ø Original / current / resulting design with “industrial stuff” Represents local / global functions Gets synthesized / mapped / verified Logic network l Represents the result of technology mapping 7

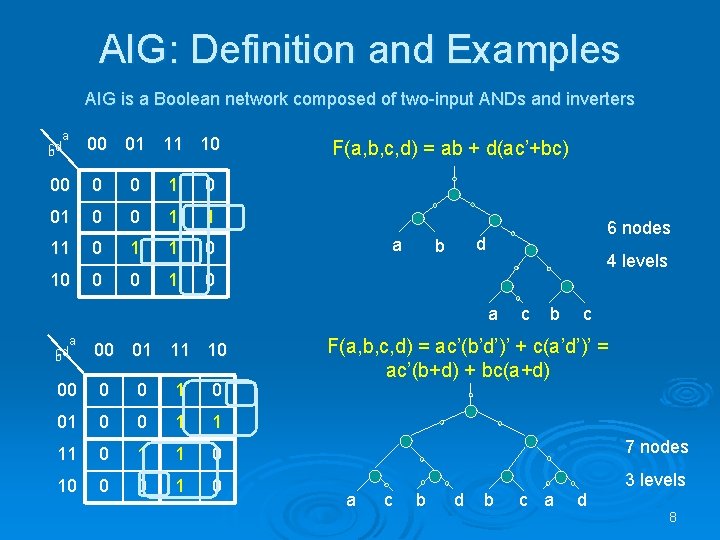

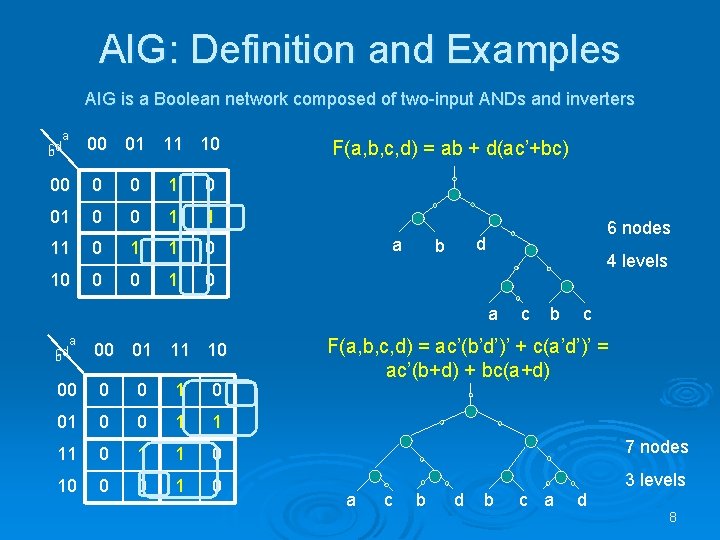

AIG: Definition and Examples AIG is a Boolean network composed of two-input ANDs and inverters a cd b 00 01 11 10 00 0 0 1 1 11 0 10 0 0 1 0 F(a, b, c, d) = ab + d(ac’+bc) a 6 nodes d b 4 levels a a cd b 00 01 11 10 c b c F(a, b, c, d) = ac’(b’d’)’ + c(a’d’)’ = ac’(b+d) + bc(a+d) 00 0 0 1 1 11 0 1 1 0 7 nodes 10 0 0 1 0 3 levels a c b d b c a d 8

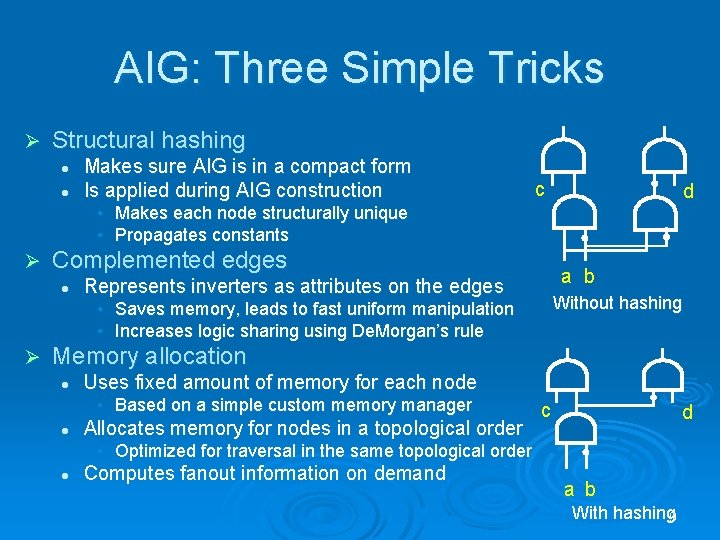

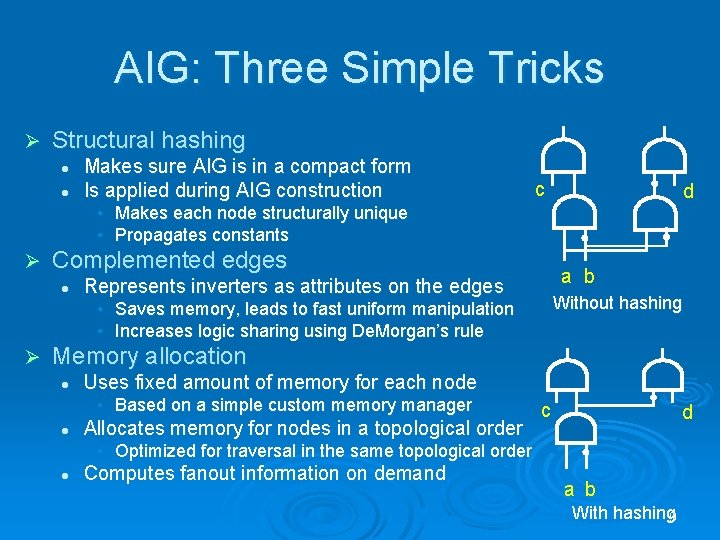

AIG: Three Simple Tricks Ø Structural hashing l l Makes sure AIG is in a compact form Is applied during AIG construction c d • Makes each node structurally unique • Propagates constants Ø Complemented edges l a b Represents inverters as attributes on the edges Without hashing • Saves memory, leads to fast uniform manipulation • Increases logic sharing using De. Morgan’s rule Ø Memory allocation l Uses fixed amount of memory for each node • Based on a simple custom memory manager l Allocates memory for nodes in a topological order c d • Optimized for traversal in the same topological order l Computes fanout information on demand a b With hashing 9

AIG: A Unifying Representation Ø An underlying data structure for various computations l l Ø A unifying representation for the whole flow l l Ø Representing both local and global functions Used in rewriting, resubstitution, simulation, SAT sweeping, induction, etc Synthesis, mapping, verification pass around AIGs Stored multiple structures for mapping (‘AIG with choices’) The main functional representation in ABC l l Foundation of ‘contemporary’ logic synthesis Source of ‘signature features’ (speed, scalability, etc) 10

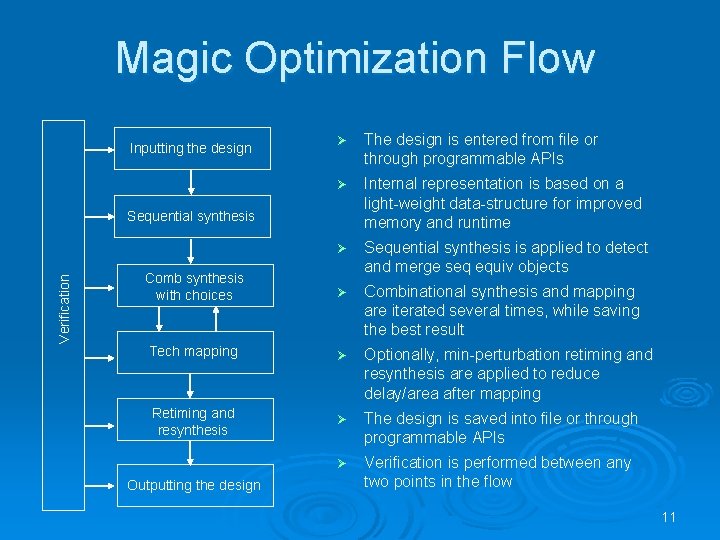

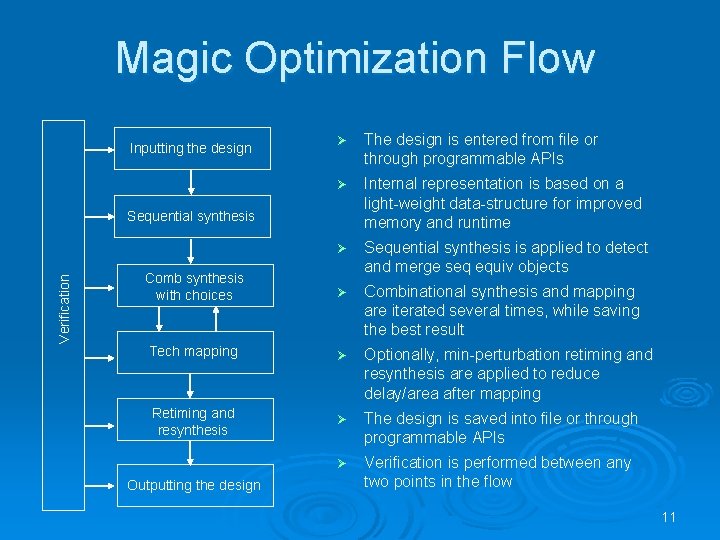

Magic Optimization Flow Ø The design is entered from file or through programmable APIs Ø Internal representation is based on a light-weight data-structure for improved memory and runtime Ø Comb synthesis with choices Sequential synthesis is applied to detect and merge seq equiv objects Ø Combinational synthesis and mapping are iterated several times, while saving the best result Tech mapping Ø Optionally, min-perturbation retiming and resynthesis are applied to reduce delay/area after mapping Retiming and resynthesis Ø The design is saved into file or through programmable APIs Ø Verification is performed between any two points in the flow Inputting the design Verification Sequential synthesis Outputting the design 11

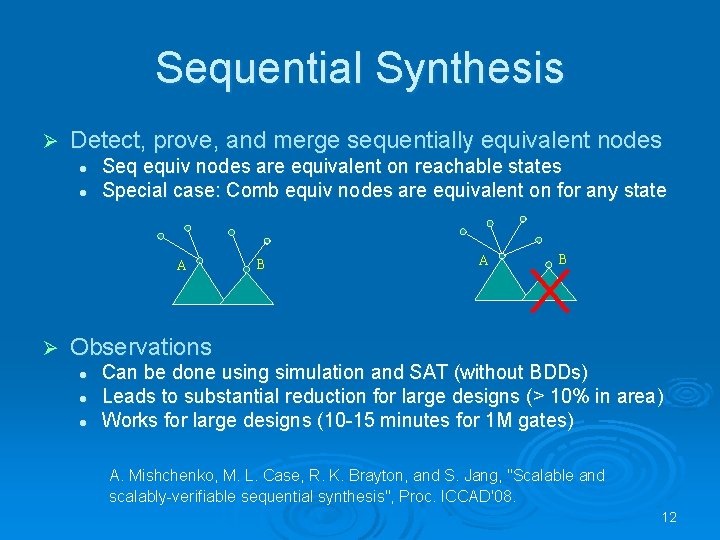

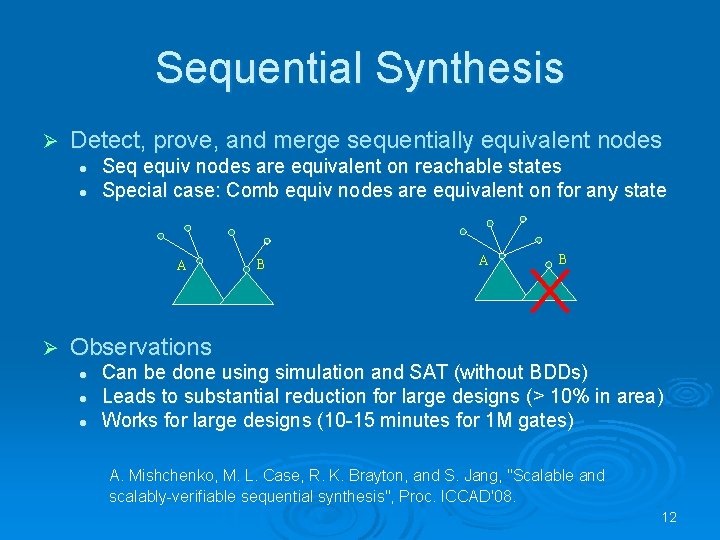

Sequential Synthesis Ø Detect, prove, and merge sequentially equivalent nodes l l Seq equiv nodes are equivalent on reachable states Special case: Comb equiv nodes are equivalent on for any state A Ø B A B Observations l l l Can be done using simulation and SAT (without BDDs) Leads to substantial reduction for large designs (> 10% in area) Works for large designs (10 -15 minutes for 1 M gates) A. Mishchenko, M. L. Case, R. K. Brayton, and S. Jang, "Scalable and scalably-verifiable sequential synthesis", Proc. ICCAD'08. 12

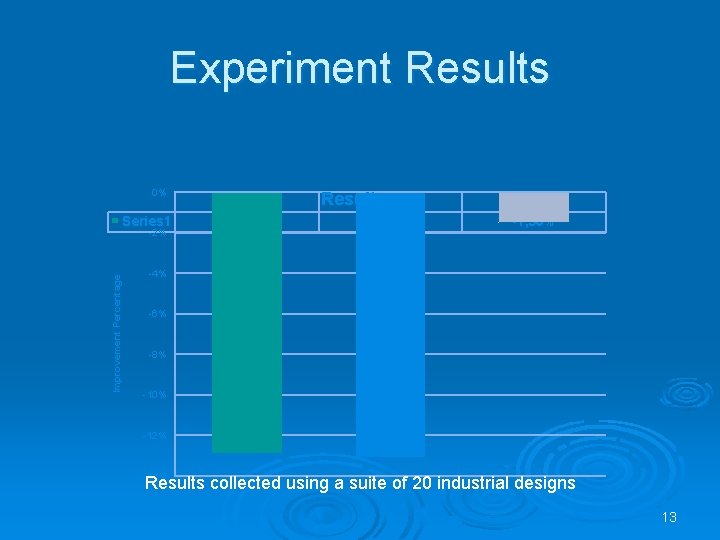

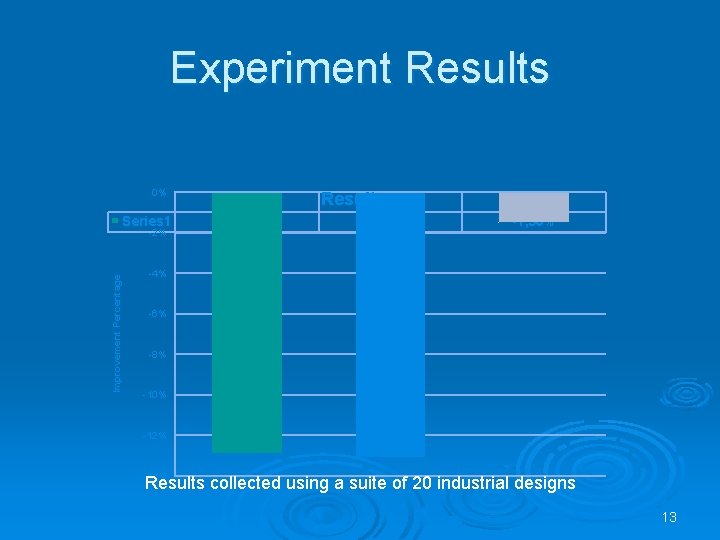

Experiment Results 0% Series 1 Improvement Percentage -2% LUT -12, 90% Results Register -13, 10% Level -1, 50% -4% -6% -8% -10% -12% -14% Results collected using a suite of 20 industrial designs 13

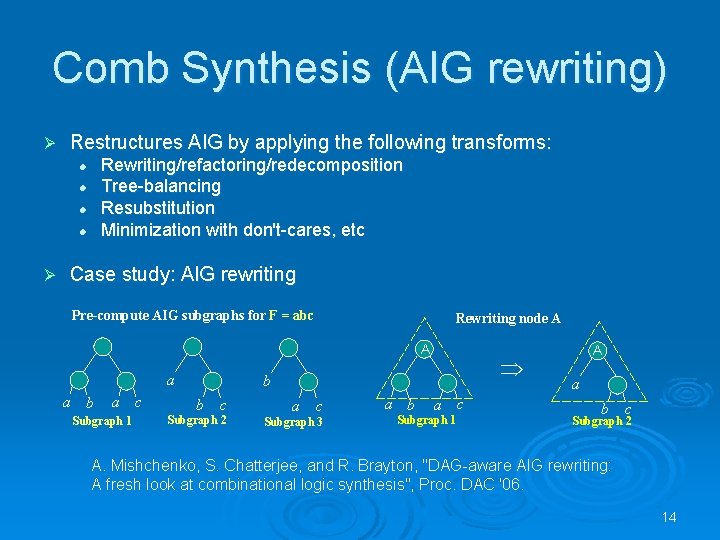

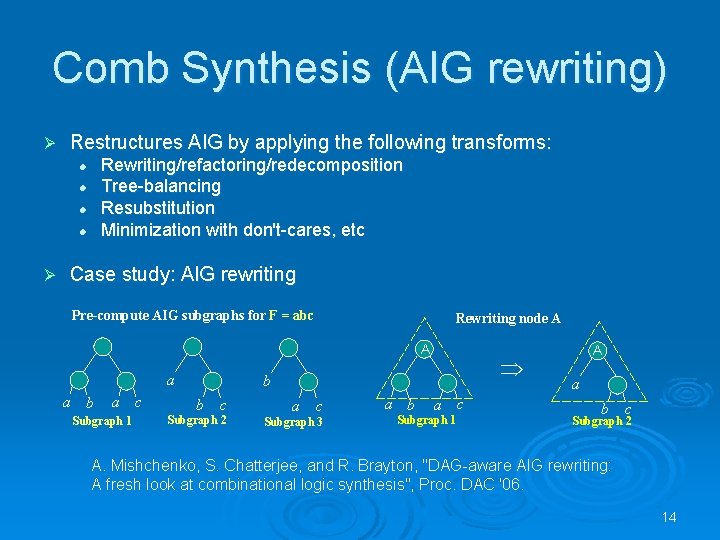

Comb Synthesis (AIG rewriting) Ø Restructures AIG by applying the following transforms: Rewriting/refactoring/redecomposition Tree-balancing Resubstitution Minimization with don't-cares, etc l l Ø Case study: AIG rewriting Pre-compute AIG subgraphs for F = abc Rewriting node A A a a b a c Subgraph 1 b b c Subgraph 2 a c Subgraph 3 a b a c Subgraph 1 A a b c Subgraph 2 A. Mishchenko, S. Chatterjee, and R. Brayton, "DAG-aware AIG rewriting: A fresh look at combinational logic synthesis", Proc. DAC '06. 14

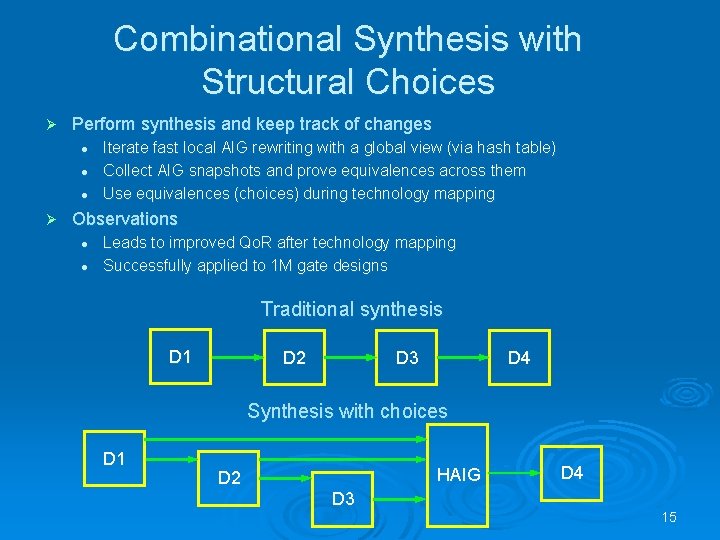

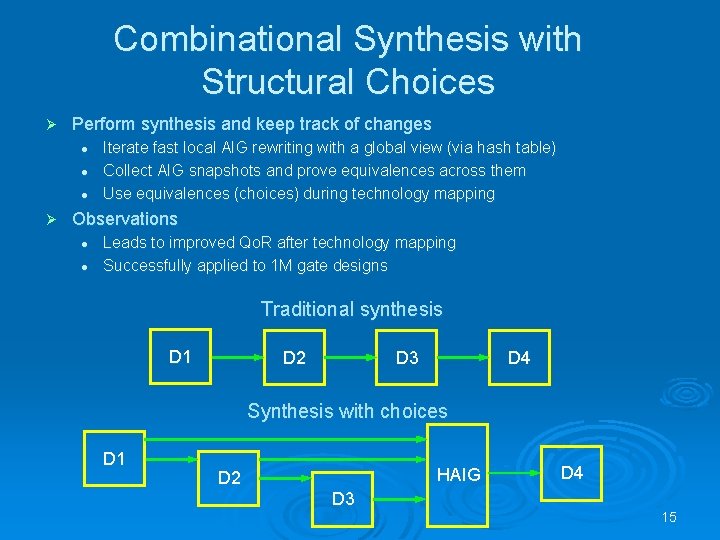

Combinational Synthesis with Structural Choices Ø Perform synthesis and keep track of changes l l l Ø Iterate fast local AIG rewriting with a global view (via hash table) Collect AIG snapshots and prove equivalences across them Use equivalences (choices) during technology mapping Observations l l Leads to improved Qo. R after technology mapping Successfully applied to 1 M gate designs Traditional synthesis D 1 D 2 D 3 D 4 Synthesis with choices D 1 HAIG D 2 D 3 D 4 15

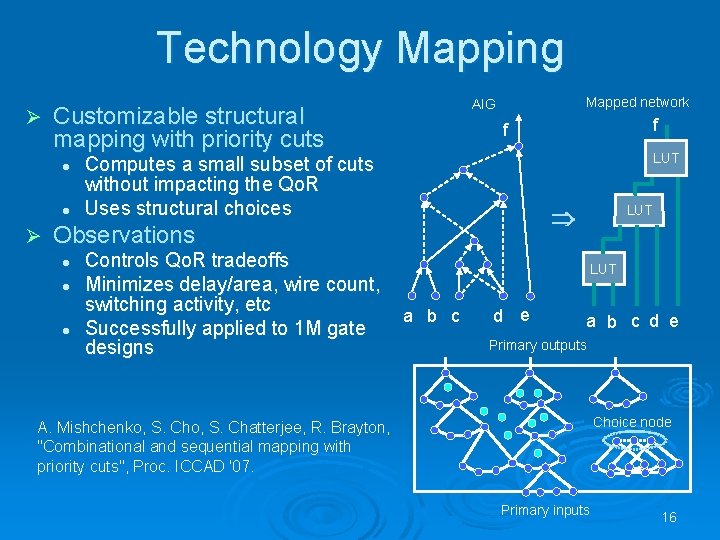

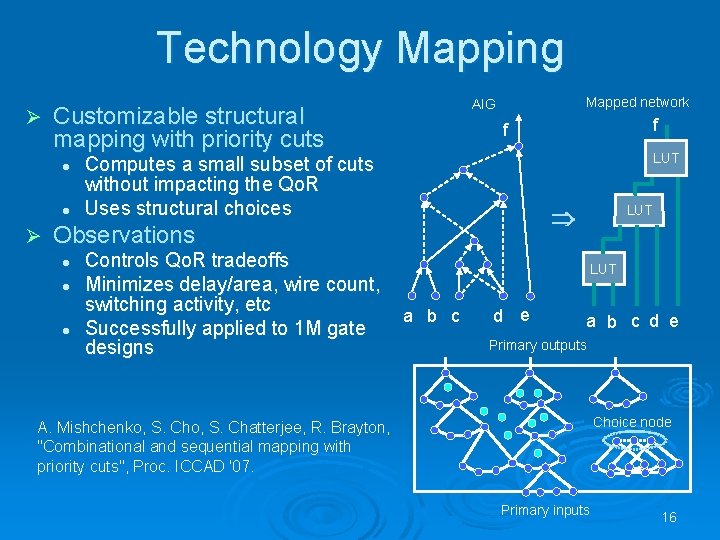

Technology Mapping Ø Customizable structural mapping with priority cuts l l Ø Mapped network AIG LUT Computes a small subset of cuts without impacting the Qo. R Uses structural choices Observations l l l Controls Qo. R tradeoffs Minimizes delay/area, wire count, switching activity, etc Successfully applied to 1 M gate designs f f LUT a b c d e Primary outputs Choice node A. Mishchenko, S. Chatterjee, R. Brayton, "Combinational and sequential mapping with priority cuts", Proc. ICCAD '07. Primary inputs 16

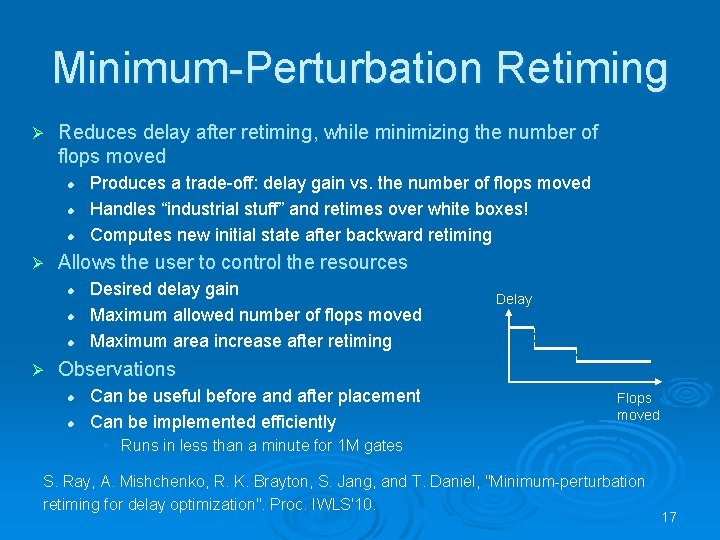

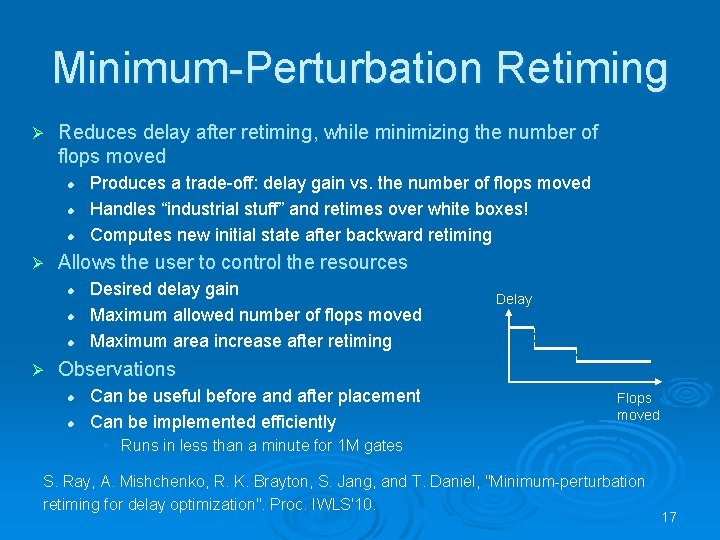

Minimum-Perturbation Retiming Ø Reduces delay after retiming, while minimizing the number of flops moved l l l Ø Allows the user to control the resources l l l Ø Produces a trade-off: delay gain vs. the number of flops moved Handles “industrial stuff” and retimes over white boxes! Computes new initial state after backward retiming Desired delay gain Maximum allowed number of flops moved Maximum area increase after retiming Delay Observations l l Can be useful before and after placement Can be implemented efficiently Flops moved • Runs in less than a minute for 1 M gates S. Ray, A. Mishchenko, R. K. Brayton, S. Jang, and T. Daniel, "Minimum-perturbation retiming for delay optimization". Proc. IWLS'10. 17

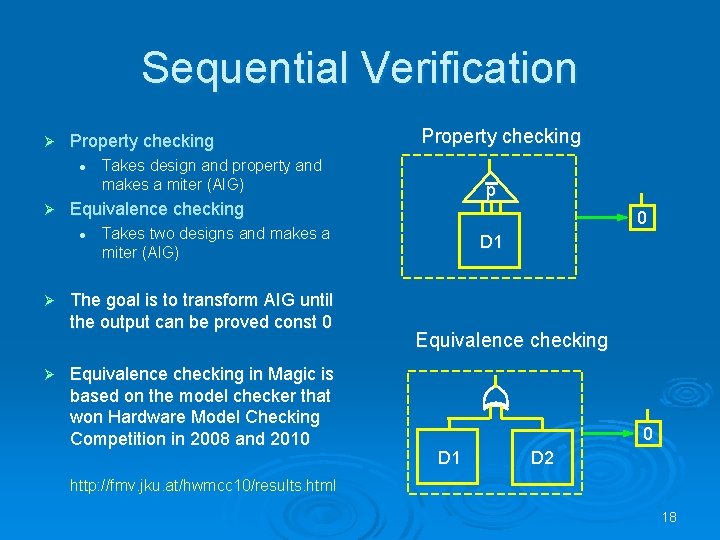

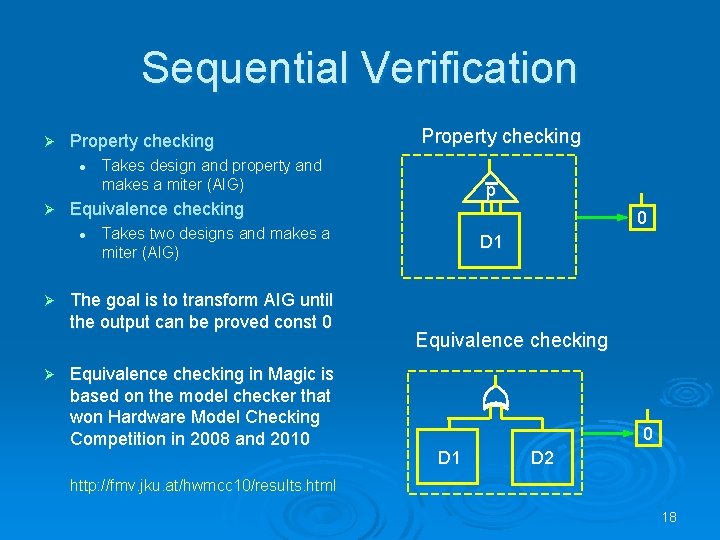

Sequential Verification Ø Property checking l Ø Ø Takes design and property and makes a miter (AIG) p Equivalence checking l Ø Property checking 0 Takes two designs and makes a miter (AIG) The goal is to transform AIG until the output can be proved const 0 Equivalence checking in Magic is based on the model checker that won Hardware Model Checking Competition in 2008 and 2010 D 1 Equivalence checking 0 D 1 D 2 http: //fmv. jku. at/hwmcc 10/results. html 18

A Naïve Way to Use ABC Ø Convert all persistent logic to black boxes l Ø Box IOs are treated as PI/POs in synthesis Adverse effects l l Losing the correlation of box outputs/inputs Restricting synthesis due to broken logic paths Not being able to propagate delays through the boxes Sequential synthesis doesn’t work well 19

A Better Way to Use ABC Ø Clock domains l l l Ø Complex controls of the flops l l l Ø Represent clock signal in the data-base Annotate flops with their clock-domain number in the AIG Separate clock domains in sequential transforms Use parametrized flop model Perform elaboration of control signals if needed Handle asynchronous reset carefully! Industrial primitives (adders, RAMs, DSPs, etc) l l Use boxes (black/white, comb/seq, merge/no_merge, etc) Currently propagates timing information, improves quality of synthesis • Elaborate boxes for seq synthesis, but do not map them l Need better support for user-specified attributes (don’t-touch, etc) 20

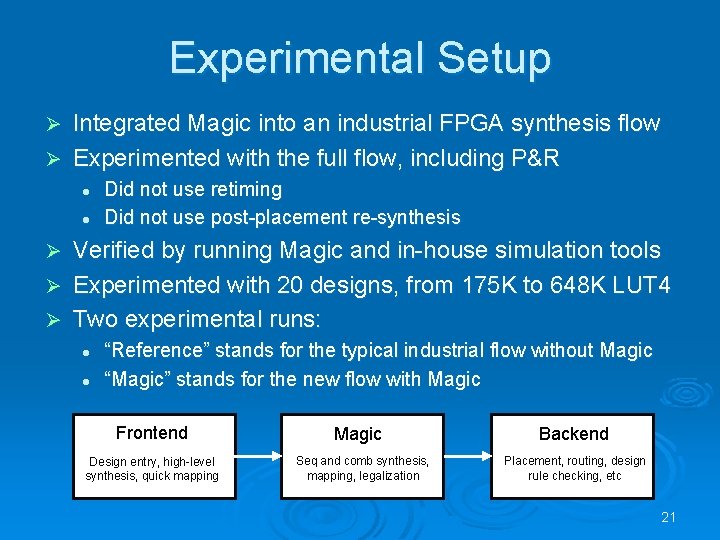

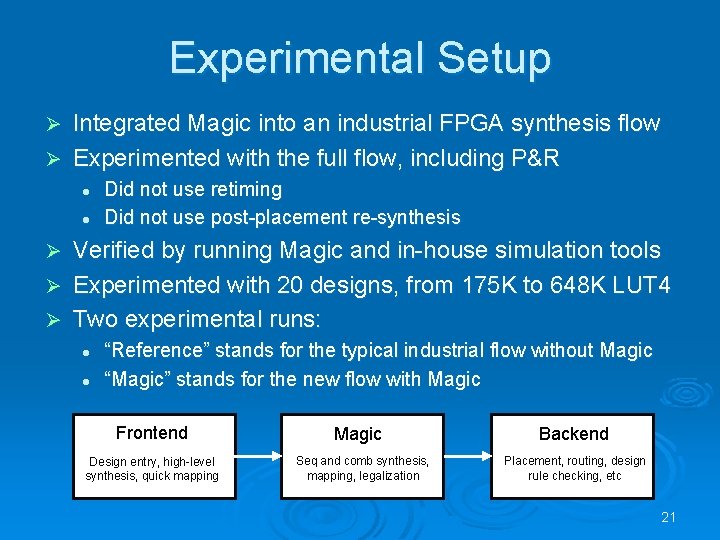

Experimental Setup Integrated Magic into an industrial FPGA synthesis flow Ø Experimented with the full flow, including P&R Ø l l Did not use retiming Did not use post-placement re-synthesis Verified by running Magic and in-house simulation tools Ø Experimented with 20 designs, from 175 K to 648 K LUT 4 Ø Two experimental runs: Ø l l “Reference” stands for the typical industrial flow without Magic “Magic” stands for the new flow with Magic Frontend Design entry, high-level synthesis, quick mapping Magic Seq and comb synthesis, mapping, legalization Backend Placement, routing, design rule checking, etc 21

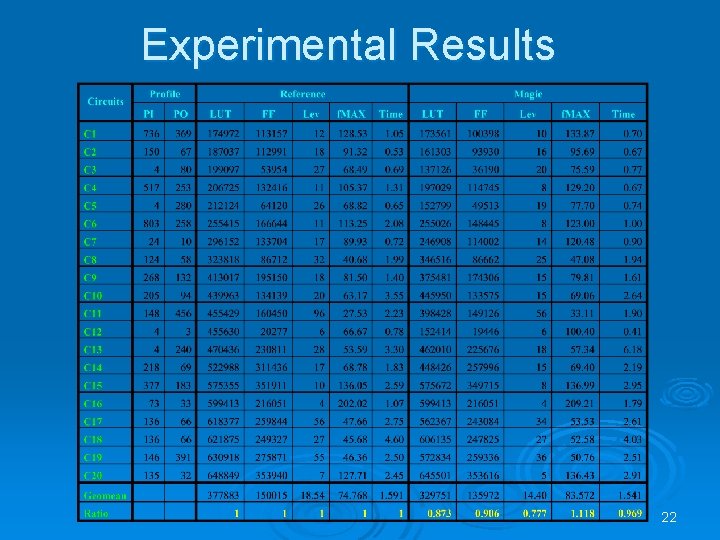

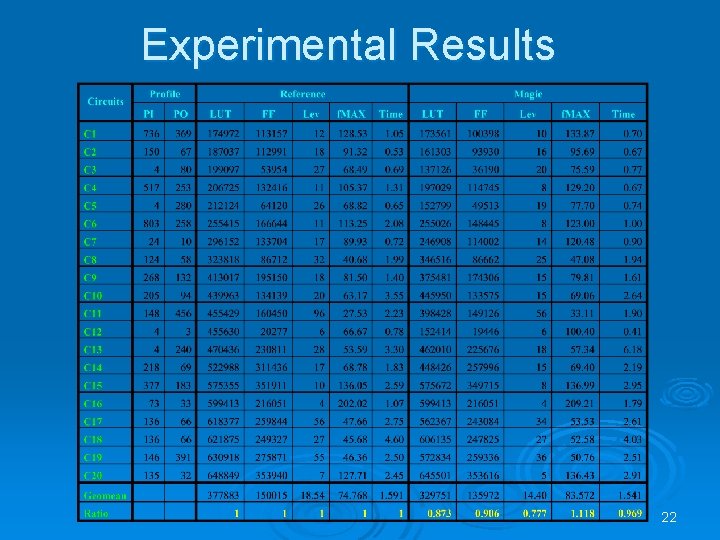

Experimental Results 22

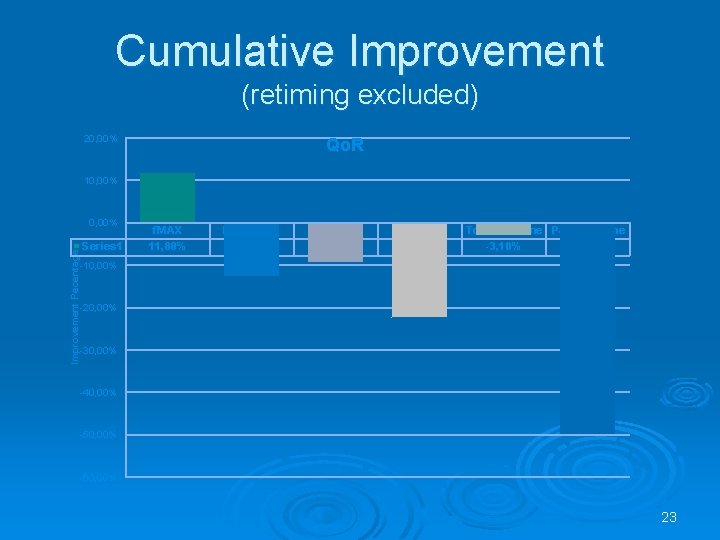

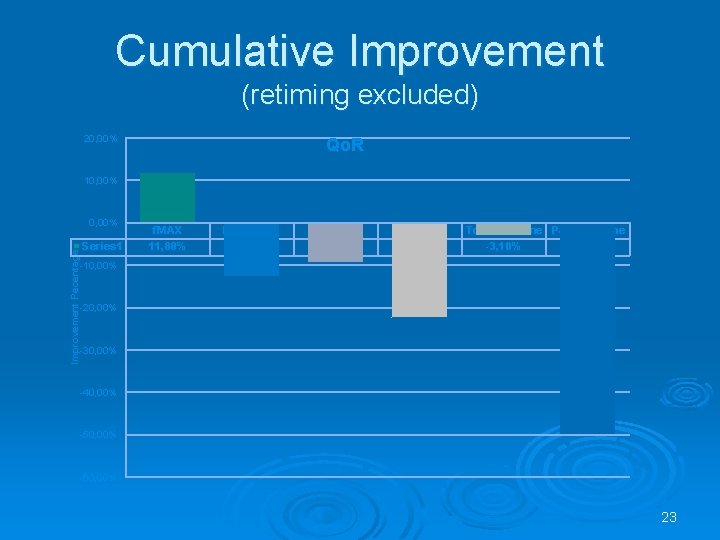

Cumulative Improvement (retiming excluded) 20, 00% Qo. R 10, 00% Improvement Pecentage 0, 00% Series 1 f. MAX 11, 80% LUT count -12, 70% Registers -9, 40% Levels -22, 30% Total Runtime P&R Runtime -3, 10% -50, 00% -10, 00% -20, 00% -30, 00% -40, 00% -50, 00% -60, 00% 23

Future Work Ø Continue to improve application packages l Ø Improve integration of logic and physical synthesis l l Ø AIG rewriting, tech-mapping, sequential synthesis, etc Synthesis/mapping/retiming before placement Retiming/restructuring after placement Extend the flow to work for other technologies l l Macro cells Standard cells 24