LowPower IC Design Ch 1 Introduction 1 TsungChu

![References [1] [2] [3] [4] [5] [6] [7] [8] [9] [10] [11] [12] [13] References [1] [2] [3] [4] [5] [6] [7] [8] [9] [10] [11] [12] [13]](https://slidetodoc.com/presentation_image_h2/869aeaa6777d6a0ffb69231ae86dcd54/image-14.jpg)

- Slides: 14

Low-Power IC Design Ch. 1 Introduction (1) Tsung-Chu Huang Dep’t of Electronic Eng. , Nat’l Changhua Univ. Spring 2007 Low-Power IC Design. Tsung-Chu Huang, NCUE Ch. 1 Introduction 1 NCUE EDAT

Introduction to Low-Power IC Design • • • Syllabus Importance – Why Low-Power ? Design Space Applications Readings and References Low-Power IC Design. Tsung-Chu Huang, NCUE Ch. 1 Introduction 2 NCUE EDAT

Syllabus • • Website: http: //163. 223. 30 Background: “Introduction to VLSI Design” Date: Thursday Time: Periods 6~8 (1: 55~4: 45 pm) Place: Rm. 31214, Baosan District, NCUE, Taiwan Level-Major Coursing Grading: – – More than 4 Lavatories/Homework (5% per Lab) Reading and Presentation (10%) Midterm (Close-book, 30%) Finals (Open-book, 40%) Low-Power IC Design. Tsung-Chu Huang, NCUE Ch. 1 Introduction 3 NCUE EDAT

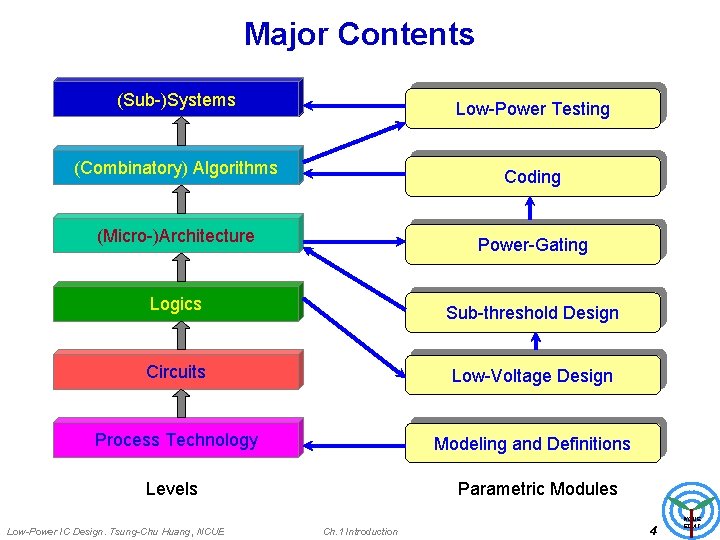

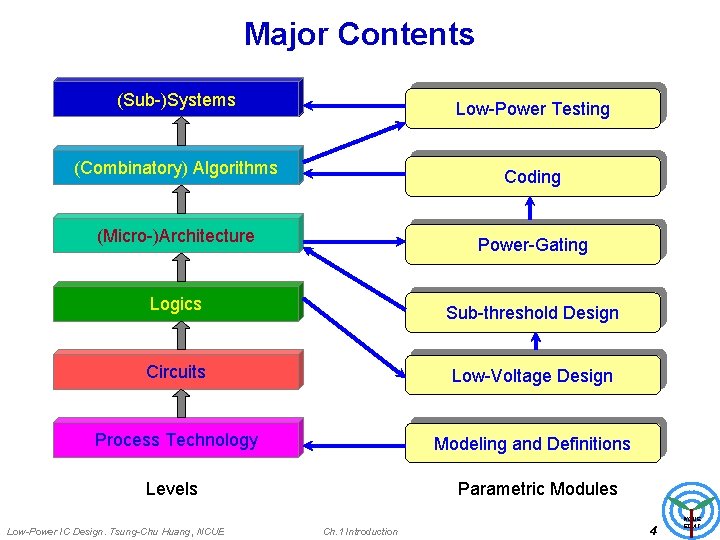

Major Contents (Sub-)Systems Low-Power Testing (Combinatory) Algorithms Coding (Micro-)Architecture Power-Gating Logics Sub-threshold Design Circuits Low-Voltage Design Process Technology Modeling and Definitions Levels Parametric Modules Low-Power IC Design. Tsung-Chu Huang, NCUE Ch. 1 Introduction 4 NCUE EDAT

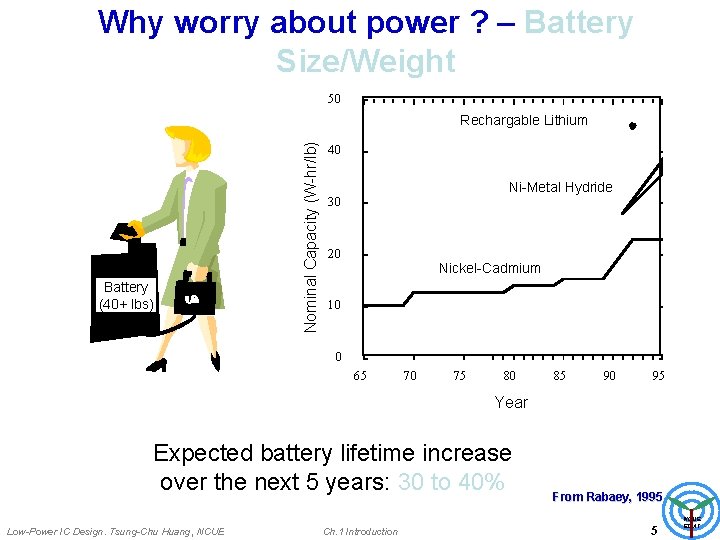

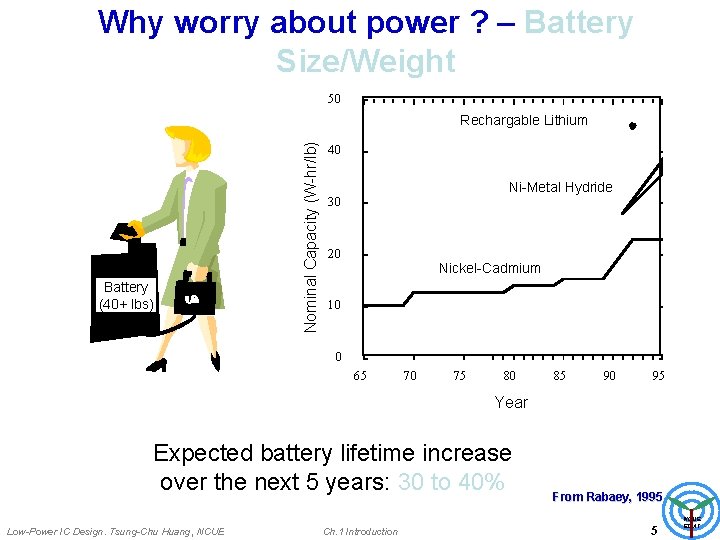

Why worry about power ? – Battery Size/Weight 50 Battery (40+ lbs) Nominal Capacity (W-hr/lb) Rechargable Lithium 40 Ni-Metal Hydride 30 20 Nickel-Cadmium 10 0 65 70 75 80 85 90 95 Year Expected battery lifetime increase over the next 5 years: 30 to 40% Low-Power IC Design. Tsung-Chu Huang, NCUE Ch. 1 Introduction From Rabaey, 1995 5 NCUE EDAT

What Happens When the CPU Coolers is Removed? • Click the following link to watch the demo. (Source: WWW. Meta. Cafe. com) Low-Power IC Design. Tsung-Chu Huang, NCUE Ch. 1 Introduction 6 NCUE EDAT

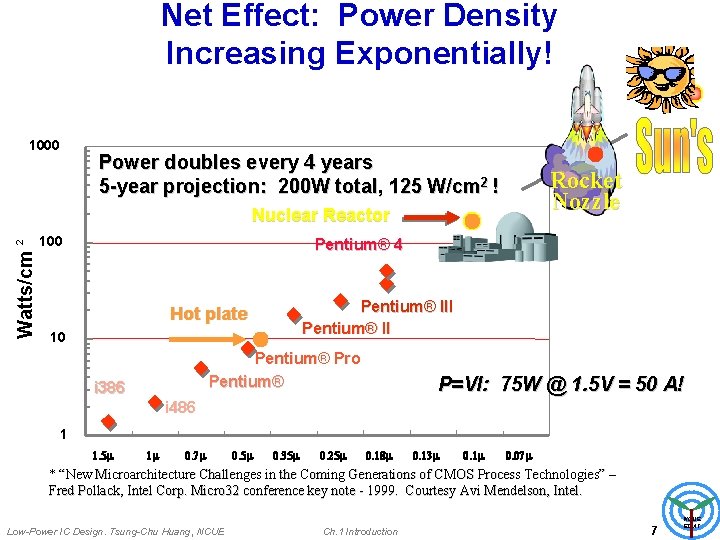

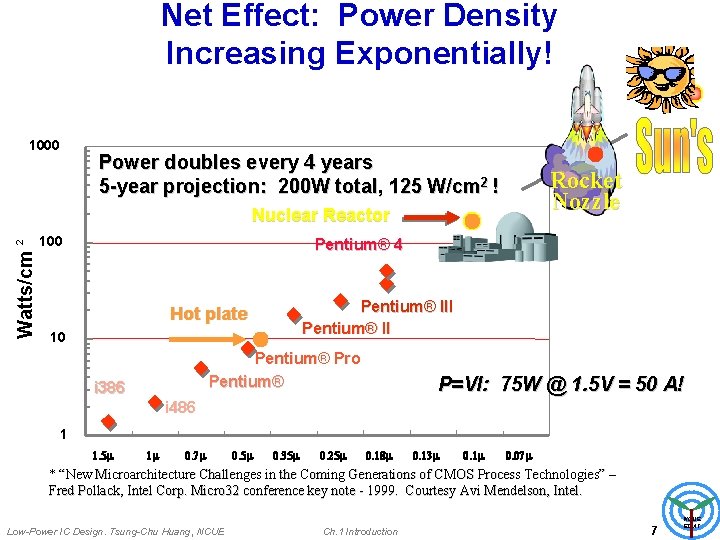

Net Effect: Power Density Increasing Exponentially! 1000 Power doubles every 4 years 5 -year projection: 200 W total, 125 W/cm 2 ! Rocket Nozzle Watts/cm 2 Nuclear Reactor 100 Pentium® 4 Pentium® III Pentium® II Hot plate 10 Pentium® Pro Pentium® i 386 P=VI: 75 W @ 1. 5 V = 50 A! i 486 1 1. 5 m 1 m 0. 7 m 0. 5 m 0. 35 m 0. 25 m 0. 18 m 0. 13 m 0. 1 m 0. 07 m * “New Microarchitecture Challenges in the Coming Generations of CMOS Process Technologies” – Fred Pollack, Intel Corp. Micro 32 conference key note - 1999. Courtesy Avi Mendelson, Intel. Low-Power IC Design. Tsung-Chu Huang, NCUE Ch. 1 Introduction 7 NCUE EDAT

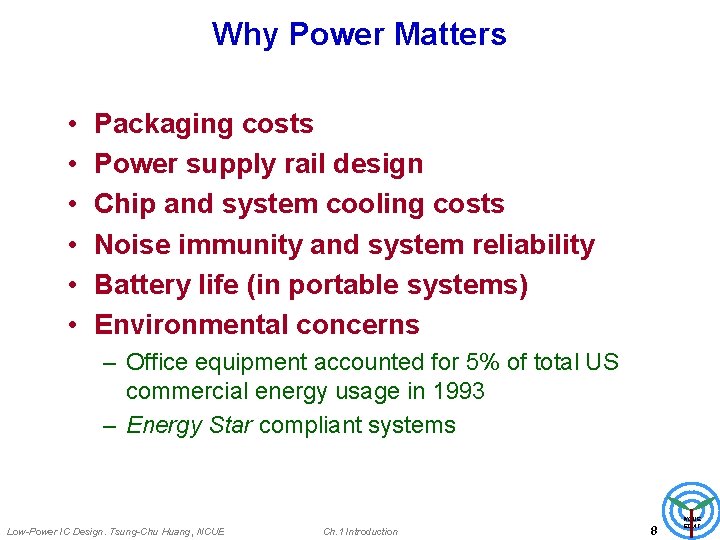

Why Power Matters • • • Packaging costs Power supply rail design Chip and system cooling costs Noise immunity and system reliability Battery life (in portable systems) Environmental concerns – Office equipment accounted for 5% of total US commercial energy usage in 1993 – Energy Star compliant systems Low-Power IC Design. Tsung-Chu Huang, NCUE Ch. 1 Introduction 8 NCUE EDAT

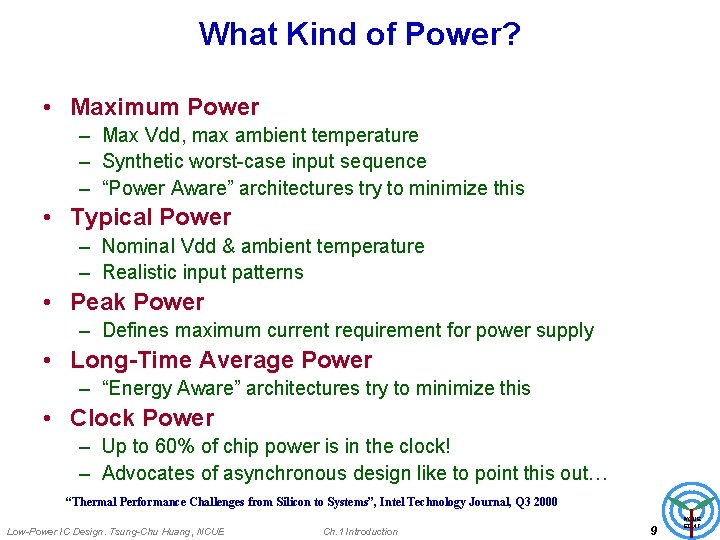

What Kind of Power? • Maximum Power – Max Vdd, max ambient temperature – Synthetic worst-case input sequence – “Power Aware” architectures try to minimize this • Typical Power – Nominal Vdd & ambient temperature – Realistic input patterns • Peak Power – Defines maximum current requirement for power supply • Long-Time Average Power – “Energy Aware” architectures try to minimize this • Clock Power – Up to 60% of chip power is in the clock! – Advocates of asynchronous design like to point this out… “Thermal Performance Challenges from Silicon to Systems”, Intel Technology Journal, Q 3 2000 Low-Power IC Design. Tsung-Chu Huang, NCUE Ch. 1 Introduction 9 NCUE EDAT

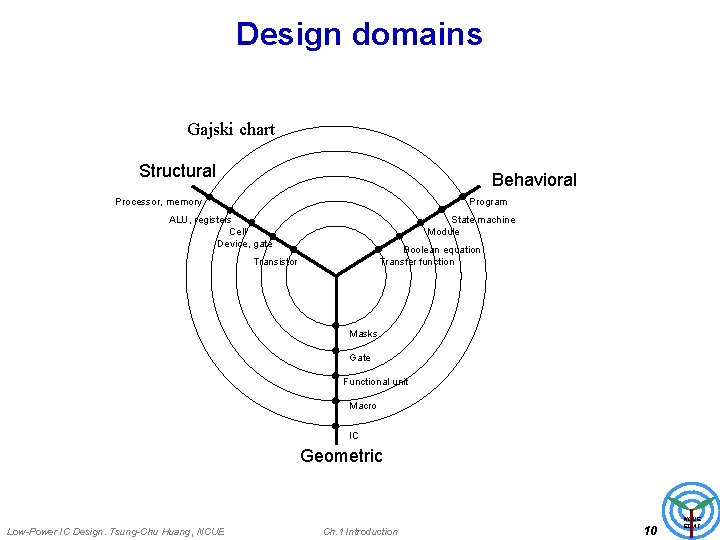

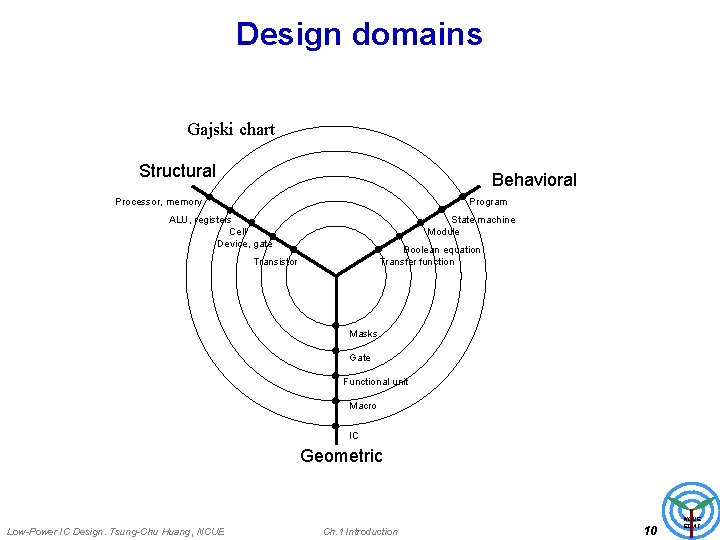

Design domains Gajski chart Structural Behavioral Program Processor, memory ALU, registers Cell Device, gate State machine Module Boolean equation Transfer function Transistor Masks Gate Functional unit Macro IC Geometric Low-Power IC Design. Tsung-Chu Huang, NCUE Ch. 1 Introduction 10 NCUE EDAT

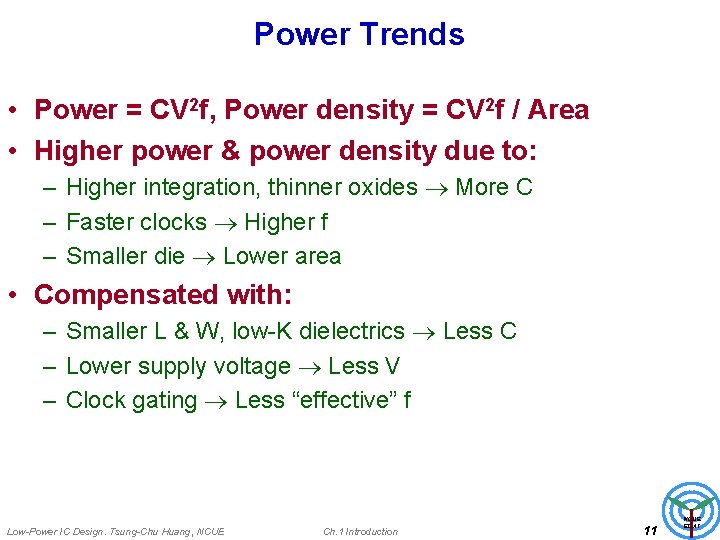

Power Trends • Power = CV 2 f, Power density = CV 2 f / Area • Higher power & power density due to: – Higher integration, thinner oxides More C – Faster clocks Higher f – Smaller die Lower area • Compensated with: – Smaller L & W, low-K dielectrics Less C – Lower supply voltage Less V – Clock gating Less “effective” f Low-Power IC Design. Tsung-Chu Huang, NCUE Ch. 1 Introduction 11 NCUE EDAT

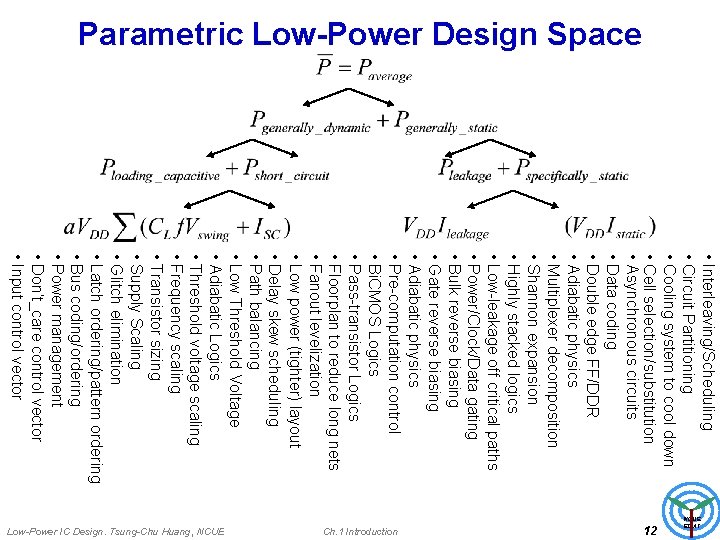

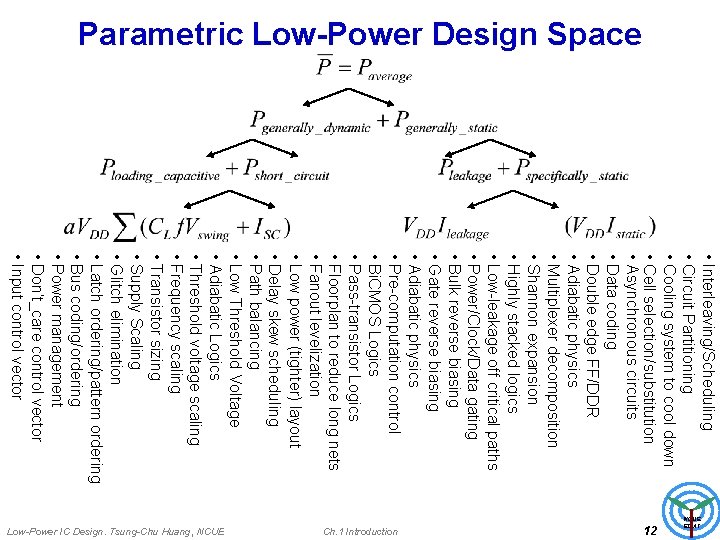

Parametric Low-Power Design Space • Interleaving/Scheduling • Circuit Partitioning • Cooling system to cool down • Cell selection/substitution • Asynchronous circuits • Data coding • Double edge FF/DDR • Adiabatic physics • Multiplexer decomposition • Shannon expansion • Highly stacked logics • Low-leakage off critical paths • Power/Clock/Data gating • Bulk reverse biasing • Gate reverse biasing • Adiabatic physics • Pre-computation control • Bi. CMOS Logics • Pass-transistor Logics • Floorplan to reduce long nets • Fanout levelization • Low power (tighter) layout • Delay skew scheduling • Path balancing • Low Threshold Voltage • Adiabatic Logics • Threshold voltage scaling • Frequency scaling • Transistor sizing • Supply Scaling • Glitch elimination • Latch ordering/pattern ordering • Bus coding/ordering • Power management • Don’t_care control vector • Input control vector NCUE EDAT 12 Ch. 1 Introduction Low-Power IC Design. Tsung-Chu Huang, NCUE

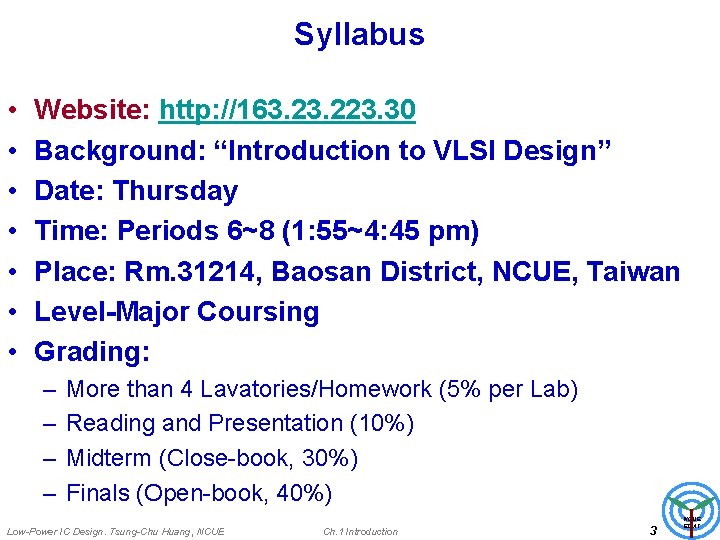

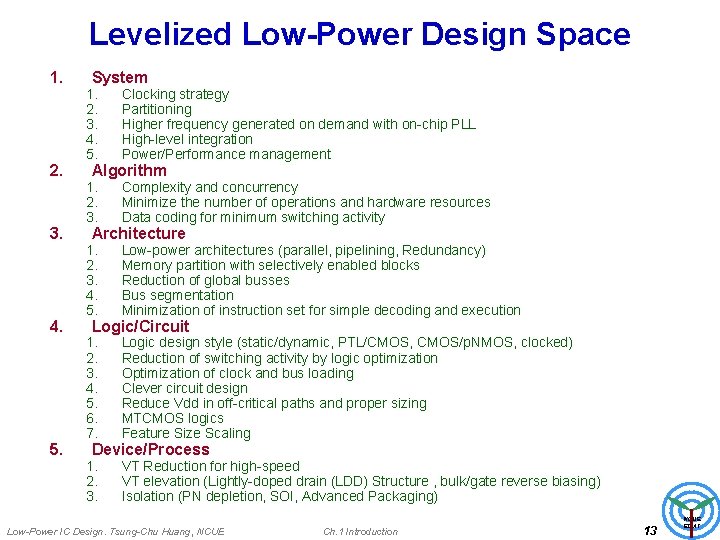

Levelized Low-Power Design Space 1. 2. 3. 4. 5. System 1. 2. 3. 4. 5. Clocking strategy Partitioning Higher frequency generated on demand with on-chip PLL High-level integration Power/Performance management 1. 2. 3. Complexity and concurrency Minimize the number of operations and hardware resources Data coding for minimum switching activity 1. 2. 3. 4. 5. Low-power architectures (parallel, pipelining, Redundancy) Memory partition with selectively enabled blocks Reduction of global busses Bus segmentation Minimization of instruction set for simple decoding and execution 1. 2. 3. 4. 5. 6. 7. Logic design style (static/dynamic, PTL/CMOS, CMOS/p. NMOS, clocked) Reduction of switching activity by logic optimization Optimization of clock and bus loading Clever circuit design Reduce Vdd in off-critical paths and proper sizing MTCMOS logics Feature Size Scaling 1. 2. 3. VT Reduction for high-speed VT elevation (Lightly-doped drain (LDD) Structure , bulk/gate reverse biasing) Isolation (PN depletion, SOI, Advanced Packaging) Algorithm Architecture Logic/Circuit Device/Process Low-Power IC Design. Tsung-Chu Huang, NCUE Ch. 1 Introduction 13 NCUE EDAT

![References 1 2 3 4 5 6 7 8 9 10 11 12 13 References [1] [2] [3] [4] [5] [6] [7] [8] [9] [10] [11] [12] [13]](https://slidetodoc.com/presentation_image_h2/869aeaa6777d6a0ffb69231ae86dcd54/image-14.jpg)

References [1] [2] [3] [4] [5] [6] [7] [8] [9] [10] [11] [12] [13] [14] [15] [16] [17] [18] [19] A. Bellaourar and M. I. Elmasry, Low-Power Digital VLSI Design – Circuits and Systems. Kluwer, 5 th ed. 2000. (Textbook 1) A. Wang, B. H. Calhoun and A. P. Chandrakasan. Sub-threshold Design for Ultra Low-Power Systems. Springer, 2006. (Textbook 2) Circuits, 27(4): 473 -484, Apr. 1992. S. Kang, "Elements of Low Power Design for Integrated Systems, " ISLPED, 2003. K. Roy. "Leakage current mechanisms and leakage reduction techniques in deep-submicrometer CMOS circuits, " K. Roy, Proc. of the IEEE, vol. 91, no. 2, 2003. S. Mutoh, "1 -V power supply high-speed digital circuit technology with multithreshold-voltage CMOS, " IEEE JSSC, Vol. 30, No. 8, 1995. M. Borah, "Transistor sizing for low power CMOS circuits, " IEEE Trans. on CAD of IC and Systems, Vol. 15, No. 6, 1996. M. Stan, et al. , "Bus-invert Coding for Low Power I/O, " IEEE Trans. on VLSI Systems, " vol. 3, no. 1, 1995. M. Alidina, et al. , "Precomputation-based sequential logic optimization for low power, " IEEE Trans. on VLSI Systems, " vol. 2, no. 4, 1994. R. Hossain, "Low power design using double edge triggered flip-flop, " IEEE Trans. on VLSI systems, Vol. 2, No. 2, 1994. Wai Chung, et al. , " A comparative analysis of low-power low-voltage dual-edge-triggered flip-flops, " IEEE Trans. on VLSI systems, vol. 10, no. 6, 2002. Stojanovic, et al. , " Comparative analysis of master-slave latches and flip-flops for high performance and low power systems, " IEEE JSSC, vol. 34, no. 4, April 1999, pp. 536 -548. A. P. Chandrakasan, "Minimizing power consumption in digital CMOS circuits, " Proceeding of the IEEE, Vol. 83, No. 4, 1995. K. Itoh, "Trends in low-power RAM circuit technologies, " Proc. of the IEEE, Vol. 83, no. 4, 1995. W. Athas, "Low power digital systems based on adiabatic-switching principles, " IEEE Trans. on VLSI systems, Vol. 2, No. 4, 1994. Vojin, "Pass-transistor adiabatic logic usingle power-clock supply, " IEEE Trans. on circuits and systems, Vol. 44, no. 10, 1997. Girard. Low Power Testing of VLSI Circuits: Problems and Solutions. IEEE International Symposium on Quality Electronic Design, pages 173 -179, 2000. J. M. Rabaey. Exploring the power dimension in digital CMOS. CICC, pp. 215 -220, 1996. F. N. Najm. Low-power design methodology: power estimation and optimization. MWCAS, pp. 1124 -1129, 1997. Low-Power IC Design. Tsung-Chu Huang, NCUE Ch. 1 Introduction 14 NCUE EDAT