CPU Design CPU Design Flow TsungChu Huang Dept

![MIPS 32 module PC(PH 1, Rst, PCWrite, PCo, PCi); output [31: 0] PCo; input MIPS 32 module PC(PH 1, Rst, PCWrite, PCo, PCi); output [31: 0] PCo; input](https://slidetodoc.com/presentation_image/477e47a25e838924f6e12fe68d977c29/image-4.jpg)

![MIPS 32 module IM(PC, Ins); input [31: 0] PC; output [31: 0] Ins; reg MIPS 32 module IM(PC, Ins); input [31: 0] PC; output [31: 0] Ins; reg](https://slidetodoc.com/presentation_image/477e47a25e838924f6e12fe68d977c29/image-5.jpg)

- Slides: 11

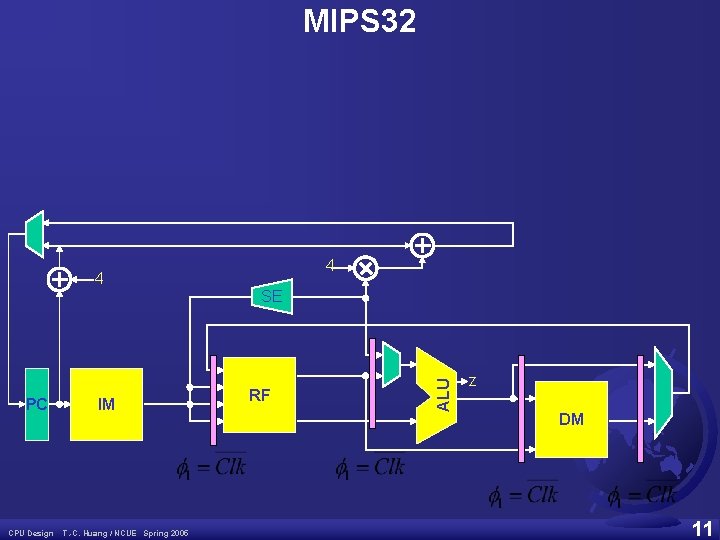

CPU Design -- CPU Design Flow Tsung-Chu Huang Dept. of Electronic Eng. National Changhua University of Ed. Email: tch@cc. ncue. edu. tw 2005/04/26 CPU Design T. -C. Huang / NCUE Spring 2005 1

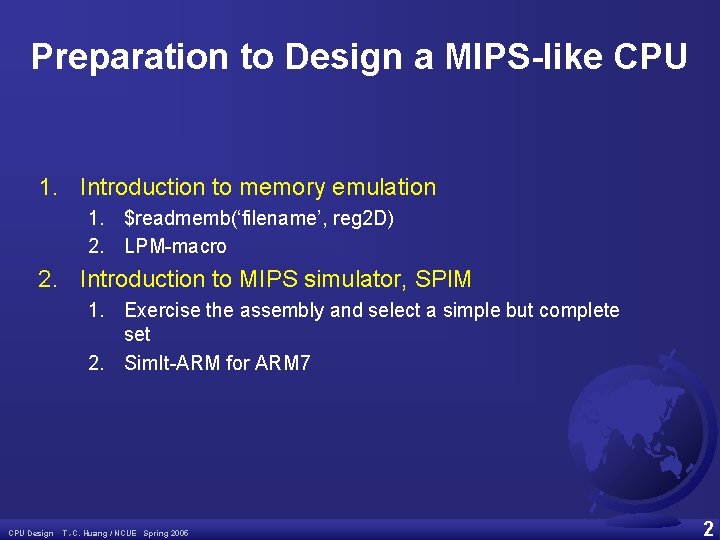

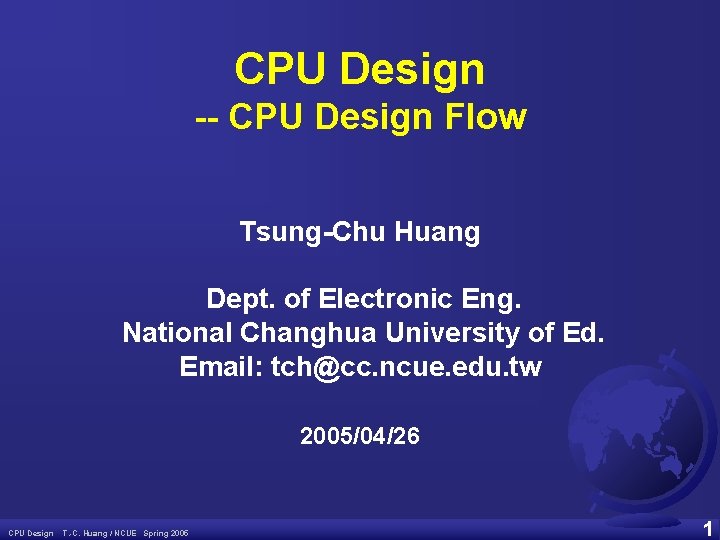

Preparation to Design a MIPS-like CPU 1. Introduction to memory emulation 1. $readmemb(‘filename’, reg 2 D) 2. LPM-macro 2. Introduction to MIPS simulator, SPIM 1. Exercise the assembly and select a simple but complete set 2. Sim. It-ARM for ARM 7 CPU Design T. -C. Huang / NCUE Spring 2005 2

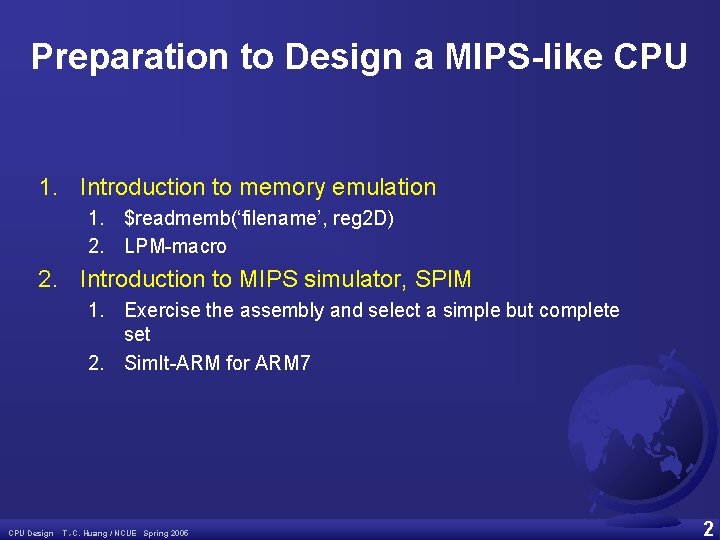

MIPS 32 4 4 PC IF: Instruction Fetch CPU Design RF IM ID: Instruction Decode T. -C. Huang / NCUE Spring 2005 ALU SE EX: Execution Stage z DM DM: Data Memory WB: Write Back 3

![MIPS 32 module PCPH 1 Rst PCWrite PCo PCi output 31 0 PCo input MIPS 32 module PC(PH 1, Rst, PCWrite, PCo, PCi); output [31: 0] PCo; input](https://slidetodoc.com/presentation_image/477e47a25e838924f6e12fe68d977c29/image-4.jpg)

MIPS 32 module PC(PH 1, Rst, PCWrite, PCo, PCi); output [31: 0] PCo; input [31: 0] PCi; input PH 1, Rst, PCWrite; reg [31: 0] PCo; always @(posedge PH 1) PCo <= Rst ? 32'h 0000 : (PCWrite ? PCi - 32'h 0001 : PCi); endmodule 4 4 PC CPU Design IM T. -C. Huang / NCUE Spring 2005 RF ALU SE z DM 4

![MIPS 32 module IMPC Ins input 31 0 PC output 31 0 Ins reg MIPS 32 module IM(PC, Ins); input [31: 0] PC; output [31: 0] Ins; reg](https://slidetodoc.com/presentation_image/477e47a25e838924f6e12fe68d977c29/image-5.jpg)

MIPS 32 module IM(PC, Ins); input [31: 0] PC; output [31: 0] Ins; reg [31: 0] MEM [0: 31]; // Programming by initial block wire [31: 0] temp = MEM[PC[31: 0]]; wire [31: 0] Ins = temp; endmodule 4 4 PC CPU Design IM T. -C. Huang / NCUE Spring 2005 RF ALU SE z DM 5

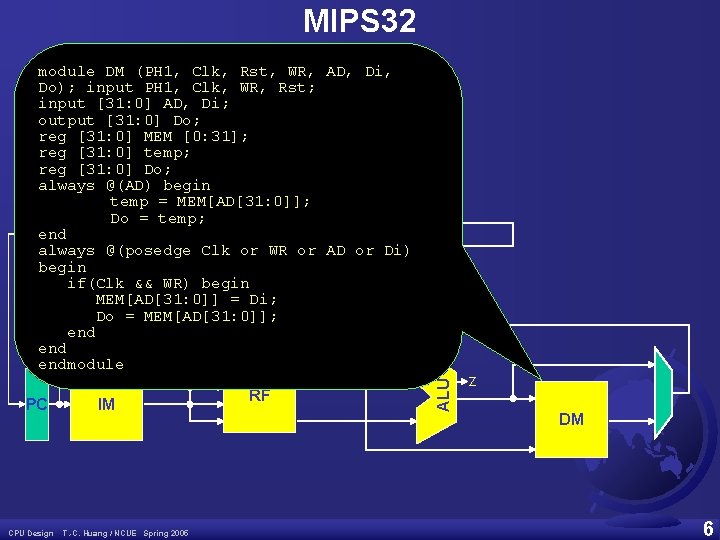

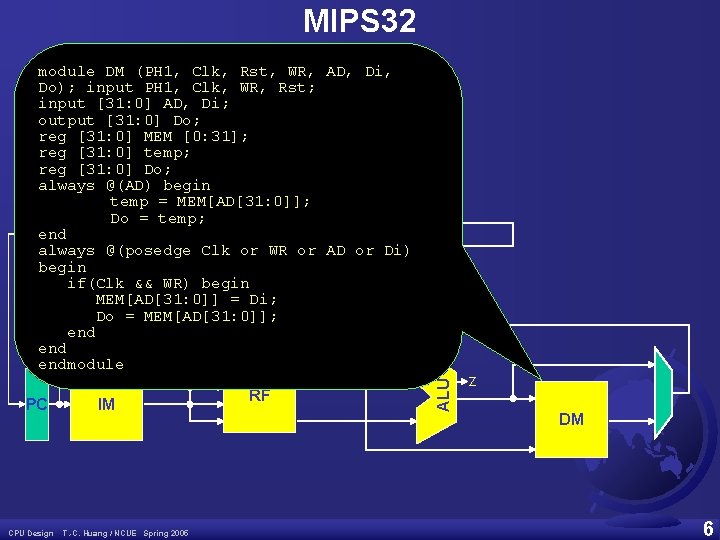

MIPS 32 PC CPU Design IM T. -C. Huang / NCUE Spring 2005 RF ALU module DM (PH 1, Clk, Rst, WR, AD, Di, Do); input PH 1, Clk, WR, Rst; input [31: 0] AD, Di; output [31: 0] Do; reg [31: 0] MEM [0: 31]; reg [31: 0] temp; reg [31: 0] Do; always @(AD) begin temp = MEM[AD[31: 0]]; Do = temp; end always @(posedge Clk or WR or AD or Di) 4 begin 4 if(Clk && WR) begin SE MEM[AD[31: 0]] = Di; Do = MEM[AD[31: 0]]; end endmodule z DM 6

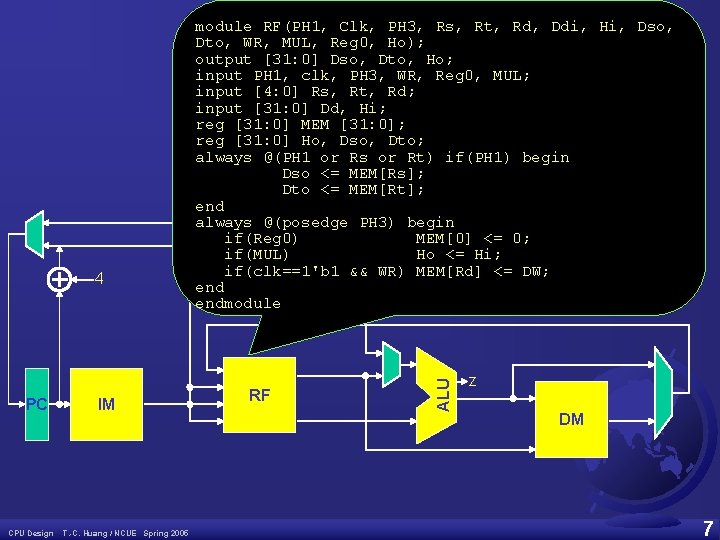

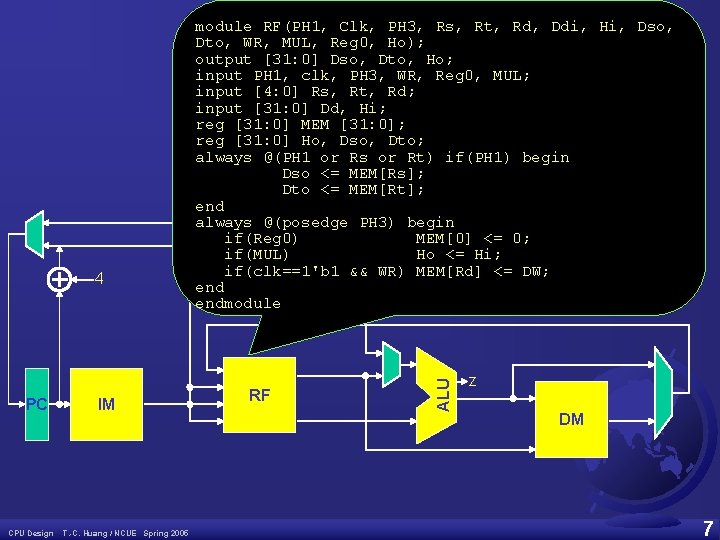

MIPS 32 PC CPU Design IM T. -C. Huang / NCUE Spring 2005 RF ALU 4 module RF(PH 1, Clk, PH 3, Rs, Rt, Rd, Ddi, Hi, Dso, Dto, WR, MUL, Reg 0, Ho); output [31: 0] Dso, Dto, Ho; input PH 1, clk, PH 3, WR, Reg 0, MUL; input [4: 0] Rs, Rt, Rd; input [31: 0] Dd, Hi; reg [31: 0] MEM [31: 0]; reg [31: 0] Ho, Dso, Dto; always @(PH 1 or Rs or Rt) if(PH 1) begin Dso <= MEM[Rs]; Dto <= MEM[Rt]; end always @(posedge PH 3) begin if(Reg 0) MEM[0] <= 0; if(MUL) Ho <= Hi; 4 if(clk==1'b 1 && WR) MEM[Rd] <= DW; end SE endmodule z DM 7

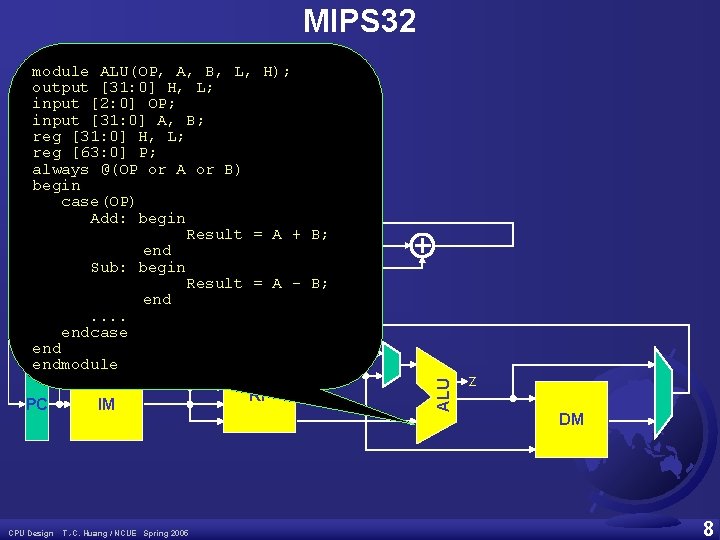

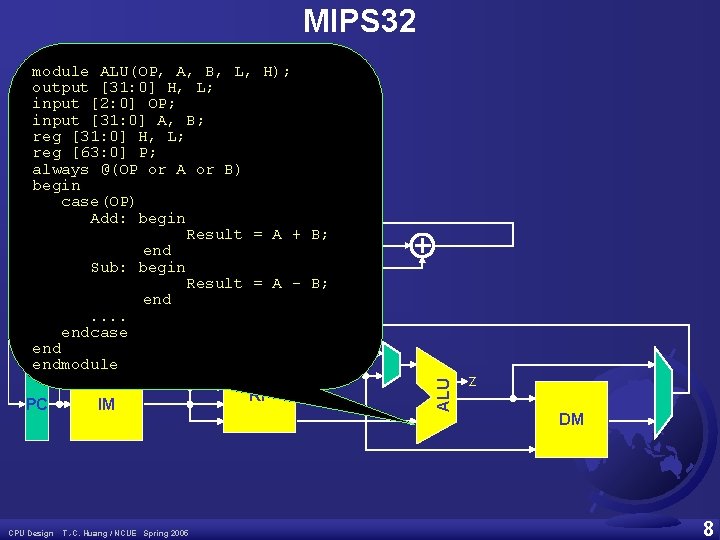

MIPS 32 PC CPU Design IM T. -C. Huang / NCUE Spring 2005 RF ALU module ALU(OP, A, B, L, H); output [31: 0] H, L; input [2: 0] OP; input [31: 0] A, B; reg [31: 0] H, L; reg [63: 0] P; always @(OP or A or B) begin case(OP) Add: begin Result = A + B; end 4 Sub: begin 4 Result = A - B; SE end. . endcase endmodule z DM 8

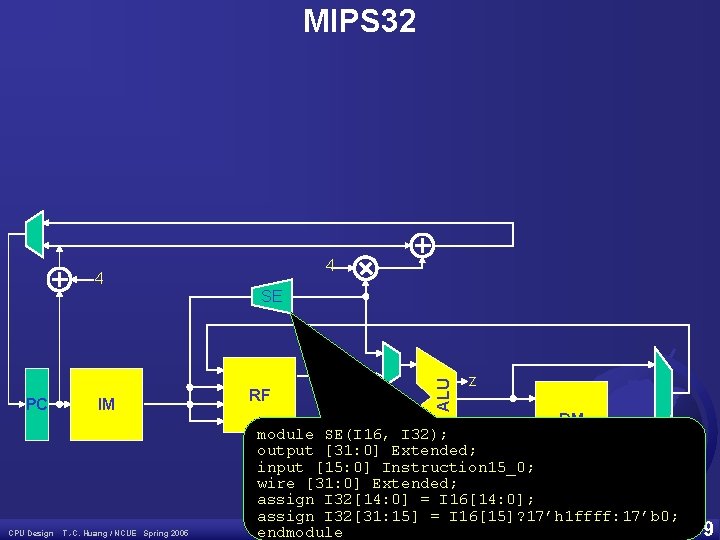

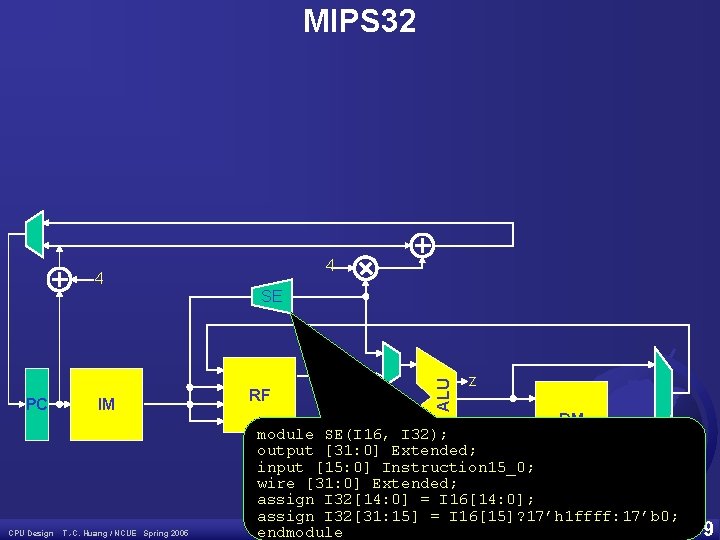

MIPS 32 4 4 PC CPU Design IM T. -C. Huang / NCUE Spring 2005 RF ALU SE z DM module SE(I 16, I 32); output [31: 0] Extended; input [15: 0] Instruction 15_0; wire [31: 0] Extended; assign I 32[14: 0] = I 16[14: 0]; assign I 32[31: 15] = I 16[15]? 17’h 1 ffff: 17’b 0; endmodule 9

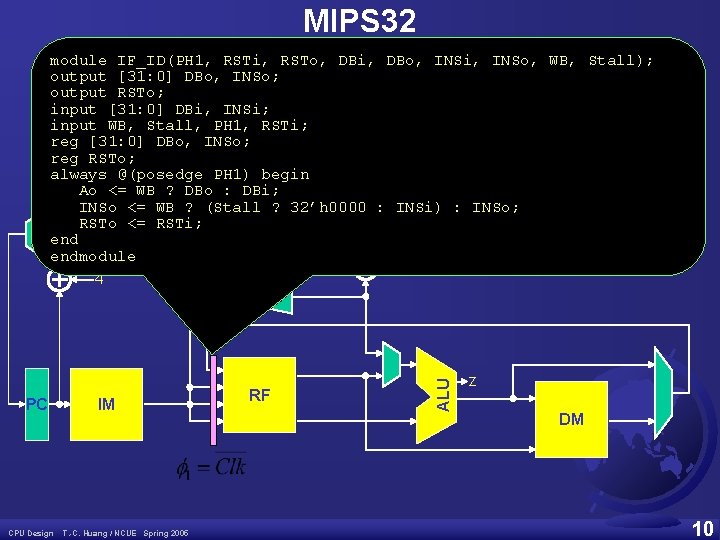

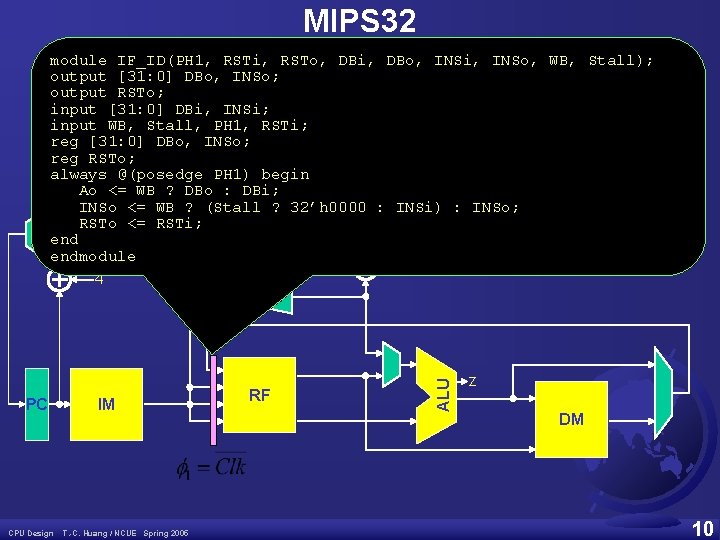

MIPS 32 PC CPU Design IM T. -C. Huang / NCUE Spring 2005 RF ALU module IF_ID(PH 1, RSTi, RSTo, DBi, DBo, INSi, INSo, WB, Stall); output [31: 0] DBo, INSo; output RSTo; input [31: 0] DBi, INSi; input WB, Stall, PH 1, RSTi; reg [31: 0] DBo, INSo; reg RSTo; always @(posedge PH 1) begin Ao <= WB ? DBo : DBi; INSo <= WB ? (Stall ? 32’h 0000 : INSi) : INSo; RSTo <= RSTi; endmodule 4 4 SE z DM 10

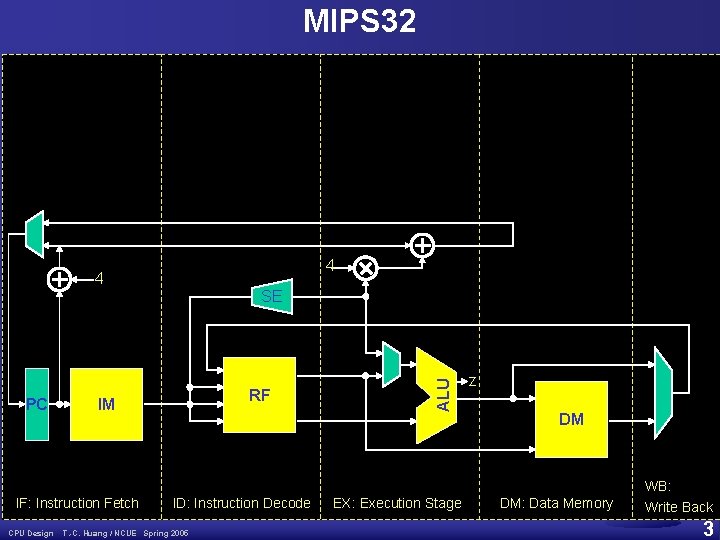

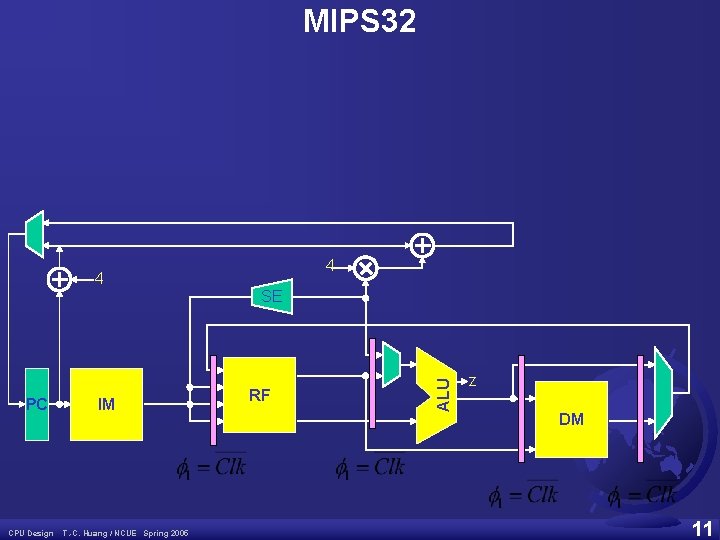

MIPS 32 4 4 PC CPU Design IM T. -C. Huang / NCUE Spring 2005 RF ALU SE z DM 11