Lecture Pipelining Hazards Topics structural and data hazards

![Problem 4 • Convert this C code into equivalent RISC assembly instructions a[i] = Problem 4 • Convert this C code into equivalent RISC assembly instructions a[i] =](https://slidetodoc.com/presentation_image_h2/ef24aeb7e71588bbee50210806da5624/image-6.jpg)

![Problem 4 • Convert this C code into equivalent RISC assembly instructions a[i] = Problem 4 • Convert this C code into equivalent RISC assembly instructions a[i] =](https://slidetodoc.com/presentation_image_h2/ef24aeb7e71588bbee50210806da5624/image-7.jpg)

- Slides: 21

Lecture: Pipelining Hazards • Topics: structural and data hazards • HW 2 posted; due in a week 1

RISC/CISC Loads/Stores Registers and memory Complex and reduced instrs Format of a load/store 2

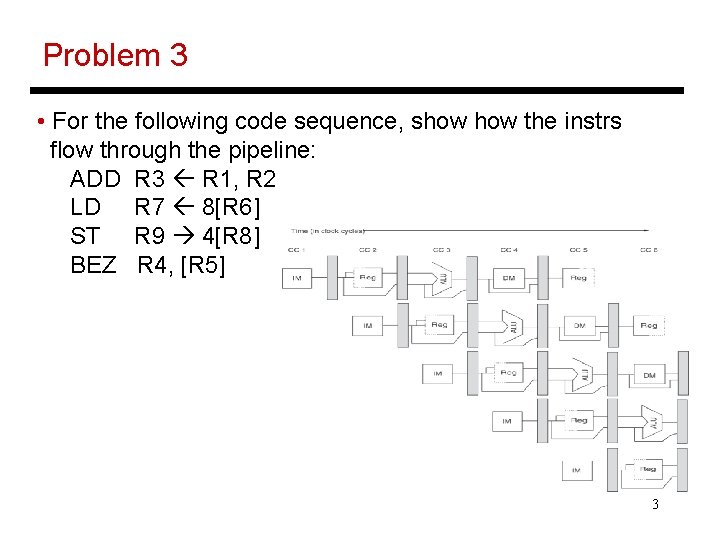

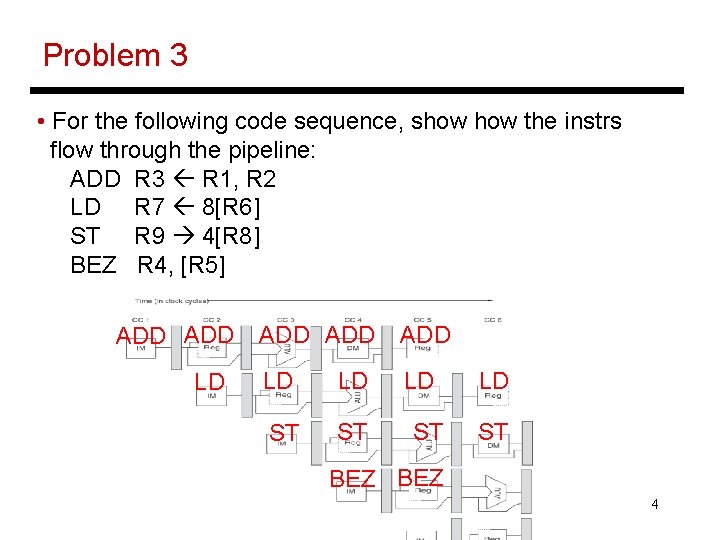

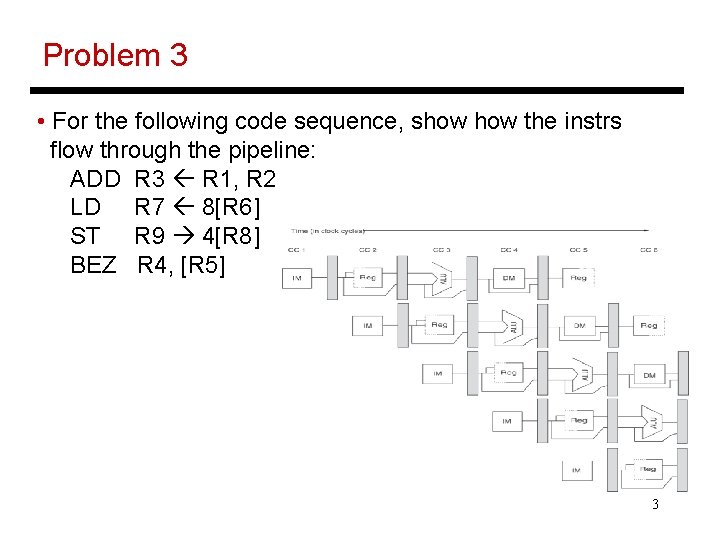

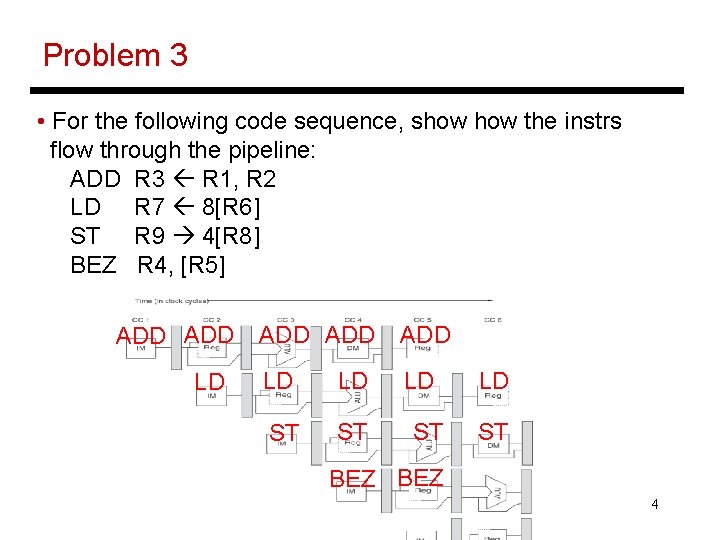

Problem 3 • For the following code sequence, show the instrs flow through the pipeline: ADD R 3 R 1, R 2 LD R 7 8[R 6] ST R 9 4[R 8] BEZ R 4, [R 5] 3

Problem 3 • For the following code sequence, show the instrs flow through the pipeline: ADD R 3 R 1, R 2 LD R 7 8[R 6] ST R 9 4[R 8] BEZ R 4, [R 5] ADD LD ADD ADD LD LD LD ST ST ST LD ST BEZ 4

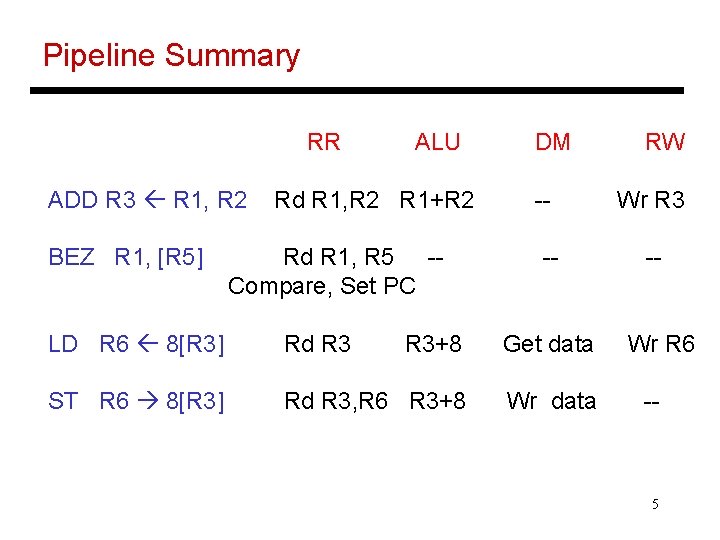

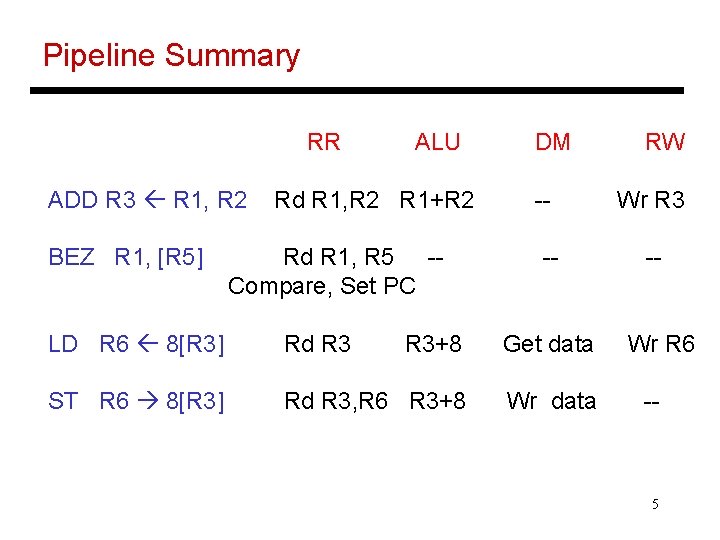

Pipeline Summary RR ADD R 3 R 1, R 2 BEZ R 1, [R 5] ALU Rd R 1, R 2 R 1+R 2 Rd R 1, R 5 -Compare, Set PC DM --- LD R 6 8[R 3] Rd R 3+8 Get data ST R 6 8[R 3] Rd R 3, R 6 R 3+8 Wr data RW Wr R 3 -Wr R 6 -- 5

![Problem 4 Convert this C code into equivalent RISC assembly instructions ai Problem 4 • Convert this C code into equivalent RISC assembly instructions a[i] =](https://slidetodoc.com/presentation_image_h2/ef24aeb7e71588bbee50210806da5624/image-6.jpg)

Problem 4 • Convert this C code into equivalent RISC assembly instructions a[i] = b[i] + c[i]; 6

![Problem 4 Convert this C code into equivalent RISC assembly instructions ai Problem 4 • Convert this C code into equivalent RISC assembly instructions a[i] =](https://slidetodoc.com/presentation_image_h2/ef24aeb7e71588bbee50210806da5624/image-7.jpg)

Problem 4 • Convert this C code into equivalent RISC assembly instructions a[i] = b[i] + c[i]; LD R 2, [R 1] # R 1 has the address for variable i MUL R 3, R 2, 8 # the offset from the start of the array ADD R 7, R 3, R 4 # R 4 has the address of a[0] ADD R 8, R 3, R 5 # R 5 has the address of b[0] ADD R 9, R 3, R 6 # R 6 has the address of c[0] LD R 10, [R 8] # Bringing b[i] LD R 11, [R 9] # Bringing c[i] ADD R 12, R 11, R 10 # Sum is in R 12 7 ST R 12, [R 7] # Putting result in a[i]

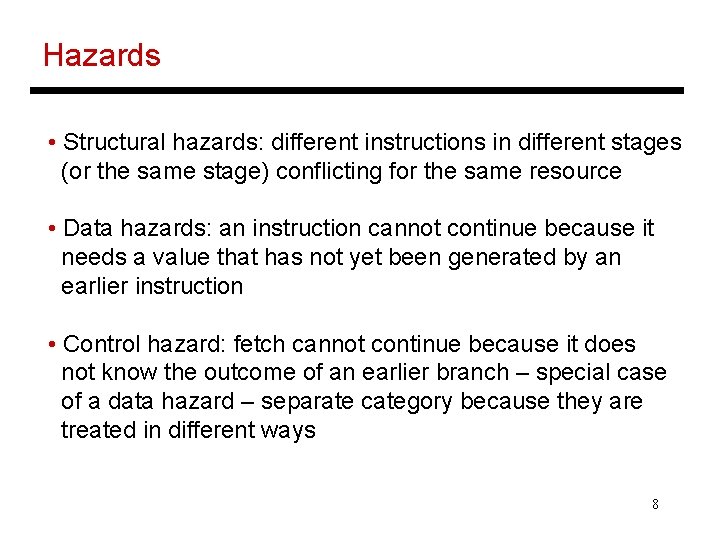

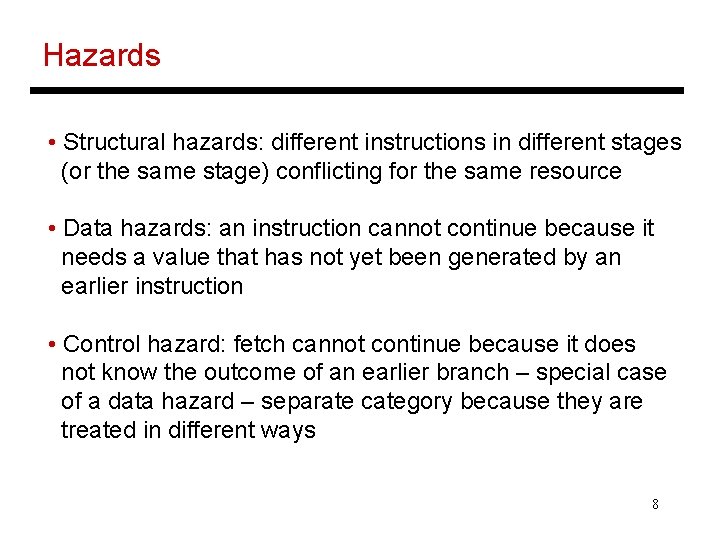

Hazards • Structural hazards: different instructions in different stages (or the same stage) conflicting for the same resource • Data hazards: an instruction cannot continue because it needs a value that has not yet been generated by an earlier instruction • Control hazard: fetch cannot continue because it does not know the outcome of an earlier branch – special case of a data hazard – separate category because they are treated in different ways 8

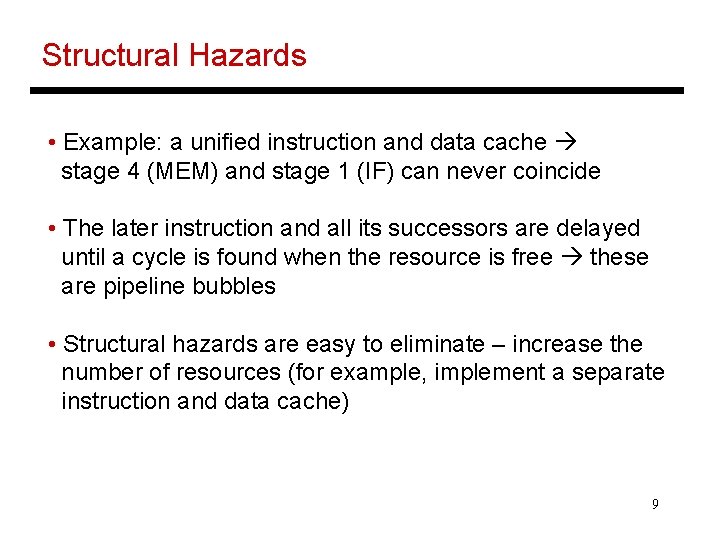

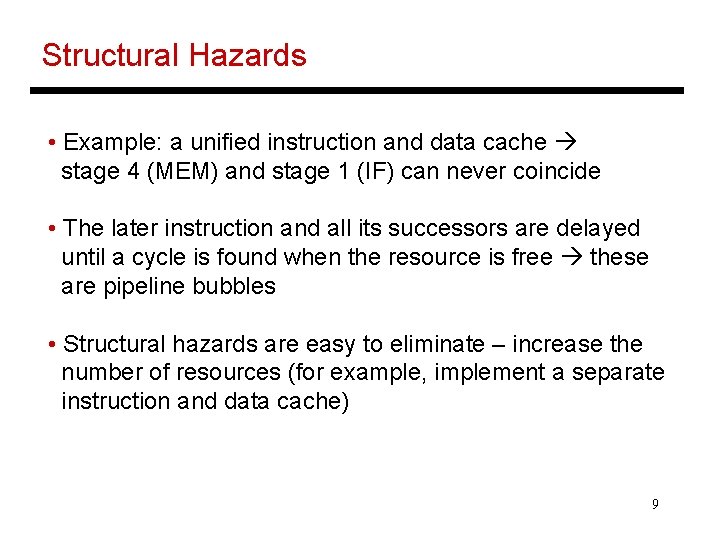

Structural Hazards • Example: a unified instruction and data cache stage 4 (MEM) and stage 1 (IF) can never coincide • The later instruction and all its successors are delayed until a cycle is found when the resource is free these are pipeline bubbles • Structural hazards are easy to eliminate – increase the number of resources (for example, implement a separate instruction and data cache) 9

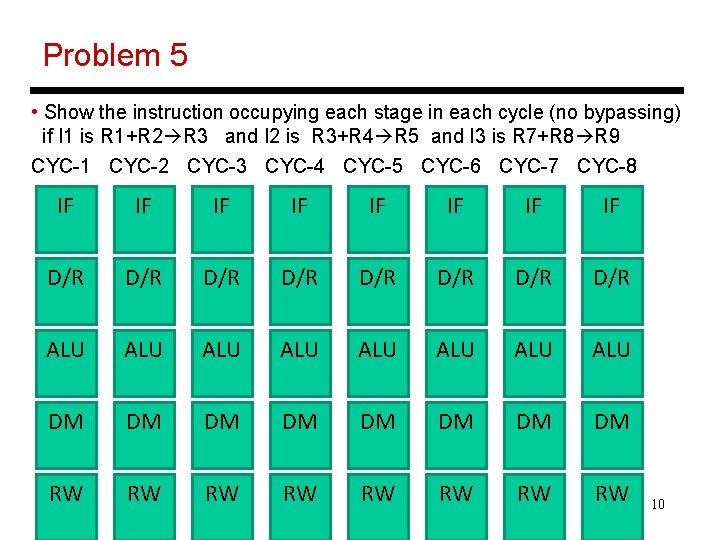

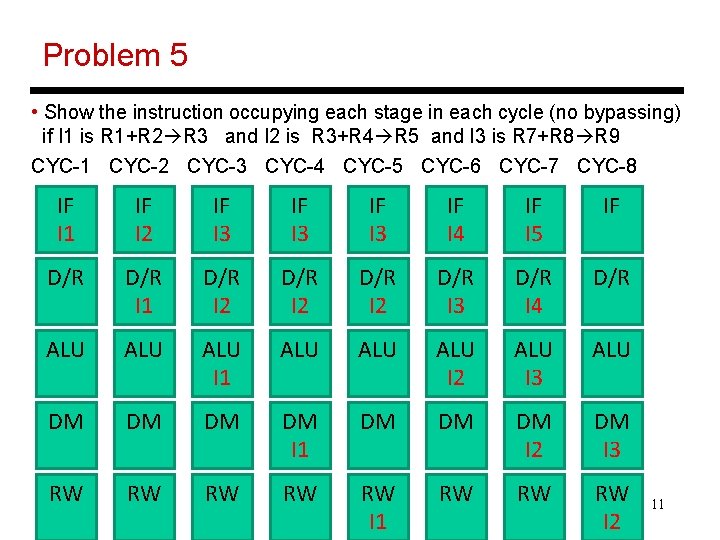

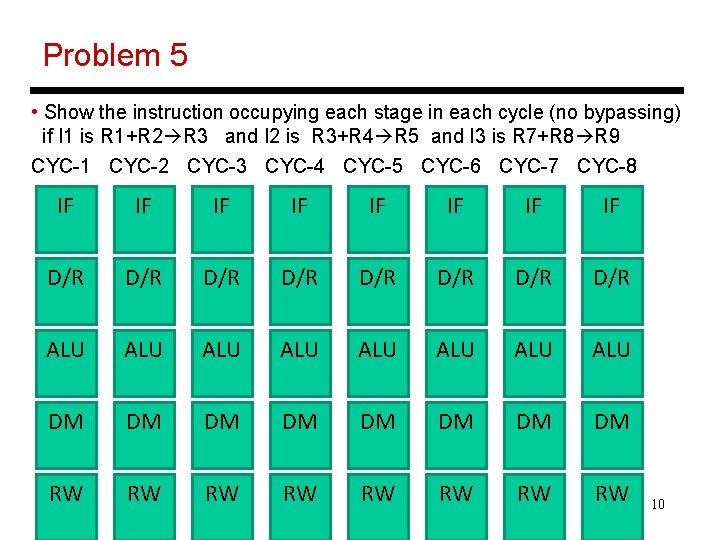

Problem 5 • Show the instruction occupying each stage in each cycle (no bypassing) if I 1 is R 1+R 2 R 3 and I 2 is R 3+R 4 R 5 and I 3 is R 7+R 8 R 9 CYC-1 CYC-2 CYC-3 CYC-4 CYC-5 CYC-6 CYC-7 CYC-8 IF IF D/R D/R ALU ALU DM DM RW RW 10

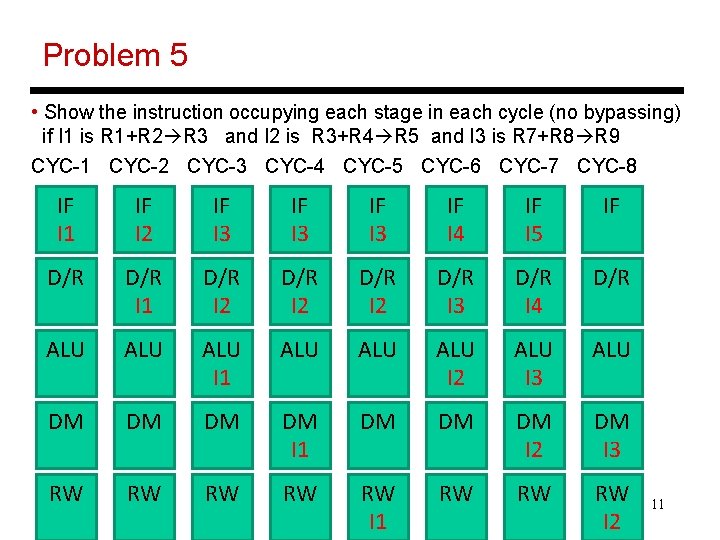

Problem 5 • Show the instruction occupying each stage in each cycle (no bypassing) if I 1 is R 1+R 2 R 3 and I 2 is R 3+R 4 R 5 and I 3 is R 7+R 8 R 9 CYC-1 CYC-2 CYC-3 CYC-4 CYC-5 CYC-6 CYC-7 CYC-8 IF I 1 IF I 2 IF I 3 IF I 4 IF I 5 IF D/R I 1 D/R I 2 D/R I 3 D/R I 4 D/R ALU ALU I 1 ALU ALU I 2 ALU I 3 ALU DM DM I 1 DM DM DM I 2 DM I 3 RW RW RW I 1 RW RW RW I 2 11

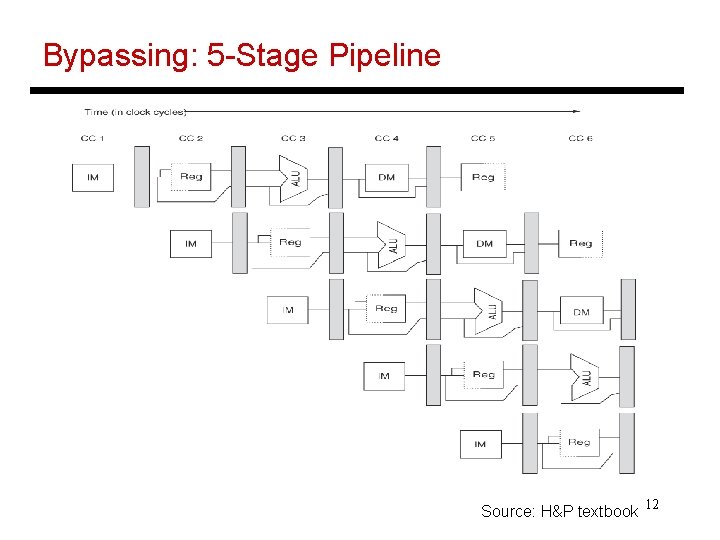

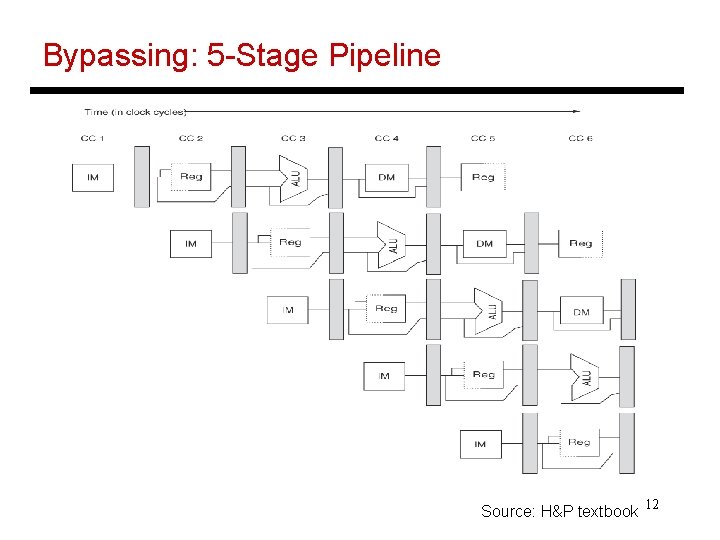

Bypassing: 5 -Stage Pipeline Source: H&P textbook 12

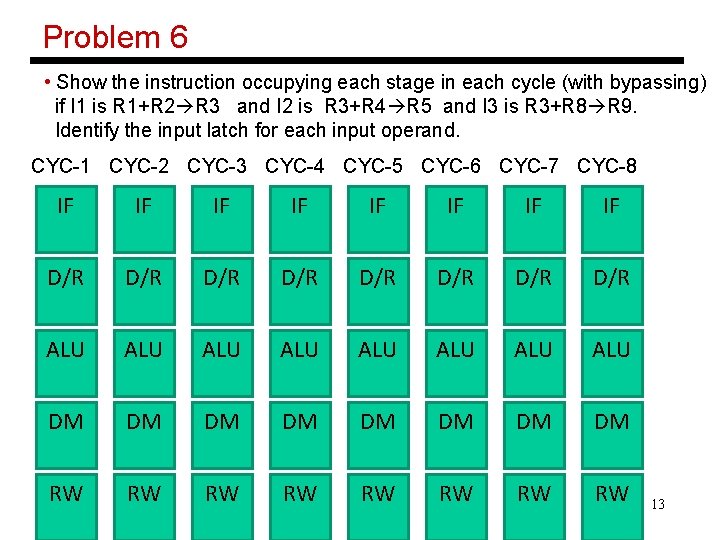

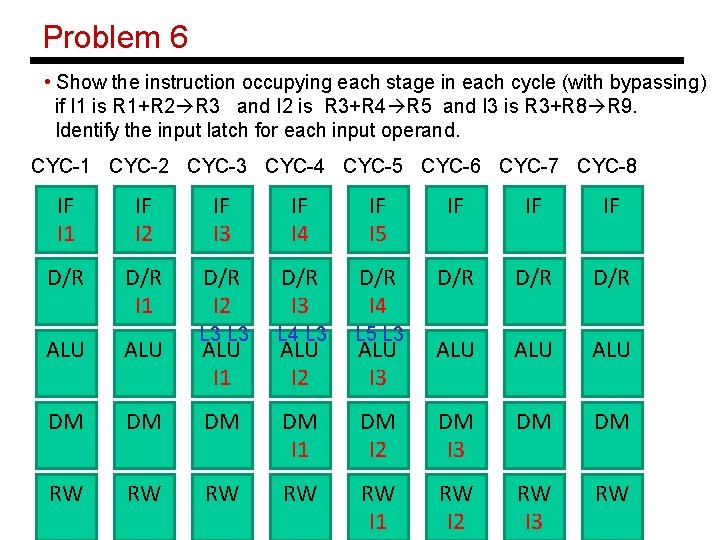

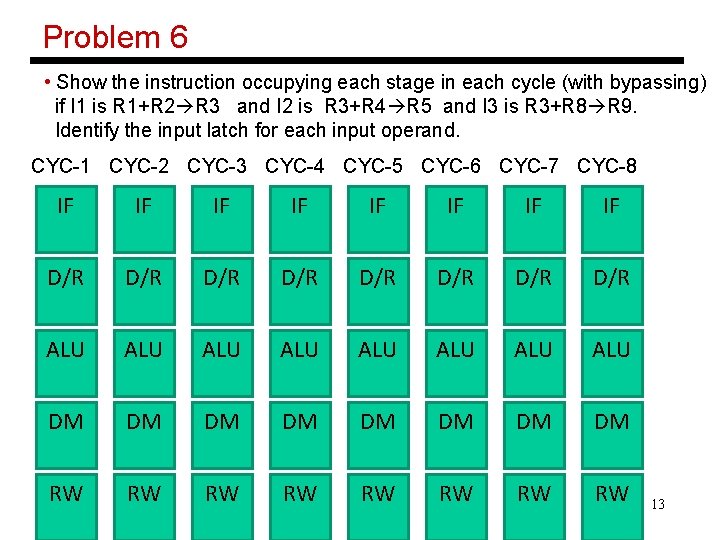

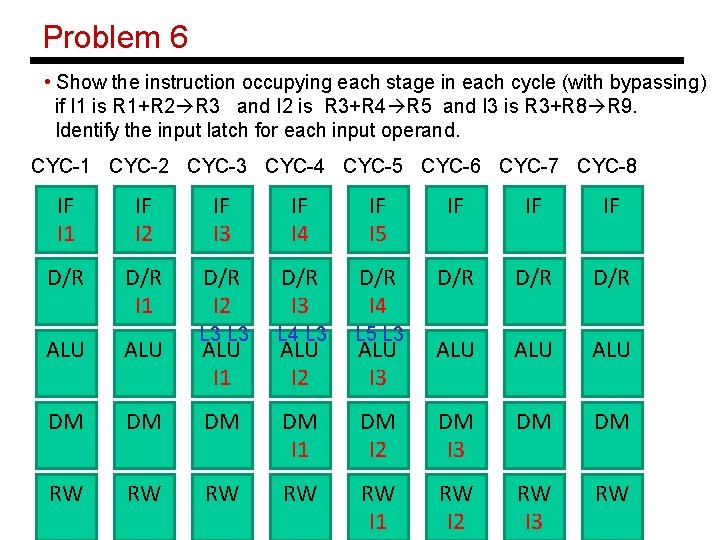

Problem 6 • Show the instruction occupying each stage in each cycle (with bypassing) if I 1 is R 1+R 2 R 3 and I 2 is R 3+R 4 R 5 and I 3 is R 3+R 8 R 9. Identify the input latch for each input operand. CYC-1 CYC-2 CYC-3 CYC-4 CYC-5 CYC-6 CYC-7 CYC-8 IF IF D/R D/R ALU ALU DM DM RW RW 13

Problem 6 • Show the instruction occupying each stage in each cycle (with bypassing) if I 1 is R 1+R 2 R 3 and I 2 is R 3+R 4 R 5 and I 3 is R 3+R 8 R 9. Identify the input latch for each input operand. CYC-1 CYC-2 CYC-3 CYC-4 CYC-5 CYC-6 CYC-7 CYC-8 IF I 1 IF I 2 IF I 3 IF I 4 IF I 5 IF IF IF D/R I 1 D/R I 2 D/R I 3 D/R I 4 D/R D/R L 3 L 4 L 3 L 5 L 3 ALU I 3 ALU ALU ALU I 1 ALU I 2 DM DM I 1 DM I 2 DM I 3 DM DM RW RW RW I 1 RW I 2 RW I 3 RW

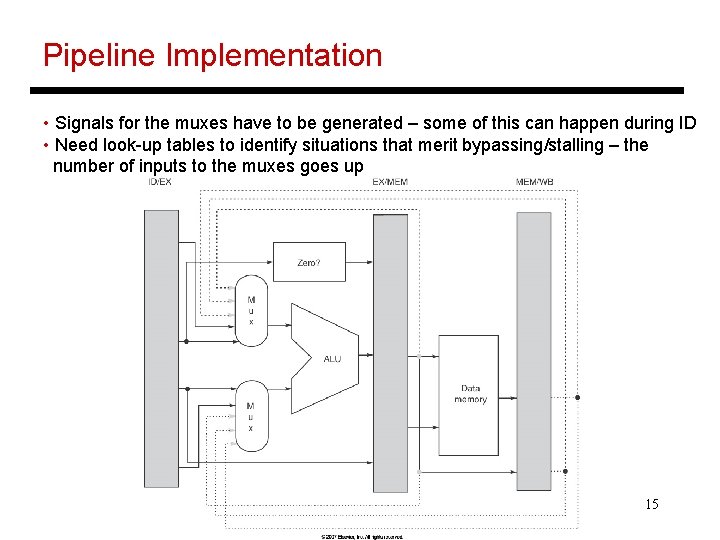

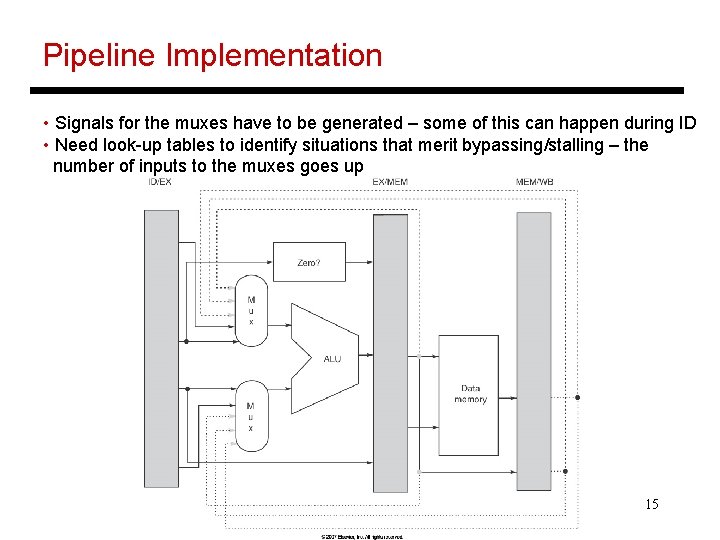

Pipeline Implementation • Signals for the muxes have to be generated – some of this can happen during ID • Need look-up tables to identify situations that merit bypassing/stalling – the number of inputs to the muxes goes up 15

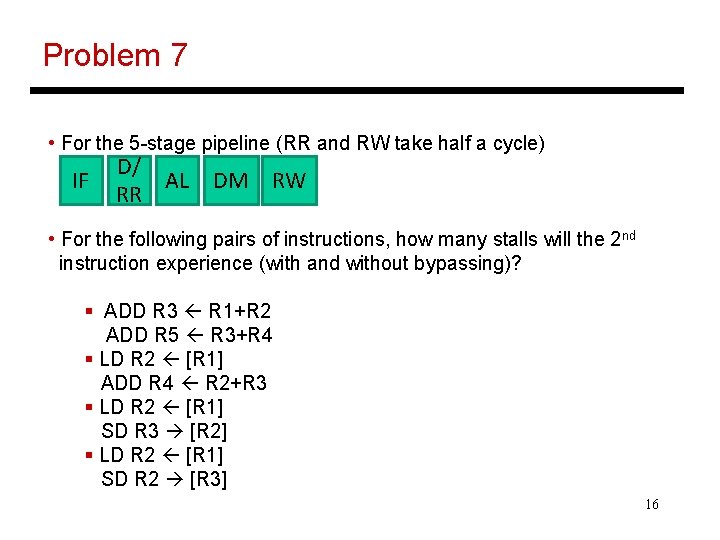

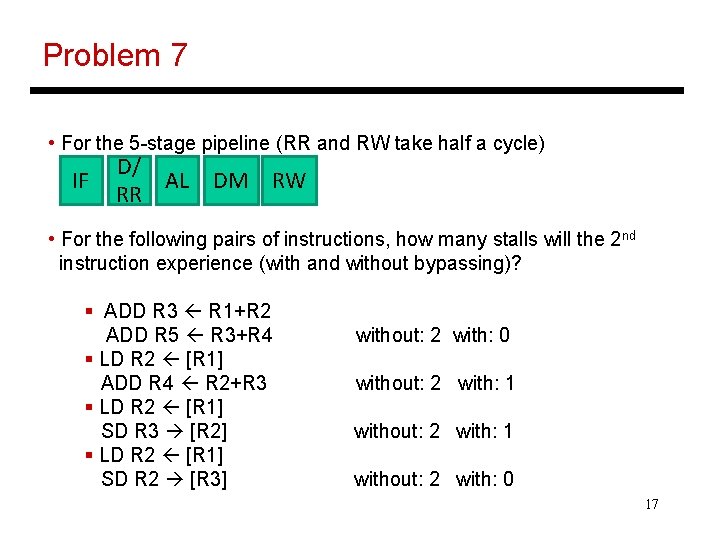

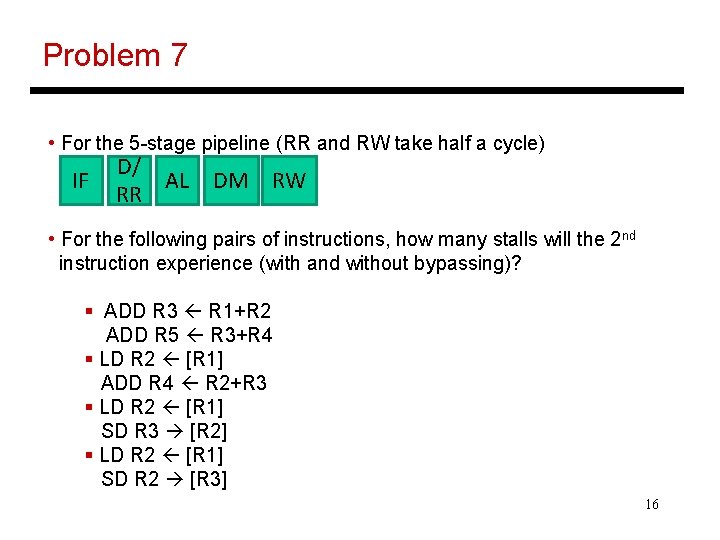

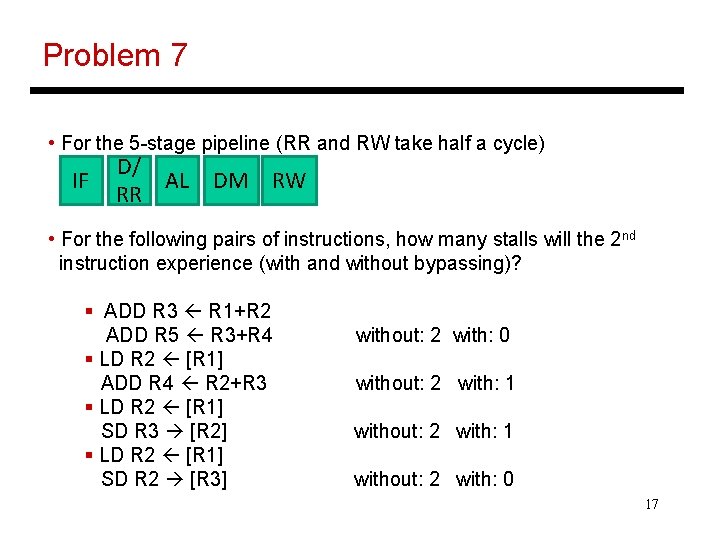

Problem 7 • For the 5 -stage pipeline (RR and RW take half a cycle) IF D/ AL RR DM RW • For the following pairs of instructions, how many stalls will the 2 nd instruction experience (with and without bypassing)? § ADD R 3 R 1+R 2 ADD R 5 R 3+R 4 § LD R 2 [R 1] ADD R 4 R 2+R 3 § LD R 2 [R 1] SD R 3 [R 2] § LD R 2 [R 1] SD R 2 [R 3] 16

Problem 7 • For the 5 -stage pipeline (RR and RW take half a cycle) IF D/ AL RR DM RW • For the following pairs of instructions, how many stalls will the 2 nd instruction experience (with and without bypassing)? § ADD R 3 R 1+R 2 ADD R 5 R 3+R 4 § LD R 2 [R 1] ADD R 4 R 2+R 3 § LD R 2 [R 1] SD R 3 [R 2] § LD R 2 [R 1] SD R 2 [R 3] without: 2 with: 0 without: 2 with: 1 without: 2 with: 0 17

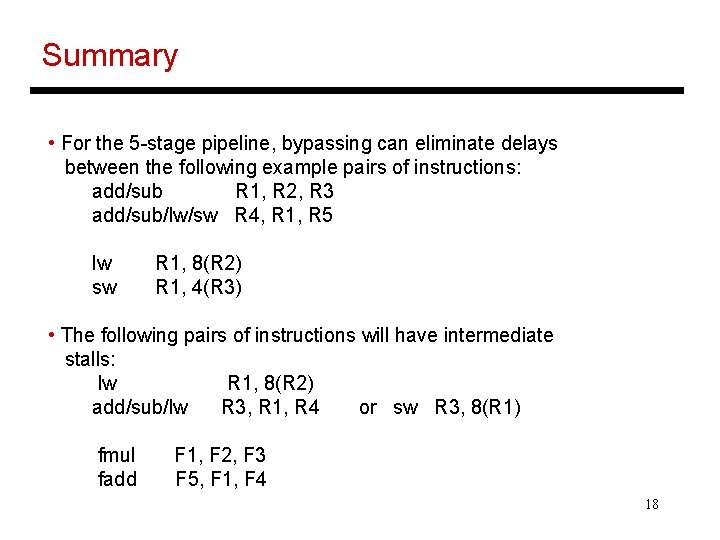

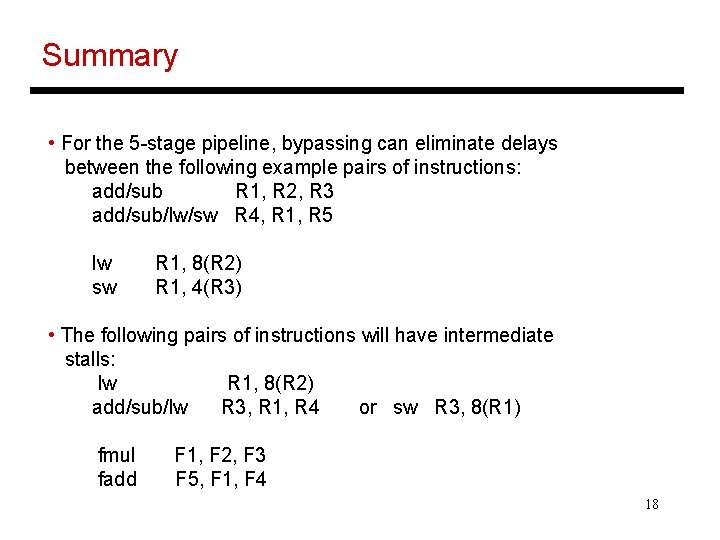

Summary • For the 5 -stage pipeline, bypassing can eliminate delays between the following example pairs of instructions: add/sub R 1, R 2, R 3 add/sub/lw/sw R 4, R 1, R 5 lw sw R 1, 8(R 2) R 1, 4(R 3) • The following pairs of instructions will have intermediate stalls: lw R 1, 8(R 2) add/sub/lw R 3, R 1, R 4 or sw R 3, 8(R 1) fmul fadd F 1, F 2, F 3 F 5, F 1, F 4 18

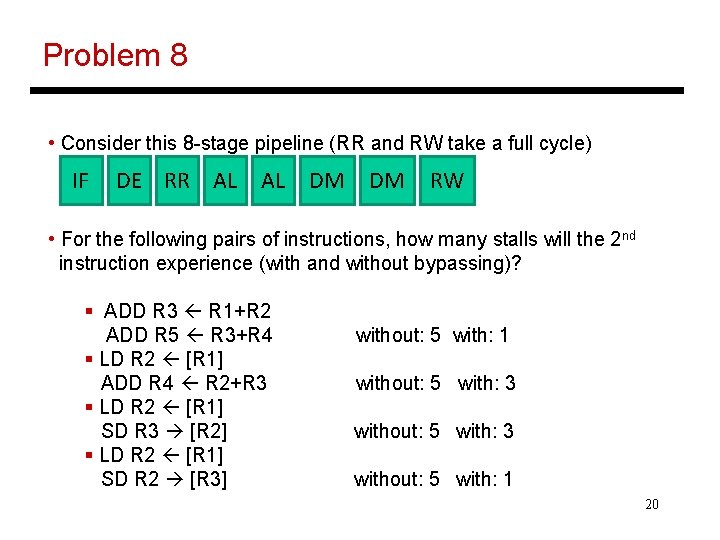

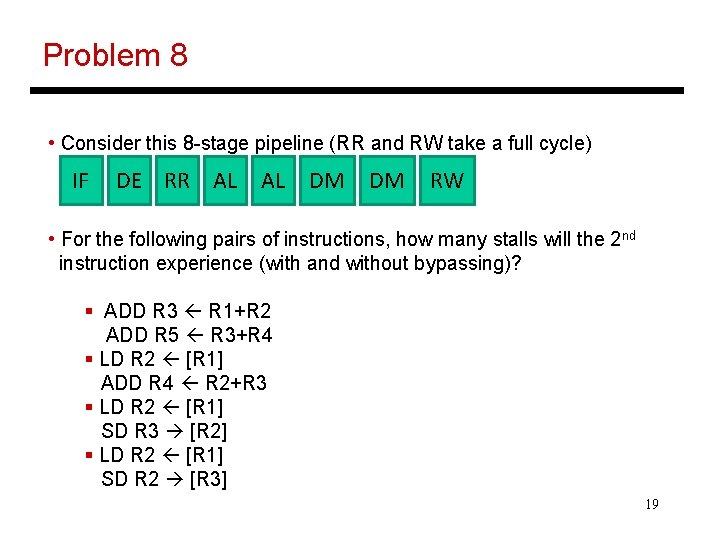

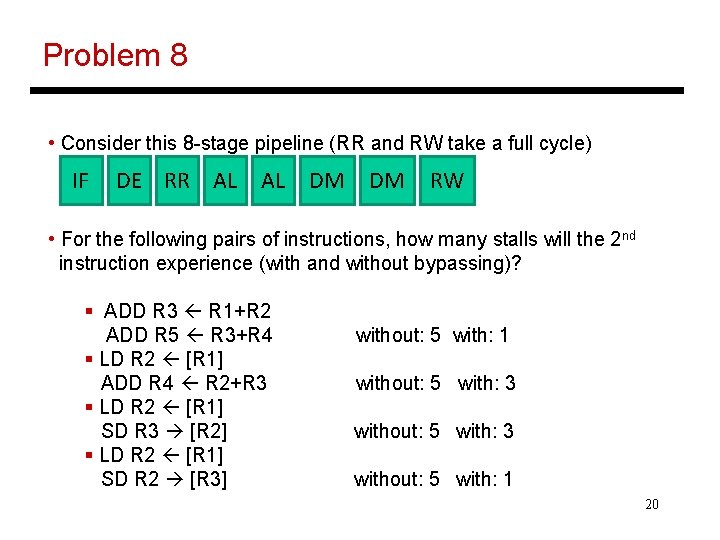

Problem 8 • Consider this 8 -stage pipeline (RR and RW take a full cycle) IF DE RR AL AL DM DM RW • For the following pairs of instructions, how many stalls will the 2 nd instruction experience (with and without bypassing)? § ADD R 3 R 1+R 2 ADD R 5 R 3+R 4 § LD R 2 [R 1] ADD R 4 R 2+R 3 § LD R 2 [R 1] SD R 3 [R 2] § LD R 2 [R 1] SD R 2 [R 3] 19

Problem 8 • Consider this 8 -stage pipeline (RR and RW take a full cycle) IF DE RR AL AL DM DM RW • For the following pairs of instructions, how many stalls will the 2 nd instruction experience (with and without bypassing)? § ADD R 3 R 1+R 2 ADD R 5 R 3+R 4 § LD R 2 [R 1] ADD R 4 R 2+R 3 § LD R 2 [R 1] SD R 3 [R 2] § LD R 2 [R 1] SD R 2 [R 3] without: 5 with: 1 without: 5 with: 3 without: 5 with: 1 20

Title • Bullet 21