Lecture 2 Digital Audio Mike Wirthlin Digital Audio

- Slides: 48

Lecture 2 Digital Audio Mike Wirthlin

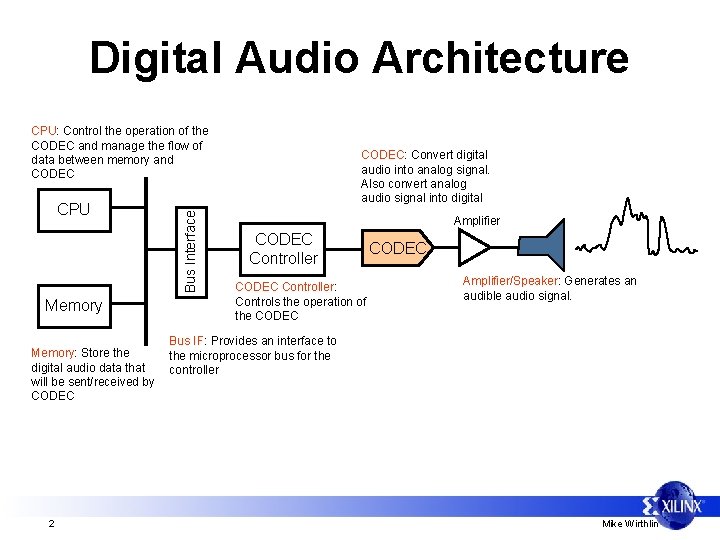

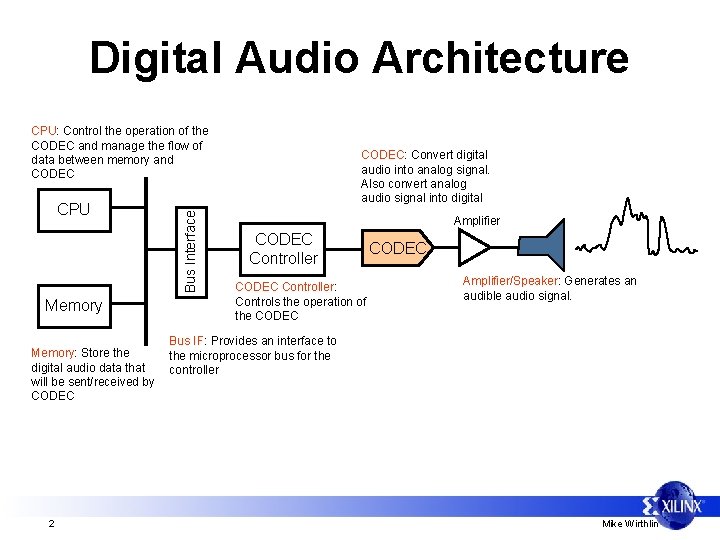

Digital Audio Architecture CPU Memory: Store the digital audio data that will be sent/received by CODEC 2 Bus Interface CPU: Control the operation of the CODEC and manage the flow of data between memory and CODEC: Convert digital audio into analog signal. Also convert analog audio signal into digital Amplifier CODEC Controller: Controls the operation of the CODEC Amplifier/Speaker: Generates an audible audio signal. Bus IF: Provides an interface to the microprocessor bus for the controller Mike Wirthlin

Outline • 1. Fundamentals of Digital Audio • 2. Digital to Analog & Analog to Digital Converters • 3. Interfacing Digital Audio to CPU • 4. Example: AC 97 3 Mike Wirthlin

1. Fundamentals of Digital Audio 4 Mike Wirthlin

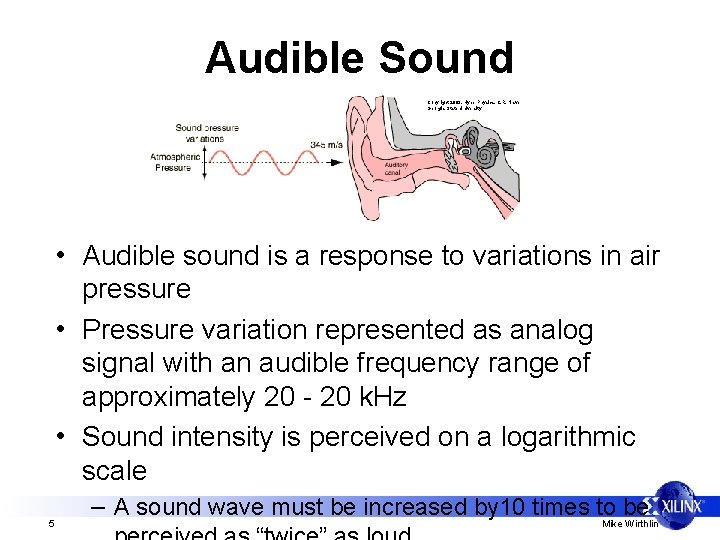

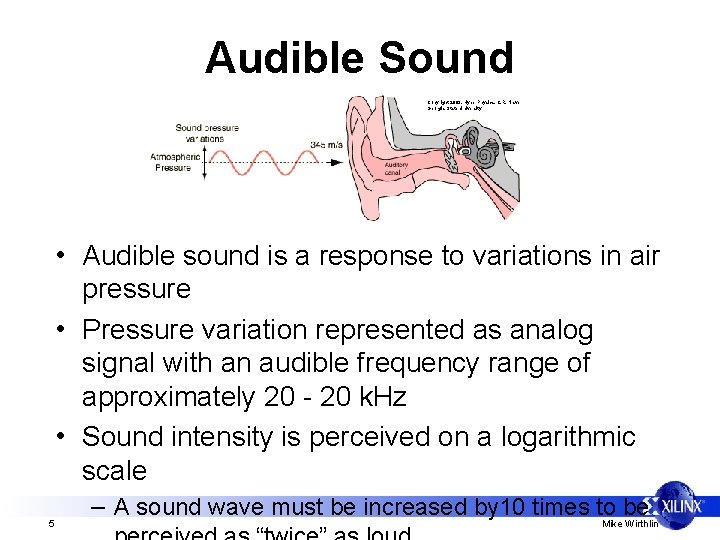

Audible Sound Copyright 2003, Hyper. Physics, C. R. Nave Georgia State University • Audible sound is a response to variations in air pressure • Pressure variation represented as analog signal with an audible frequency range of approximately 20 - 20 k. Hz • Sound intensity is perceived on a logarithmic scale 5 – A sound wave must be increased by 10 times to be Mike Wirthlin

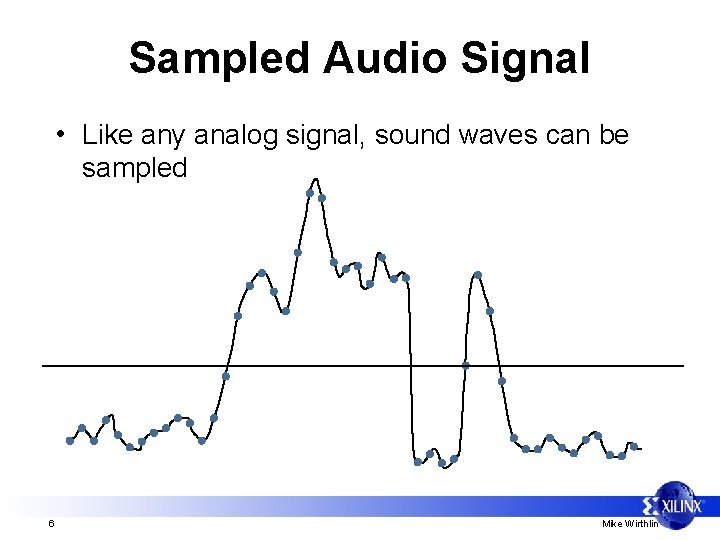

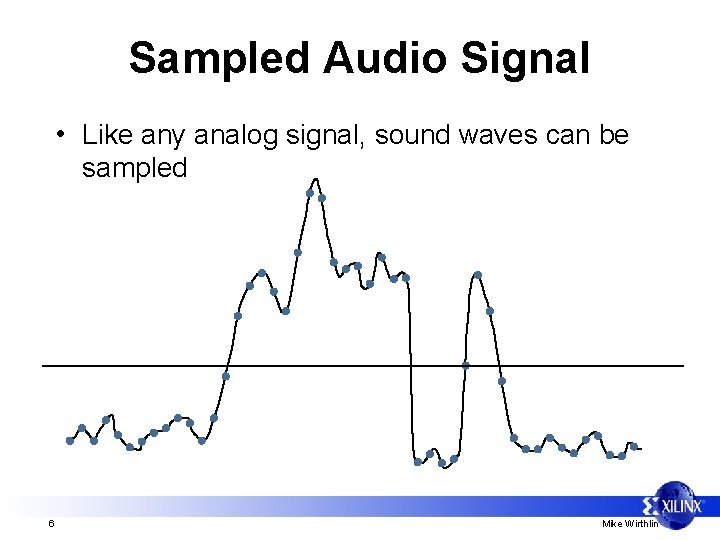

Sampled Audio Signal • Like any analog signal, sound waves can be sampled 6 Mike Wirthlin

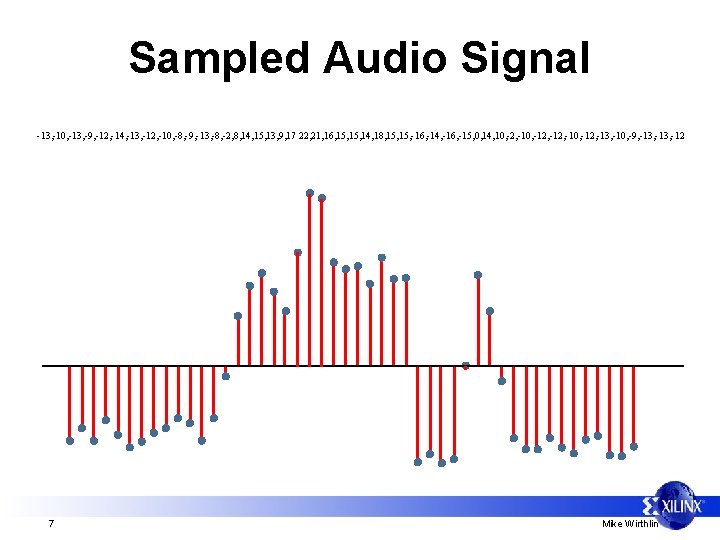

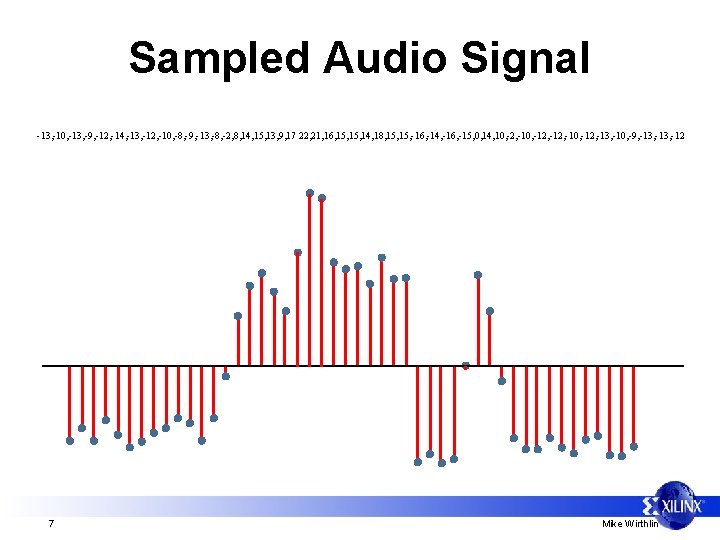

Sampled Audio Signal -13, -10, -13, -9, -12, -14, -13, -12, -10, -8, -9, -13, -8, -2, 8, 14, 15, 13, 9, 17 22, 21, 16, 15, 14, 18, 15, -16, -14, -16, -15, 0, 14, 10, -2, -10, -12, -13, -10, -9, -13, -12 7 Mike Wirthlin

Sampled Audio Signal Pulse Code Modulation (PCM): Encoding of analog signal with digital signals sampled at regular intervals. 8 Mike Wirthlin

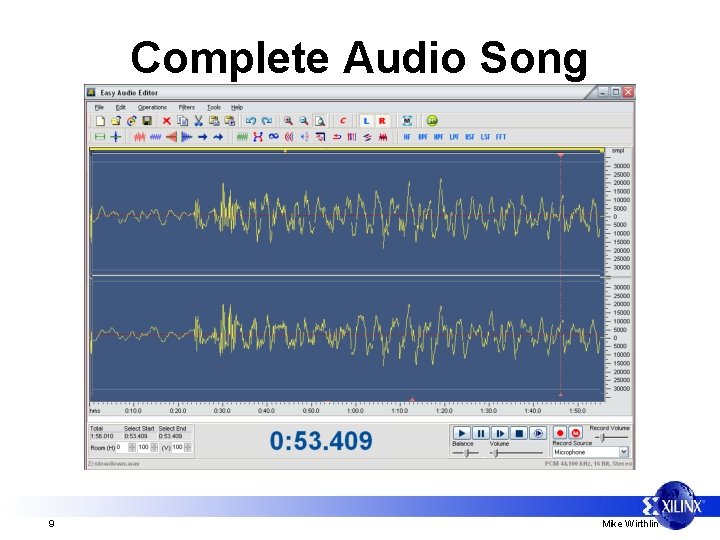

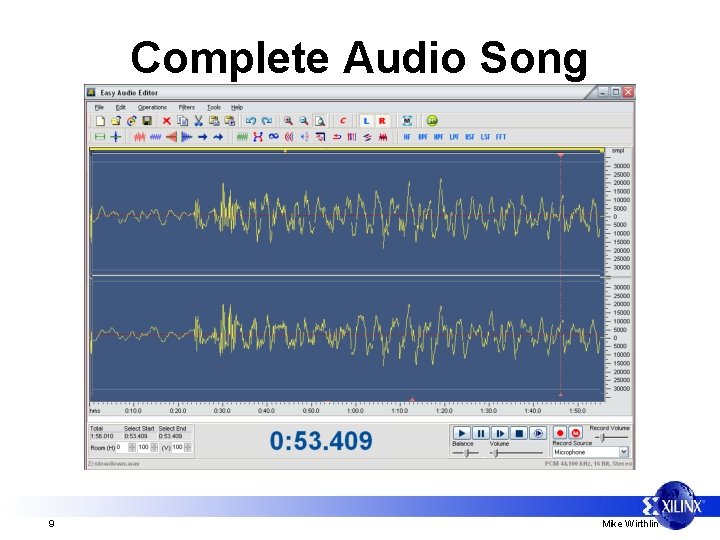

Complete Audio Song 9 Mike Wirthlin

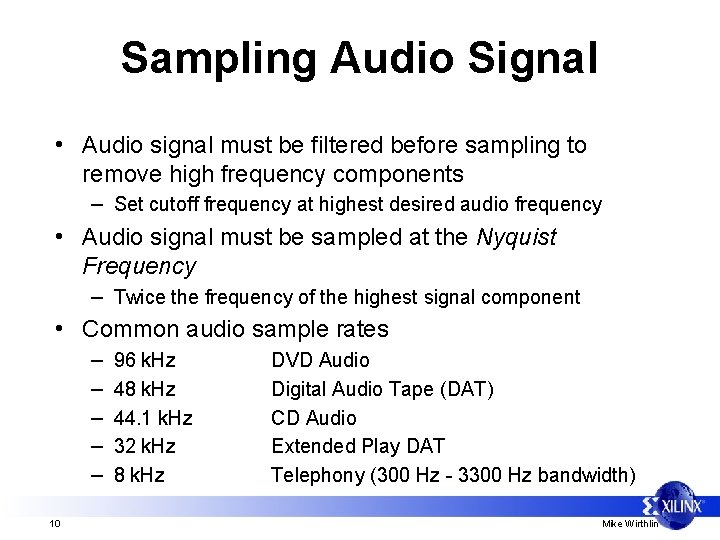

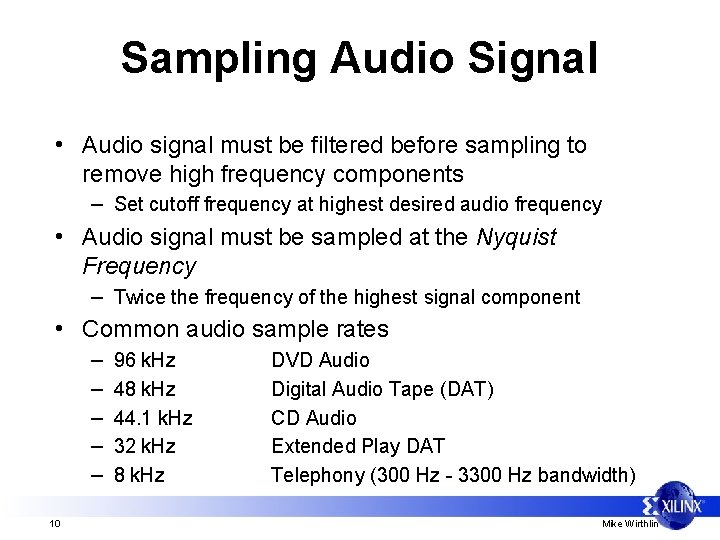

Sampling Audio Signal • Audio signal must be filtered before sampling to remove high frequency components – Set cutoff frequency at highest desired audio frequency • Audio signal must be sampled at the Nyquist Frequency – Twice the frequency of the highest signal component • Common audio sample rates – – – 10 96 k. Hz 48 k. Hz 44. 1 k. Hz 32 k. Hz 8 k. Hz DVD Audio Digital Audio Tape (DAT) CD Audio Extended Play DAT Telephony (300 Hz - 3300 Hz bandwidth) Mike Wirthlin

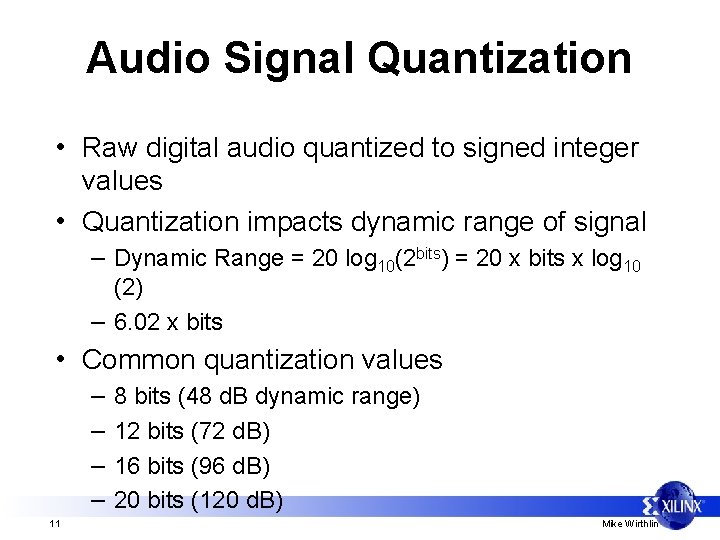

Audio Signal Quantization • Raw digital audio quantized to signed integer values • Quantization impacts dynamic range of signal – Dynamic Range = 20 log 10(2 bits) = 20 x bits x log 10 (2) – 6. 02 x bits • Common quantization values – – 11 8 bits (48 d. B dynamic range) 12 bits (72 d. B) 16 bits (96 d. B) 20 bits (120 d. B) Mike Wirthlin

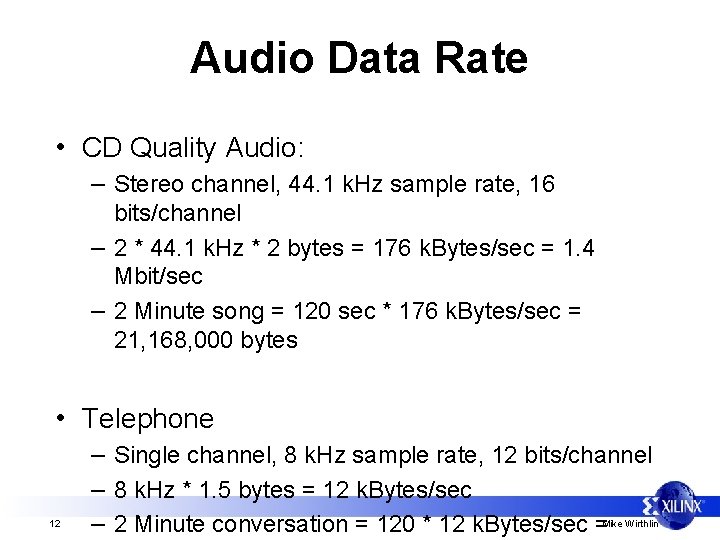

Audio Data Rate • CD Quality Audio: – Stereo channel, 44. 1 k. Hz sample rate, 16 bits/channel – 2 * 44. 1 k. Hz * 2 bytes = 176 k. Bytes/sec = 1. 4 Mbit/sec – 2 Minute song = 120 sec * 176 k. Bytes/sec = 21, 168, 000 bytes • Telephone 12 – Single channel, 8 k. Hz sample rate, 12 bits/channel – 8 k. Hz * 1. 5 bytes = 12 k. Bytes/sec – 2 Minute conversation = 120 * 12 k. Bytes/sec = Mike Wirthlin

Audio Compression • Audio data can be compressed to reduced the amount of data – -Law, and A-law – ADPCM bits – MPEG logarithmic encoding Compress 16 -bit data in 4 Perceptual coding • Example: 2 minute raw stereo audio vs. MP 3 encoding – Raw: 21, 168, 000 bytes – MPEG: ~2, 000 bytes (10 x compression) 13 Mike Wirthlin

Digital Audio Formats • Self Describing Formats – Contain sample rate, encoding, #channels file/stream • • • . au. aif(f). mp 3. ra. wav Ne. XT, Sun format Apple, SGI MPEG Standard Real Networks Microsoft • Audio File Format FAQ – http: //sox. sourceforge. net/Audio. Formats. html 14 Mike Wirthlin

2. Digital/Analog Conversion 15 Mike Wirthlin

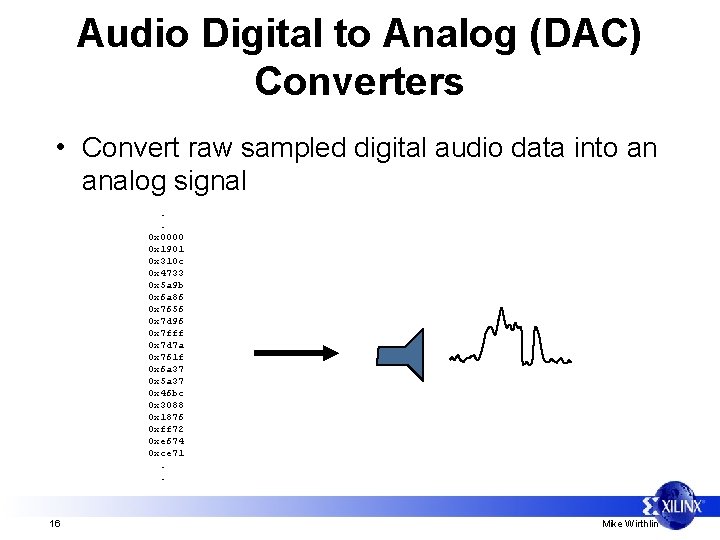

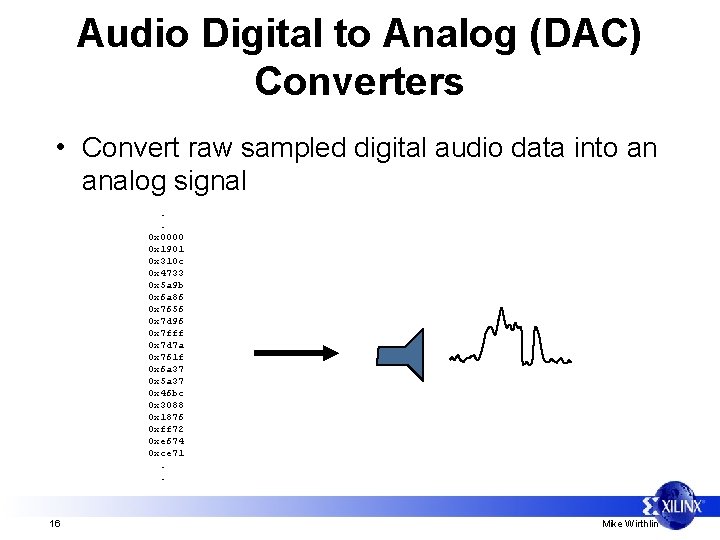

Audio Digital to Analog (DAC) Converters • Convert raw sampled digital audio data into an analog signal. . 0 x 0000 0 x 1901 0 x 310 c 0 x 4733 0 x 5 a 9 b 0 x 6 a 86 0 x 7656 0 x 7 d 96 0 x 7 fff 0 x 7 d 7 a 0 x 761 f 0 x 6 a 37 0 x 5 a 37 0 x 46 bc 0 x 3088 0 x 1876 0 xff 72 0 xe 674 0 xce 71. . 16 Mike Wirthlin

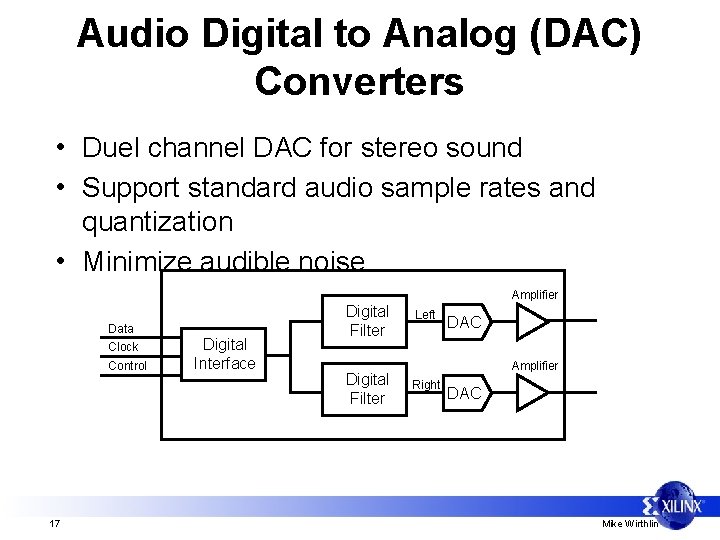

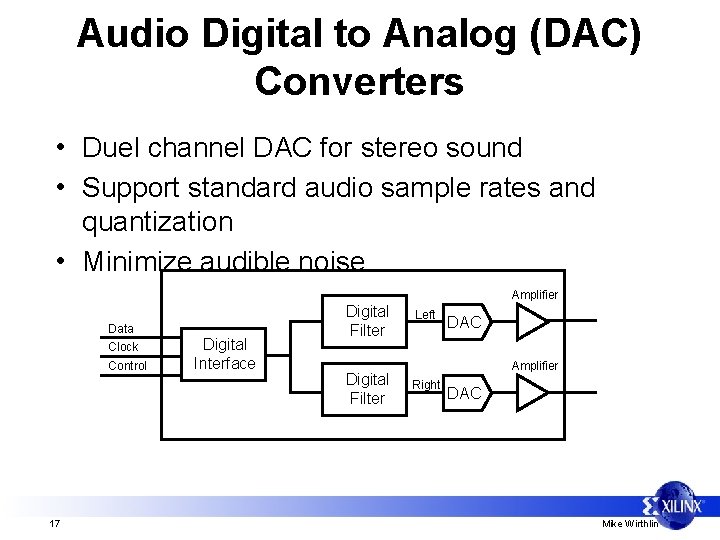

Audio Digital to Analog (DAC) Converters • Duel channel DAC for stereo sound • Support standard audio sample rates and quantization • Minimize audible noise Amplifier Data Clock Control 17 Digital Interface Digital Filter Left DAC Amplifier Right DAC Mike Wirthlin

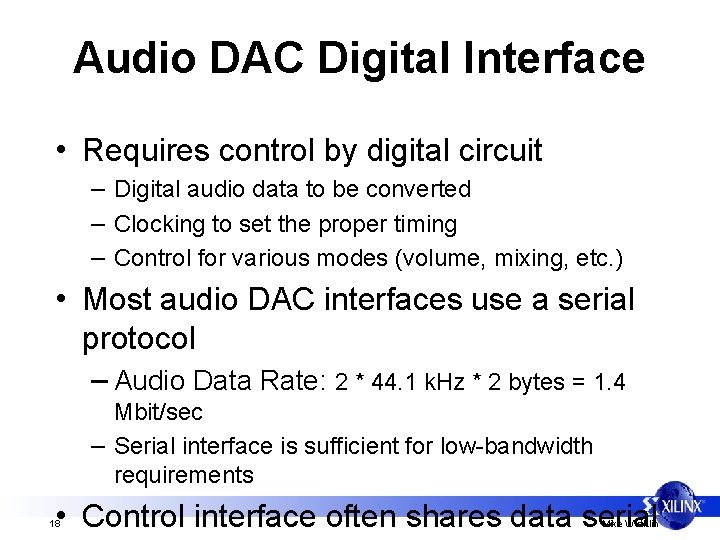

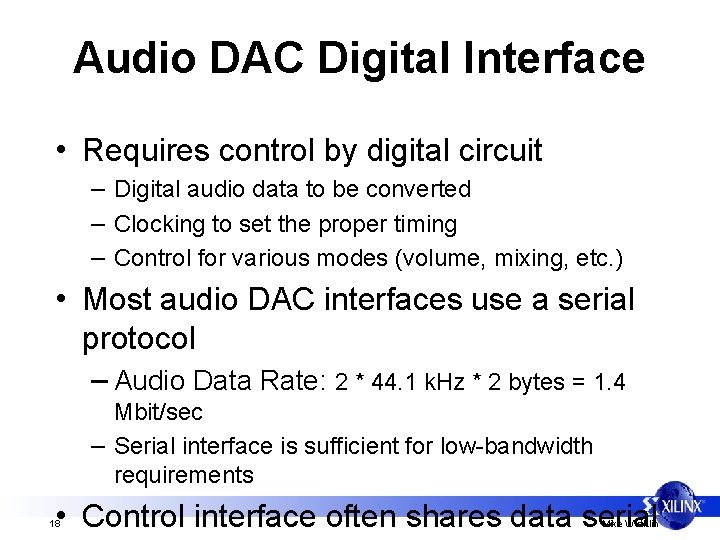

Audio DAC Digital Interface • Requires control by digital circuit – Digital audio data to be converted – Clocking to set the proper timing – Control for various modes (volume, mixing, etc. ) • Most audio DAC interfaces use a serial protocol – Audio Data Rate: 2 * 44. 1 k. Hz * 2 bytes = 1. 4 Mbit/sec – Serial interface is sufficient for low-bandwidth requirements • Control interface often shares data serial 18 Mike Wirthlin

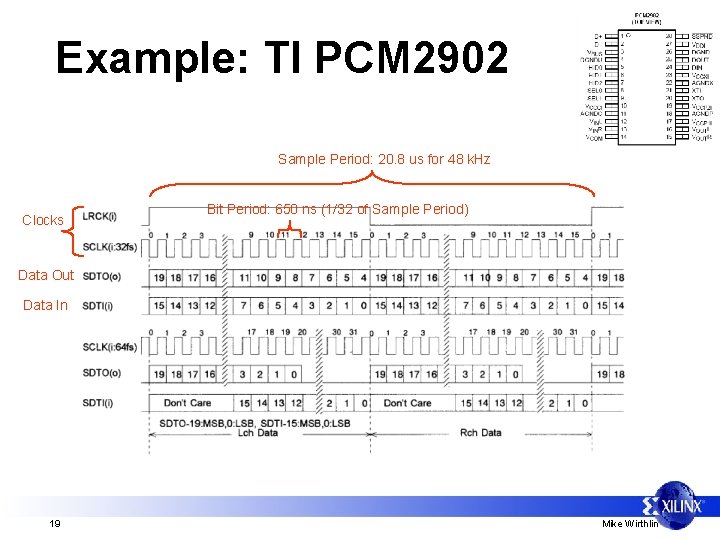

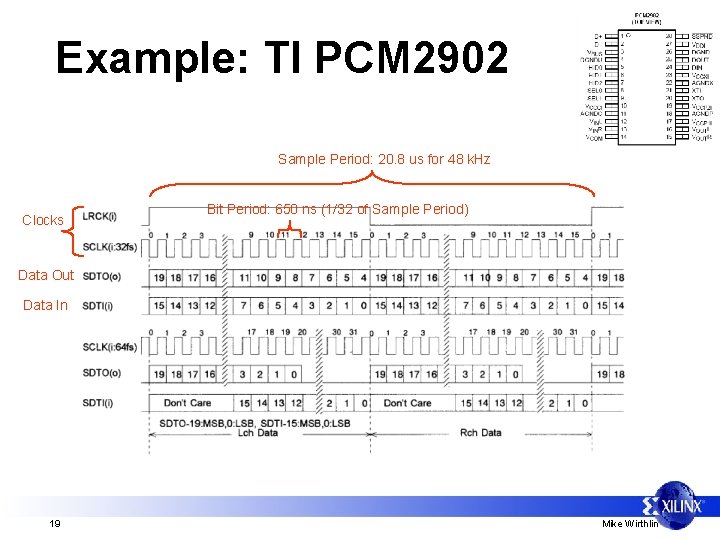

Example: TI PCM 2902 Sample Period: 20. 8 us for 48 k. Hz Clocks Bit Period: 650 ns (1/32 of Sample Period) Data Out Data In 19 Mike Wirthlin

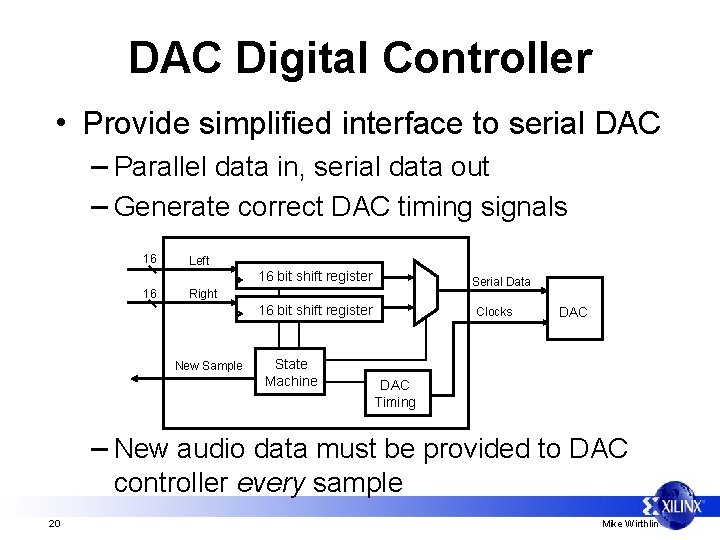

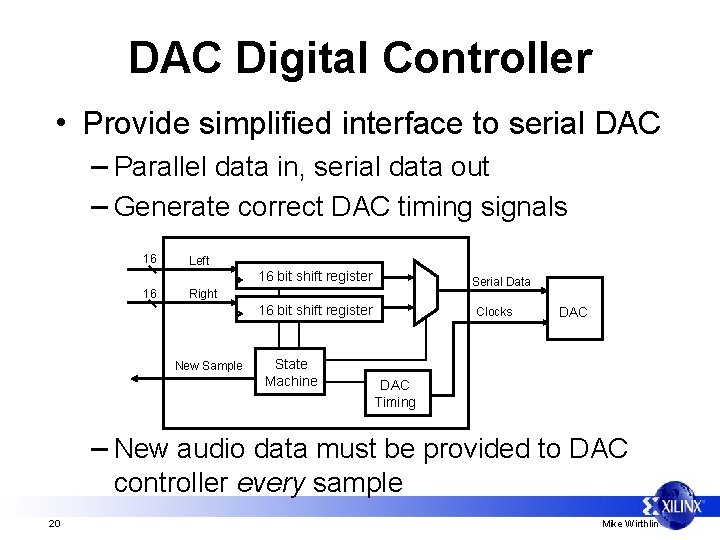

DAC Digital Controller • Provide simplified interface to serial DAC – Parallel data in, serial data out – Generate correct DAC timing signals 16 Left 16 bit shift register 16 Serial Data Right 16 bit shift register New Sample State Machine Clocks DAC Timing – New audio data must be provided to DAC controller every sample 20 Mike Wirthlin

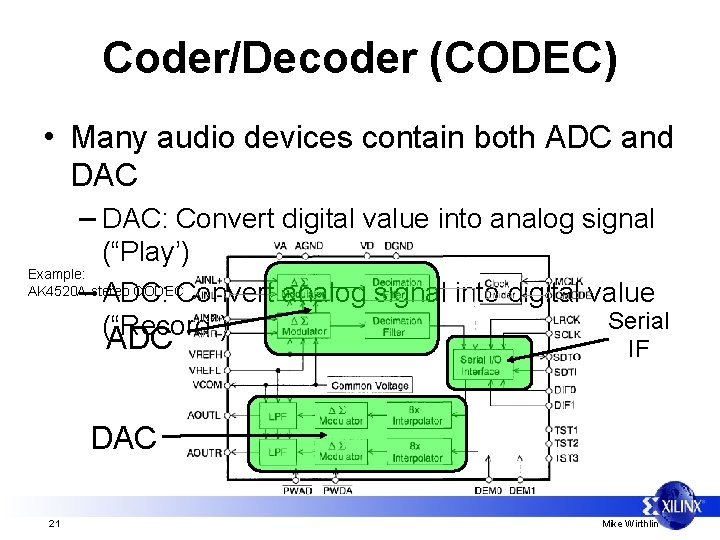

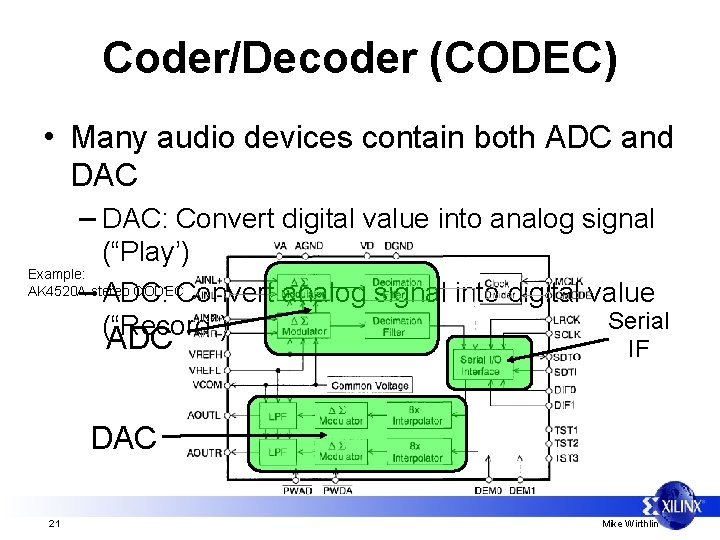

Coder/Decoder (CODEC) • Many audio devices contain both ADC and DAC – DAC: Convert digital value into analog signal (“Play’) Example: AK 4520 A CODEC –stereo ADC: Convert analog signal into digital value Serial (“Record”) ADC IF DAC 21 Mike Wirthlin

3. Interfacing Digital Audio 22 Mike Wirthlin

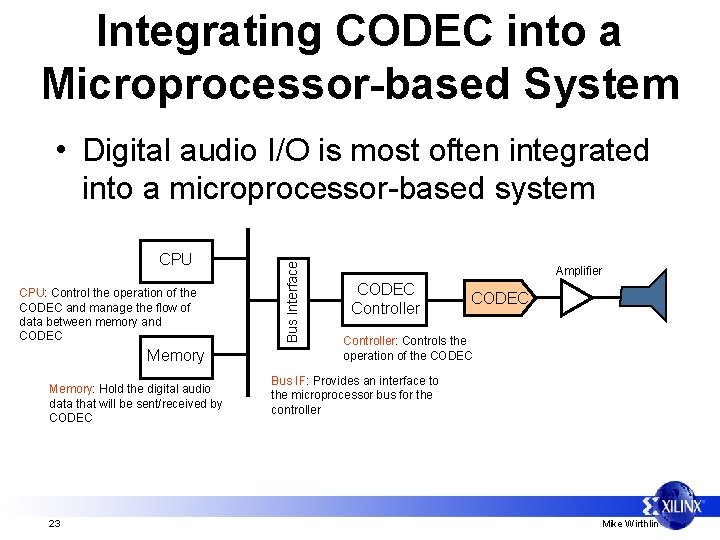

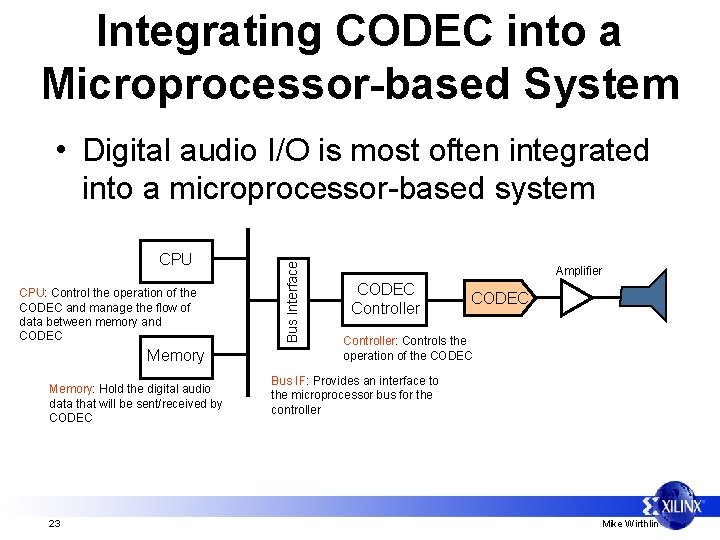

Integrating CODEC into a Microprocessor-based System • Digital audio I/O is most often integrated CPU: Control the operation of the CODEC and manage the flow of data between memory and CODEC Memory: Hold the digital audio data that will be sent/received by CODEC 23 Bus Interface into a microprocessor-based system Amplifier CODEC Controller: Controls the operation of the CODEC Bus IF: Provides an interface to the microprocessor bus for the controller Mike Wirthlin

Audio Data Transfer • Animation of data moving from memory to CPU, CPU to codec, CODEC to data out. 24 Mike Wirthlin

CPU Data Transfer • CPU must insure timely transfer of audio data – New sample is required every 20. 8 us (48 k. Hz) – CODEC will continue to operate with or without data – Failure to provide new data fast enough will result in skipping, stuttering, or other unpleasant sounds • Challenge: CPU may not respond to each 25 sample request Mike Wirthlin

Data Buffering • Picture of buffer. Explain sequence (fill buffer, wait until buffer is empty, refill). – Codec controller takes data every sample – CPU fills buffer in bursts • Issue buffer depth – Greater buffer reduces fill frequency requires more mem • Response time 26 Mike Wirthlin

Determining Buffer Fill • Polling – Determining when to send: interrupts or polling – Buffering scheme: • Latency of processor response (must fill before worst case delay) • Overhead of transfer • Sample software for doing polling & interrupts 27 Mike Wirthlin

External Audio Data • Discuss system in which audio data is not in memory – On disk – Over the network • Why you might not want to load entire song • Audio buffer from disk (you may not be able to access disk in time due to seek times) 28 Mike Wirthlin

DMA • DMA example 29 Mike Wirthlin

4. Audio Codec ‘ 97 (AC 97) 30 Mike Wirthlin

Audio Codec ‘ 97 (AC 97) • Specification for implementing digital audio in mainstream PCs • Includes support for most PC audio needs – Microphone recording – Stereo Line In/Stereo Line out – Headphone (auxiliary output) For AC 97 specification, see: http: //www. intel. com/labs/media/audio/ 31 Mike Wirthlin

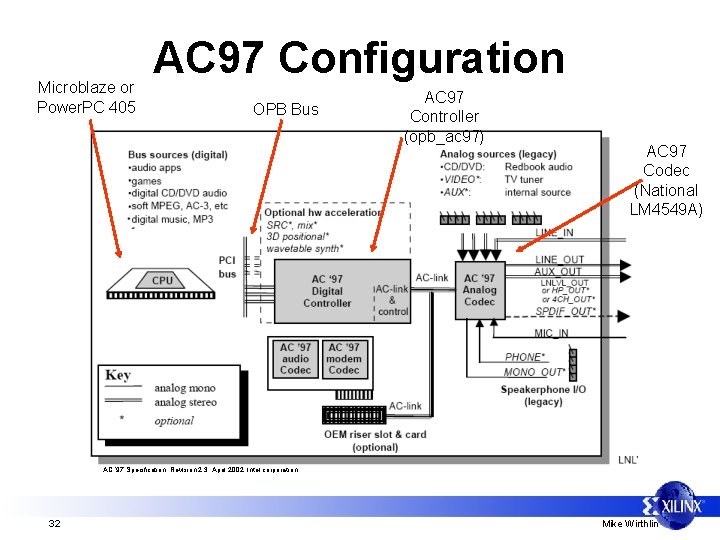

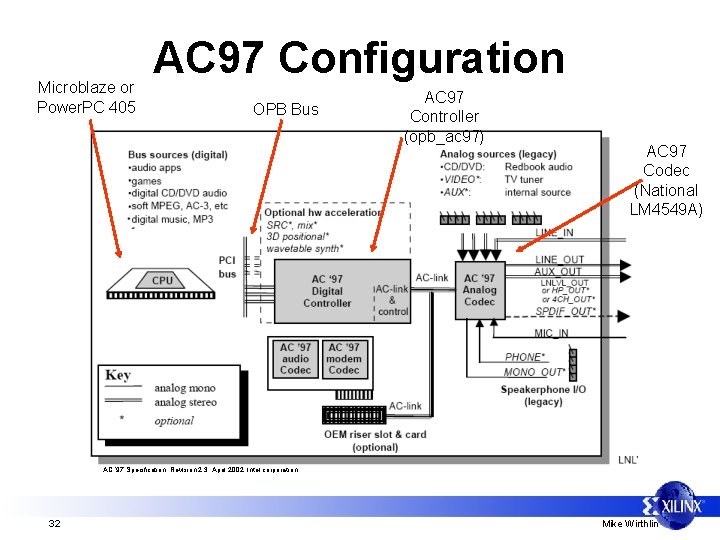

Microblaze or Power. PC 405 AC 97 Configuration OPB Bus AC 97 Controller (opb_ac 97) AC 97 Codec (National LM 4549 A) AC ‘ 97 Specification, Revision 2. 3, April 2002, Intel corporation 32 Mike Wirthlin

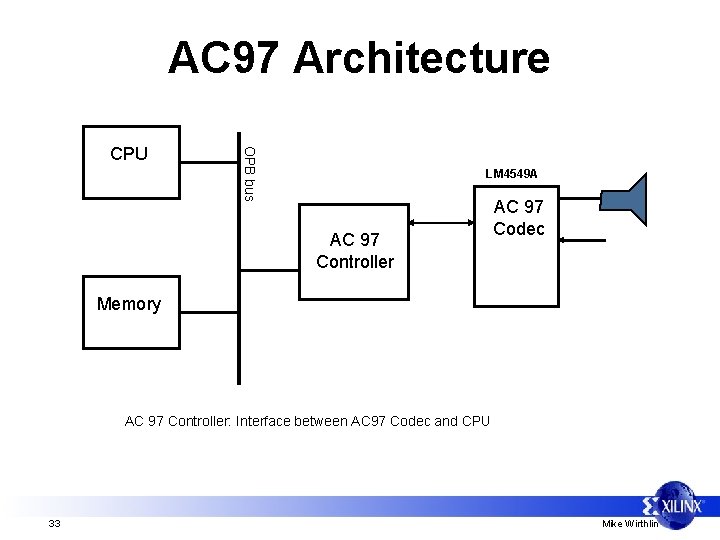

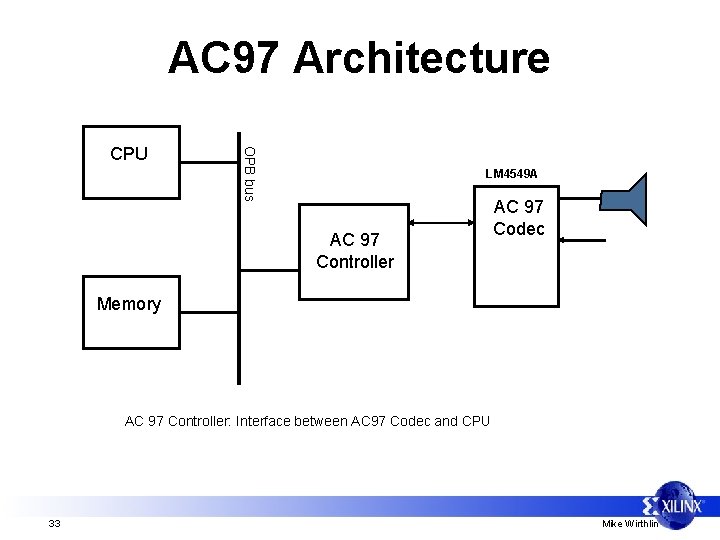

AC 97 Architecture OPB bus CPU LM 4549 A AC 97 Controller AC 97 Codec Memory AC 97 Controller: Interface between AC 97 Codec and CPU 33 Mike Wirthlin

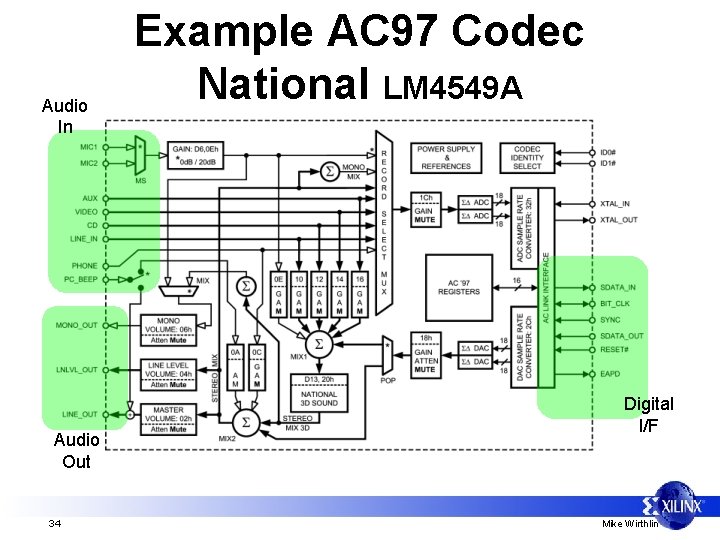

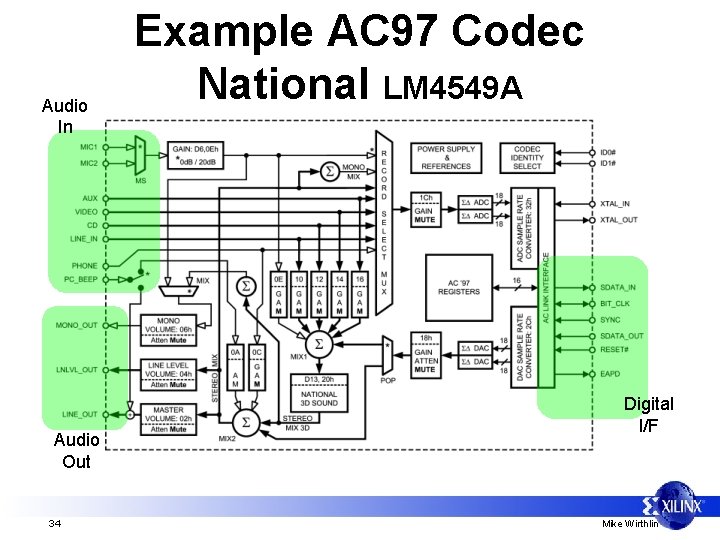

Audio In Audio Out 34 Example AC 97 Codec National LM 4549 A Digital I/F Mike Wirthlin

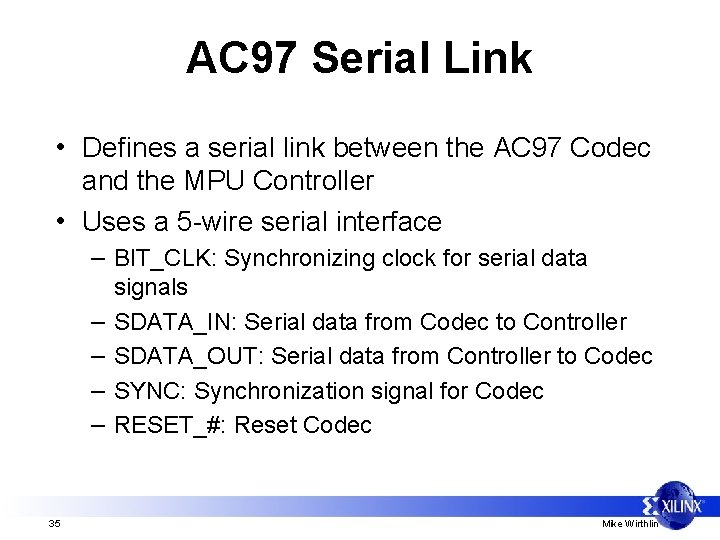

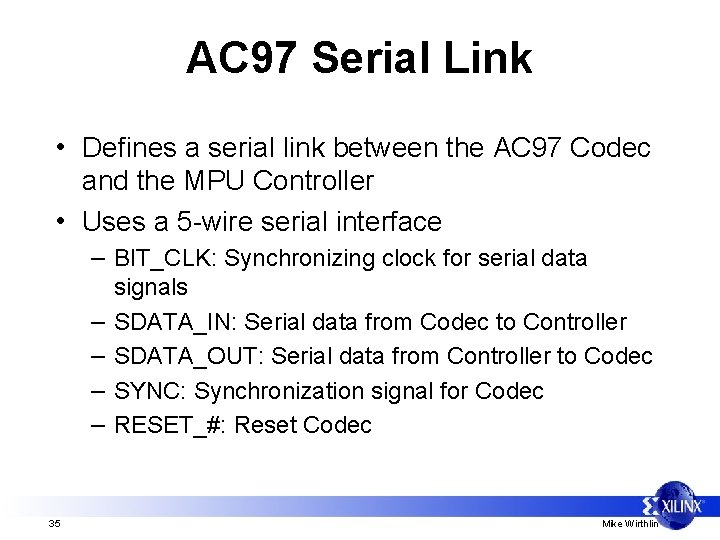

AC 97 Serial Link • Defines a serial link between the AC 97 Codec and the MPU Controller • Uses a 5 -wire serial interface – BIT_CLK: Synchronizing clock for serial data – – 35 signals SDATA_IN: Serial data from Codec to Controller SDATA_OUT: Serial data from Controller to Codec SYNC: Synchronization signal for Codec RESET_#: Reset Codec Mike Wirthlin

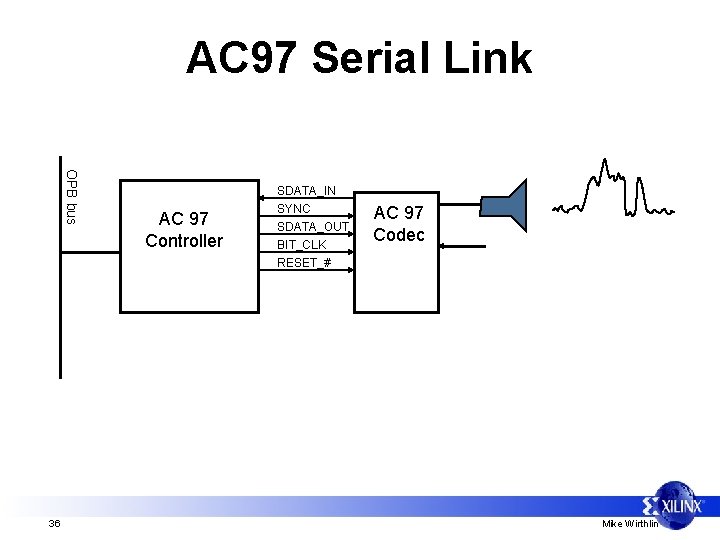

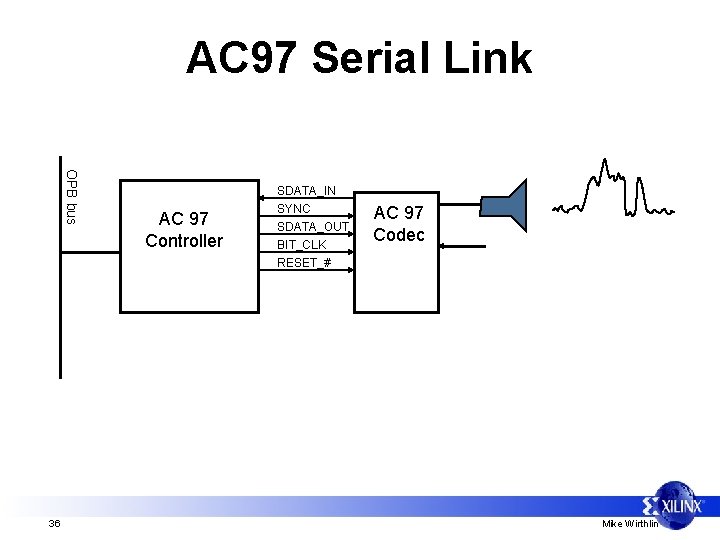

AC 97 Serial Link OPB bus 36 AC 97 Controller SDATA_IN SYNC SDATA_OUT BIT_CLK RESET_# AC 97 Codec Mike Wirthlin

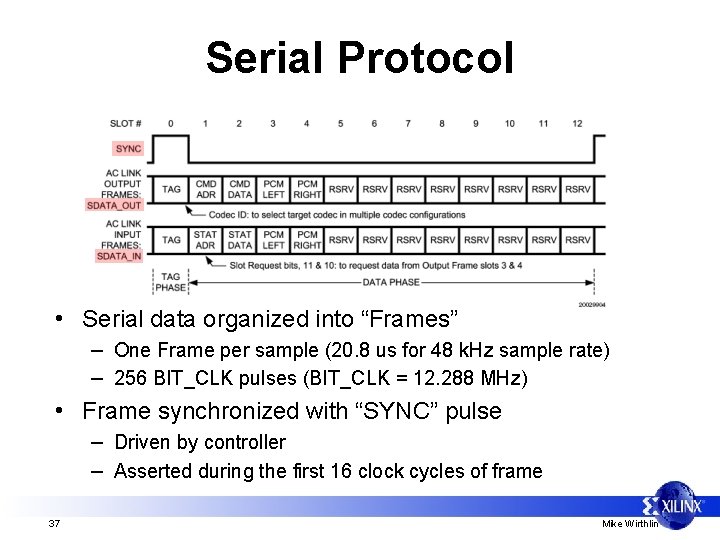

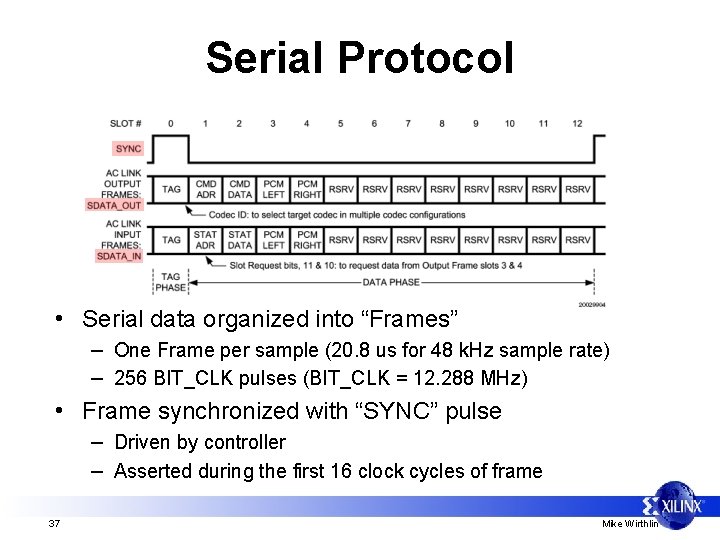

Serial Protocol • Serial data organized into “Frames” – One Frame per sample (20. 8 us for 48 k. Hz sample rate) – 256 BIT_CLK pulses (BIT_CLK = 12. 288 MHz) • Frame synchronized with “SYNC” pulse – Driven by controller – Asserted during the first 16 clock cycles of frame 37 Mike Wirthlin

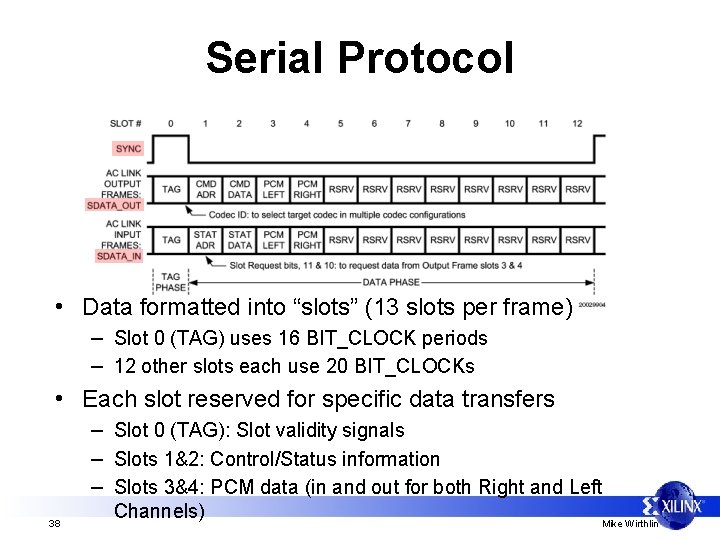

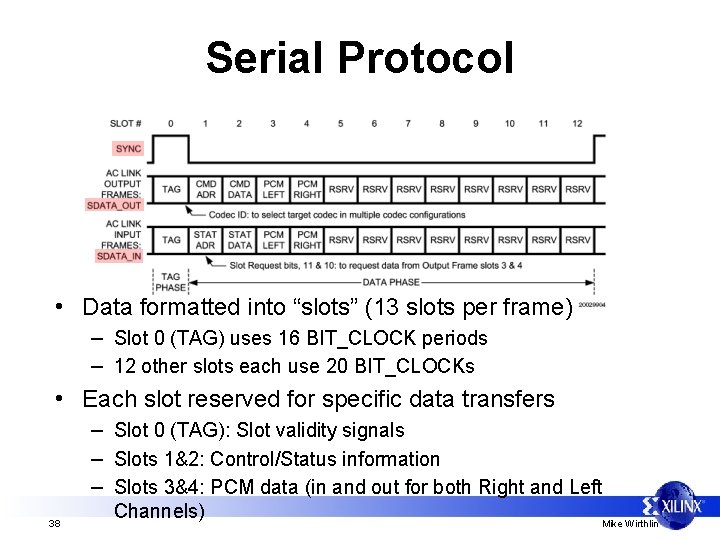

Serial Protocol • Data formatted into “slots” (13 slots per frame) – Slot 0 (TAG) uses 16 BIT_CLOCK periods – 12 other slots each use 20 BIT_CLOCKs • Each slot reserved for specific data transfers – Slot 0 (TAG): Slot validity signals – Slots 1&2: Control/Status information – Slots 3&4: PCM data (in and out for both Right and Left 38 Channels) Mike Wirthlin

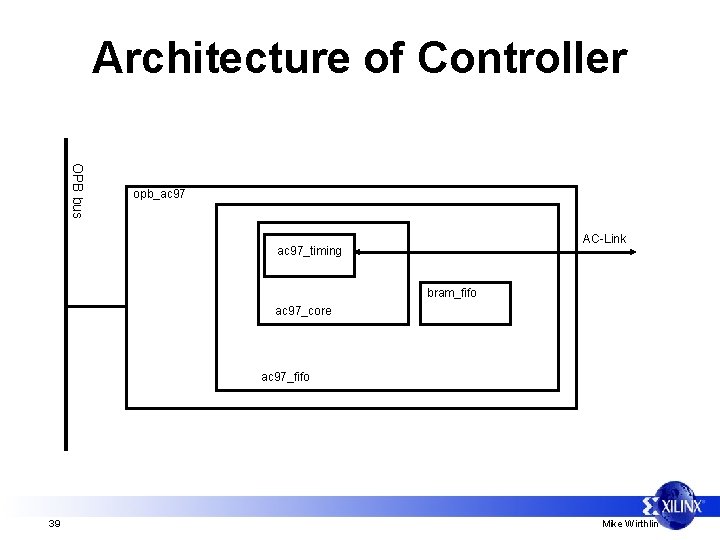

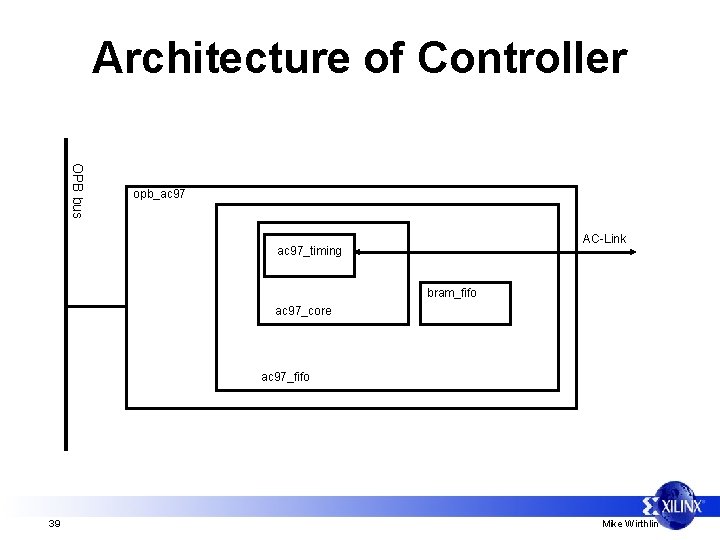

Architecture of Controller OPB bus opb_ac 97 AC-Link ac 97_timing bram_fifo ac 97_core ac 97_fifo 39 Mike Wirthlin

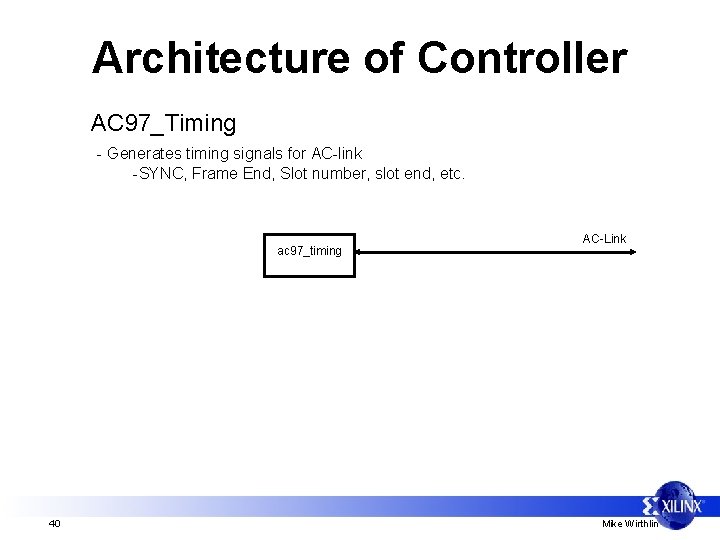

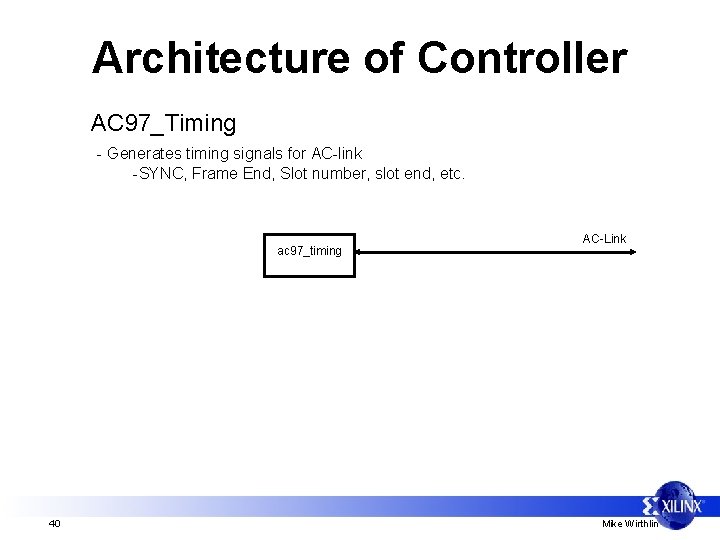

Architecture of Controller AC 97_Timing - Generates timing signals for AC-link -SYNC, Frame End, Slot number, slot end, etc. ac 97_timing 40 AC-Link Mike Wirthlin

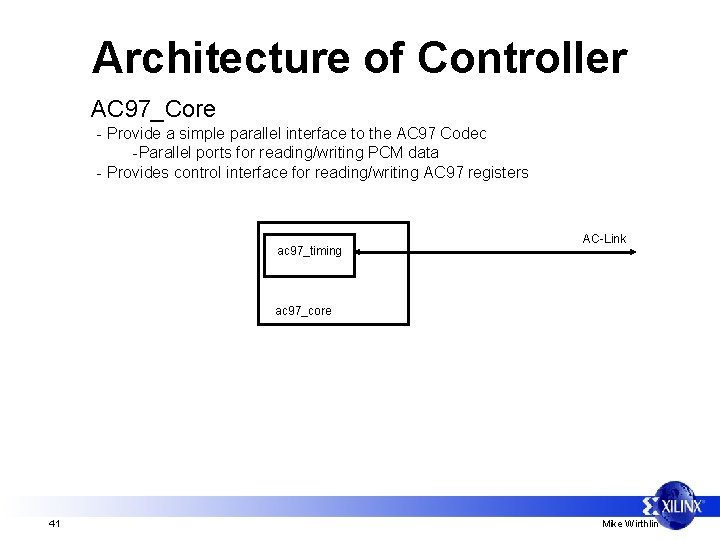

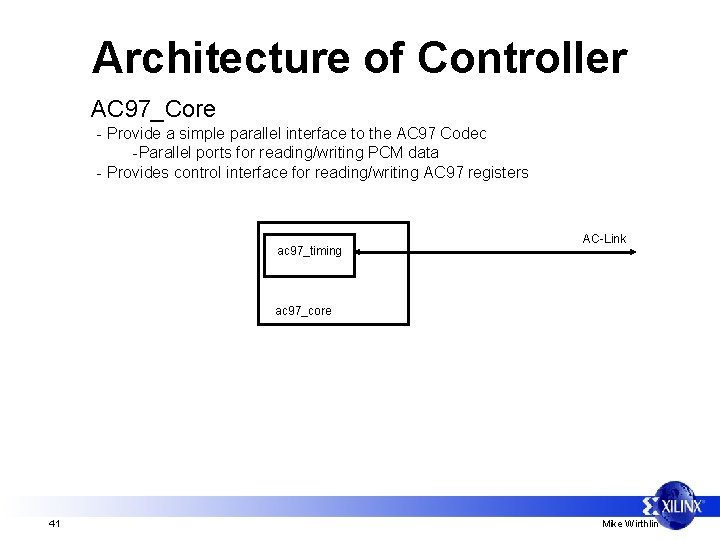

Architecture of Controller AC 97_Core - Provide a simple parallel interface to the AC 97 Codec -Parallel ports for reading/writing PCM data - Provides control interface for reading/writing AC 97 registers ac 97_timing AC-Link ac 97_core 41 Mike Wirthlin

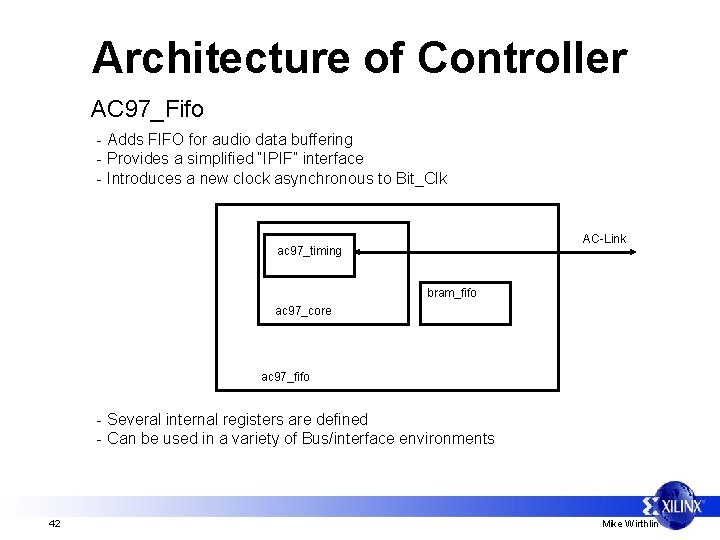

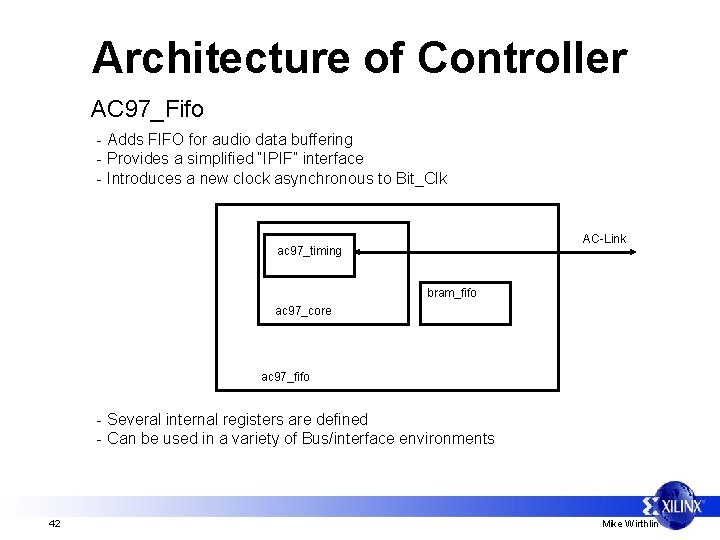

Architecture of Controller AC 97_Fifo - Adds FIFO for audio data buffering - Provides a simplified “IPIF” interface - Introduces a new clock asynchronous to Bit_Clk AC-Link ac 97_timing bram_fifo ac 97_core ac 97_fifo - Several internal registers are defined - Can be used in a variety of Bus/interface environments 42 Mike Wirthlin

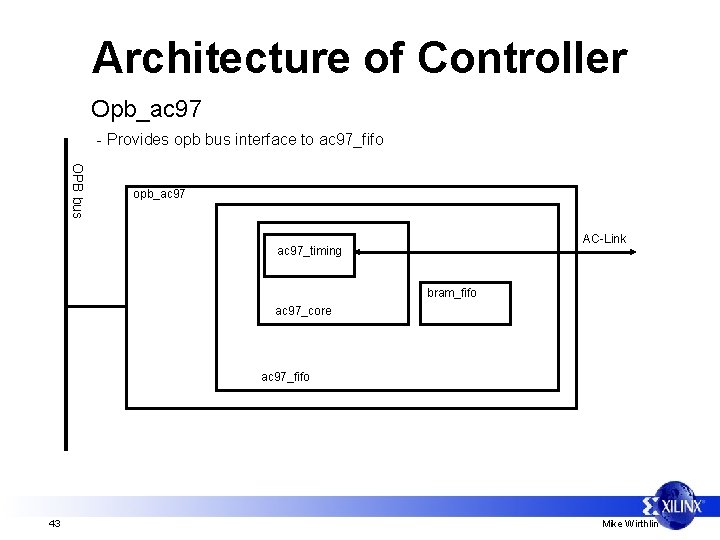

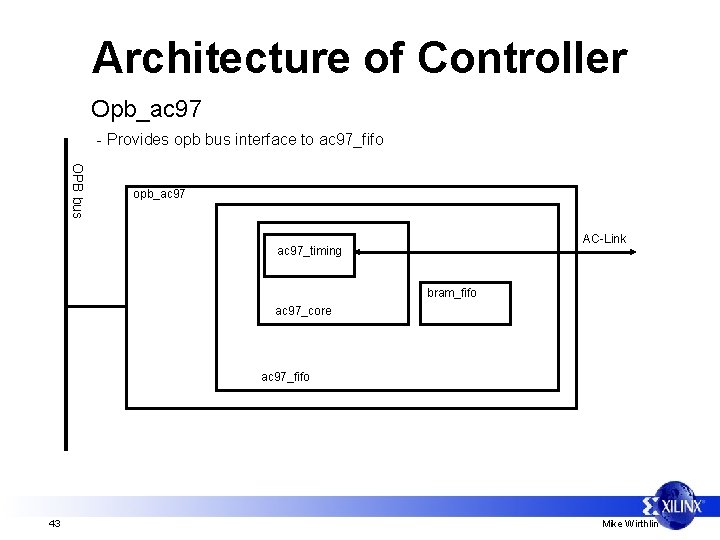

Architecture of Controller Opb_ac 97 - Provides opb bus interface to ac 97_fifo OPB bus opb_ac 97 AC-Link ac 97_timing bram_fifo ac 97_core ac 97_fifo 43 Mike Wirthlin

Sample System • Provide a sample system with Microblaze • AC 97 example • Provide code for interrupt routine and CODEC initialization 44 Mike Wirthlin

Audio Assignment Tasks • Create digital controller circuit – Provide digital data to your DAC board in the format it expects – Provide appropriate control of DAC board • Create circuit to play sinusoid tone – Interface to sinusoid table – Provide appropriate user interface (buttons/switches) – Send data to your digital controller circuit 45 Mike Wirthlin

Audio Assignment • Play a sinusoidal tone on both channels of analog output – I will provide the VHDL sinusoid table • Frequency of sinusoid determined by dip switches – SW 8 -SW 5 control left channel – SW 4 -SW 1 control right channel • Signal should be muted when buttons pressed – Mute left channel when Pushbutton 1 pressed (D 7) – Mute right channel when Pushbutton 2 pressed (A 6) • Due on Friday, February 20 (4 weeks from 46 Mike Wirthlin

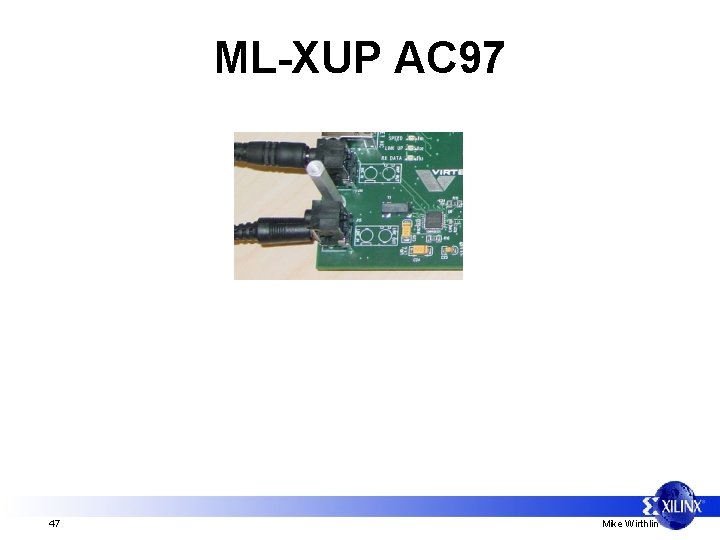

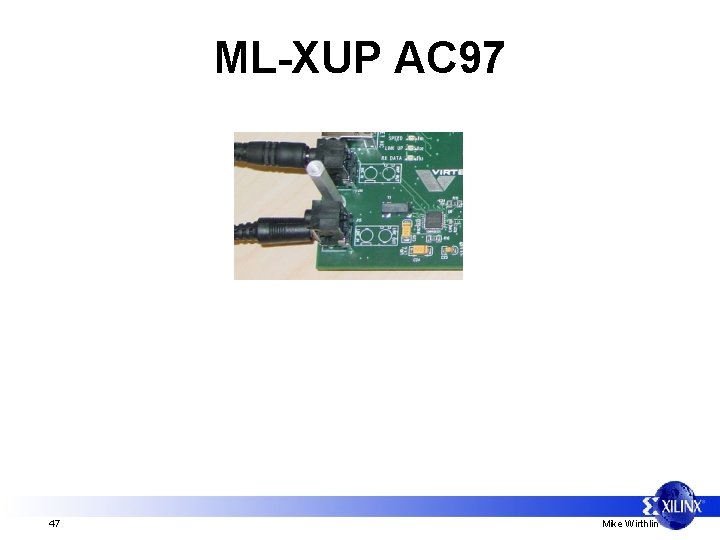

ML-XUP AC 97 47 Mike Wirthlin

Sample circuits/interfaces • Non-cpu interface? • Simple sin wave table • Memory interface (pre-loaded sound file) 48 Mike Wirthlin