Lecture 13 Models of Computation Embedded Computing Systems

Lecture 13: Models of Computation Embedded Computing Systems Mikko Lipasti, adapted from M. Schulte Based on slides and textbook from Wayne Wolf High Performance Embedded Computing © 2007 Elsevier

Topics n n Overview of programming languages Interrupt oriented languages Data flow languages Control-oriented languages © 2006 Elsevier

Programming languages n Embedded computing uses many models of computation: q q q n n Signal processing. Control/protocols. Algorithmic. Different languages have specialized uses, require different compilation methods. Models of computations must interact properly. © 2006 Elsevier

Reactive systems and synchronous languages n Reactive systems react to inputs, generate outputs. q n Synchronous languages were designed to model reactive systems. q q n e. g. , a digital control system Assume inputs and associated outputs happen simultaneously an instantly Allow a program to be written as several interacting modules. Synchronous languages are deterministic. © 2006 Elsevier

Rules of synchronous languages n n n A change in the state of one module is simultaneous with receipt of inputs. Outputs from a module are simultaneous with changes in state. Communication between modules is synchronous and instantaneous. Output behavior of the modules is determined by the interleaving of input signals. NOTE: implementation relaxes these ideal assumptions which are useful for reasoning about correctness © 2006 Elsevier

Interrupt-oriented languages n Interrupts are important sources of asynchronous behavior and timing constraints. q n Interrupt handlers are difficult to debug. q q n May facilitate I/O anc inter-processor communication Perform parallel operations between the device and the CPU using low-level techniques Layered approach for modeling devices is slow. Interrupt-oriented languages compile efficient implementations of drivers. © 2006 Elsevier

Video driver language n n Thibault et al. developed a language for X Windows video device drivers. Abstract machine defines operations, data transfers, control operations. Language can be used to describe details of the video adapter, program the interface. Allows video drivers to be specified using much fewer lines of code than C q 9 times fewer for a particular 35, 000 line video driver © 2006 Elsevier

Conway and Edwards NDL n n The Network Device Language (NDL) is a specialized language for device drivers State of I/O device is declared as part of the NDL (Network Device Language) program. q n n Memory-mapped I/O locations are defined using ioport construct (like a struct in C) NDL program declares device’s states, which includes actions to occur when in those states. NDL compiler generates device drivers in C after performing several optimizations. © 2006 Elsevier

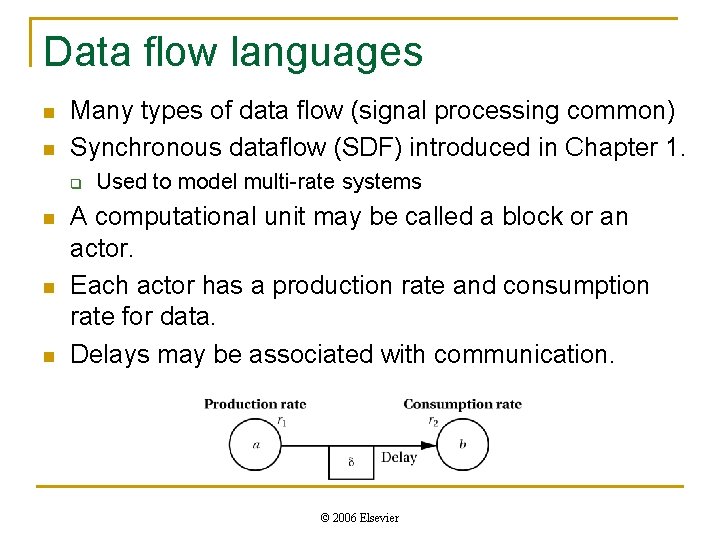

Data flow languages n n Many types of data flow (signal processing common) Synchronous dataflow (SDF) introduced in Chapter 1. q n n n Used to model multi-rate systems A computational unit may be called a block or an actor. Each actor has a production rate and consumption rate for data. Delays may be associated with communication. © 2006 Elsevier

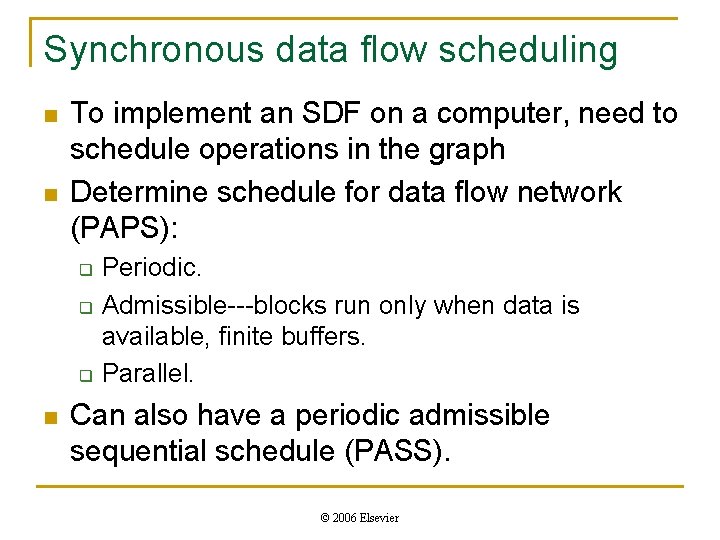

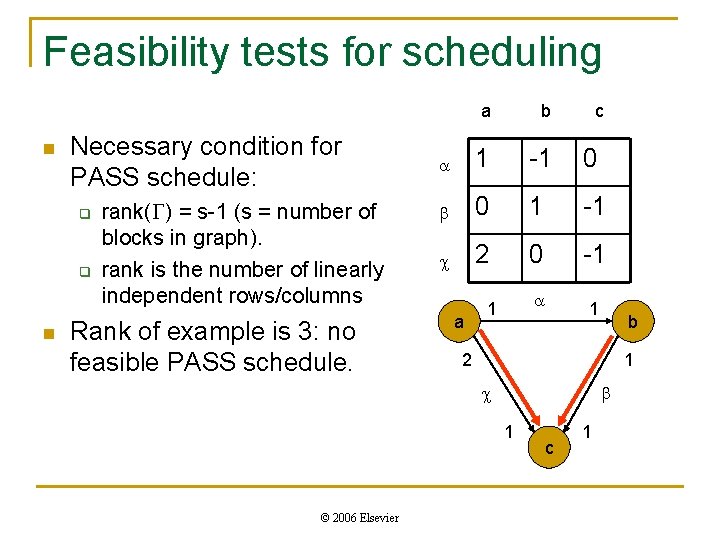

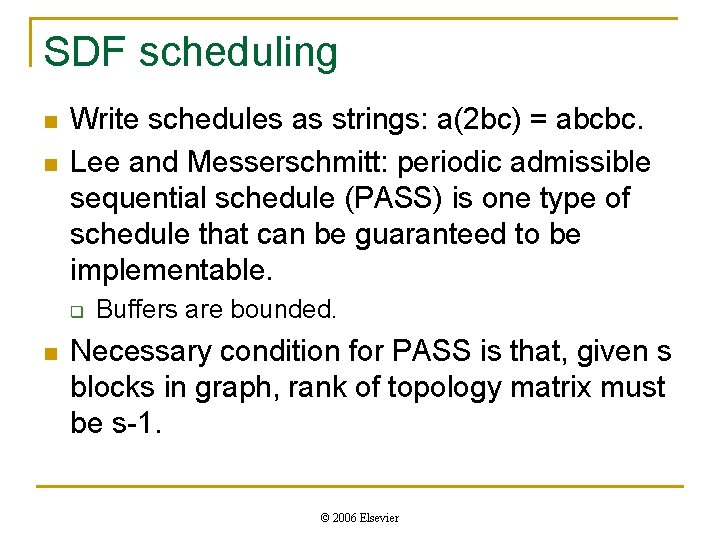

Synchronous data flow scheduling n n To implement an SDF on a computer, need to schedule operations in the graph Determine schedule for data flow network (PAPS): q q q n Periodic. Admissible---blocks run only when data is available, finite buffers. Parallel. Can also have a periodic admissible sequential schedule (PASS). © 2006 Elsevier

Periodic Sequential Schedule a b c time © 2006 Elsevier

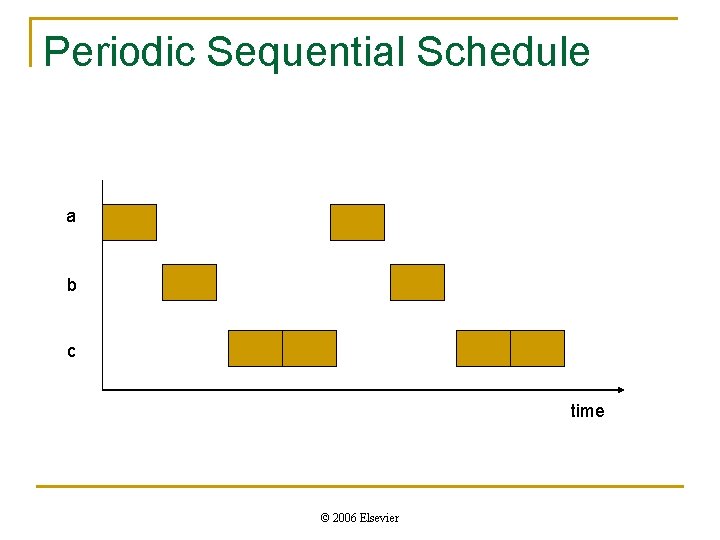

Describing the SDF network n Topology matrix (G) describes an SDF network q q q Rows are edges. Columns are nodes. Matrix entries correspond to data rates (data flow into a node is negative) a a 1 1 2 1 c b 1 c a b a 1 -1 0 b 0 1 -1 c 2 0 -1 b 1 © 2006 Elsevier c

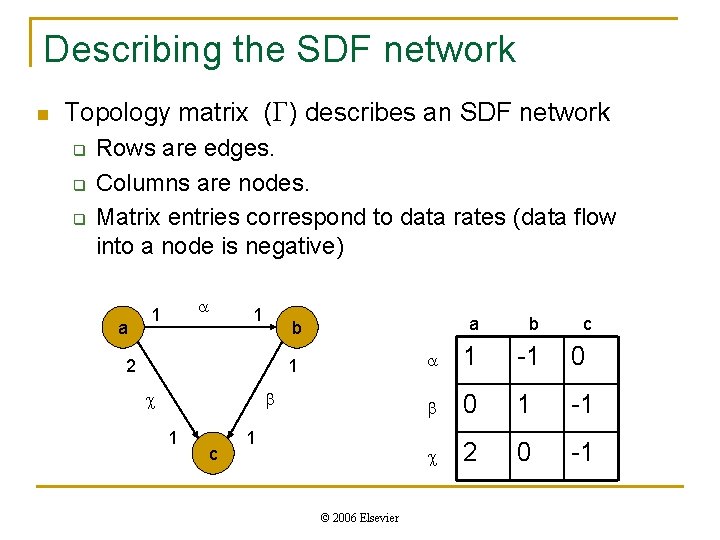

Feasibility tests for scheduling n Necessary condition for PASS schedule: q q n rank(G) = s-1 (s = number of blocks in graph). rank is the number of linearly independent rows/columns Rank of example is 3: no feasible PASS schedule. a b a 1 -1 0 b 0 1 -1 c 2 0 -1 a a 1 c 1 2 1 c b 1 © 2006 Elsevier b c 1

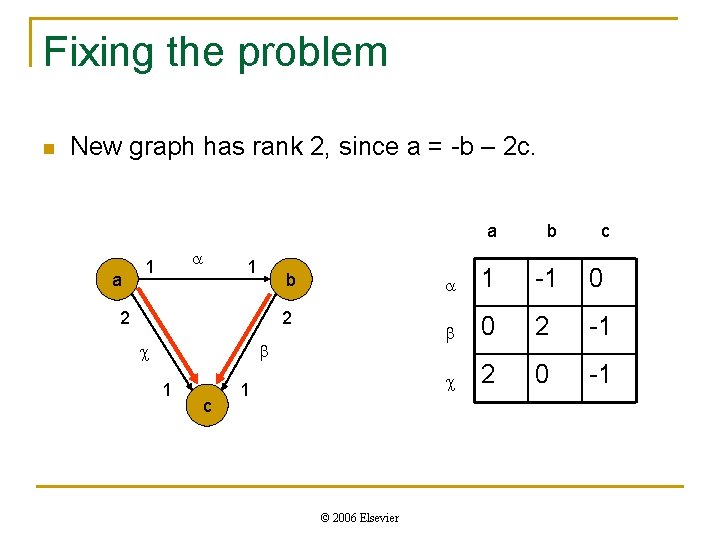

Fixing the problem n New graph has rank 2, since a = -b – 2 c. a a 1 1 b 2 2 c b 1 c 1 © 2006 Elsevier a b c a 1 -1 0 b 0 2 -1 c 2 0 -1

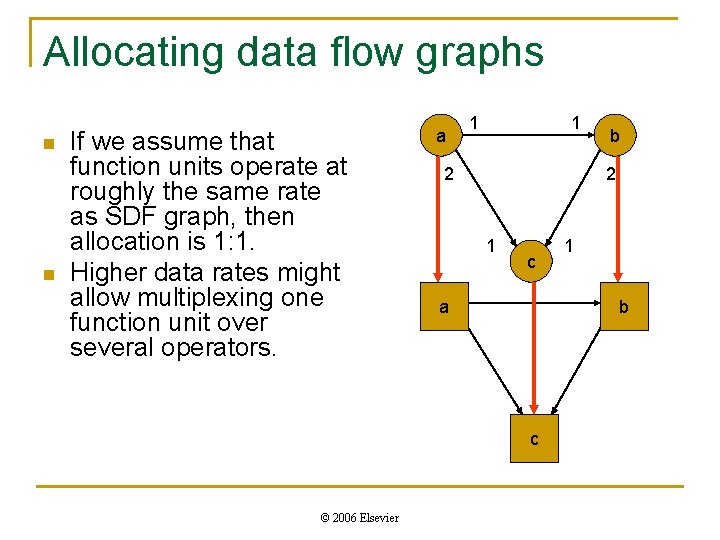

Allocating data flow graphs n n If we assume that function units operate at roughly the same rate as SDF graph, then allocation is 1: 1. Higher data rates might allow multiplexing one function unit over several operators. a 1 1 2 2 1 c a 1 b c © 2006 Elsevier b

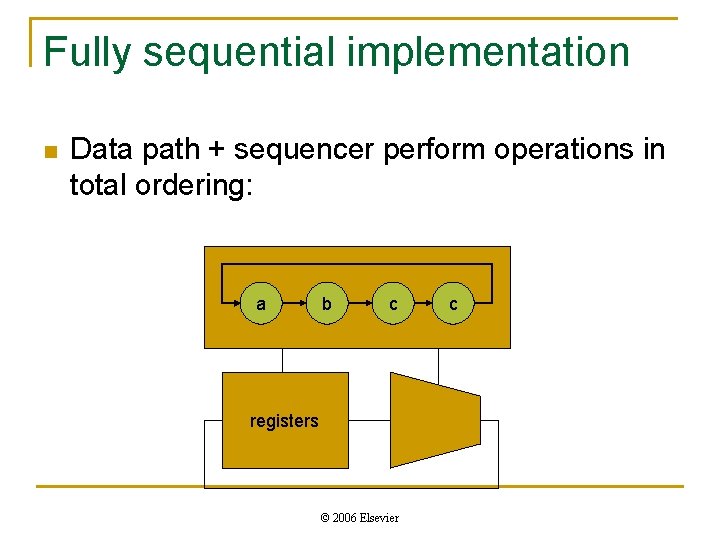

Fully sequential implementation n Data path + sequencer perform operations in total ordering: a b c registers © 2006 Elsevier c

SDF scheduling n n Write schedules as strings: a(2 bc) = abcbc. Lee and Messerschmitt: periodic admissible sequential schedule (PASS) is one type of schedule that can be guaranteed to be implementable. q n Buffers are bounded. Necessary condition for PASS is that, given s blocks in graph, rank of topology matrix must be s-1. © 2006 Elsevier

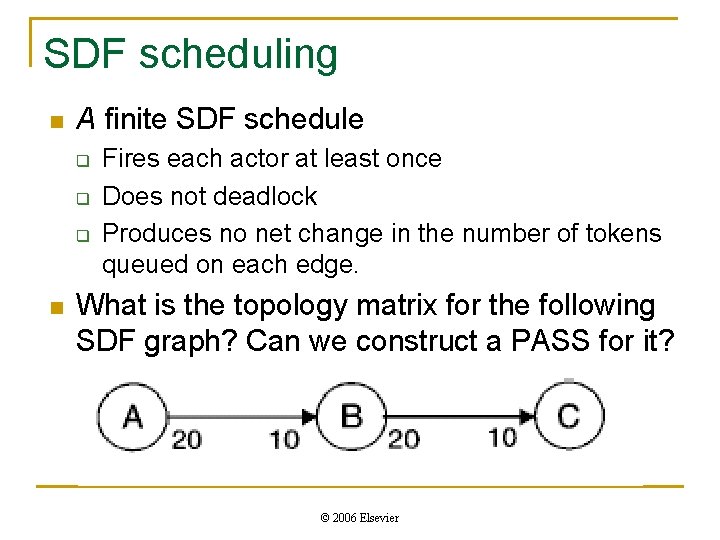

SDF scheduling n A finite SDF schedule q q q n Fires each actor at least once Does not deadlock Produces no net change in the number of tokens queued on each edge. What is the topology matrix for the following SDF graph? Can we construct a PASS for it? © 2006 Elsevier

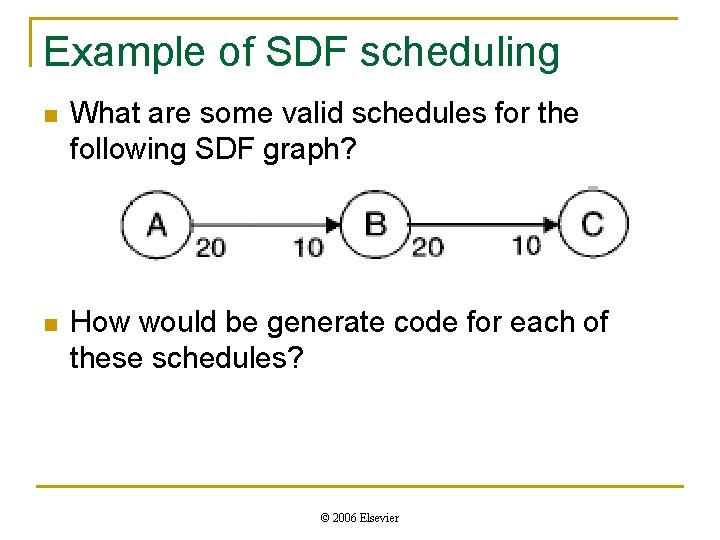

Example of SDF scheduling n What are some valid schedules for the following SDF graph? n How would be generate code for each of these schedules? © 2006 Elsevier

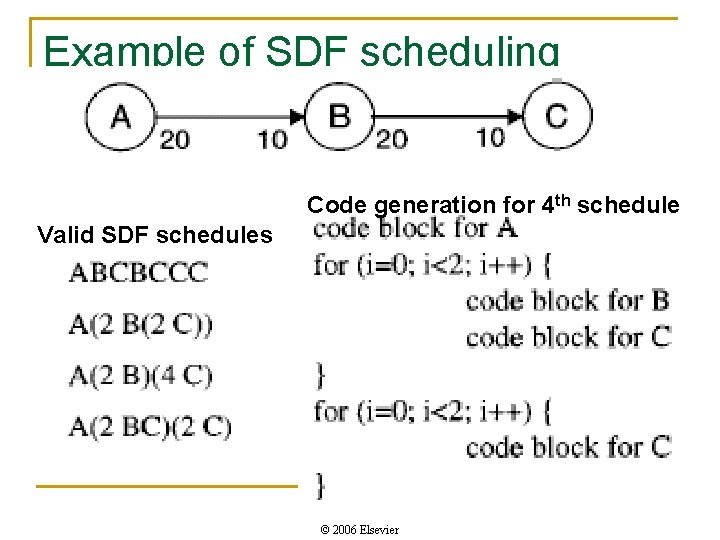

Example of SDF scheduling Code generation for 4 th schedule Valid SDF schedules © 2006 Elsevier

![Buffer overlay analysis [Bha 94 b] © 1994 IEEE © 2006 Elsevier Buffer overlay analysis [Bha 94 b] © 1994 IEEE © 2006 Elsevier](http://slidetodoc.com/presentation_image_h2/205fb41db30b3148a549d9f68b8720ee/image-21.jpg)

Buffer overlay analysis [Bha 94 b] © 1994 IEEE © 2006 Elsevier

Examples of SDF languages n n LUSTRE SIGNAL Esterel See book for details, examples, references © 2006 Elsevier

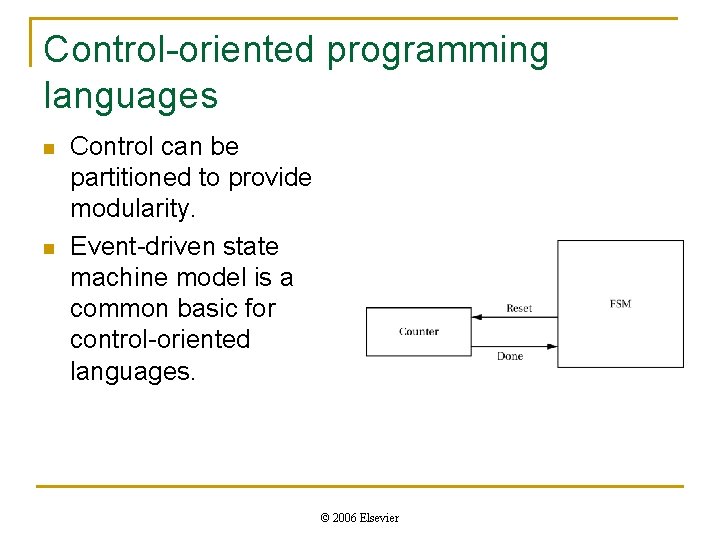

Control-oriented programming languages n n Control can be partitioned to provide modularity. Event-driven state machine model is a common basic for control-oriented languages. © 2006 Elsevier

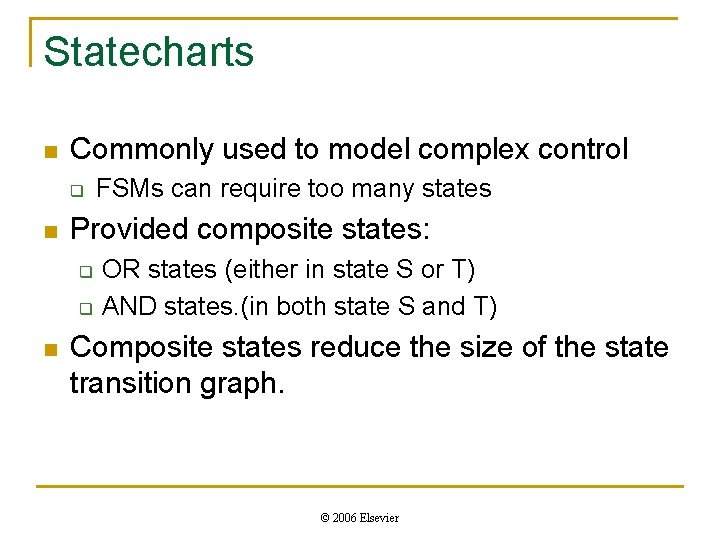

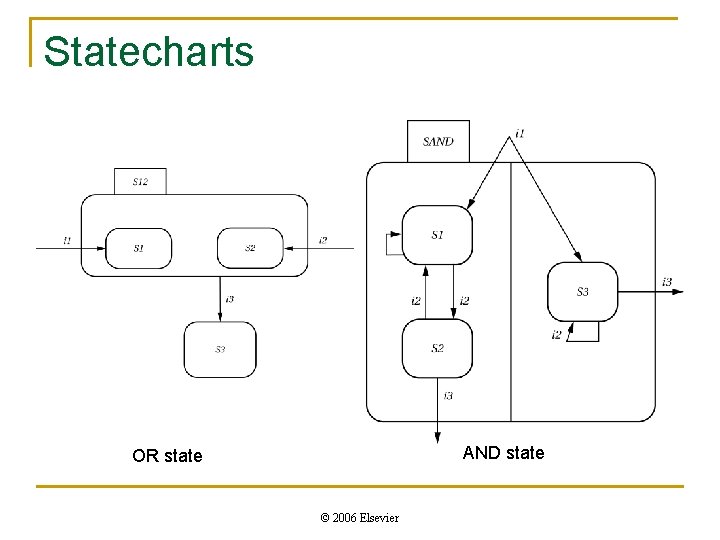

Statecharts n Commonly used to model complex control q n Provided composite states: q q n FSMs can require too many states OR states (either in state S or T) AND states. (in both state S and T) Composite states reduce the size of the state transition graph. © 2006 Elsevier

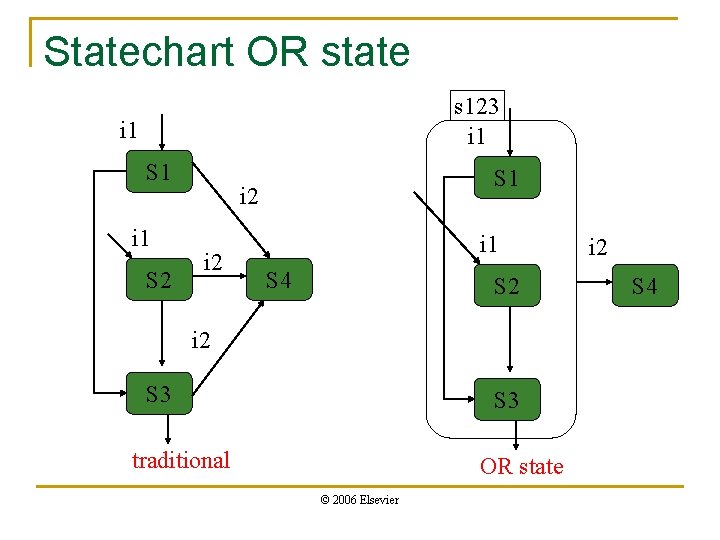

Statechart OR state s 123 i 1 S 1 i 1 S 2 S 1 i 2 i 1 S 4 S 2 i 2 S 3 traditional OR state © 2006 Elsevier i 2 S 4

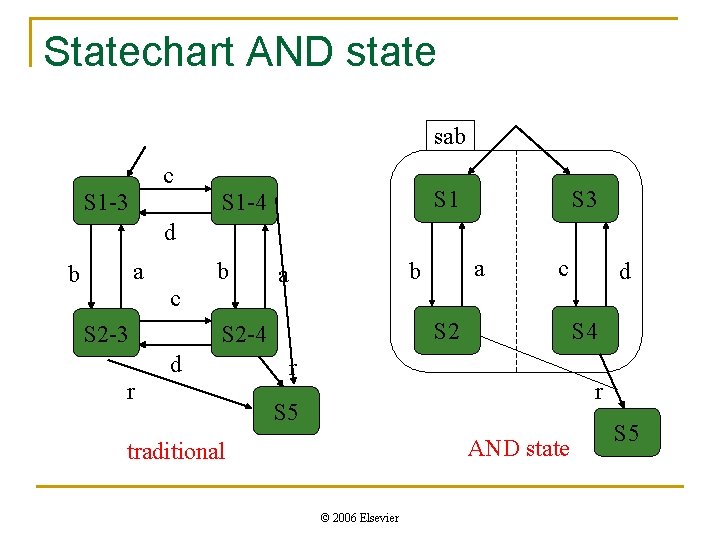

Statechart AND state sab c S 1 -3 S 1 -4 S 3 d a b b c S 2 -3 r c S 2 -4 d a b a d S 4 r r S 5 AND state traditional © 2006 Elsevier S 5

Statecharts AND state OR state © 2006 Elsevier

![Esterel example © 2006 Elsevier [Bou 91] © 1991 IEEE Esterel example © 2006 Elsevier [Bou 91] © 1991 IEEE](http://slidetodoc.com/presentation_image_h2/205fb41db30b3148a549d9f68b8720ee/image-28.jpg)

Esterel example © 2006 Elsevier [Bou 91] © 1991 IEEE

Summary n n n Interrupt oriented languages Data flow languages Control-oriented languages © 2006 Elsevier

- Slides: 29