King Fahd University of Petroleum and Minerals College

- Slides: 37

King Fahd University of Petroleum and Minerals College of Computer Science And Engineering Computer Engineering Department COE 308 Building the Datapath COE 308 Datapath Design 1

King Fahd University of Petroleum and Minerals College of Computer Science And Engineering Computer Engineering Department Definitions • The processor executes instructions that operate on data. • Data is modified, moved, produced and discarded as a result of the program’s target • The Datapath is the hardware circuitry of the processor where the Data is: – Temporarily stored – Modified • By opposition, the Control Unit is responsible for controlling and monitoring the Datapath to ensure the proper execution of the instructions COE 308 Datapath Design 2

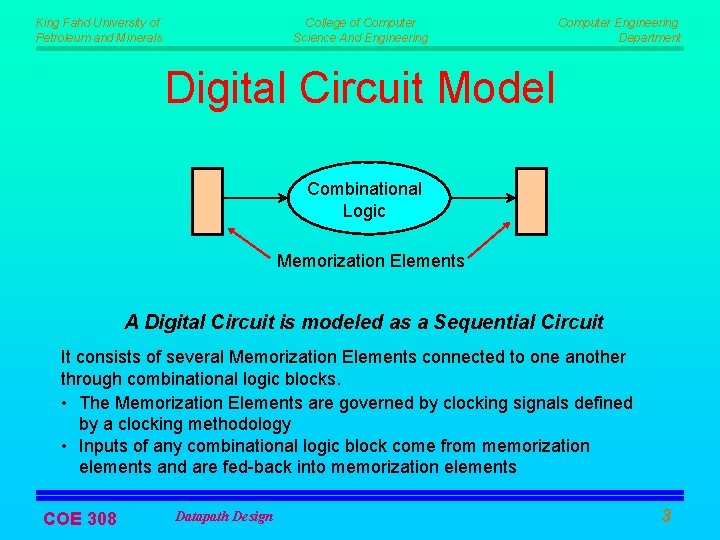

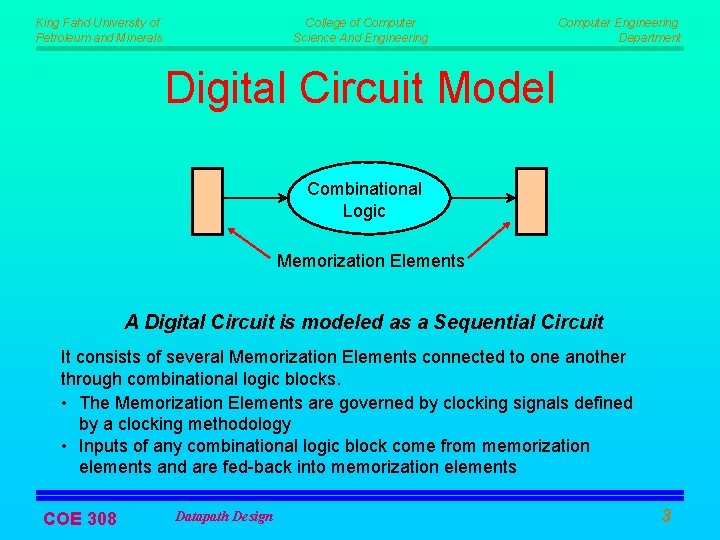

King Fahd University of Petroleum and Minerals College of Computer Science And Engineering Computer Engineering Department Digital Circuit Model Combinational Logic Memorization Elements A Digital Circuit is modeled as a Sequential Circuit It consists of several Memorization Elements connected to one another through combinational logic blocks. • The Memorization Elements are governed by clocking signals defined by a clocking methodology • Inputs of any combinational logic block come from memorization elements and are fed-back into memorization elements COE 308 Datapath Design 3

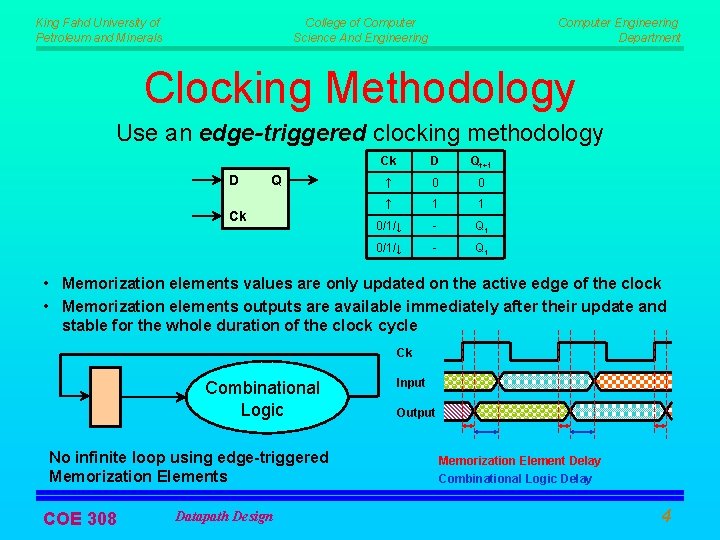

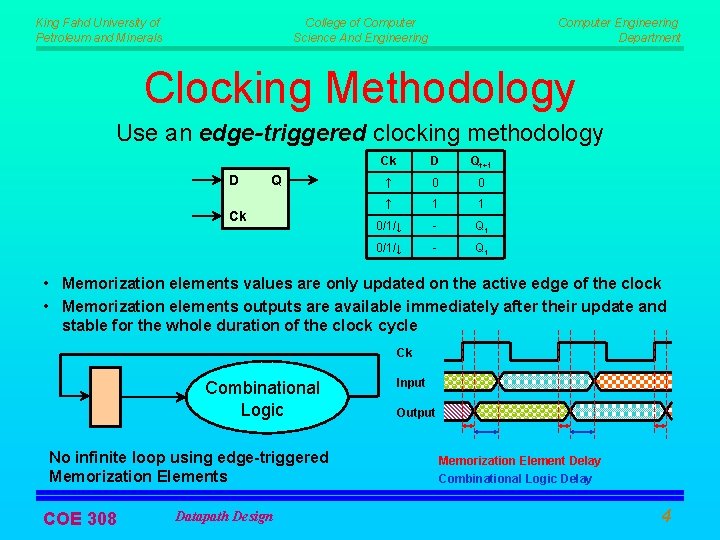

King Fahd University of Petroleum and Minerals College of Computer Science And Engineering Computer Engineering Department Clocking Methodology Use an edge-triggered clocking methodology D Q Ck Ck D Qt+1 ↑ 0 0 ↑ 1 1 0/1/↓ - Qt • Memorization elements values are only updated on the active edge of the clock • Memorization elements outputs are available immediately after their update and stable for the whole duration of the clock cycle Ck Combinational Logic No infinite loop using edge-triggered Memorization Elements COE 308 Datapath Design Input Output Memorization Element Delay Combinational Logic Delay 4

King Fahd University of Petroleum and Minerals College of Computer Science And Engineering Computer Engineering Department General Design Methodology • Clearly understand the list of requirements • Translate the requirements list into design-oriented requirements that can be directly mapped into design blocks • Divide the design into several design blocks organized by function that implement the list of requirements • Clearly define the inputs and outputs of each block (interface) • Connect the blocks together to form the design entity as a whole • Refine the details by verifying that each item in the requirement list is fully fulfilled. Add the necessary modifications if needed. COE 308 Datapath Design 5

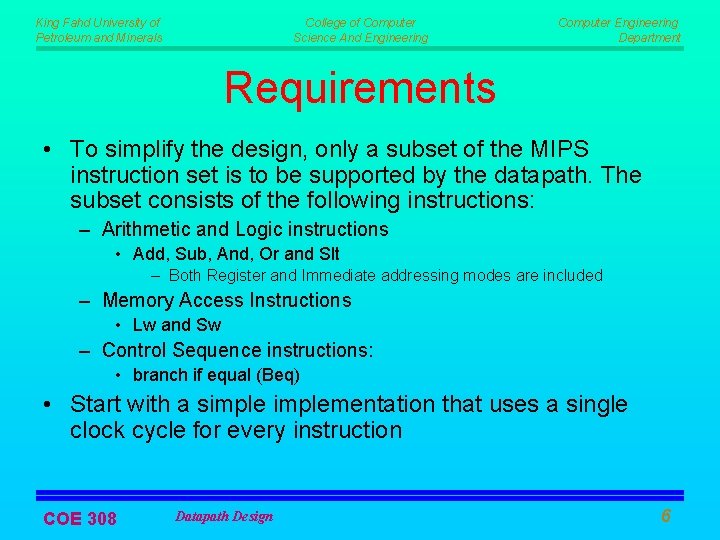

King Fahd University of Petroleum and Minerals College of Computer Science And Engineering Computer Engineering Department Requirements • To simplify the design, only a subset of the MIPS instruction set is to be supported by the datapath. The subset consists of the following instructions: – Arithmetic and Logic instructions • Add, Sub, And, Or and Slt – Both Register and Immediate addressing modes are included – Memory Access Instructions • Lw and Sw – Control Sequence instructions: • branch if equal (Beq) • Start with a simplementation that uses a single clock cycle for every instruction COE 308 Datapath Design 6

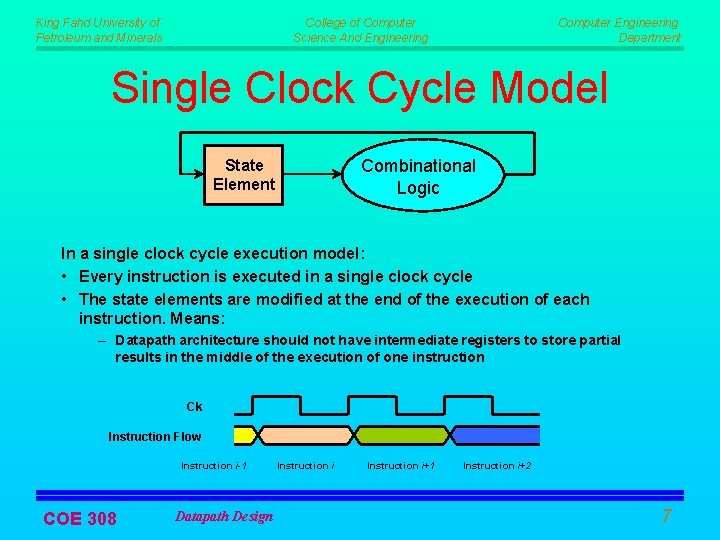

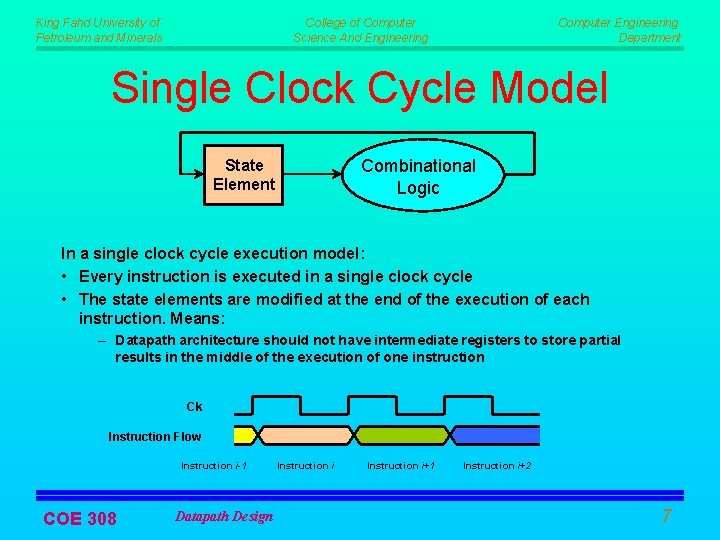

King Fahd University of Petroleum and Minerals College of Computer Science And Engineering Computer Engineering Department Single Clock Cycle Model Combinational Logic State Element In a single clock cycle execution model: • Every instruction is executed in a single clock cycle • The state elements are modified at the end of the execution of each instruction. Means: – Datapath architecture should not have intermediate registers to store partial results in the middle of the execution of one instruction Ck Instruction Flow Instruction i-1 COE 308 Datapath Design Instruction i+1 Instruction i+2 7

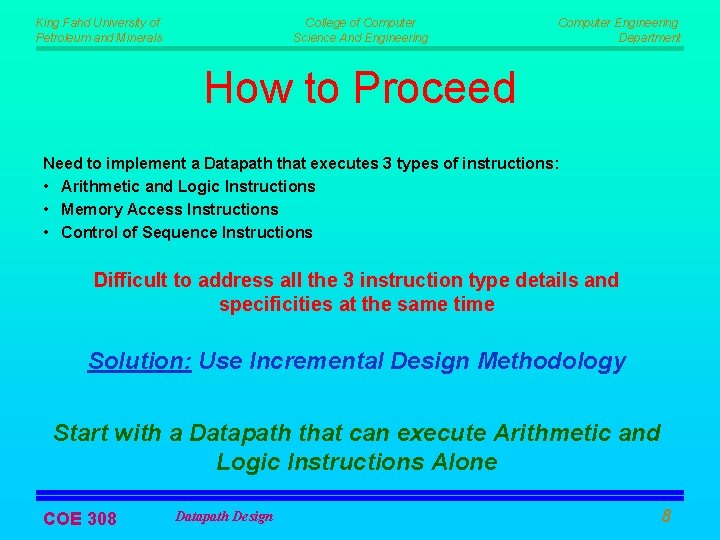

King Fahd University of Petroleum and Minerals College of Computer Science And Engineering Computer Engineering Department How to Proceed Need to implement a Datapath that executes 3 types of instructions: • Arithmetic and Logic Instructions • Memory Access Instructions • Control of Sequence Instructions Difficult to address all the 3 instruction type details and specificities at the same time Solution: Use Incremental Design Methodology Start with a Datapath that can execute Arithmetic and Logic Instructions Alone COE 308 Datapath Design 8

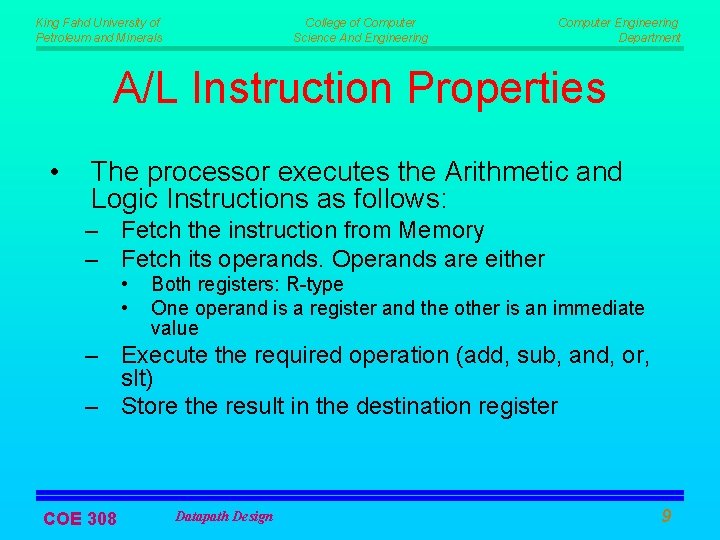

King Fahd University of Petroleum and Minerals College of Computer Science And Engineering Computer Engineering Department A/L Instruction Properties • The processor executes the Arithmetic and Logic Instructions as follows: – Fetch the instruction from Memory – Fetch its operands. Operands are either • • Both registers: R-type One operand is a register and the other is an immediate value – Execute the required operation (add, sub, and, or, slt) – Store the result in the destination register COE 308 Datapath Design 9

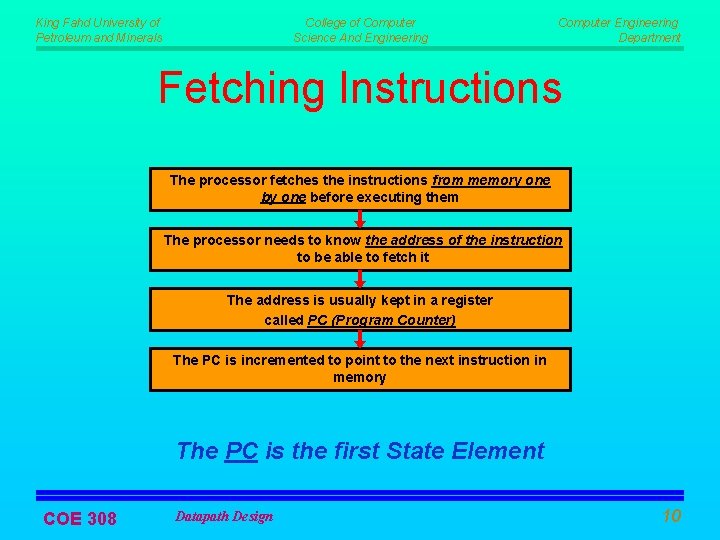

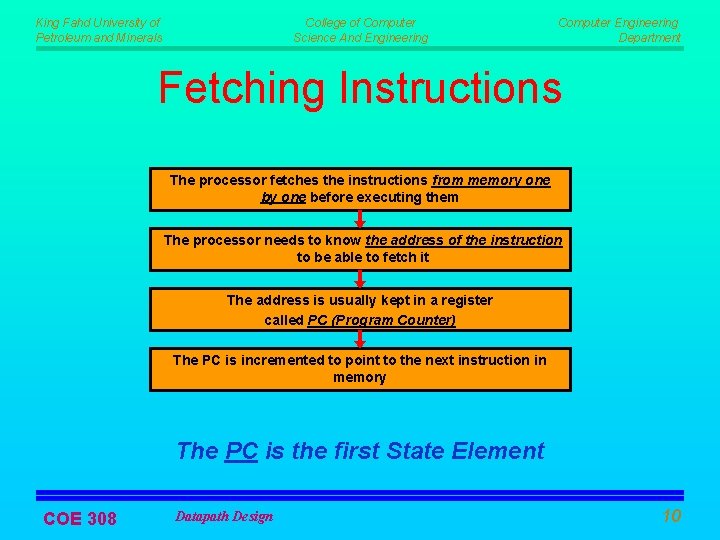

King Fahd University of Petroleum and Minerals College of Computer Science And Engineering Computer Engineering Department Fetching Instructions The processor fetches the instructions from memory one before executing them The processor needs to know the address of the instruction to be able to fetch it The address is usually kept in a register called PC (Program Counter) The PC is incremented to point to the next instruction in memory The PC is the first State Element COE 308 Datapath Design 10

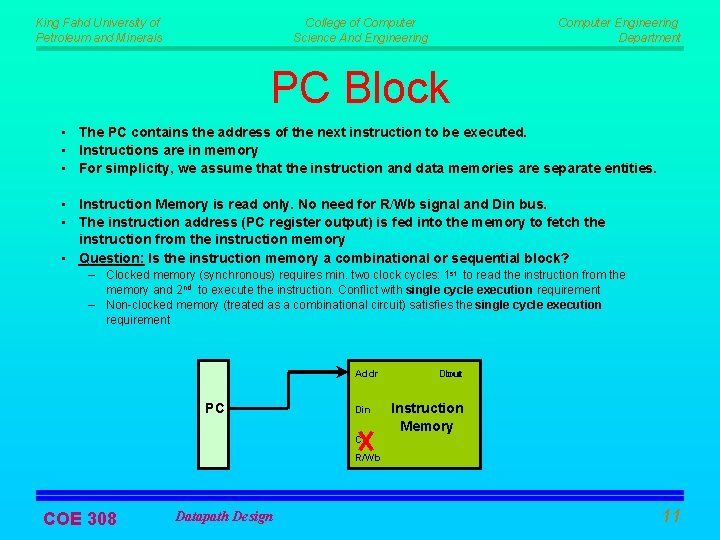

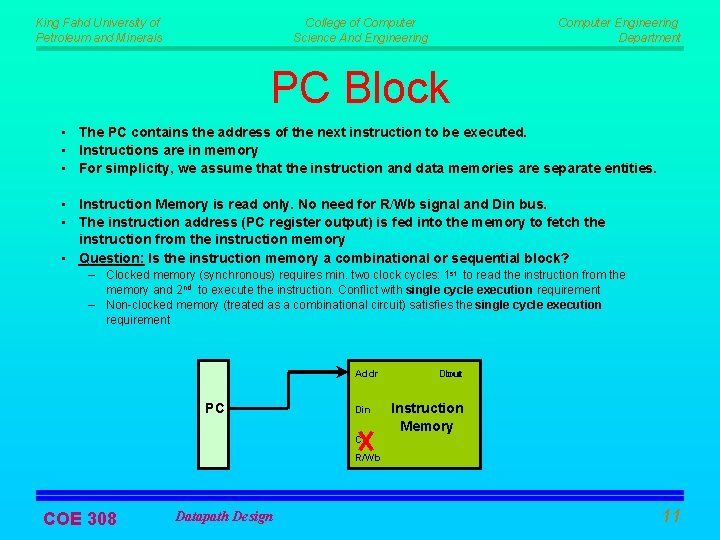

King Fahd University of Petroleum and Minerals College of Computer Science And Engineering Computer Engineering Department PC Block • The PC contains the address of the next instruction to be executed. • Instructions are in memory • For simplicity, we assume that the instruction and data memories are separate entities. • Instruction Memory is read only. No need for R/Wb signal and Din bus. • The instruction address (PC register output) is fed into the memory to fetch the instruction from the instruction memory • Question: Is the instruction memory a combinational or sequential block? – Clocked memory (synchronous) requires min. two clock cycles: 1 st to read the instruction from the memory and 2 nd to execute the instruction. Conflict with single cycle execution requirement – Non-clocked memory (treated as a combinational circuit) satisfies the single cycle execution requirement Addr PC Din Ck Dout Instruction Memory R/Wb COE 308 Datapath Design 11

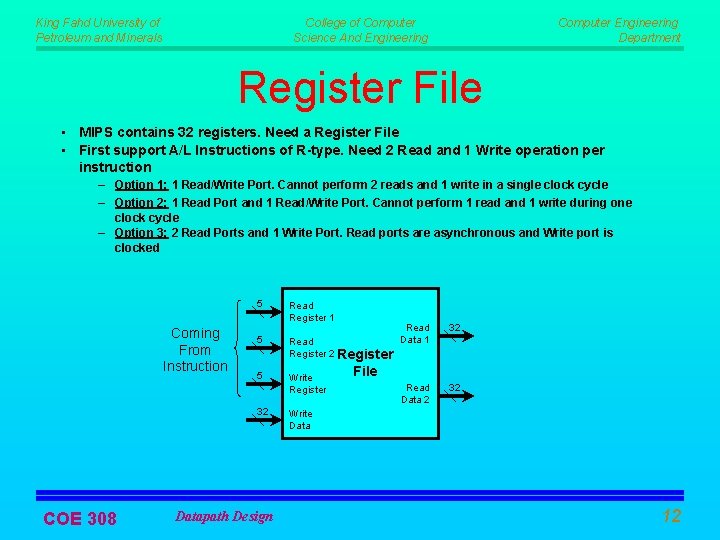

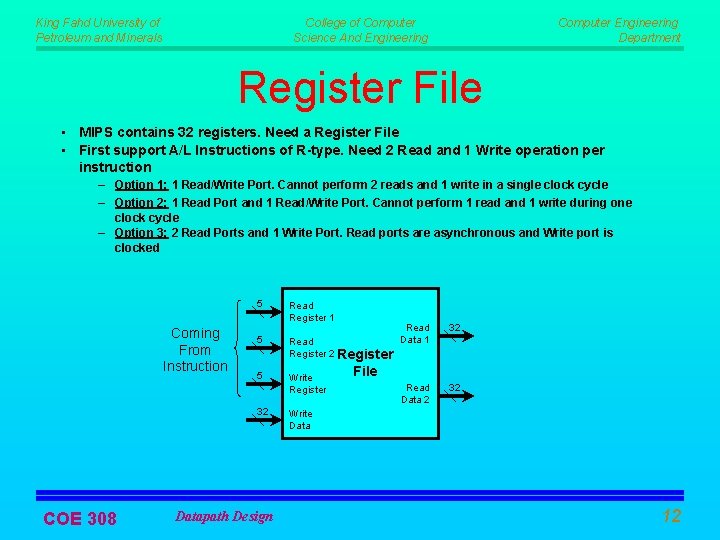

King Fahd University of Petroleum and Minerals College of Computer Science And Engineering Computer Engineering Department Register File • MIPS contains 32 registers. Need a Register File • First support A/L Instructions of R-type. Need 2 Read and 1 Write operation per instruction – Option 1: 1 Read/Write Port. Cannot perform 2 reads and 1 write in a single clock cycle – Option 2: 1 Read Port and 1 Read/Write Port. Cannot perform 1 read and 1 write during one clock cycle – Option 3: 2 Read Ports and 1 Write Port. Read ports are asynchronous and Write port is clocked 5 Coming From Instruction 5 Read Register 2 Register 5 Write Register 32 COE 308 Read Register 1 Datapath Design Read Data 1 32 Read Data 2 32 File Write Data 12

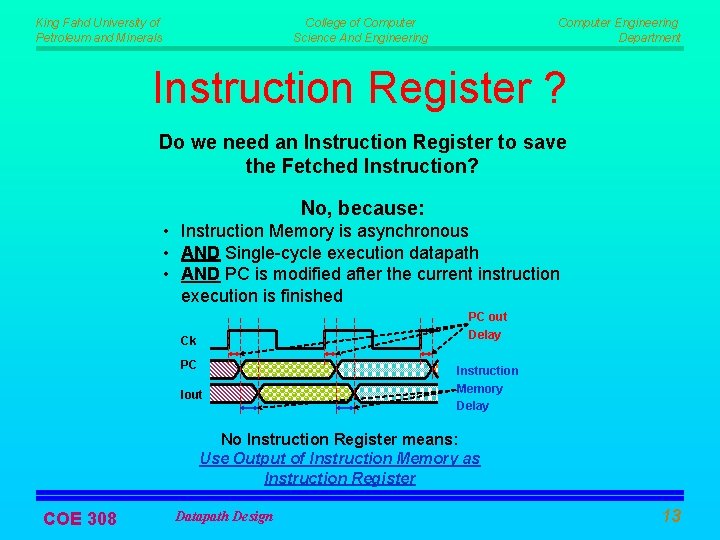

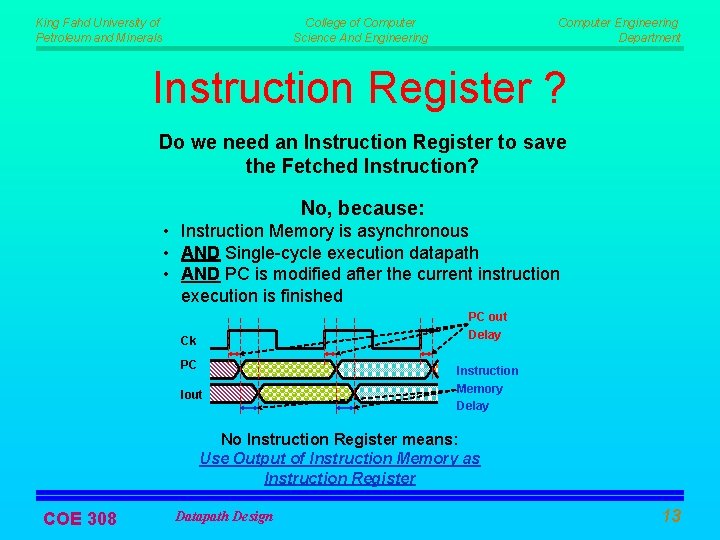

King Fahd University of Petroleum and Minerals College of Computer Science And Engineering Computer Engineering Department Instruction Register ? Do we need an Instruction Register to save the Fetched Instruction? No, because: • Instruction Memory is asynchronous • AND Single-cycle execution datapath • AND PC is modified after the current instruction execution is finished PC out Delay Ck PC Iout Instruction Memory Delay No Instruction Register means: Use Output of Instruction Memory as Instruction Register COE 308 Datapath Design 13

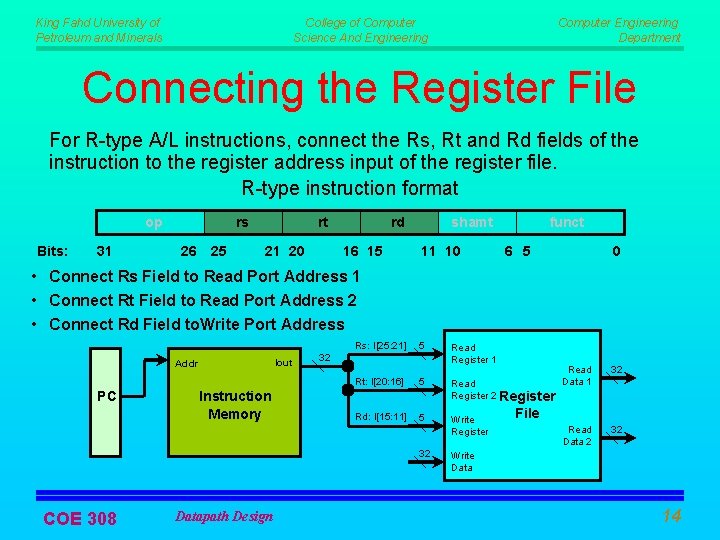

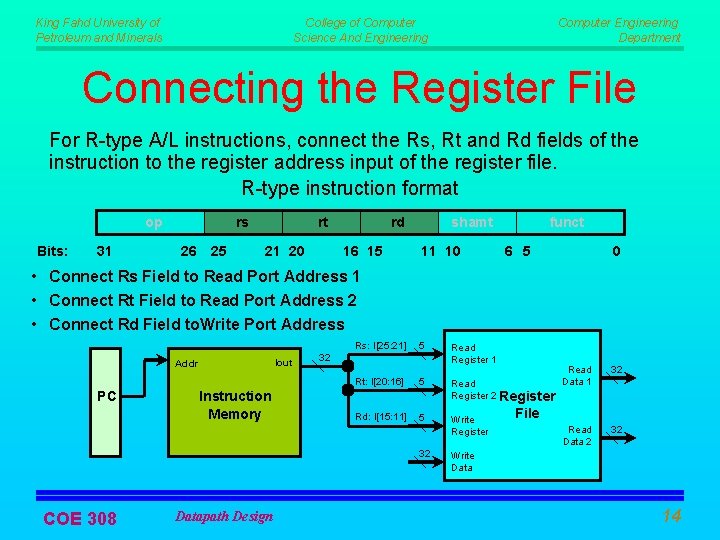

King Fahd University of Petroleum and Minerals College of Computer Science And Engineering Computer Engineering Department Connecting the Register File For R-type A/L instructions, connect the Rs, Rt and Rd fields of the instruction to the register address input of the register file. R-type instruction format op Bits: 31 rs 26 25 rt 21 20 rd 16 15 shamt 11 10 funct 6 5 0 • Connect Rs Field to Read Port Address 1 • Connect Rt Field to Read Port Address 2 • Connect Rd Field to. Write Port Address Iout Addr PC Instruction Memory Rs: I[25: 21] 5 Rt: I[20: 16] 5 Rd: I[15: 11] 5 32 32 COE 308 Datapath Design Read Register 1 Read Data 1 Read Register 2 Register Write Register 32 File Read Data 2 32 Write Data 14

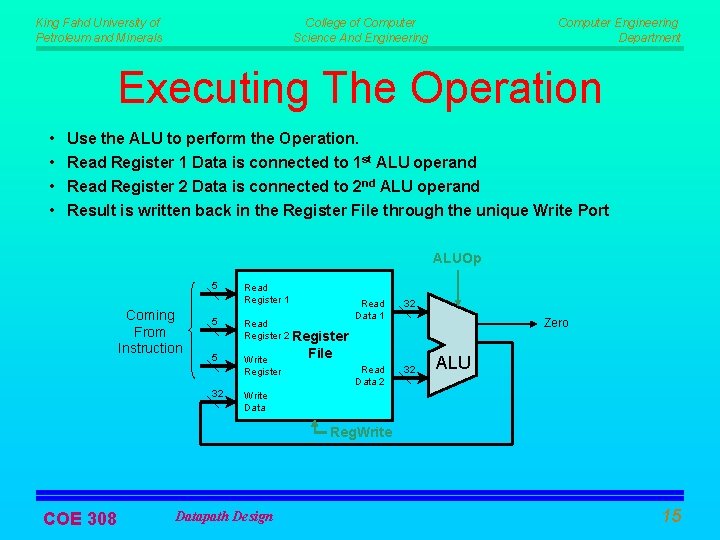

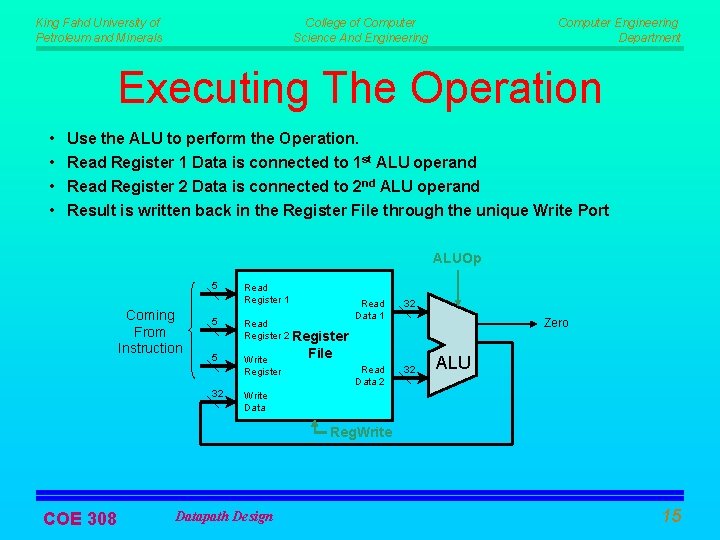

King Fahd University of Petroleum and Minerals College of Computer Science And Engineering Computer Engineering Department Executing The Operation • • Use the ALU to perform the Operation. Read Register 1 Data is connected to 1 st ALU operand Read Register 2 Data is connected to 2 nd ALU operand Result is written back in the Register File through the unique Write Port ALUOp 5 Coming From Instruction Read Register 1 5 Read Register 2 Register 5 Write Register 32 Read Data 1 32 Read Data 2 32 Zero File ALU Write Data Reg. Write COE 308 Datapath Design 15

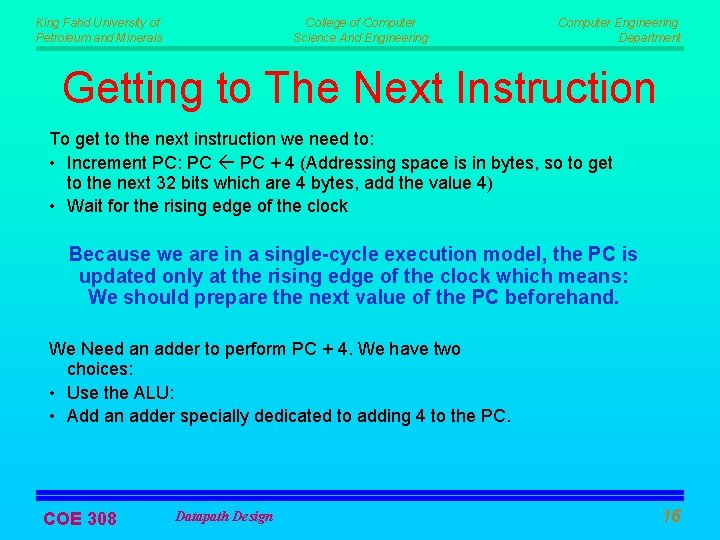

King Fahd University of Petroleum and Minerals College of Computer Science And Engineering Computer Engineering Department Getting to The Next Instruction To get to the next instruction we need to: • Increment PC: PC + 4 (Addressing space is in bytes, so to get to the next 32 bits which are 4 bytes, add the value 4) • Wait for the rising edge of the clock Because we are in a single-cycle execution model, the PC is updated only at the rising edge of the clock which means: We should prepare the next value of the PC beforehand. We Need an adder to perform PC + 4. We have two choices: • Use the ALU: • Add an adder specially dedicated to adding 4 to the PC. COE 308 Datapath Design 16

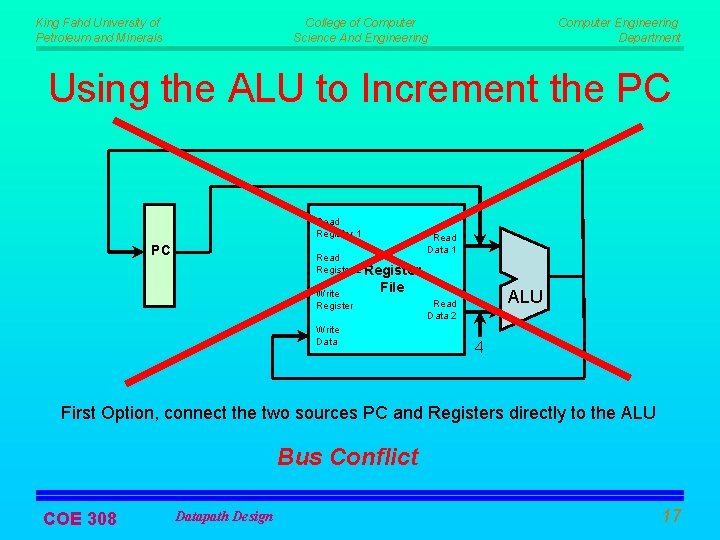

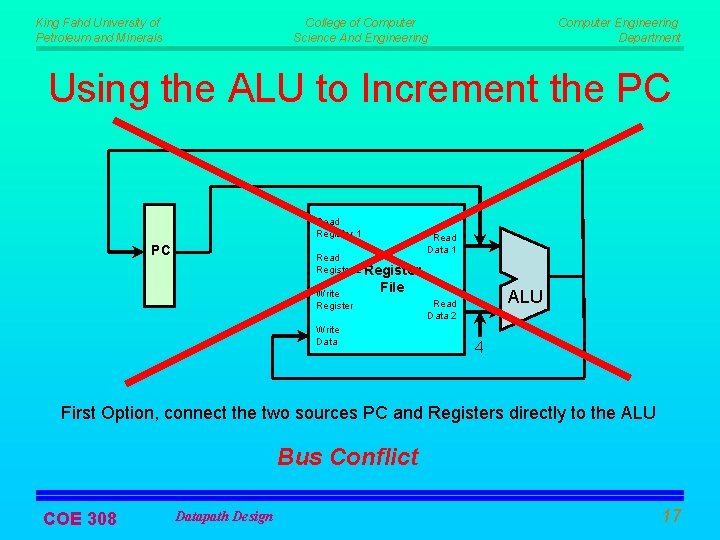

King Fahd University of Petroleum and Minerals College of Computer Science And Engineering Computer Engineering Department Using the ALU to Increment the PC Read Register 1 PC Read Register 2 Register Write Register Read Data 1 File Write Data ALU Read Data 2 4 First Option, connect the two sources PC and Registers directly to the ALU Bus Conflict COE 308 Datapath Design 17

King Fahd University of Petroleum and Minerals College of Computer Science And Engineering Computer Engineering Department Using the ALU to Increment the PC (2) Read Register 1 PC Read Register 2 Register Write Data File Read Data 1 ALU Read Data 2 4 Second Option, connect the two sources PC and Registers through Muxes to select which block uses the ALU Need 2 phases (clock cycles) COE 308 Datapath Design 18

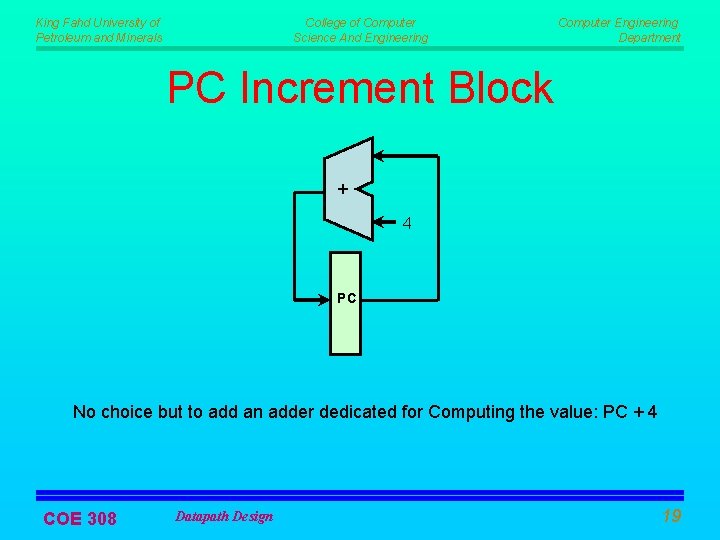

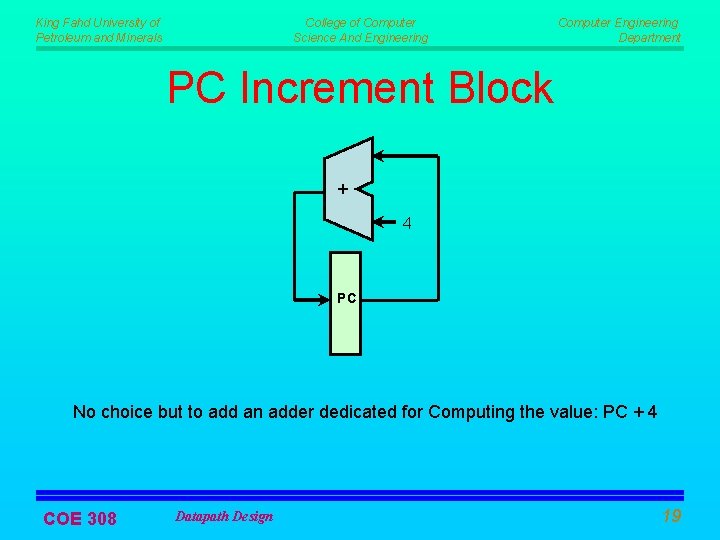

King Fahd University of Petroleum and Minerals College of Computer Science And Engineering Computer Engineering Department PC Increment Block + 4 PC No choice but to add an adder dedicated for Computing the value: PC + 4 COE 308 Datapath Design 19

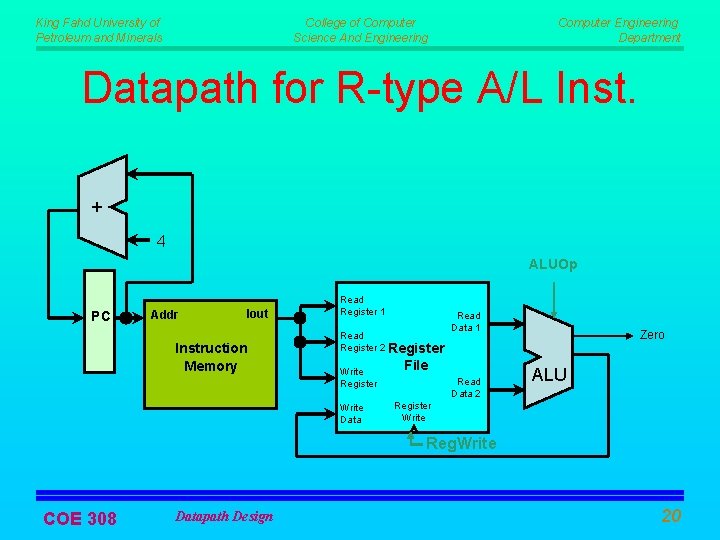

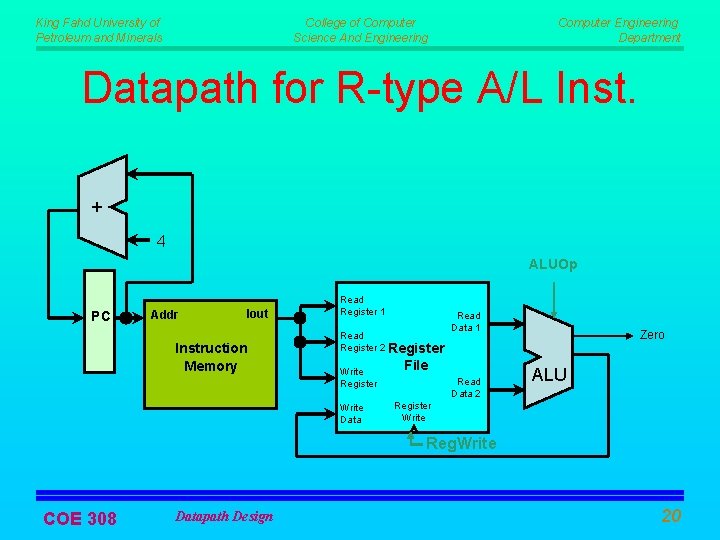

King Fahd University of Petroleum and Minerals College of Computer Science And Engineering Computer Engineering Department Datapath for R-type A/L Inst. + 4 ALUOp PC Addr Iout Instruction Memory Read Register 1 Read Register 2 Register Write Data Read Data 1 File Read Data 2 Zero ALU Register Write Reg. Write COE 308 Datapath Design 20

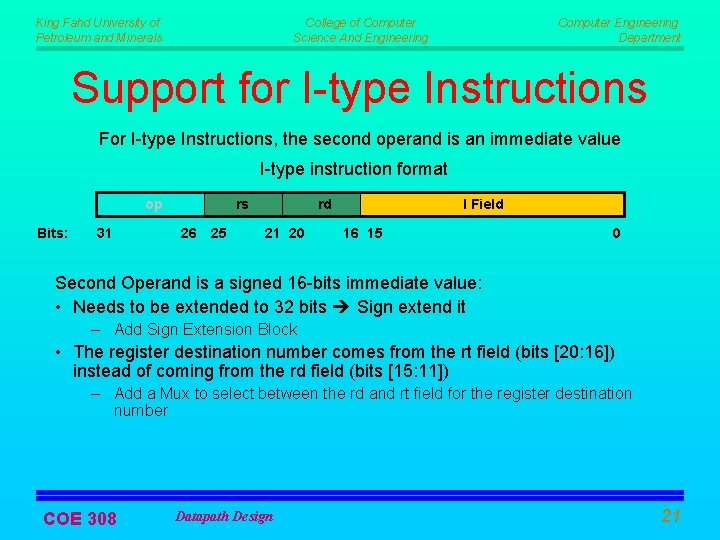

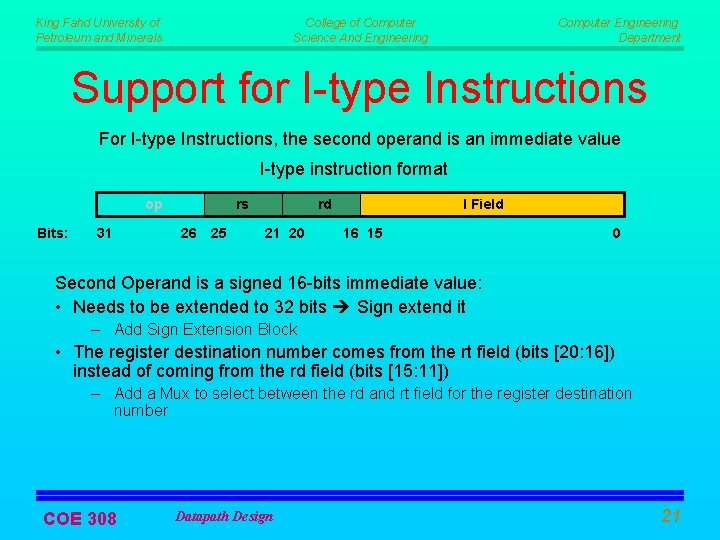

King Fahd University of Petroleum and Minerals College of Computer Science And Engineering Computer Engineering Department Support for I-type Instructions For I-type Instructions, the second operand is an immediate value I-type instruction format op Bits: 31 rs 26 25 rd 21 20 I Field 16 15 0 Second Operand is a signed 16 -bits immediate value: • Needs to be extended to 32 bits Sign extend it – Add Sign Extension Block • The register destination number comes from the rt field (bits [20: 16]) instead of coming from the rd field (bits [15: 11]) – Add a Mux to select between the rd and rt field for the register destination number COE 308 Datapath Design 21

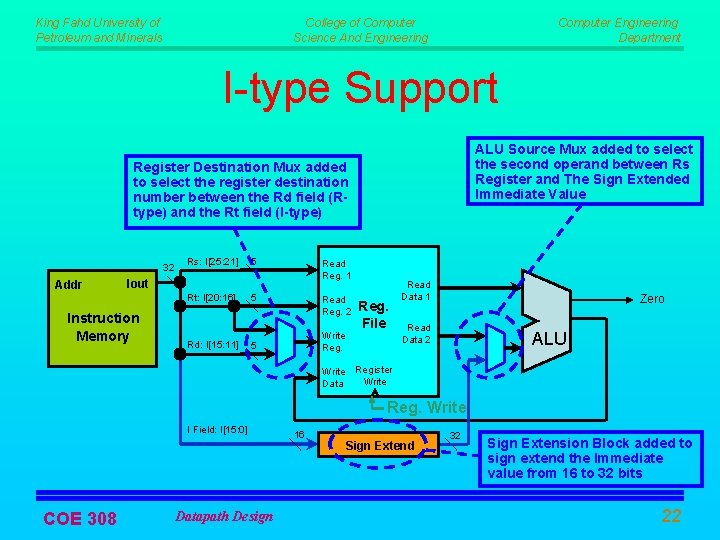

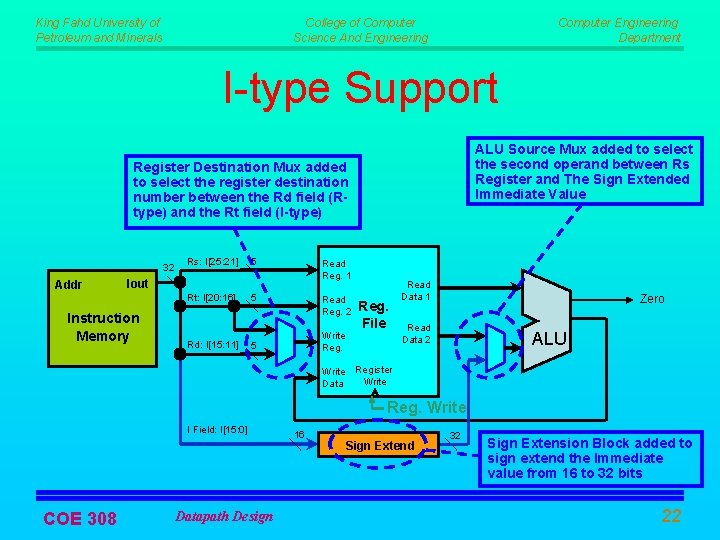

King Fahd University of Petroleum and Minerals College of Computer Science And Engineering Computer Engineering Department I-type Support ALU Source Mux added to select the second operand between Rs Register and The Sign Extended Immediate Value Register Destination Mux added to select the register destination number between the Rd field (Rtype) and the Rt field (I-type) 32 Addr Rs: I[25: 21] 5 Read Reg. 1 Rt: I[20: 16] 5 Read Reg. 2 Iout Instruction Memory Rd: I[15: 11] Write Reg. 5 Reg. File Read Data 1 Zero Read Data 2 ALU Write Register Write Data Reg. Write I Field: I[15: 0] COE 308 Datapath Design 16 Sign Extend 32 Sign Extension Block added to sign extend the Immediate value from 16 to 32 bits 22

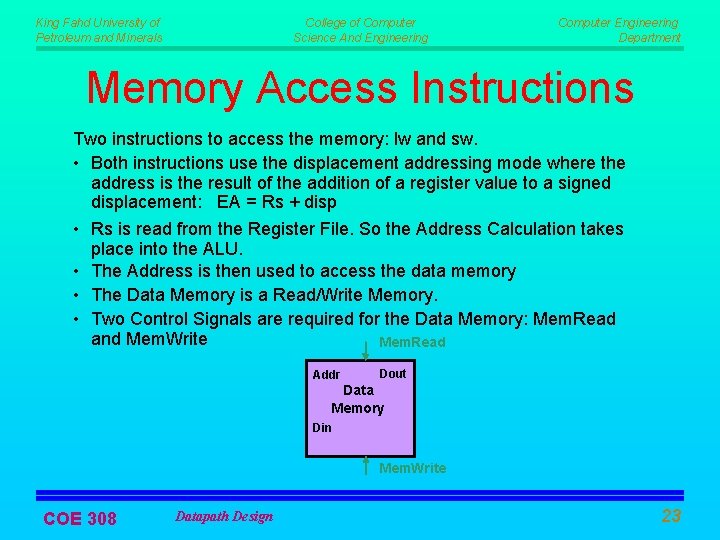

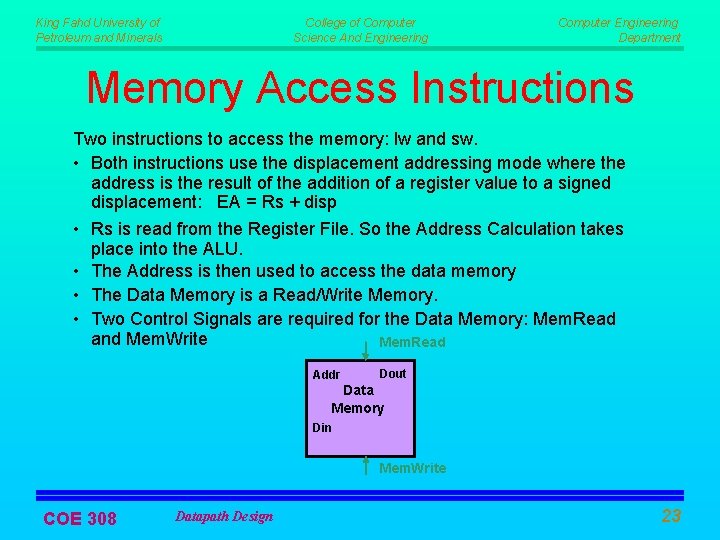

King Fahd University of Petroleum and Minerals College of Computer Science And Engineering Computer Engineering Department Memory Access Instructions Two instructions to access the memory: lw and sw. • Both instructions use the displacement addressing mode where the address is the result of the addition of a register value to a signed displacement: EA = Rs + disp • Rs is read from the Register File. So the Address Calculation takes place into the ALU. • The Address is then used to access the data memory • The Data Memory is a Read/Write Memory. • Two Control Signals are required for the Data Memory: Mem. Read and Mem. Write Mem. Read Addr Dout Data Memory Din Mem. Write COE 308 Datapath Design 23

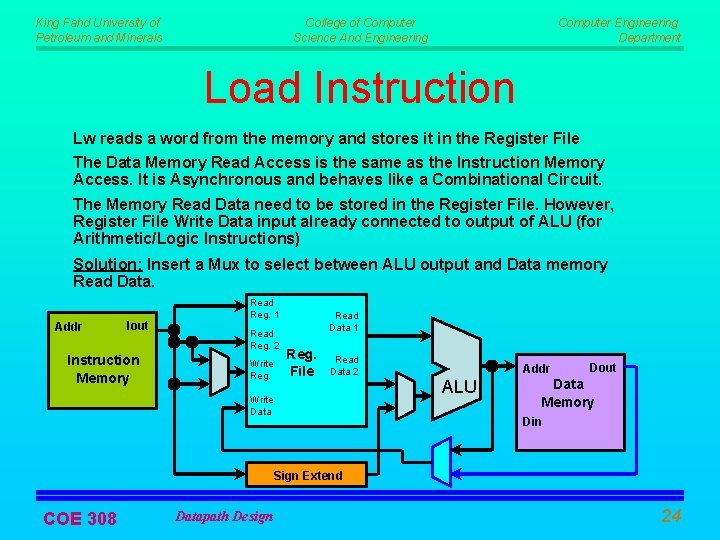

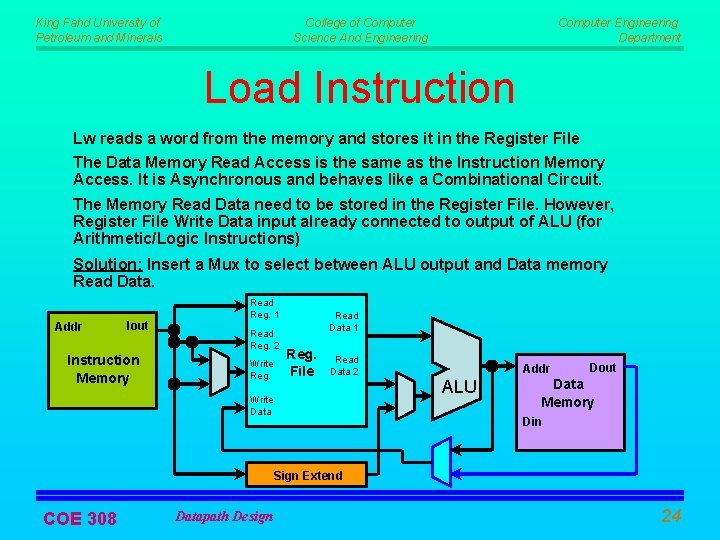

King Fahd University of Petroleum and Minerals College of Computer Science And Engineering Computer Engineering Department Load Instruction Lw reads a word from the memory and stores it in the Register File The Data Memory Read Access is the same as the Instruction Memory Access. It is Asynchronous and behaves like a Combinational Circuit. The Memory Read Data need to be stored in the Register File. However, Register File Write Data input already connected to output of ALU (for Arithmetic/Logic Instructions) Solution: Insert a Mux to select between ALU output and Data memory Read Data. Addr Iout Instruction Memory Read Reg. 1 Read Reg. 2 Write Reg. Read Data 1 Reg. File Read Data 2 Write Data Addr ALU Dout Data Memory Din Sign Extend COE 308 Datapath Design 24

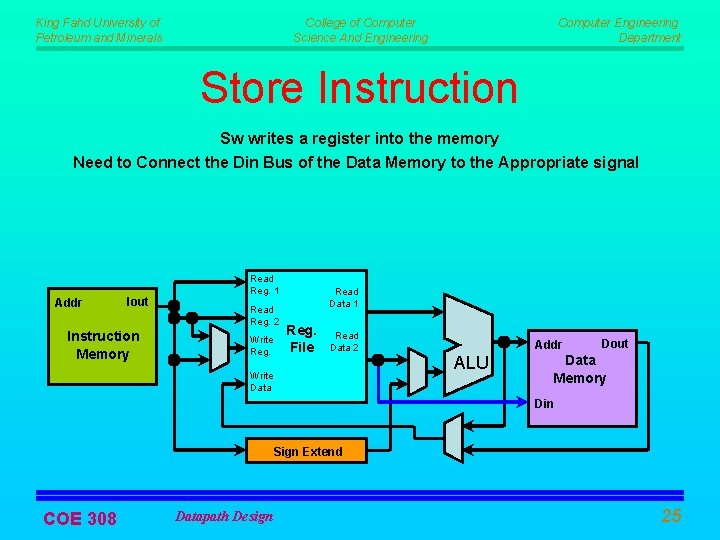

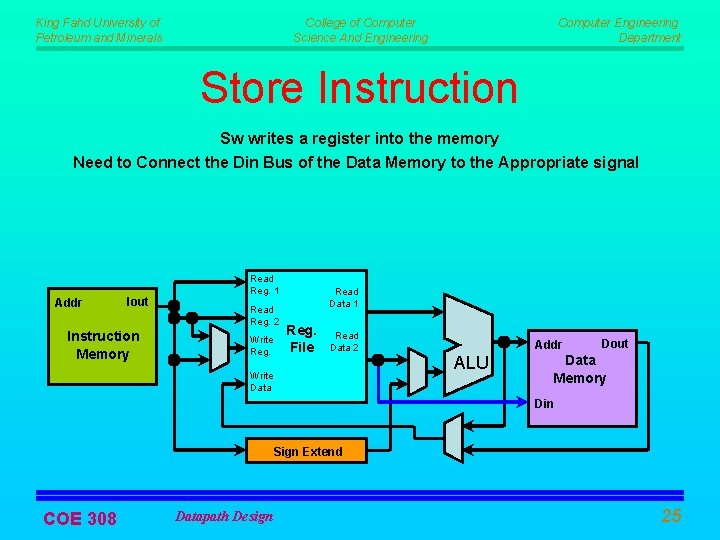

King Fahd University of Petroleum and Minerals College of Computer Science And Engineering Computer Engineering Department Store Instruction Sw writes a register into the memory Need to Connect the Din Bus of the Data Memory to the Appropriate signal Addr Iout Instruction Memory Read Reg. 1 Read Reg. 2 Write Reg. Read Data 1 Reg. File Read Data 2 Write Data Addr ALU Dout Data Memory Din Sign Extend COE 308 Datapath Design 25

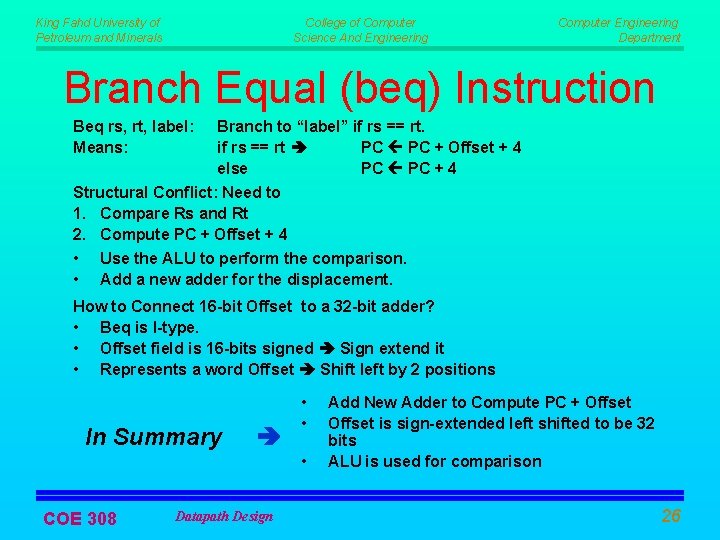

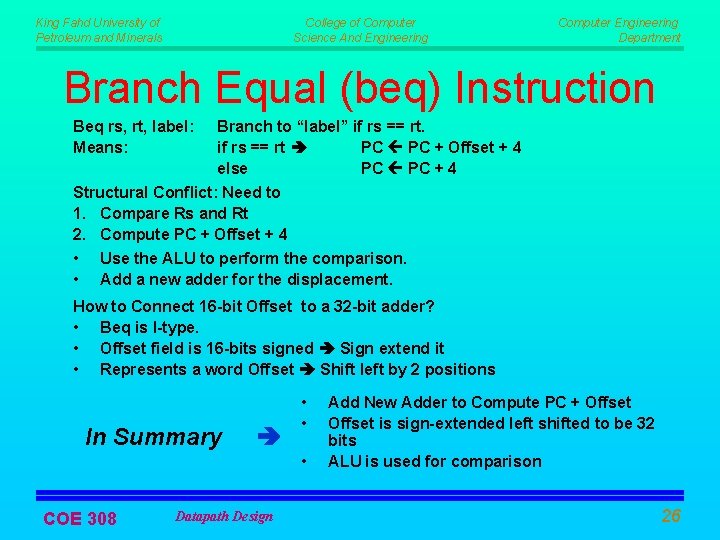

King Fahd University of Petroleum and Minerals College of Computer Science And Engineering Computer Engineering Department Branch Equal (beq) Instruction Beq rs, rt, label: Means: Branch to “label” if rs == rt PC + Offset + 4 else PC + 4 Structural Conflict: Need to 1. Compare Rs and Rt 2. Compute PC + Offset + 4 • Use the ALU to perform the comparison. • Add a new adder for the displacement. How to Connect 16 -bit Offset to a 32 -bit adder? • Beq is I-type. • Offset field is 16 -bits signed Sign extend it • Represents a word Offset Shift left by 2 positions In Summary • • • COE 308 Datapath Design Add New Adder to Compute PC + Offset is sign-extended left shifted to be 32 bits ALU is used for comparison 26

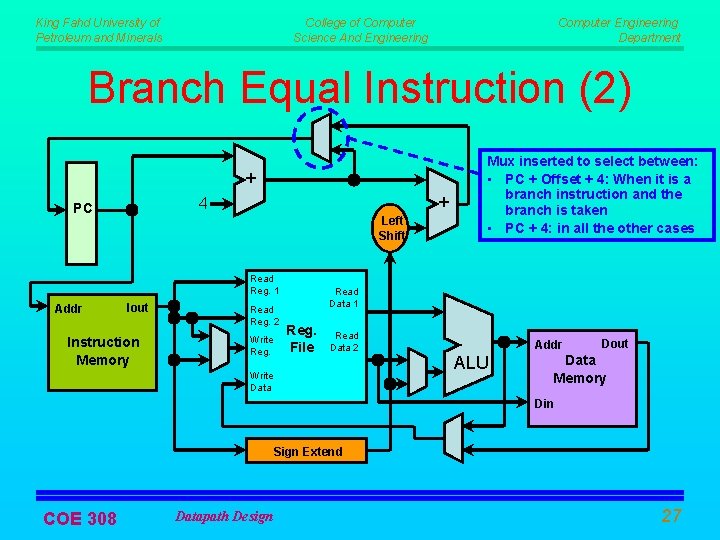

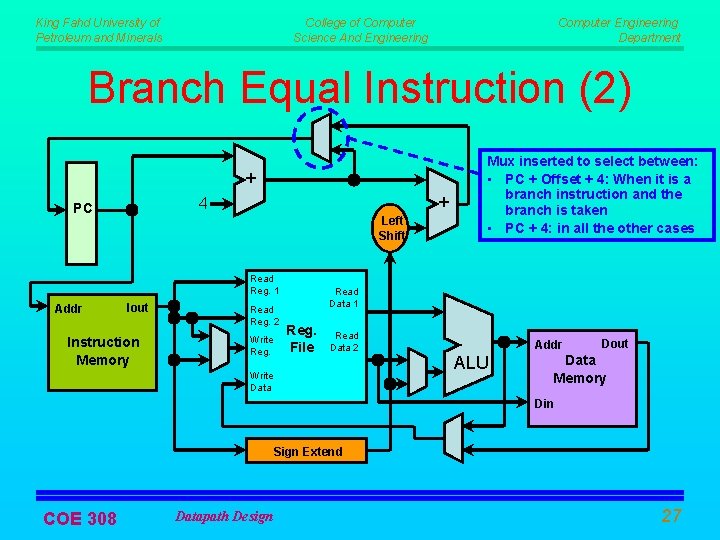

King Fahd University of Petroleum and Minerals College of Computer Science And Engineering Computer Engineering Department Branch Equal Instruction (2) + + 4 PC Left Shift Read Reg. 1 Addr Iout Instruction Memory Read Reg. 2 Write Reg. Mux inserted to select between: • PC + Offset + 4: When it is a branch instruction and the branch is taken • PC + 4: in all the other cases Read Data 1 Reg. File Read Data 2 Write Data Addr ALU Dout Data Memory Din Sign Extend COE 308 Datapath Design 27

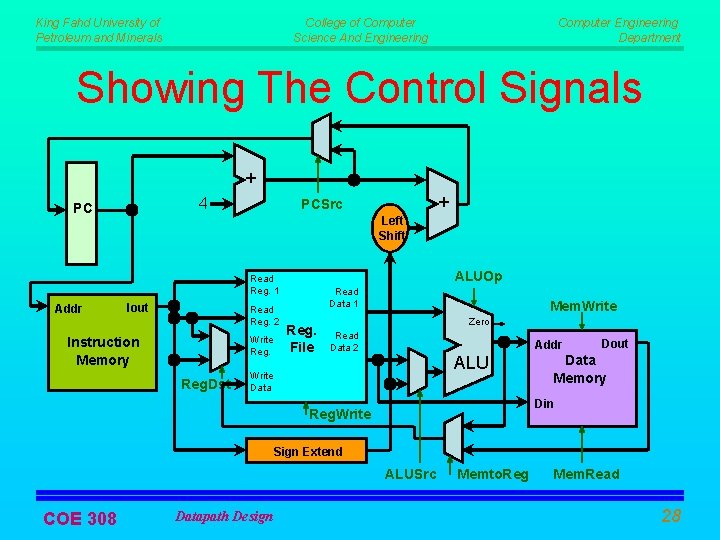

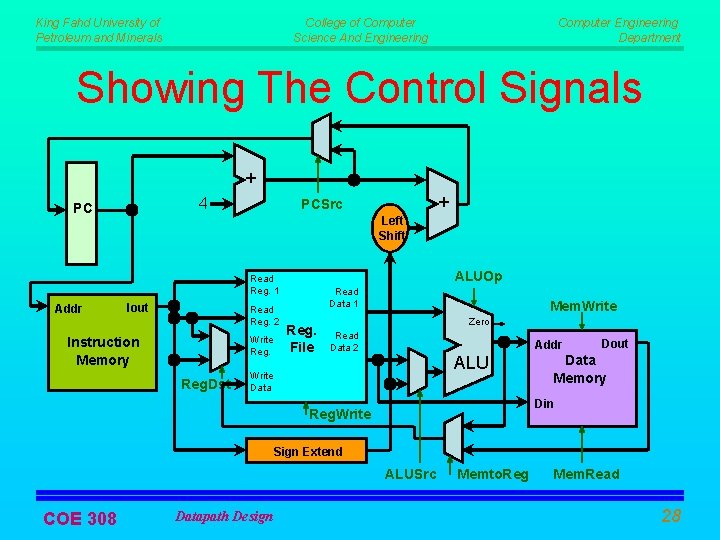

King Fahd University of Petroleum and Minerals College of Computer Science And Engineering Computer Engineering Department Showing The Control Signals + 4 PC Left Shift ALUOp Read Reg. 1 Addr + PCSrc Iout Read Reg. 2 Write Reg. Instruction Memory Reg. Dst Read Data 1 Reg. File Mem. Write Zero Read Data 2 Addr ALU Write Data Dout Data Memory Din Reg. Write Sign Extend ALUSrc COE 308 Datapath Design Memto. Reg Mem. Read 28

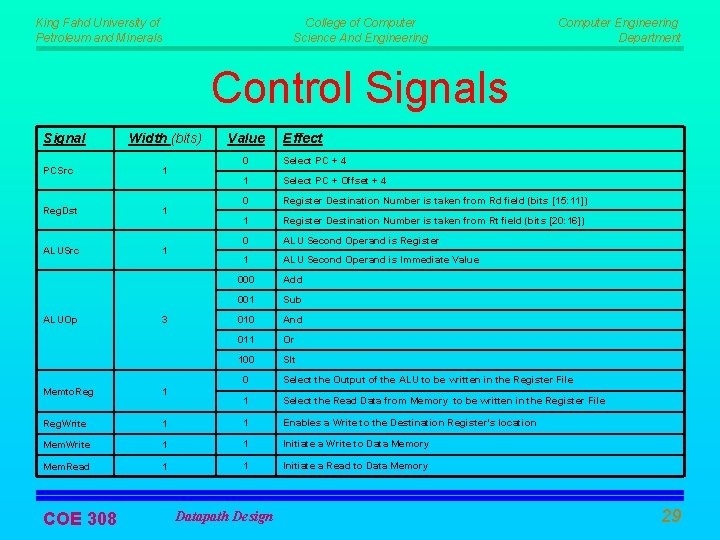

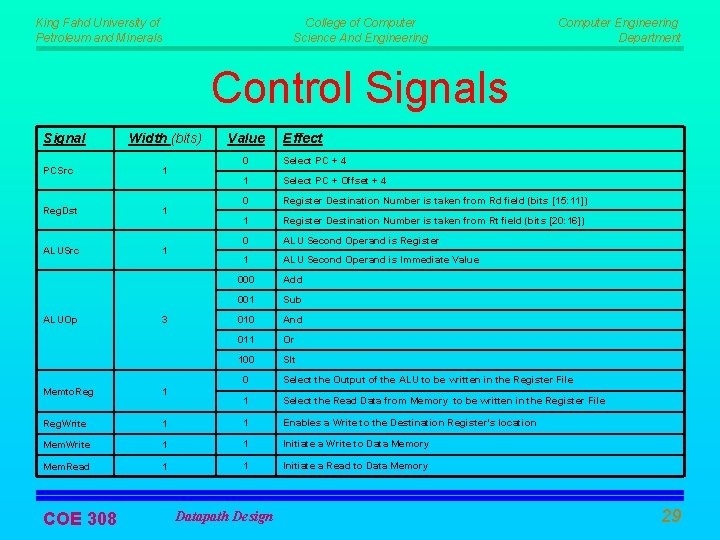

King Fahd University of Petroleum and Minerals College of Computer Science And Engineering Computer Engineering Department Control Signals Signal Width (bits) PCSrc 1 Reg. Dst 1 ALUSrc 1 ALUOp 3 Value Effect 0 Select PC + 4 1 Select PC + Offset + 4 0 Register Destination Number is taken from Rd field (bits [15: 11]) 1 Register Destination Number is taken from Rt field (bits [20: 16]) 0 ALU Second Operand is Register 1 ALU Second Operand is Immediate Value 000 Add 001 Sub 010 And 011 Or 100 Slt 0 Select the Output of the ALU to be written in the Register File 1 Select the Read Data from Memory to be written in the Register File 1 1 Enables a Write to the Destination Register’s location Mem. Write 1 1 Initiate a Write to Data Memory Mem. Read 1 1 Initiate a Read to Data Memory Memto. Reg 1 Reg. Write COE 308 Datapath Design 29

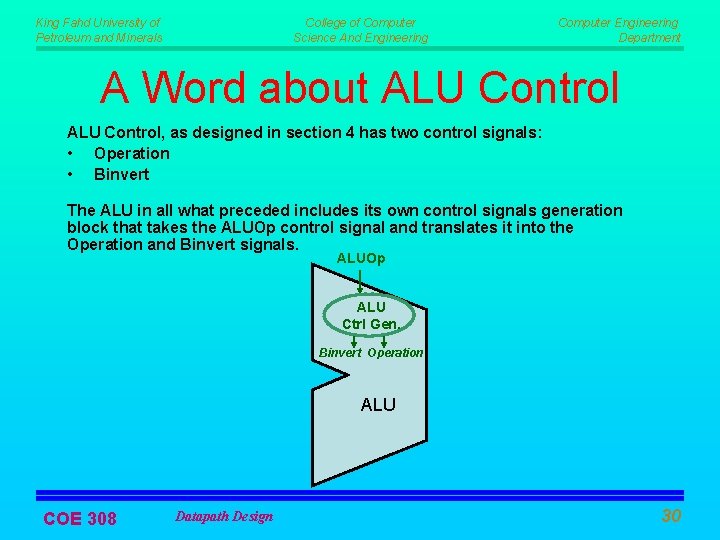

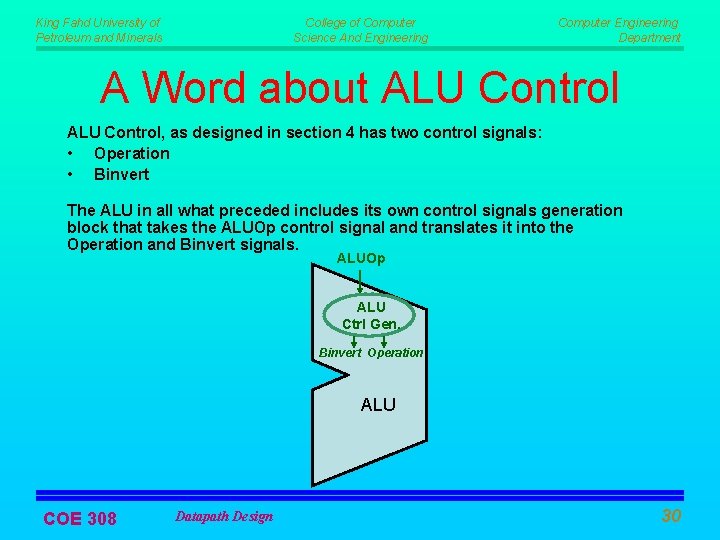

King Fahd University of Petroleum and Minerals College of Computer Science And Engineering Computer Engineering Department A Word about ALU Control, as designed in section 4 has two control signals: • Operation • Binvert The ALU in all what preceded includes its own control signals generation block that takes the ALUOp control signal and translates it into the Operation and Binvert signals. ALUOp ALU Ctrl Gen. Binvert Operation ALU COE 308 Datapath Design 30

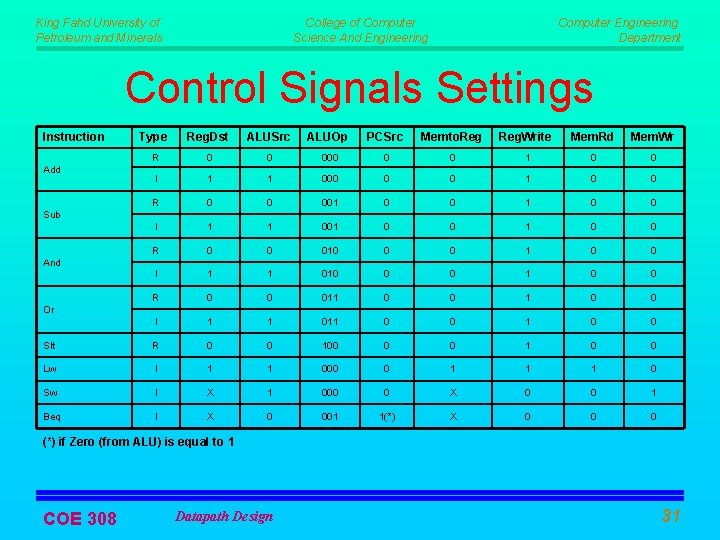

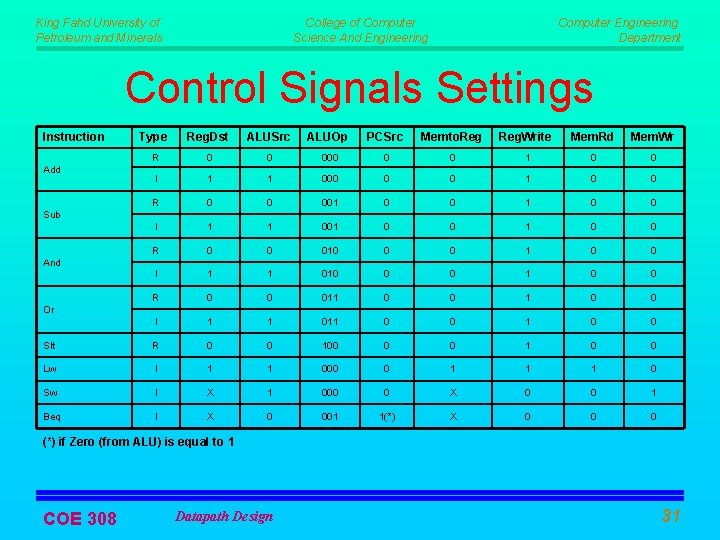

King Fahd University of Petroleum and Minerals College of Computer Science And Engineering Computer Engineering Department Control Signals Settings Instruction Type Reg. Dst ALUSrc ALUOp PCSrc Memto. Reg. Write Mem. Rd Mem. Wr R 0 0 000 0 0 1 0 0 I 1 1 000 0 0 1 0 0 R 0 0 001 0 0 I 1 1 001 0 0 R 0 0 010 0 0 1 0 0 I 1 1 010 0 0 1 0 0 R 0 0 011 0 0 I 1 1 011 0 0 Slt R 0 0 100 0 0 1 0 0 Lw I 1 1 000 0 1 1 1 0 Sw I X 1 000 0 X 0 0 1 Beq I X 0 001 1(*) X 0 0 0 Add Sub And Or (*) if Zero (from ALU) is equal to 1 COE 308 Datapath Design 31

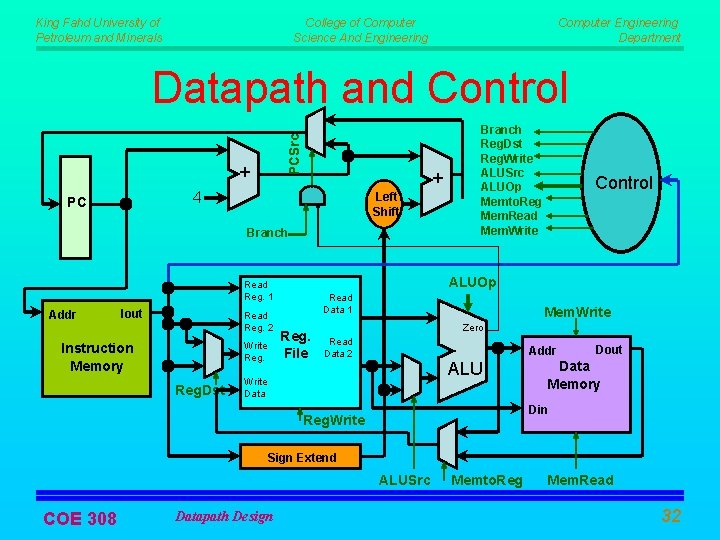

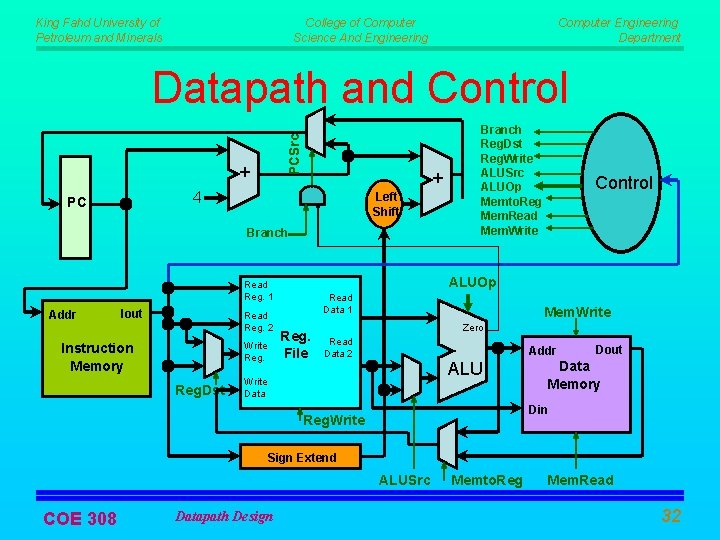

King Fahd University of Petroleum and Minerals College of Computer Science And Engineering Computer Engineering Department PCSrc Datapath and Control + + 4 PC Left Shift Branch Iout Read Reg. 2 Write Reg. Instruction Memory Reg. Dst Control ALUOp Read Reg. 1 Addr Branch Reg. Dst Reg. Write ALUSrc ALUOp Memto. Reg Mem. Read Mem. Write Read Data 1 Reg. File Mem. Write Zero Read Data 2 Addr ALU Write Data Dout Data Memory Din Reg. Write Sign Extend ALUSrc COE 308 Datapath Design Memto. Reg Mem. Read 32

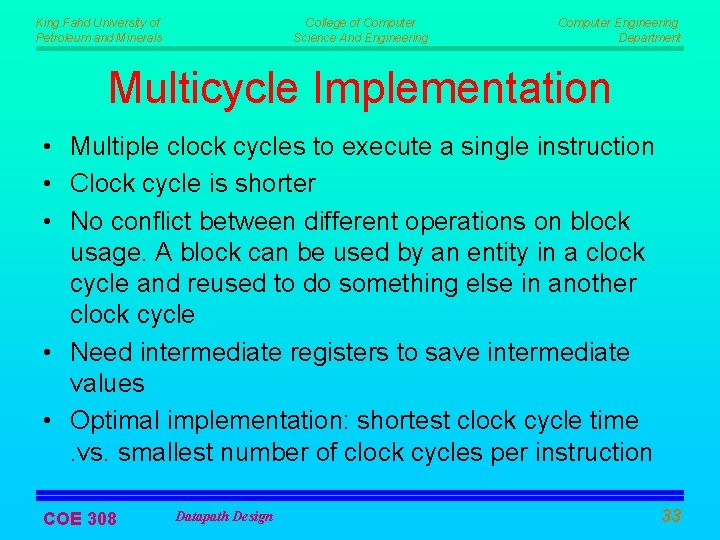

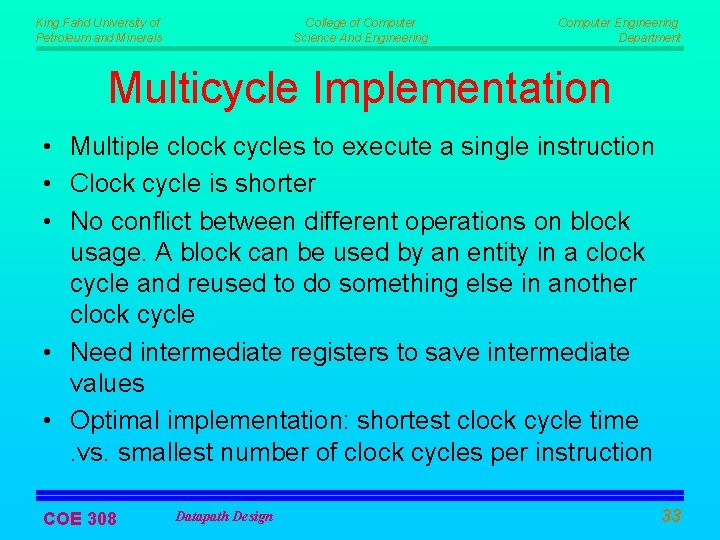

King Fahd University of Petroleum and Minerals College of Computer Science And Engineering Computer Engineering Department Multicycle Implementation • Multiple clock cycles to execute a single instruction • Clock cycle is shorter • No conflict between different operations on block usage. A block can be used by an entity in a clock cycle and reused to do something else in another clock cycle • Need intermediate registers to save intermediate values • Optimal implementation: shortest clock cycle time. vs. smallest number of clock cycles per instruction COE 308 Datapath Design 33

King Fahd University of Petroleum and Minerals College of Computer Science And Engineering Computer Engineering Department How many clock cycles ? Choose a clock cycle to perform ONE operation at a time. For example: – Instruction Fetch – Operand Fetch – ALU Operation – PC + 4 – Memory Access – Result Write Back in Register File COE 308 Datapath Design 34

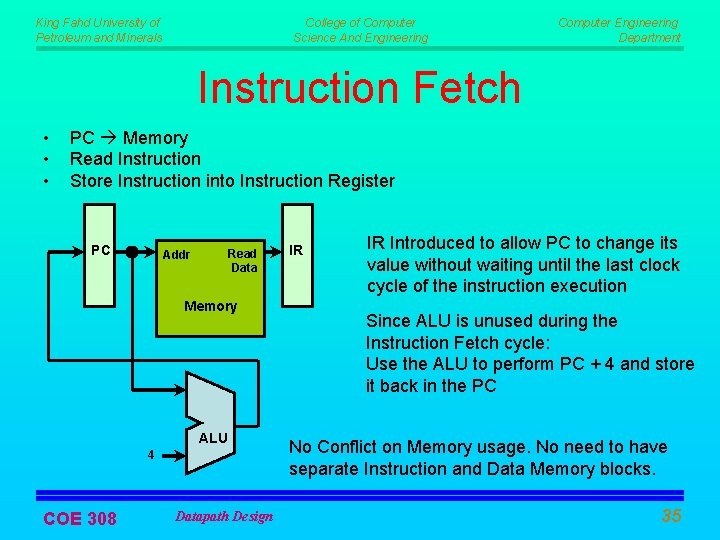

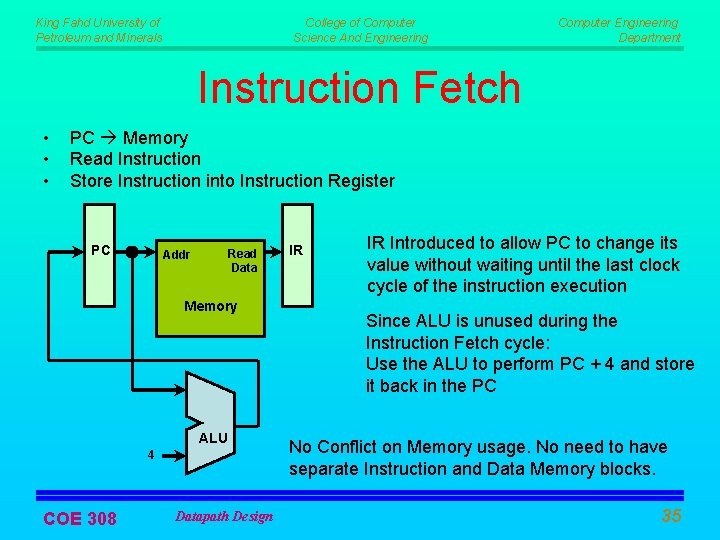

King Fahd University of Petroleum and Minerals College of Computer Science And Engineering Computer Engineering Department Instruction Fetch • • • PC Memory Read Instruction Store Instruction into Instruction Register PC Read Data Addr Memory ALU 4 COE 308 Datapath Design IR IR Introduced to allow PC to change its value without waiting until the last clock cycle of the instruction execution Since ALU is unused during the Instruction Fetch cycle: Use the ALU to perform PC + 4 and store it back in the PC No Conflict on Memory usage. No need to have separate Instruction and Data Memory blocks. 35

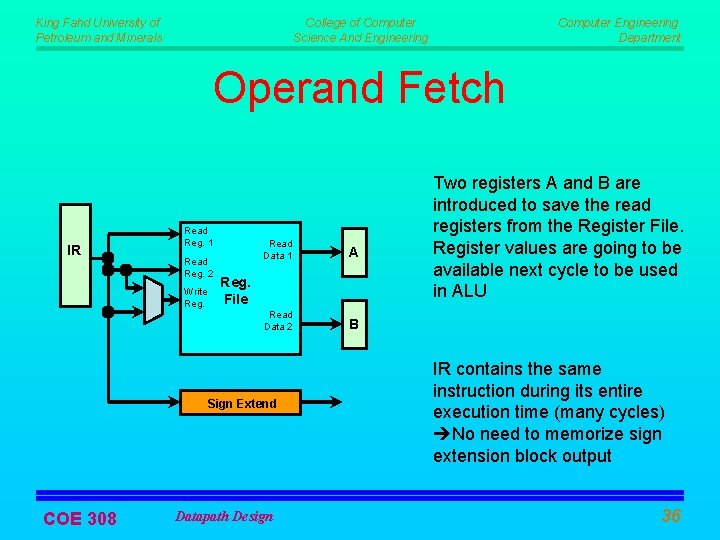

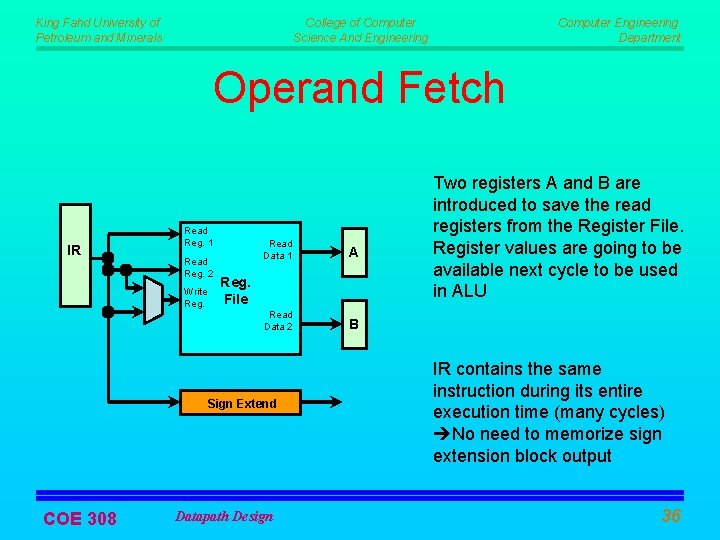

King Fahd University of Petroleum and Minerals College of Computer Science And Engineering Computer Engineering Department Operand Fetch IR Read Reg. 1 Read Reg. 2 Write Reg. Read Data 1 A Read Data 2 B Reg. File Sign Extend COE 308 Datapath Design Two registers A and B are introduced to save the read registers from the Register File. Register values are going to be available next cycle to be used in ALU IR contains the same instruction during its entire execution time (many cycles) No need to memorize sign extension block output 36

King Fahd University of Petroleum and Minerals College of Computer Science And Engineering Computer Engineering Department ALU Operation COE 308 Datapath Design 37