Interrupt Replay a debugging method for parallel programs

Interrupt Replay: a debugging method for parallel programs with interrupts K. M. R. Audenaert and L. J. Levrouw Gan Lin, OS Lab. , GNU Feb. 21, 2012

Au. Le 94 • K. M. R. Audenaert, and L. Levrouw, "Interrupt Replay: a debugging method for parallel programs with interrupts, " Microprocessors and Microsystems, Vol. 18(10): 601 -612, December, 1994 • This paper present an extension of Instant Replay method for replaying parallel programs with interrupts, which records shared object accesses and interrupt occurrences, and then replay programs by the log. 2021/9/7 Au. Le 94_Gan. Lin 2

Contents • • • Replaying Parallel Programs Interrupts Replaying Interrupts Experiment Conclusion 2021/9/7 Au. Le 94_Gan. Lin 3

Replaying Parallel Programs • Debugging parallel programs is difficult – Non-determinate behaviors of programs execution. • Repeatability is important for debugging – Replay method can solve this problem. 2021/9/7 Au. Le 94_Gan. Lin 4

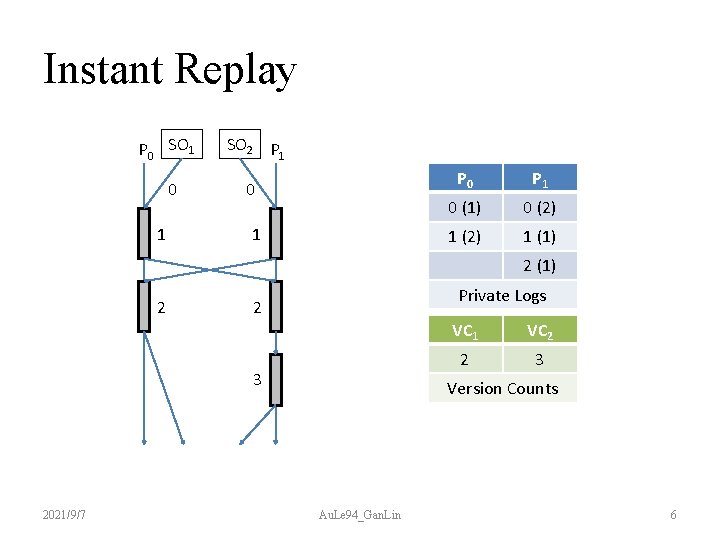

Instant Replay • Instant replay records the orderings between the relevant events, not the events themselves. • Every processor maintains a private log that records version count to represent the shared memory accesses ordering. • Every version count must be kept in a separate shared variable, the version counter. • It prefer to monitor the shared memory access protocol, rather than the accesses themselves. 2021/9/7 Au. Le 94_Gan. Lin 5

Instant Replay P 0 SO 1 0 1 SO 2 P 1 0 1 P 0 P 1 0 (1) 0 (2) 1 (1) 2 Private Logs 2 3 2021/9/7 VC 1 VC 2 2 3 Version Counts Au. Le 94_Gan. Lin 6

Comparison of Replay Level • Program execution can be divided into a number of levels: – Application level – OS level – Hardware level TOP BOTTOM • On top: many kinds of synchronization primitives and thread package dependent. • On bottom: less synchronization primitives and thread package independent. 2021/9/7 Au. Le 94_Gan. Lin 7

The Environment Replay • To nicely replay a program, it is better to replay the environment also. • Sometimes, the environment cannot be easily replayed as programs instrumentation and replay, for example, interrupts from peripheral devices. • To solve this problem, a simulator can be used to simulate the environment, then instrument the simulator and replay it. 2021/9/7 Au. Le 94_Gan. Lin 8

Interrupts • Interrupts are very important mechanism in computer system to respond quickly to critical situations. 2021/9/7 Au. Le 94_Gan. Lin 9

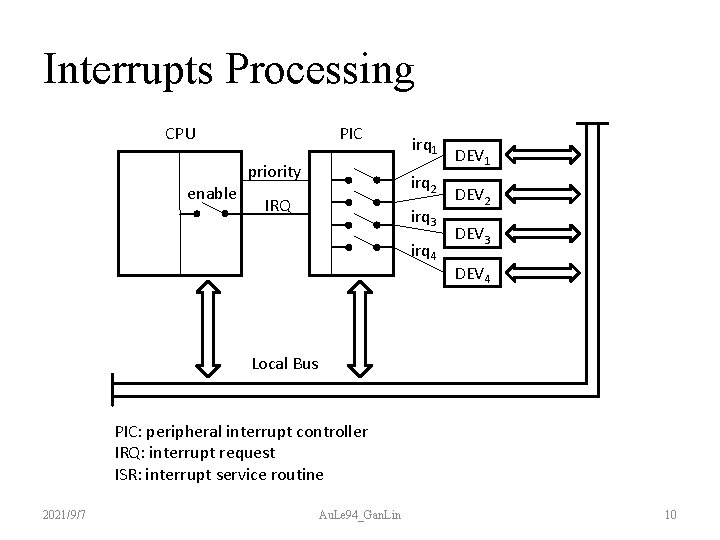

Interrupts Processing CPU PIC priority enable irq 1 irq 2 IRQ irq 3 irq 4 DEV 1 DEV 2 DEV 3 DEV 4 Local Bus PIC: peripheral interrupt controller IRQ: interrupt request ISR: interrupt service routine 2021/9/7 Au. Le 94_Gan. Lin 10

Interrupts Position • Since the environment is now represented by an environment process, we can classify in: – The interrupted processor is also running the environment process, and is thus equal to the interrupting processor; – The environment process runs on a processor other than the interrupted processor; the interrupted processor is thus not the interrupting processor. 2021/9/7 Au. Le 94_Gan. Lin 11

Generation of Interrupts • An interrupt occurs due to one or more causes such as actions of CPU, which is called generator. • If an interrupts type has multiple conjunctive generators, then only the last generator has to be considered. • If it has multiple generators, then each of the generators has to be considered. 2021/9/7 Au. Le 94_Gan. Lin 12

Replaying Interrupts • There is few research on this area: • {Do. Ra 92} Using an instruction counter to record the time when the interrupt occurs, and to replay the interrupt by this instruction counter. – During replay, the hardware interrupts themselves do not occur, rather their respective ISRs are called. 2021/9/7 Au. Le 94_Gan. Lin 13

Interrupt Replay • An interrupt is modelled by two entities: – Interrupt windows (IW) – Generators • In logged execution, every interrupt is enabled during a number of intervals (IWs). • If both ISR and foreground routine can access the same variable, called interrupt race. • Interrupt Replay assume there are no interrupt race. 2021/9/7 Au. Le 94_Gan. Lin 14

• To ensure this, interrupts should be disabled while the foreground process accesses critical data, thus the foreground process and ISRs are mutex. • Therefore, the IWs are delimited by interrupt enable and disable operations. • For absence of interrupt race, it prefer to count the two instructions bounding the particular IW, rather than the other instructions, thus software instruction counter (SIC) is used. 2021/9/7 Au. Le 94_Gan. Lin 15

• To update the SIC, whenever the interrupt generators, interrupt enables and disables (CPU, PIC, etc. ), including the ISR call and return instructions, and the Csentry and Csexit operations. 2021/9/7 Au. Le 94_Gan. Lin 16

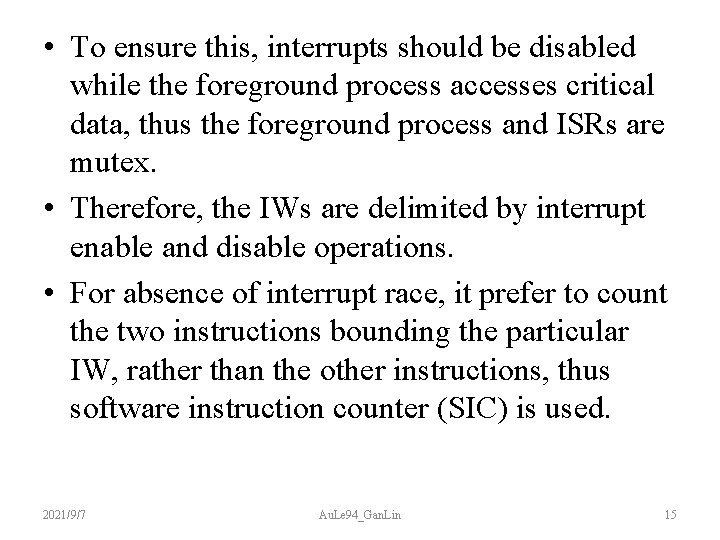

Algorithm: Logging P 0 SIC 0=0 SO 1 P 1 IRQ 1 SIC 1=0 SIC 0=1 LOG 0=(sema, 1) SIC 0=2 LOG 0(irq 1, 2) SIC 0=3 SIC 1=1 LOG 1=(sema, 2) SIC 1=2 SIC 0=4 P 0 P 1 sema, 2 irq 1, 2 Private Log P 0 P 1 4 4 SIC LOG 1(irq 1, 2) SIC 1=3 SIC 0=4 2021/9/7 Au. Le 94_Gan. Lin 17

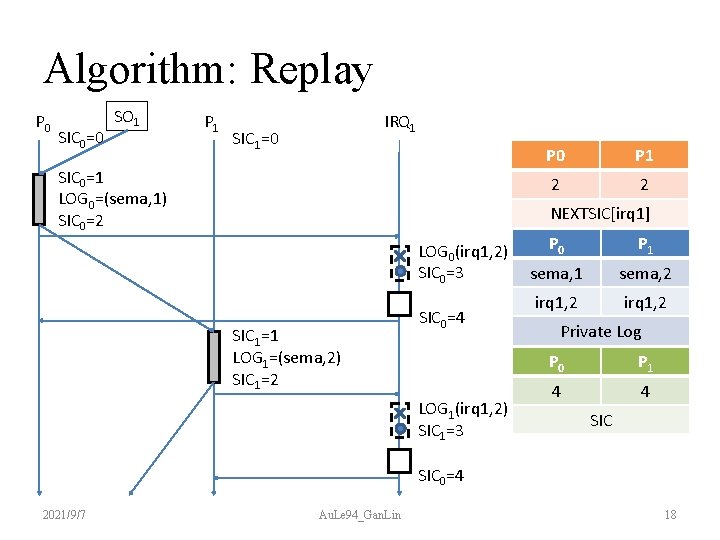

Algorithm: Replay P 0 SIC 0=0 SO 1 P 1 IRQ 1 SIC 1=0 SIC 0=1 LOG 0=(sema, 1) SIC 0=2 P 0 P 1 2 2 NEXTSIC[irq 1] LOG 0(irq 1, 2) SIC 0=3 SIC 1=1 LOG 1=(sema, 2) SIC 1=2 SIC 0=4 LOG 1(irq 1, 2) SIC 1=3 P 0 P 1 sema, 2 irq 1, 2 Private Log P 0 P 1 4 4 SIC 0=4 2021/9/7 Au. Le 94_Gan. Lin 18

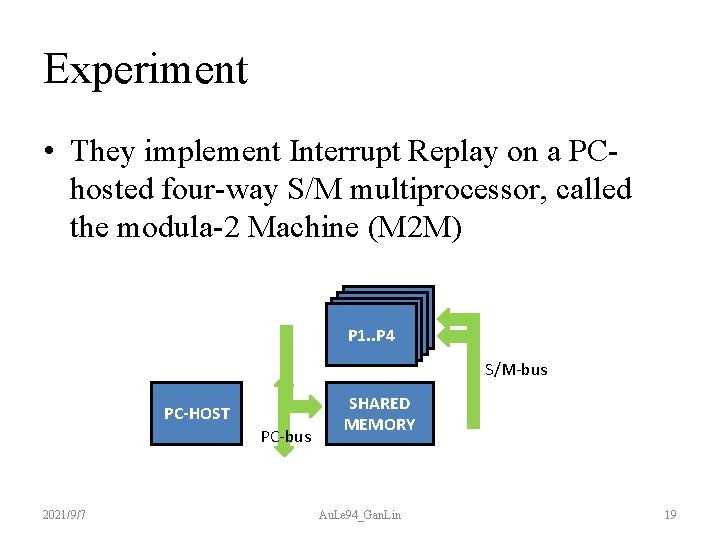

Experiment • They implement Interrupt Replay on a PChosted four-way S/M multiprocessor, called the modula-2 Machine (M 2 M) P 1. . P 4 S/M-bus PC-HOST PC-bus 2021/9/7 SHARED MEMORY Au. Le 94_Gan. Lin 19

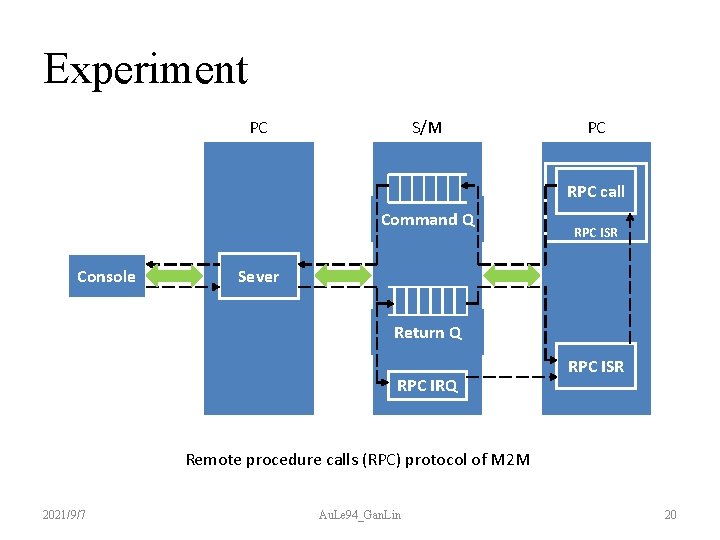

Experiment PC S/M PC RPC call Command Q Console RPC ISR Sever Return Q RPC IRQ RPC ISR Remote procedure calls (RPC) protocol of M 2 M 2021/9/7 Au. Le 94_Gan. Lin 20

Conclusion • This paper present a interesting method for debugging programs that use interrupts, by defining IWs and recording SICs, these programs can be easily replayed; however, the programs should be interrupt race free. 2021/9/7 Au. Le 94_Gan. Lin 21

2021/9/7 Au. Le 94_Gan. Lin 22

- Slides: 22