EXTERNAL INTERRUPT REQUEST MODULE IRQ External Interrupt Module

- Slides: 16

EXTERNAL INTERRUPT REQUEST MODULE (IRQ) External Interrupt Module MTT 48 13 - 1

Module Objective By the end of this module, you should be able to: • Enable/disable IRQ interrupts • Configure the trigger sensitivity • Acknowledge the interrupts • Configure port external interrupts External Interrupt Module MTT 48 13 - 3

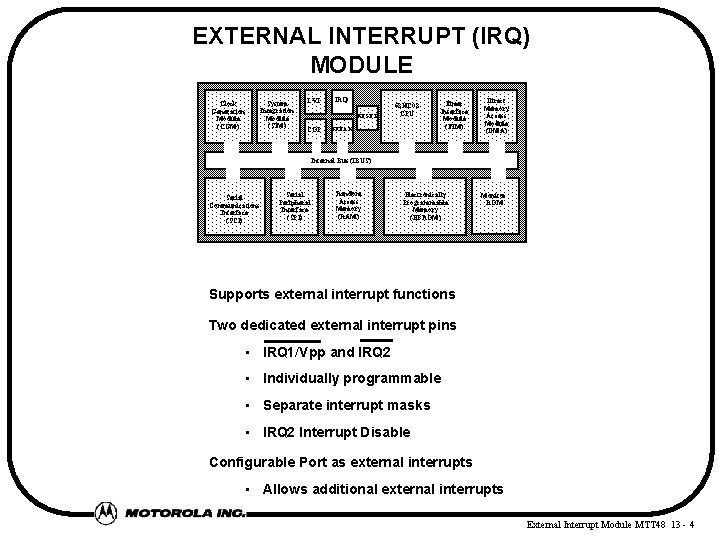

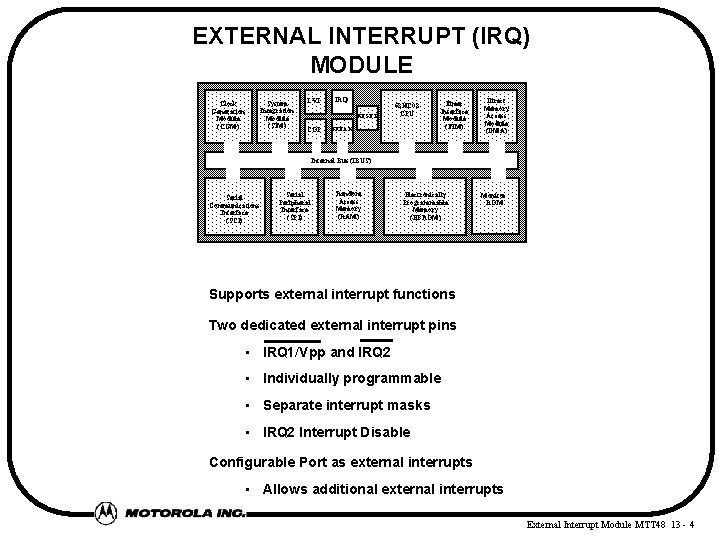

EXTERNAL INTERRUPT (IRQ) MODULE Clock Generation Module (CGM) System Integration Module (SIM) LVI IRQ COP BREAK RESET 68 HC 08 CPU Timer Interface Module (TIM) Direct Memory Access Module (DMA) Internal Bus (IBUS) Serial Communications Interface (SCI) Serial Peripheral Interface (SPI) Random Access Memory (RAM) Electronically Programmable Memory (EPROM) Monitor ROM Supports external interrupt functions Two dedicated external interrupt pins • IRQ 1/Vpp and IRQ 2 • Individually programmable • Separate interrupt masks • IRQ 2 Interrupt Disable Configurable Port as external interrupts • Allows additional external interrupts External Interrupt Module MTT 48 13 - 4

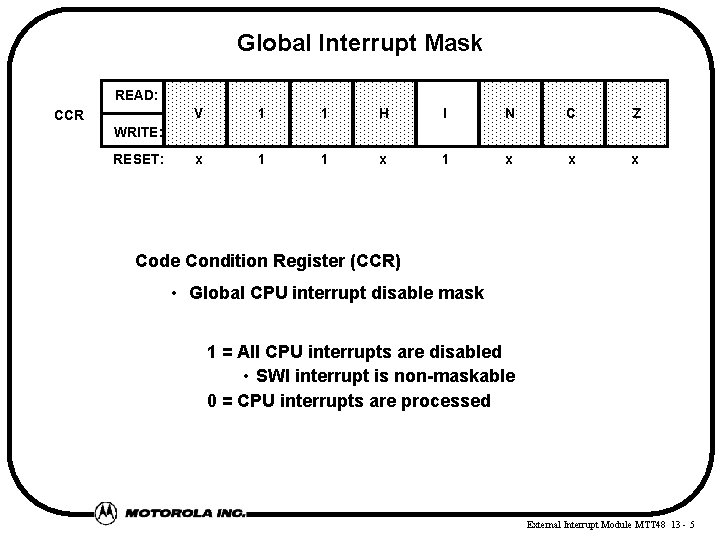

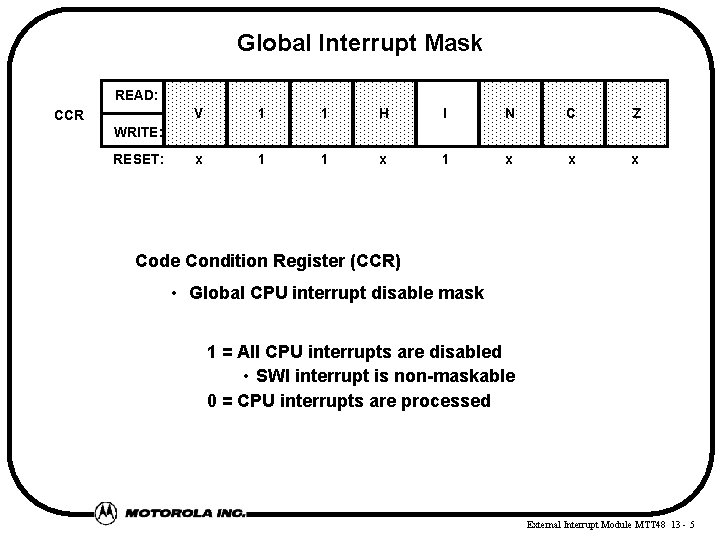

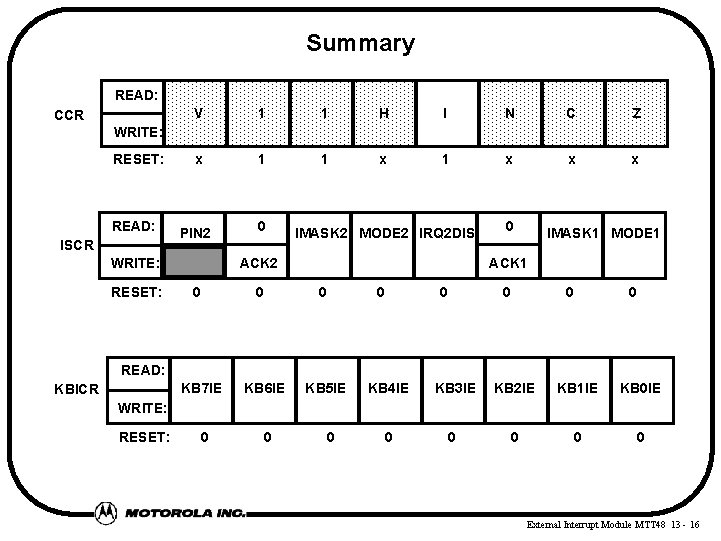

Global Interrupt Mask READ: CCR V 1 1 H I N C Z x 1 1 x x x WRITE: RESET: Code Condition Register (CCR) • Global CPU interrupt disable mask 1 = All CPU interrupts are disabled • SWI interrupt is non-maskable 0 = CPU interrupts are processed External Interrupt Module MTT 48 13 - 5

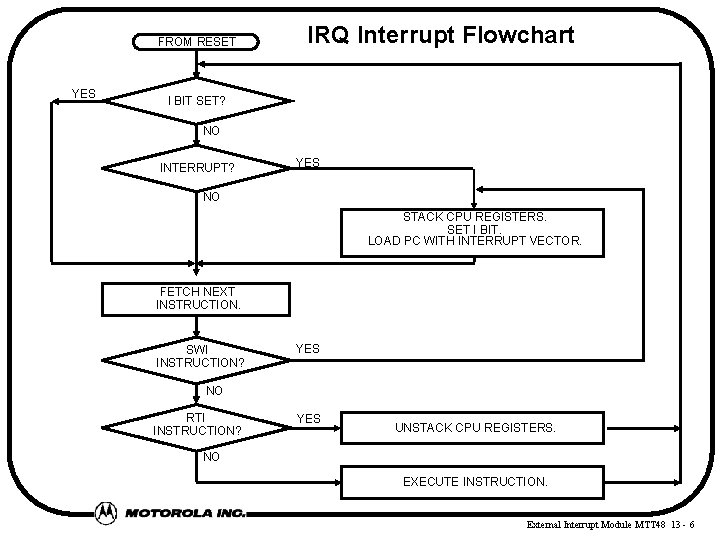

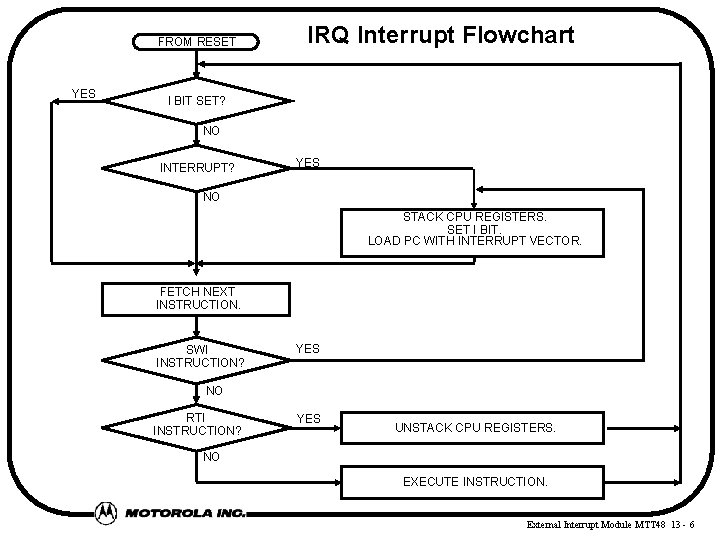

FROM RESET YES IRQ Interrupt Flowchart I BIT SET? NO INTERRUPT? YES NO STACK CPU REGISTERS. SET I BIT. LOAD PC WITH INTERRUPT VECTOR. FETCH NEXT INSTRUCTION. SWI INSTRUCTION? YES NO RTI INSTRUCTION? YES UNSTACK CPU REGISTERS. NO EXECUTE INSTRUCTION. External Interrupt Module MTT 48 13 - 6

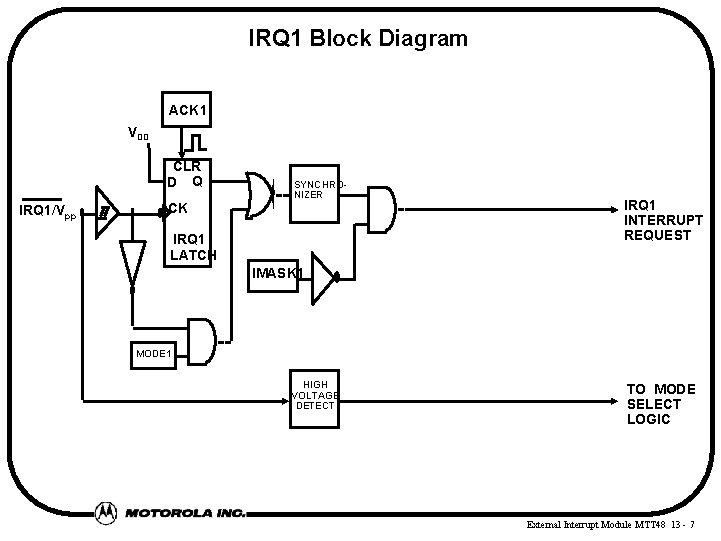

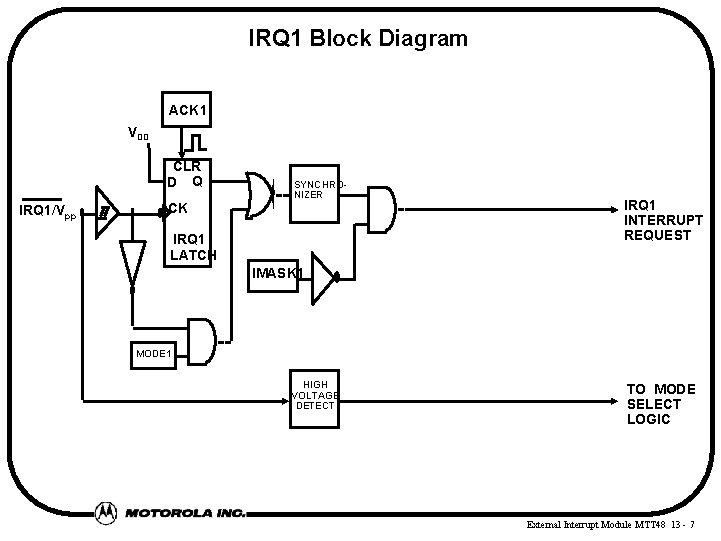

IRQ 1 Block Diagram ACK 1 VDD CLR D Q IRQ 1/Vpp CK SYNCHRONIZER IRQ 1 LATCH IRQ 1 INTERRUPT REQUEST IMASK 1 MODE 1 HIGH VOLTAGE DETECT TO MODE SELECT LOGIC External Interrupt Module MTT 48 13 - 7

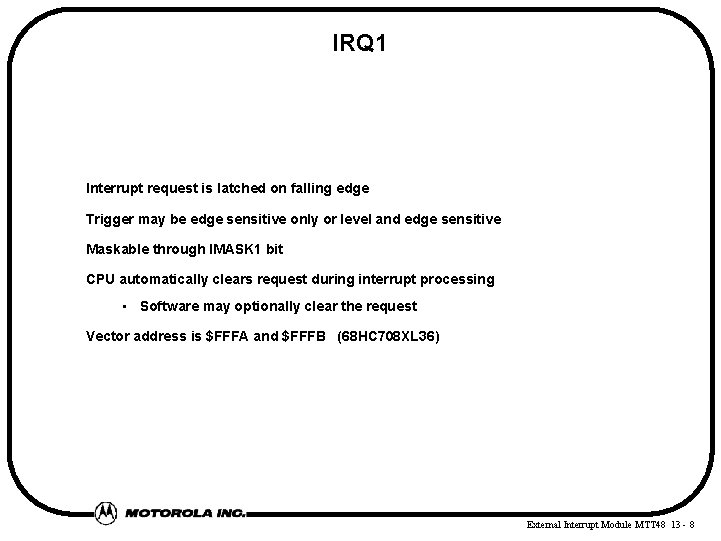

IRQ 1 Interrupt request is latched on falling edge Trigger may be edge sensitive only or level and edge sensitive Maskable through IMASK 1 bit CPU automatically clears request during interrupt processing • Software may optionally clear the request Vector address is $FFFA and $FFFB (68 HC 708 XL 36) External Interrupt Module MTT 48 13 - 8

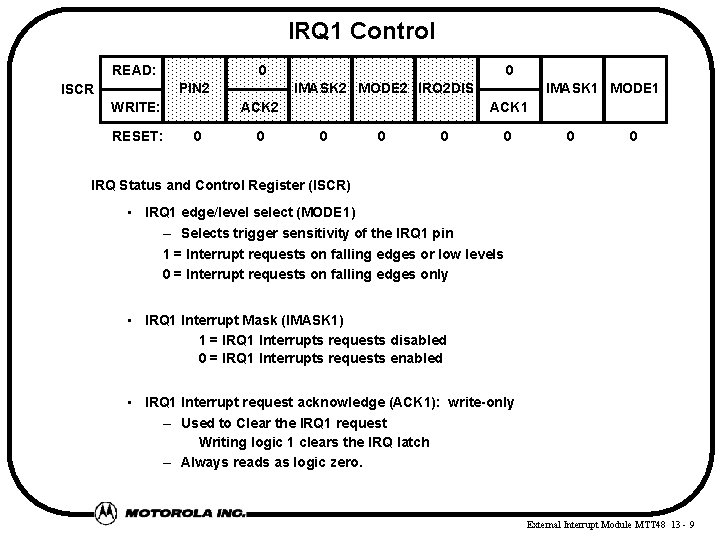

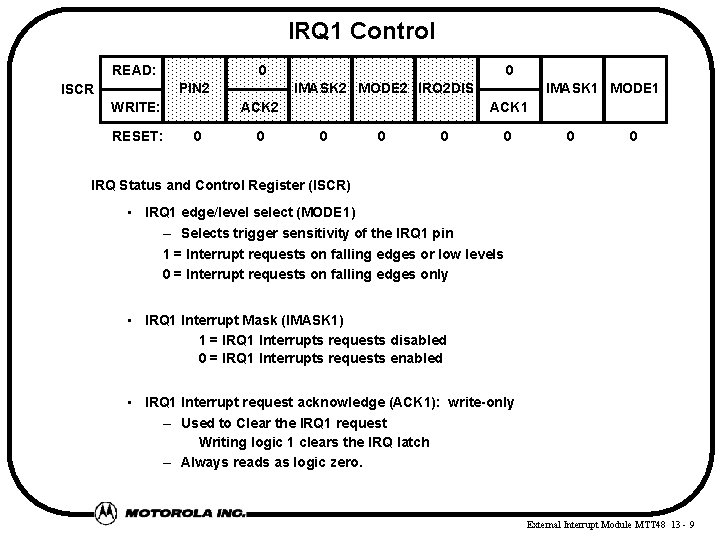

IRQ 1 Control READ: 0 PIN 2 ISCR WRITE: RESET: 0 IMASK 2 MODE 2 IRQ 2 DIS ACK 2 0 0 IMASK 1 MODE 1 ACK 1 0 0 0 IRQ Status and Control Register (ISCR) • IRQ 1 edge/level select (MODE 1) – Selects trigger sensitivity of the IRQ 1 pin 1 = Interrupt requests on falling edges or low levels 0 = Interrupt requests on falling edges only • IRQ 1 Interrupt Mask (IMASK 1) 1 = IRQ 1 Interrupts requests disabled 0 = IRQ 1 Interrupts requests enabled • IRQ 1 Interrupt request acknowledge (ACK 1): write-only – Used to Clear the IRQ 1 request Writing logic 1 clears the IRQ latch – Always reads as logic zero. External Interrupt Module MTT 48 13 - 9

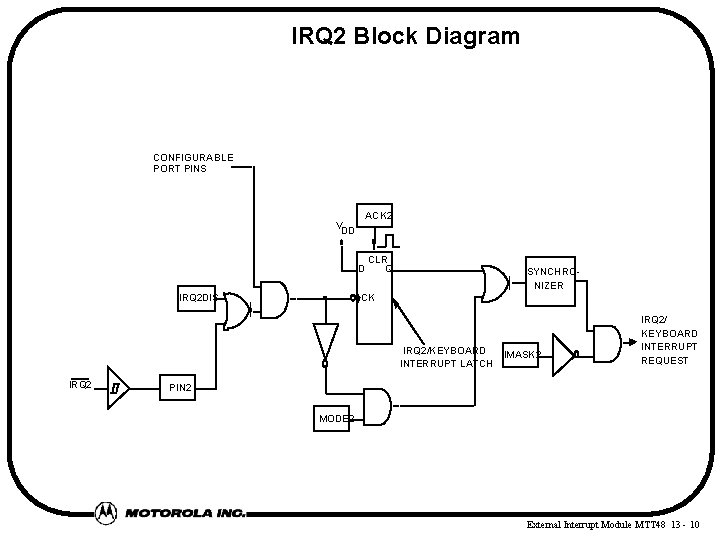

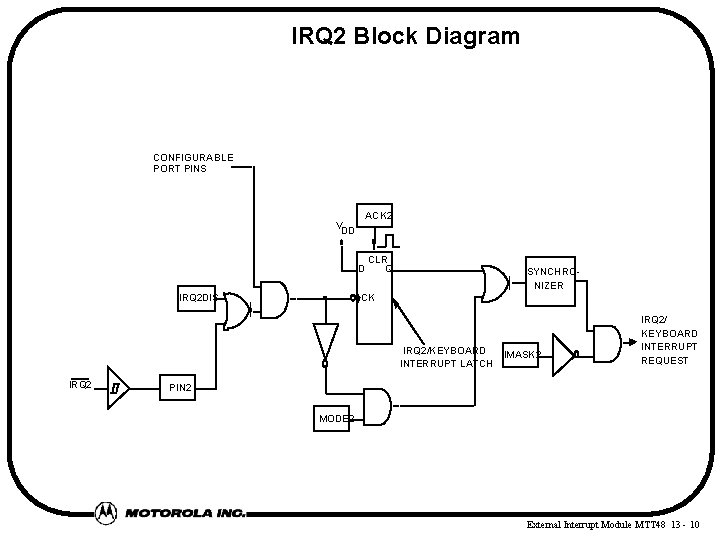

IRQ 2 Block Diagram CONFIGURABLE PORT PINS V DD ACK 2 D IRQ 2 DIS CLR Q SYNCHRONIZER CK IRQ 2/KEYBOARD IMASK 2 INTERRUPT LATCH IRQ 2/ KEYBOARD INTERRUPT REQUEST PIN 2 MODE 2 External Interrupt Module MTT 48 13 - 10

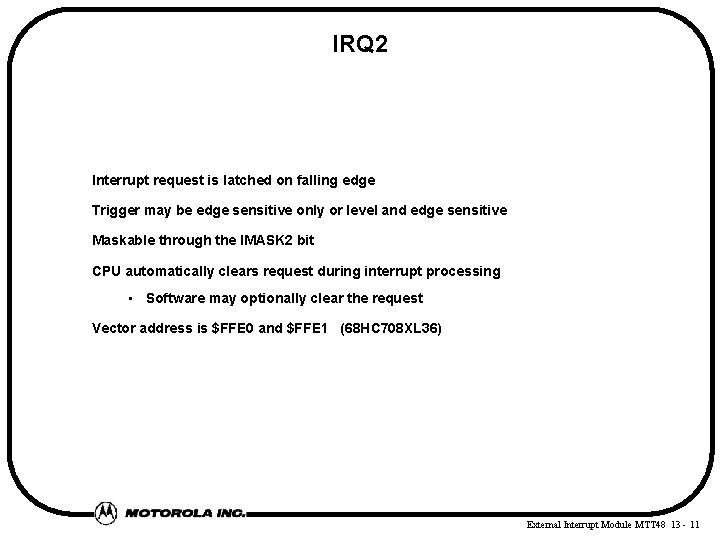

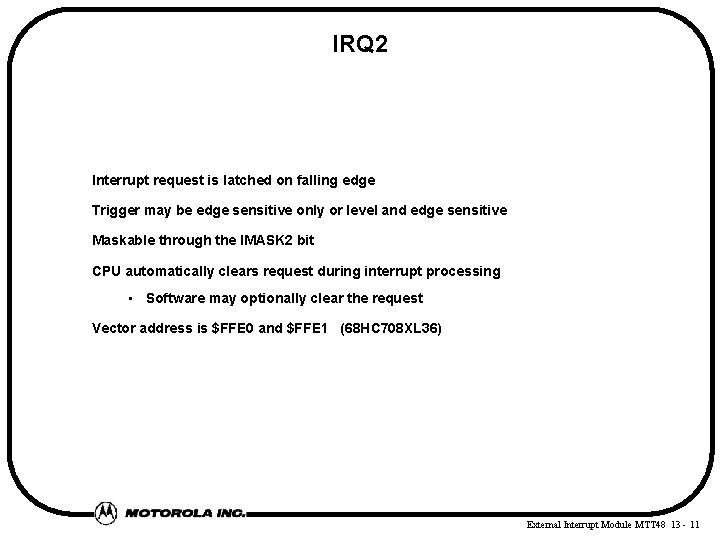

IRQ 2 Interrupt request is latched on falling edge Trigger may be edge sensitive only or level and edge sensitive Maskable through the IMASK 2 bit CPU automatically clears request during interrupt processing • Software may optionally clear the request Vector address is $FFE 0 and $FFE 1 (68 HC 708 XL 36) External Interrupt Module MTT 48 13 - 11

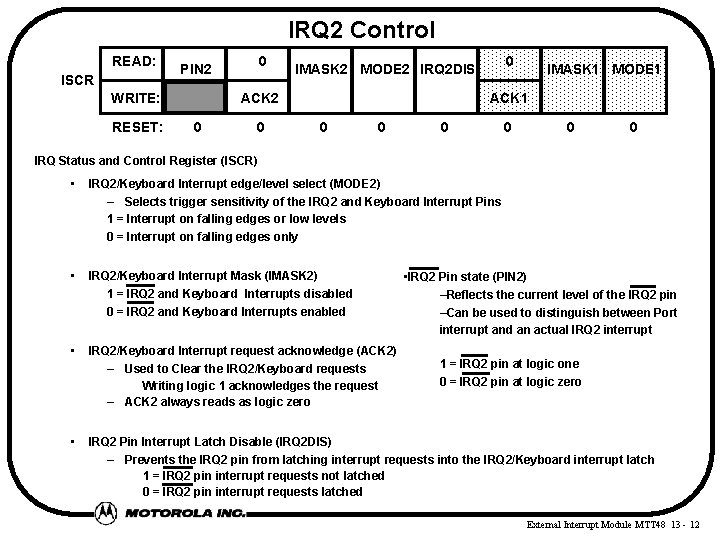

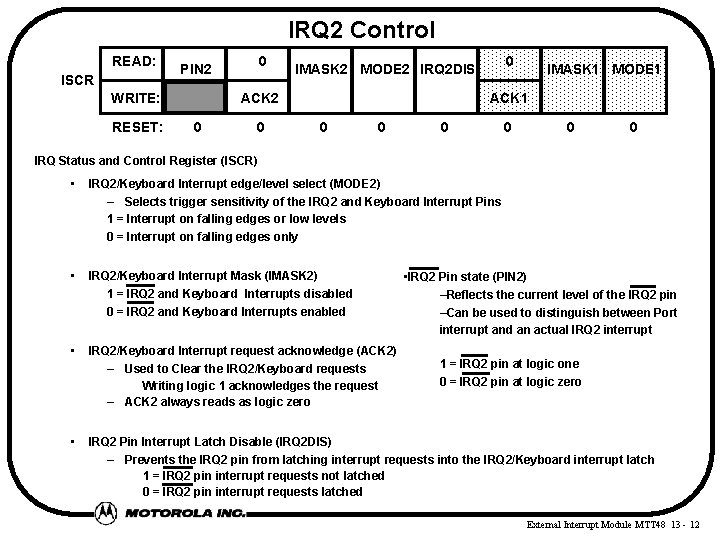

IRQ 2 Control READ: ISCR WRITE: RESET: 0 PIN 2 ACK 2 0 0 IMASK 2 MODE 2 IRQ 2 DIS 0 IMASK 1 MODE 1 ACK 1 0 0 0 IRQ Status and Control Register (ISCR) • IRQ 2/Keyboard Interrupt edge/level select (MODE 2) – Selects trigger sensitivity of the IRQ 2 and Keyboard Interrupt Pins 1 = Interrupt on falling edges or low levels 0 = Interrupt on falling edges only • IRQ 2/Keyboard Interrupt Mask (IMASK 2) 1 = IRQ 2 and Keyboard Interrupts disabled 0 = IRQ 2 and Keyboard Interrupts enabled • IRQ 2/Keyboard Interrupt request acknowledge (ACK 2) – Used to Clear the IRQ 2/Keyboard requests Writing logic 1 acknowledges the request – ACK 2 always reads as logic zero • • IRQ 2 Pin state (PIN 2) –Reflects the current level of the IRQ 2 pin –Can be used to distinguish between Port interrupt and an actual IRQ 2 interrupt 1 = IRQ 2 pin at logic one 0 = IRQ 2 pin at logic zero IRQ 2 Pin Interrupt Latch Disable (IRQ 2 DIS) – Prevents the IRQ 2 pin from latching interrupt requests into the IRQ 2/Keyboard interrupt latch 1 = IRQ 2 pin interrupt requests not latched 0 = IRQ 2 pin interrupt requests latched External Interrupt Module MTT 48 13 - 12

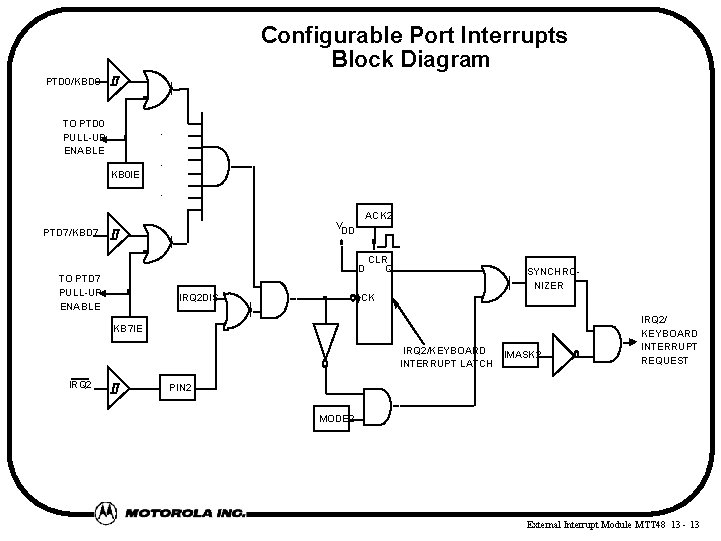

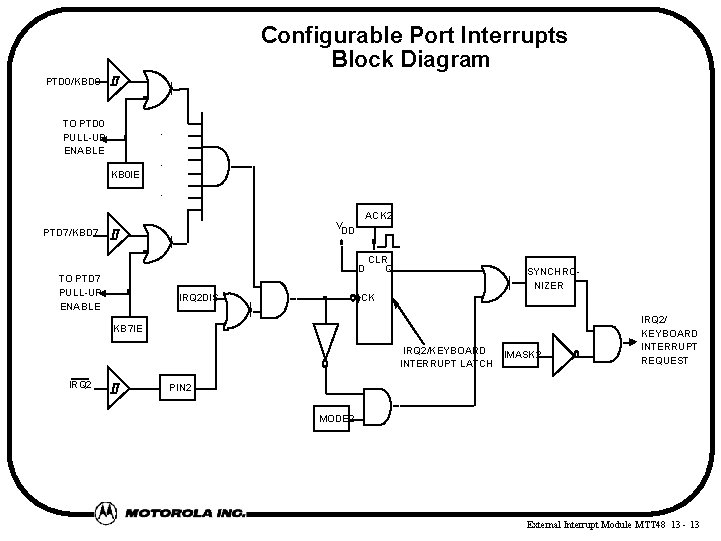

Configurable Port Interrupts Block Diagram PTD 0/KBD 0 TO PTD 0 PULL-UP ENABLE . . KB 0 IE. V DD PTD 7/KBD 7 ACK 2 D TO PTD 7 PULL-UP ENABLE IRQ 2 DIS CLR Q SYNCHRONIZER CK KB 7 IE IRQ 2/KEYBOARD IMASK 2 INTERRUPT LATCH IRQ 2/ KEYBOARD INTERRUPT REQUEST PIN 2 MODE 2 External Interrupt Module MTT 48 13 - 13

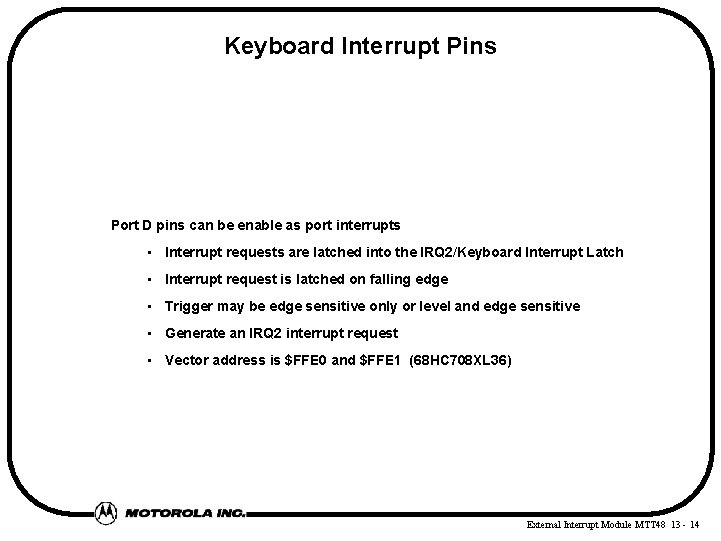

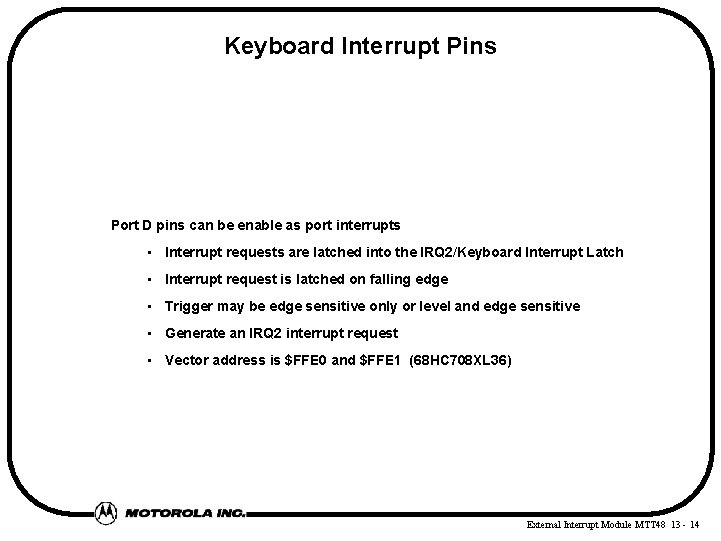

Keyboard Interrupt Pins Port D pins can be enable as port interrupts • Interrupt requests are latched into the IRQ 2/Keyboard Interrupt Latch • Interrupt request is latched on falling edge • Trigger may be edge sensitive only or level and edge sensitive • Generate an IRQ 2 interrupt request • Vector address is $FFE 0 and $FFE 1 (68 HC 708 XL 36) External Interrupt Module MTT 48 13 - 14

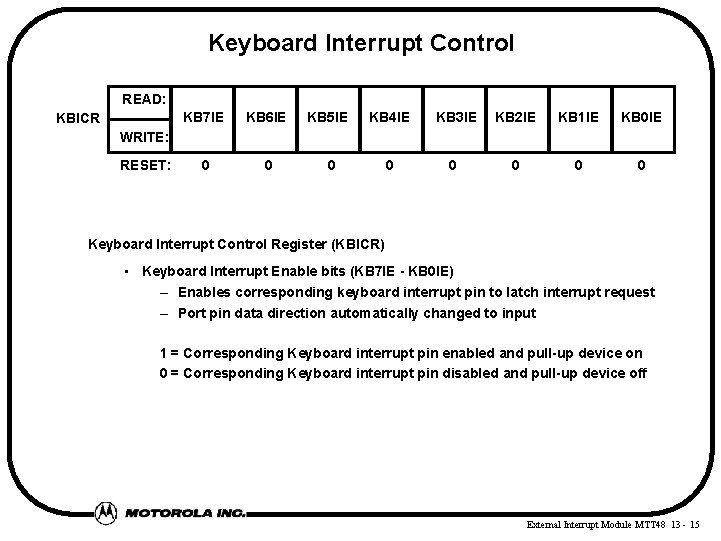

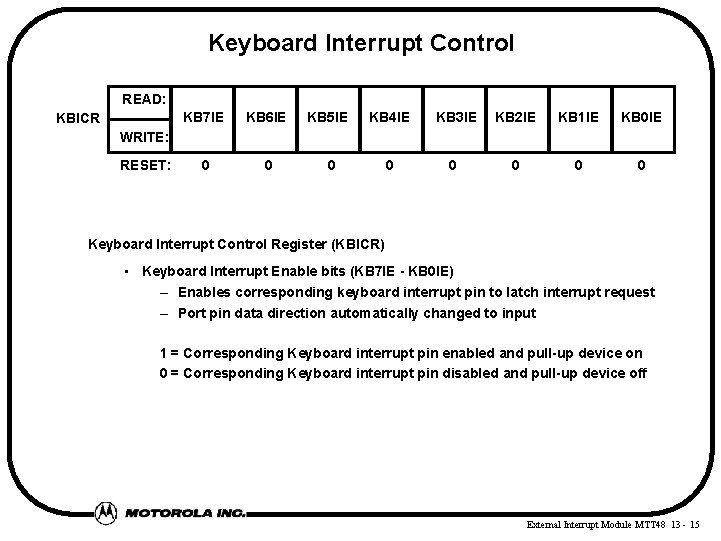

Keyboard Interrupt Control READ: KBICR KB 7 IE KB 6 IE 0 0 KB 5 IE KB 4 IE KB 3 IE KB 2 IE KB 1 IE KB 0 IE 0 0 0 WRITE: RESET: 0 Keyboard Interrupt Control Register (KBICR) • Keyboard Interrupt Enable bits (KB 7 IE - KB 0 IE) – Enables corresponding keyboard interrupt pin to latch interrupt request – Port pin data direction automatically changed to input 1 = Corresponding Keyboard interrupt pin enabled and pull-up device on 0 = Corresponding Keyboard interrupt pin disabled and pull-up device off External Interrupt Module MTT 48 13 - 15

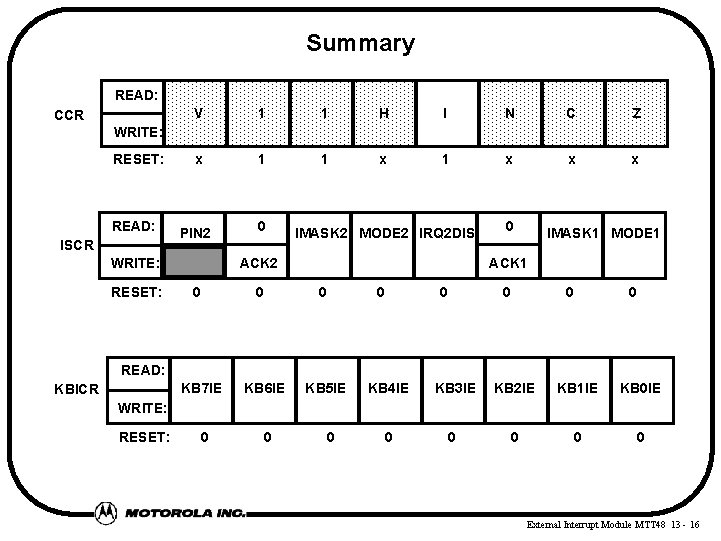

Summary READ: CCR V 1 1 H I N C Z x 1 1 x x x WRITE: RESET: READ: ISCR PIN 2 WRITE: RESET: 0 IMASK 2 MODE 2 IRQ 2 DIS ACK 2 0 0 0 IMASK 1 MODE 1 ACK 1 0 0 0 READ: KBICR KB 7 IE KB 6 IE 0 0 KB 5 IE KB 4 IE KB 3 IE KB 2 IE KB 1 IE KB 0 IE 0 0 0 WRITE: RESET: 0 External Interrupt Module MTT 48 13 - 16